### Silicon Labs - C8051F312 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                         |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                  |

| Number of I/O              | 29                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25К х 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 21x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f312 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

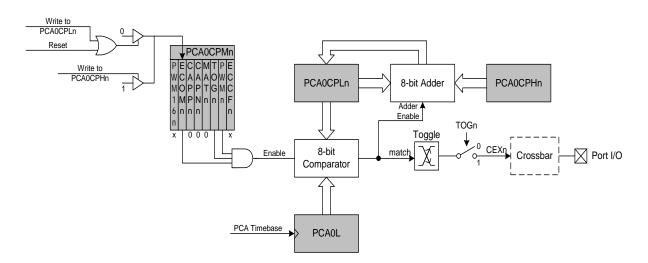

| 18.2.3.High-Speed Output Mode                  | 208 |

|------------------------------------------------|-----|

| 18.2.4. Frequency Output Mode                  | 209 |

| 18.2.5.8-Bit Pulse Width Modulator Mode        |     |

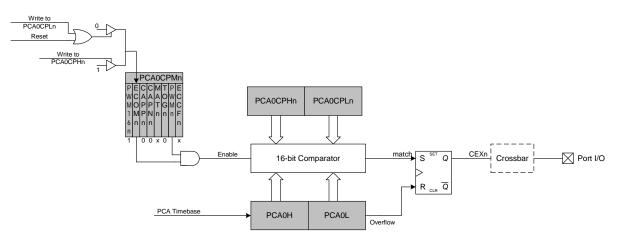

| 18.2.6.16-Bit Pulse Width Modulator Mode       | 211 |

| 18.3.Watchdog Timer Mode                       | 212 |

| 18.3.1.Watchdog Timer Operation                |     |

| 18.3.2.Watchdog Timer Usage                    | 213 |

| 18.4.Register Descriptions for PCA             |     |

| 19. Revision Specific Behavior                 |     |

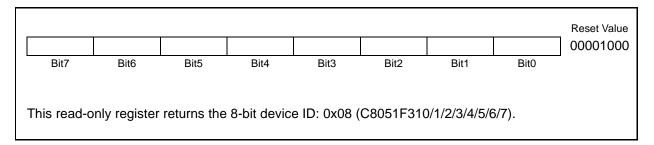

| 19.1.Revision Identification                   |     |

| 19.2.Reset Behavior                            | 221 |

| 19.2.1.Weak Pullups on GPI <u>O P</u> ins      | 221 |

| 19.2.2.V <sub>DD</sub> Monitor and the RST Pin |     |

| 19.3.PCA Counter                               |     |

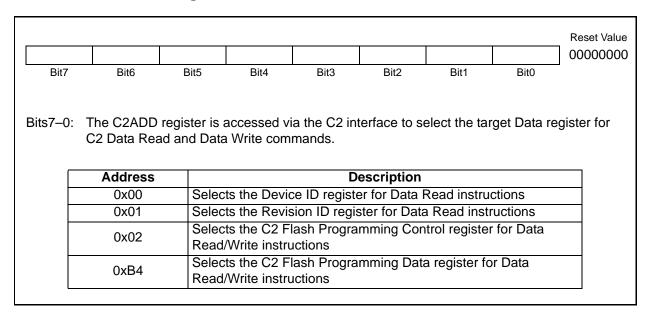

| 20. C2 Interface                               |     |

| 20.1.C2 Interface Registers                    |     |

| -                                              | 225 |

| -                                              | 226 |

|                                                | 228 |

|                                                |     |

NOTES:

### 1. System Overview

C8051F31x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- True 10-bit 200 ksps 25-channel single-ended/differential ADC with analog multiplexer (C8051F310/1/2/3/6)

- Precision programmable 25 MHz internal oscillator

- 16 kB (C8051F310/1/6/7) or 8 kB (C8051F312/3/4/5) of on-chip Flash memory

- 1280 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

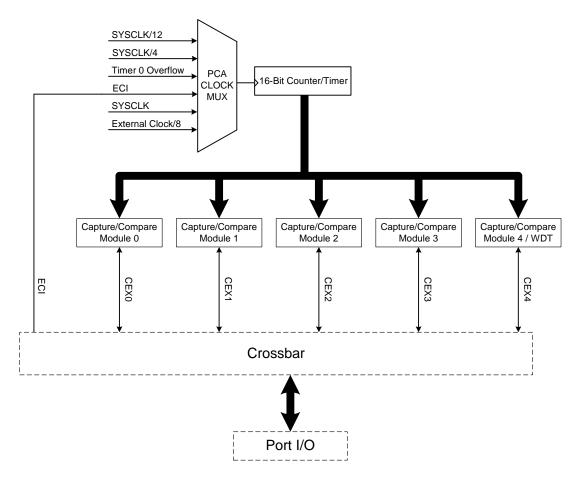

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- On-chip Voltage Comparators (2)

- 29/25/21 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  monitor, Watchdog Timer, and clock oscillator, the C8051F31x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system programming and debugging without occupying package pins.

Each device is specified for 2.7-to-3.6 V operation over the industrial temperature range (–45 to +85 °C). The Port I/O and RST pins are tolerant of input signals up to 5 V. The C8051F31x are available in 32-pin LQFP, 28-pin QFN, and 24-pin QFN packages. See Table 1.1 for ordering part numbers. Note: QFN packages are also referred to as MLP or MLF packages.

Inputs are measured from '0' to VREF \* 1023/1024. Example codes are shown below for both right-justified and left-justified data. Unused bits in the ADC0H and ADC0L registers are set to '0'.

| Input Voltage    | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------|----------------------------------------------|---------------------------------------------|

| VREF x 1023/1024 | 0x03FF                                       | 0xFFC0                                      |

| VREF x 512/1024  | 0x0200                                       | 0x8000                                      |

| VREF x 256/1024  | 0x0100                                       | 0x4000                                      |

| 0                | 0x0000                                       | 0x0000                                      |

When in Differential Mode, conversion codes are represented as 10-bit signed 2's complement numbers. Inputs are measured from -VREF to VREF \* 511/512. Example codes are shown below for both right-justified and left-justified data. For right-justified data, the unused MSBs of ADC0H are a sign-extension of the data word. For left-justified data, the unused LSBs in the ADC0L register are set to '0'.

| Input Voltage   | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|-----------------|----------------------------------------------|---------------------------------------------|

| VREF x 511/512  | 0x01FF                                       | 0x7FC0                                      |

| VREF x 256/512  | 0x0100                                       | 0x4000                                      |

| 0               | 0x0000                                       | 0x0000                                      |

| –VREF x 256/512 | 0xFF00                                       | 0xC000                                      |

| –VREF           | 0xFE00                                       | 0x8000                                      |

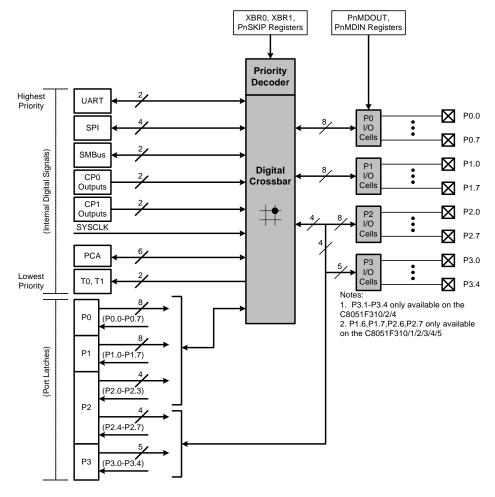

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to '0' the corresponding bit in register PnMDIN (for n = 0,1,2,3). To force the Crossbar to skip a Port pin, set to '1' the corresponding bit in register PnSKIP (for n = 0,1,2). See **Section "13. Port Input/Output" on page 129** for more Port I/O configuration details.

### 5.2. Temperature Sensor

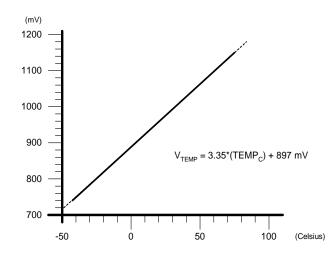

The typical temperature sensor transfer function is shown in Figure 5.2. The output voltage ( $V_{TEMP}$ ) is the positive ADC input when the temperature sensor is selected by bits AMX0P4-0 in register AMX0P.

Figure 5.2. Typical Temperature Sensor Transfer Function

NOTES:

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2). The re-programmable Flash can also be read and changed a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in **Section "20. C2 Interface" on page 223**.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including an editor, evaluation compiler, assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

### 8.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the

| R/W            | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                                | R/W                                                                                                                                | R/W                                                                                                                             | R/W                                                                                                                  | R/W                                                                         | R                                                                     | Reset Value               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| CY             | AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F0                                                                                                                                                 | RS1                                                                                                                                | RS0                                                                                                                             | OV                                                                                                                   | F1                                                                          | PARITY                                                                | 00000000                  |

| Bit7           | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                               | Bit4                                                                                                                               | Bit3                                                                                                                            | Bit2                                                                                                                 | Bit1                                                                        | Bit0                                                                  | SFR Address               |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      | (bi                                                                         | t addressable)                                                        | 0xD0                      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| Bit7:          | CY: Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Flag.                                                                                                                                              |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | he last arithmet                                                                                                                   |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       | a borrow                  |

|                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                  | eared to logic 0 l                                                                                                                 | by all other                                                                                                                    | arithmetic                                                                                                           | operations                                                                  |                                                                       |                           |

| Bit6:          | AC: Auxilia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    | •                                                                                                                                  |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | ne last arithmeti                                                                                                                  | •                                                                                                                               |                                                                                                                      |                                                                             | ```                                                                   |                           |

|                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | raction) the                                                                                                                                       | e high order nib                                                                                                                   | ble. It is cle                                                                                                                  | eared to log                                                                                                         | gic 0 by all o                                                              | other arithm                                                          | etic opera-               |

| D:46.          | tions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| Bit5:          | F0: User F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                  | oble general p                                                                                                                     | urnaaa flag                                                                                                                     | forupaup                                                                                                             | dor ooftwor                                                                 | o control                                                             |                           |

| Bits4–3:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | able, general pu<br>Bank Select.                                                                                                   | irpose nag                                                                                                                      | tor use un                                                                                                           | der soltware                                                                | e control.                                                            |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| DII54-5.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  |                                                                                                                                    | k is used d                                                                                                                     | uring rogic                                                                                                          | tor accore                                                                  |                                                                       |                           |

| DII54-5.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  | ich register ban                                                                                                                   | k is used d                                                                                                                     | luring regis                                                                                                         | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  |                                                                                                                                    | _                                                                                                                               |                                                                                                                      | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh                                                                                                                                          | ich register ban                                                                                                                   | _                                                                                                                               | ess                                                                                                                  | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh                                                                                                                                          | ich register ban<br>Register Bank                                                                                                  | Addr                                                                                                                            | <b>ess</b><br>0x07                                                                                                   | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits RS1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | select wh                                                                                                                                          | ich register ban<br>Register Bank<br>0                                                                                             | Addr<br>0x00-                                                                                                                   | <b>ess</b><br>0x07<br>0x0F                                                                                           | ter accesse                                                                 | 95.                                                                   |                           |

| Ы134—3.        | These bits          RS1         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | select wh<br>RS0<br>0<br>1                                                                                                                         | ich register ban<br>Register Bank<br>0<br>1                                                                                        | Addr<br>0x00-<br>0x08-                                                                                                          | ess<br>0x07<br>0x0F<br>0x17                                                                                          | ter accesse                                                                 | 95.                                                                   |                           |

|                | RS1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th="">         1         <th1< th=""> <th1< th=""></th1<></th1<></th1<> | select wh<br><b>RS0</b><br>0<br>1<br>0<br>1                                                                                                        | ich register ban<br>Register Bank<br>0<br>1<br>2                                                                                   | Addr<br>0x00-<br>0x08-<br>0x10-                                                                                                 | ess<br>0x07<br>0x0F<br>0x17                                                                                          | ter accesse                                                                 | es.                                                                   |                           |

|                | These bits          RS1         0         1         1         OV: Overfit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.                                                                                                   | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3                                                                              | Addr           0x00-           0x08-           0x10-           0x18-                                                            | ess<br>0x07<br>0x0F<br>0x17<br>0x1F                                                                                  |                                                                             |                                                                       |                           |

|                | These bits          RS1         0         1         1         OV: Overfi         This bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un                                                                                    | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>der the followin                                                          | Addr           0x00-           0x08-           0x10-           0x18-           g circumsta                                      | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /                                                                   | ADD, ADDC                                                                   | C, or SUBB i                                                          |                           |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang                                                                      | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>ider the followin<br>je overflow, a M                                     | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta                                                                         | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an <i>I</i><br>cion results                                            | ADD, ADDC                                                                   | C, or SUBB i<br>low (result is                                        | s greater                 |

|                | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in                                                       | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause                                       | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta<br>UL instruct<br>es a divide                                           | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /<br>tion results<br>-by-zero co                                    | ADD, ADDC<br>in an overfl<br>indition. The                                  | C, or SUBB i<br>low (result is<br>e OV bit is c                       | s greater                 |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,                                           | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>ider the followin<br>je overflow, a M                                     | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta<br>UL instruct<br>es a divide                                           | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /<br>tion results<br>-by-zero co                                    | ADD, ADDC<br>in an overfl<br>indition. The                                  | C, or SUBB i<br>low (result is<br>e OV bit is c                       | s greater                 |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADIF1: User F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>flag 1.                                | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>le overflow, a M<br>nstruction cause<br>SUBB, MUL, ar | Addr       0x00–       0x08–       0x10–       0x18–       g circumsta       UL instructed       a divided       DIV instructed | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an A<br>cion results<br>-by-zero co<br>ructions in                     | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas                 | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.               | s greater                 |

| Bit2:<br>Bit1: | These bitsRS100110V: OverfiThis bit iscauses a sthan 255),by the ADIF1: User FThis is a b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>Tlag 1.<br>it-addressa                 | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause<br>SUBB, MUL, ar<br>able, general pu  | Addr       0x00–       0x08–       0x10–       0x18–       g circumsta       UL instructed       a divided       DIV instructed | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an A<br>cion results<br>-by-zero co<br>ructions in                     | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas                 | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.               | s greater                 |

|                | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADIF1: User FThis is a bPARITY: F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>flag 1.<br>it-addressa<br>'arity Flag. | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause<br>SUBB, MUL, ar<br>able, general pu  | g circumsta<br>UL instruct<br>a divide-<br>d DIV instruct<br>urpose flag                                                        | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an <i>I</i><br>ion results<br>-by-zero co<br>ructions in<br>for use un | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas<br>der software | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.<br>e control. | s greater<br>cleared to ( |

### SFR Definition 8.4. PSW: Program Status Word

## SFR Definition 8.5. ACC: Accumulator

| R/W<br>ACC.7 | R/W<br>ACC.6                | R/W<br>ACC.5 | R/W<br>ACC.4 | R/W<br>ACC.3 | R/W<br>ACC.2 | R/W<br>ACC.1 | R/W<br>ACC.0   | Reset Value  |

|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|----------------|--------------|

| Bit7         | Bit6                        | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0           | SFR Address: |

| Bitt         | Eno                         | 2.10         | Ditt         | 2.10         | BILL         |              | t addressable) |              |

|              | ACC: Accum<br>This register |              | mulator for  | arithmetic o | operations.  |              |                |              |

| SFR Definition | n 8.9. EIE1: | Extended | Interrupt | Enable 1 |

|----------------|--------------|----------|-----------|----------|

|----------------|--------------|----------|-----------|----------|

| R/W   | R/W                            | R/W         | R/W         | R/W           | R/W        | R/W           | R/W       | Reset Value  |

|-------|--------------------------------|-------------|-------------|---------------|------------|---------------|-----------|--------------|

| ET3   | ECP1                           | ECP0        | EPCA0       | EADC0         | EWADC0     | Reserved      | ESMB0     | 00000000     |

| Bit7  | Bit6                           | Bit5        | Bit4        | Bit3          | Bit2       | Bit1          | Bit0      | SFR Address: |

|       |                                |             |             |               |            |               |           | 0xE6         |

| Bit7: | ET3: Enable                    | Timer 3 Int | errupt.     |               |            |               |           |              |

|       | This bit sets                  |             |             | ner 3 interru | pt.        |               |           |              |

|       | 0: Disable Ti                  |             | •           |               | 1          |               |           |              |

|       | 1: Enable int                  | errupt requ | ests genera | ated by the   | TF3L or TF | 3H flags.     |           |              |

| Bit6: | ECP1: Enab                     | le Compara  | ator1 (CP1) | Interrupt.    |            | -             |           |              |

|       | This bit sets                  | the maskin  | g of the CP | 1 interrupt.  |            |               |           |              |

|       | 0: Disable C                   |             |             |               |            |               |           |              |

|       | 1: Enable int                  |             | •           | •             | CP1RIF or  | CP1FIF flag   | S.        |              |

| Bit5: | ECP0: Enab                     |             |             |               |            |               |           |              |

|       | This bit sets                  |             | •           | 0 interrupt.  |            |               |           |              |

|       | 0: Disable C                   |             |             |               |            |               |           |              |

| D'14  | 1: Enable int                  |             |             |               |            |               | S.        |              |

| Bit4: | EPCA0: Ena                     | •           |             |               | ` '        | errupt.       |           |              |

|       | This bit sets<br>0: Disable al |             | •           | AU Interrup   | IS.        |               |           |              |

|       | 1: Enable int                  |             | •           | ated by PC/   | 0          |               |           |              |

| Bit3: | EADC0: Ena                     |             | •           | •             |            |               |           |              |

| Dito. | This bit sets                  |             |             |               |            | ete interrunt |           |              |

|       | 0: Disable A                   |             |             |               |            |               |           |              |

|       | 1: Enable int                  |             |             |               | •          | J.            |           |              |

| Bit2: | EWADC0: E                      |             | •           |               |            | 5             |           |              |

|       | This bit sets                  |             |             |               | •          | terrupt.      |           |              |

|       | 0: Disable A                   |             | •           |               |            | •             |           |              |

|       | 1: Enable int                  | errupt requ | ests genera | ated by AD    | C0 Window  | Compare fla   | ig (AD0WI | NT).         |

| Bit1: | RESERVED                       | . Read = 0. | Must Write  | e 0.          |            |               | -         |              |

| Bit0: | ESMB0: Ena                     | able SMBus  | s (SMB0) In | terrupt.      |            |               |           |              |

|       | This bit sets                  |             |             | 1B0 interrup  | t.         |               |           |              |

|       | 0: Disable al                  |             |             |               |            |               |           |              |

|       | 1: Enable int                  | errupt requ | ests genera | ated by SMI   | 30.        |               |           |              |

### 9.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read '1', signifying the MCD as the reset source; otherwise, this bit reads '0'. Writing a '1' to the MCDRSF bit enables the Missing Clock Detector; writing a '0' disables it. The state of the RST pin is unaffected by this reset.

### 9.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

### 9.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in **Section "18.3. Watchdog Timer Mode" on page 212**; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

### 9.7. Flash Error Reset