Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

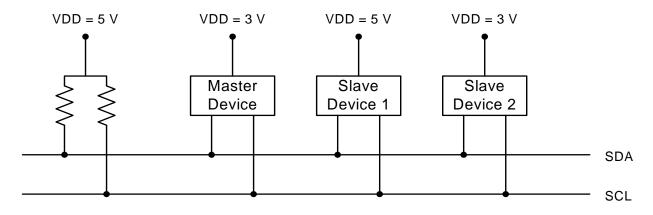

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25К х 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 17x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 28-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 28-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f313-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR | Definition | 13.5. P0MDOUT: Port0 Output Mode                     | 137 |

|-----|------------|------------------------------------------------------|-----|

| SFR | Definition | 13.6. P0SKIP: Port0 Skip                             | 137 |

| SFR | Definition | 13.7. P1: Port1                                      | 138 |

| SFR | Definition | 13.8. P1MDIN: Port1 Input Mode                       | 138 |

| SFR | Definition | 13.9. P1MDOUT: Port1 Output Mode                     | 139 |

| SFR | Definition | 13.10. P1SKIP: Port1 Skip                            | 139 |

| SFR | Definition | 13.11. P2: Port2                                     | 140 |

| SFR | Definition | 13.12. P2MDIN: Port2 Input Mode                      | 140 |

|     |            | 13.13. P2MDOUT: Port2 Output Mode                    |     |

| SFR | Definition | 13.14. P2SKIP: Port2 Skip                            | 141 |

| SFR | Definition | 13.15. P3: Port3                                     | 142 |

| SFR | Definition | 13.16. P3MDIN: Port3 Input Mode                      | 142 |

| SFR | Definition | 13.17. P3MDOUT: Port3 Output Mode                    | 143 |

|     |            | 14.1. SMB0CF: SMBus Clock/Configuration              |     |

|     |            | 14.2. SMB0CN: SMBus Control                          |     |

| SFR | Definition | 14.3. SMB0DAT: SMBus Data                            | 156 |

| SFR | Definition | 15.1. SCON0: Serial Port 0 Control                   | 168 |

| SFR | Definition | 15.2. SBUF0: Serial (UART0) Port Data Buffer         | 169 |

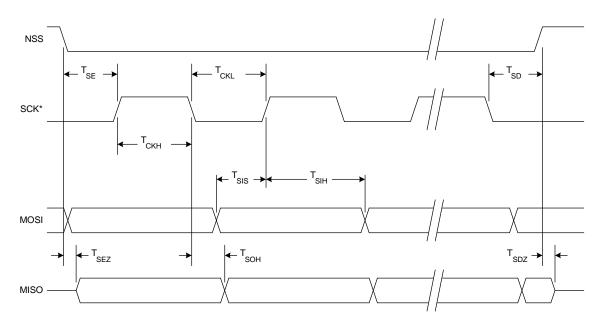

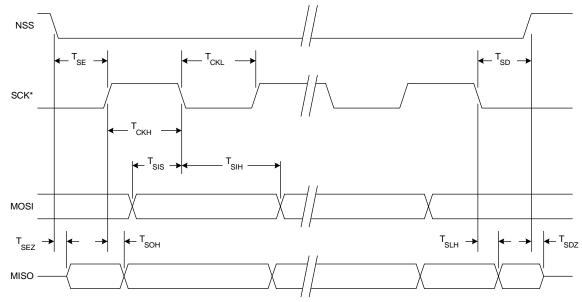

| SFR | Definition | 16.1. SPI0CFG: SPI0 Configuration                    | 180 |

|     |            | 16.2. SPI0CN: SPI0 Control                           |     |

| SFR | Definition | 16.3. SPI0CKR: SPI0 Clock Rate                       | 182 |

| SFR | Definition | 16.4. SPI0DAT: SPI0 Data                             | 182 |

|     |            | 17.1. TCON: Timer Control                            |     |

|     |            | 17.2. TMOD: Timer Mode                               |     |

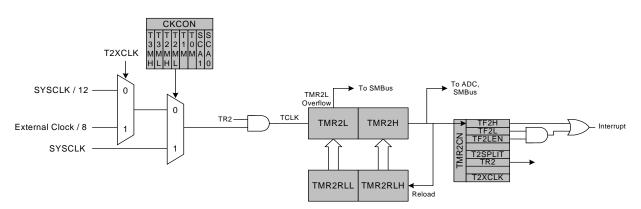

| SFR | Definition | 17.3. CKCON: Clock Control                           | 193 |

| SFR | Definition | 17.4. TL0: Timer 0 Low Byte                          | 194 |

|     |            | 17.5. TL1: Timer 1 Low Byte                          |     |

|     |            | 17.6. THO: Timer 0 High Byte                         |     |

|     |            | 17.7. TH1: Timer 1 High Byte                         |     |

| SFR | Definition | 17.8. TMR2CN: Timer 2 Control                        | 197 |

| SFR | Definition | 17.9. TMR2RLL: Timer 2 Reload Register Low Byte      | 198 |

| SFR | Definition | 17.10. TMR2RLH: Timer 2 Reload Register High Byte    | 198 |

| SFR | Definition | 17.11. TMR2L: Timer 2 Low Byte                       | 198 |

|     |            | 17.12. TMR2H Timer 2 High Byte                       |     |

| SFR | Definition | 17.13. TMR3CN: Timer 3 Control                       | 201 |

| SFR | Definition | 17.14. TMR3RLL: Timer 3 Reload Register Low Byte     | 202 |

| SFR | Definition | 17.15. TMR3RLH: Timer 3 Reload Register High Byte    | 202 |

|     |            | 17.16. TMR3L: Timer 3 Low Byte                       |     |

|     |            | 17.17. TMR3H Timer 3 High Byte                       |     |

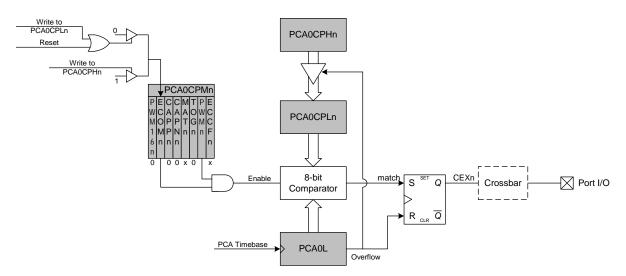

|     |            | 18.1. PCA0CN: PCA Control                            |     |

| SFR | Definition | 18.2. PCA0MD: PCA Mode                               | 216 |

| SFR | Definition | 18.3. PCA0CPMn: PCA Capture/Compare Mode Registers . | 217 |

|     |            | 18.4. PCA0L: PCA Counter/Timer Low Byte              |     |

|     |            | 18.5. PCA0H: PCA Counter/Timer High Byte             |     |

|     |            | 18.6. PCA0CPLn: PCA Capture Module Low Byte          |     |

|     |            |                                                      |     |

# C8051F310/1/2/3/4/5/6/7

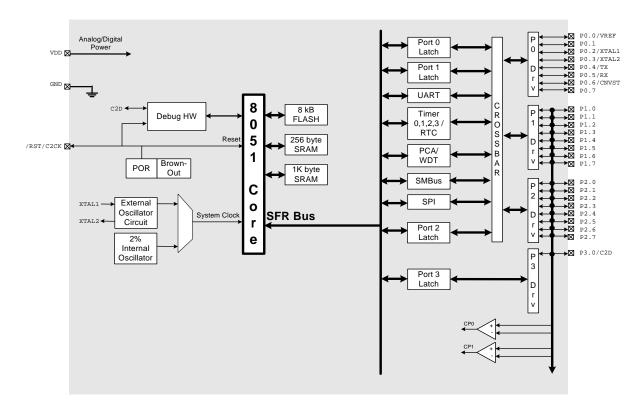

Figure 1.6. C8051F315 Block Diagram

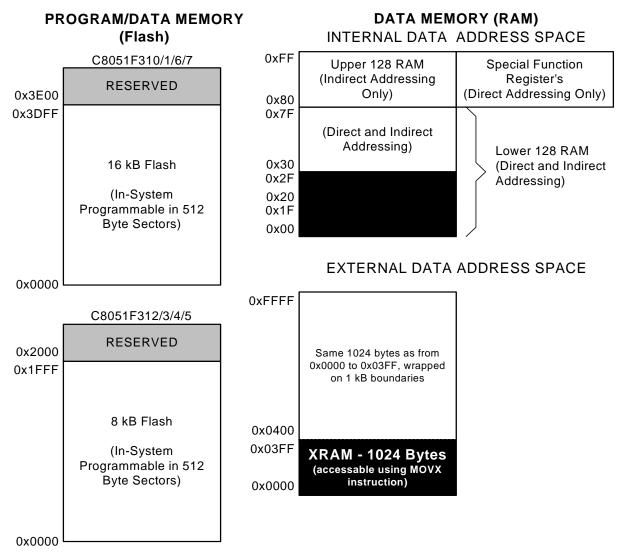

## 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory consists of 8 or 16 kB of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.11 for the MCU system memory map.

Figure 1.11. On-Board Memory Map

# C8051F310/1/2/3/4/5/6/7

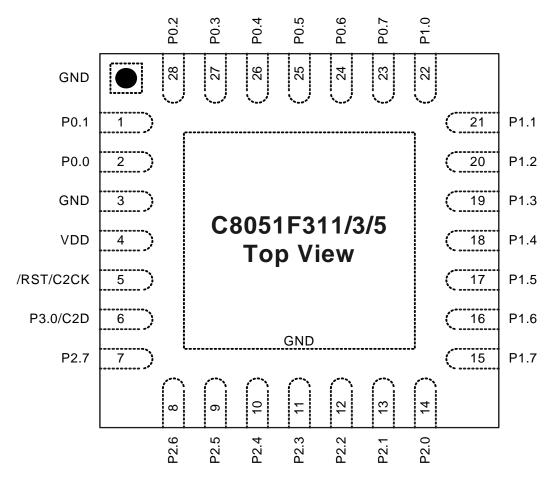

Figure 4.3. QFN-28 Pinout Diagram (Top View)

| R/W      | R              | R/W           | R/W        | R/W          | R/W           | R/W             | R/W        | Reset Value  |

|----------|----------------|---------------|------------|--------------|---------------|-----------------|------------|--------------|

| CP0EN    | CP0OUT         | <b>CP0RIF</b> | CP0FIF     | CP0HYP1      | CP0HYP0       | CP0HYN1         | CP0HYN0    | 00000000     |

| Bit7     | Bit6           | Bit5          | Bit4       | Bit3         | Bit2          | Bit1            | Bit0       | SFR Address: |

|          |                |               |            |              |               |                 |            | 0x9B         |

|          |                |               |            |              |               |                 |            |              |

| Bit7:    | CP0EN: Cor     | nparator0 E   | nable Bit. |              |               |                 |            |              |

|          | 0: Comparat    | or0 Disable   | d.         |              |               |                 |            |              |

|          | 1: Comparat    |               |            |              |               |                 |            |              |

| Bit6:    | CP0OUT: Co     |               |            | ate Flag.    |               |                 |            |              |

|          | 0: Voltage or  |               |            |              |               |                 |            |              |

|          | 1: Voltage or  |               |            |              |               |                 |            |              |

| Bit5:    | CPORIF: Co     |               |            |              |               |                 |            |              |

|          | 0: No Comp     |               | 0 0        |              |               | ice this flag   | was last c | leared.      |

| DitA     | 1: Comparat    | -             | -          | •            |               |                 |            |              |

| Bit4:    | CP0FIF: Co     |               |            |              |               | a a a thia flag |            |              |

|          | 0: No Comparat |               |            |              |               | nce this hag    | was last c | cieareo.     |

| Bits3-2: | CP0HYP1-0      |               |            |              |               | -               |            |              |

| Dit35-2. | 00: Positive   |               |            | errysteresis |               | 5.              |            |              |

|          | 01: Positive   |               |            |              |               |                 |            |              |

|          | 10: Positive   |               |            |              |               |                 |            |              |

|          | 11: Positive   |               |            |              |               |                 |            |              |

| Bits1–0: | CP0HYN1-0      |               |            | ve Hvsteres  | is Control Bi | its.            |            |              |

|          | 00: Negative   | •             | -          | •            |               |                 |            |              |

|          | 01: Negative   |               |            |              |               |                 |            |              |

|          | 10: Negative   | e Hysteresis  | = 10 mV.   |              |               |                 |            |              |

|          | 11: Negative   | Hysteresis    | = 20 mV.   |              |               |                 |            |              |

|          |                |               |            |              |               |                 |            |              |

## SFR Definition 7.1. CPT0CN: Comparator0 Control

| R/W            | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                                | R/W                                                                                                                                | R/W                                                                                                                             | R/W                                                                                                                  | R/W                                                                         | R                                                                     | Reset Value               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| CY             | AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F0                                                                                                                                                 | RS1                                                                                                                                | RS0                                                                                                                             | OV                                                                                                                   | F1                                                                          | PARITY                                                                | 00000000                  |

| Bit7           | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                               | Bit4                                                                                                                               | Bit3                                                                                                                            | Bit2                                                                                                                 | Bit1                                                                        | Bit0                                                                  | SFR Address               |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      | (bi                                                                         | t addressable)                                                        | 0xD0                      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| Bit7:          | CY: Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Flag.                                                                                                                                              |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | he last arithmet                                                                                                                   |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       | a borrow                  |

|                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                  | eared to logic 0 l                                                                                                                 | by all other                                                                                                                    | arithmetic                                                                                                           | operations                                                                  |                                                                       |                           |

| Bit6:          | AC: Auxilia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    | •                                                                                                                                  |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | ne last arithmeti                                                                                                                  | •                                                                                                                               |                                                                                                                      |                                                                             | ```                                                                   |                           |

|                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | raction) the                                                                                                                                       | e high order nib                                                                                                                   | ble. It is cle                                                                                                                  | eared to log                                                                                                         | gic 0 by all o                                                              | other arithm                                                          | etic opera-               |

| D:46.          | tions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| Bit5:          | F0: User F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                  | oble general p                                                                                                                     | urpage flog                                                                                                                     | forupaup                                                                                                             | dor ooftwor                                                                 | o control                                                             |                           |

| Bits4–3:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | able, general pu<br>Bank Select.                                                                                                   | irpose nag                                                                                                                      | tor use un                                                                                                           | der soltware                                                                | e control.                                                            |                           |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                    |                                                                                                                                 |                                                                                                                      |                                                                             |                                                                       |                           |

| DII54-5.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  |                                                                                                                                    | k is used d                                                                                                                     | uring rogic                                                                                                          | tor accore                                                                  |                                                                       |                           |

| DII54-5.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  | ich register ban                                                                                                                   | k is used d                                                                                                                     | luring regis                                                                                                         | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                  |                                                                                                                                    | _                                                                                                                               |                                                                                                                      | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh                                                                                                                                          | ich register ban                                                                                                                   | _                                                                                                                               | ess                                                                                                                  | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh                                                                                                                                          | ich register ban<br>Register Bank                                                                                                  | Addr                                                                                                                            | <b>ess</b><br>0x07                                                                                                   | ter accesse                                                                 | es.                                                                   |                           |

| DII34-3.       | These bits RS1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | select wh                                                                                                                                          | ich register ban<br>Register Bank<br>0                                                                                             | Addr<br>0x00-                                                                                                                   | <b>ess</b><br>0x07<br>0x0F                                                                                           | ter accesse                                                                 | 95.                                                                   |                           |

| Ы134—3.        | These bits          RS1         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | select wh<br>RS0<br>0<br>1                                                                                                                         | ich register ban<br>Register Bank<br>0<br>1                                                                                        | Addr<br>0x00-<br>0x08-                                                                                                          | ess<br>0x07<br>0x0F<br>0x17                                                                                          | ter accesse                                                                 | 95.                                                                   |                           |

|                | RS1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th="">         1         <th1< th=""> <th1< th=""></th1<></th1<></th1<> | select wh<br><b>RS0</b><br>0<br>1<br>0<br>1                                                                                                        | ich register ban<br>Register Bank<br>0<br>1<br>2                                                                                   | Addr<br>0x00-<br>0x08-<br>0x10-                                                                                                 | ess<br>0x07<br>0x0F<br>0x17                                                                                          | ter accesse                                                                 | es.                                                                   |                           |

|                | These bits          RS1         0         1         1         OV: Overfit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.                                                                                                   | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3                                                                              | Addr           0x00-           0x08-           0x10-           0x18-                                                            | ess<br>0x07<br>0x0F<br>0x17<br>0x1F                                                                                  |                                                                             |                                                                       |                           |

|                | These bits          RS1         0         1         1         OV: Overfi         This bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un                                                                                    | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>der the followin                                                          | Addr           0x00-           0x08-           0x10-           0x18-           g circumsta                                      | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /                                                                   | ADD, ADDC                                                                   | C, or SUBB i                                                          |                           |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang                                                                      | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>ider the followin<br>je overflow, a M                                     | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta                                                                         | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an <i>I</i><br>cion results                                            | ADD, ADDC                                                                   | C, or SUBB i<br>low (result is                                        | s greater                 |

|                | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in                                                       | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause                                       | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta<br>UL instruct<br>es a divide                                           | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /<br>tion results<br>-by-zero co                                    | ADD, ADDC<br>in an overfl<br>indition. The                                  | C, or SUBB i<br>low (result is<br>e OV bit is c                       | s greater                 |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,                                           | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>ider the followin<br>je overflow, a M                                     | Addr<br>0x00–<br>0x08–<br>0x10–<br>0x18–<br>g circumsta<br>UL instruct<br>es a divide                                           | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an /<br>tion results<br>-by-zero co                                    | ADD, ADDC<br>in an overfl<br>indition. The                                  | C, or SUBB i<br>low (result is<br>e OV bit is c                       | s greater                 |

| Bit2:          | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADIF1: User F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>flag 1.                                | ich register ban<br>Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>le overflow, a M<br>nstruction cause<br>SUBB, MUL, ar | Addr       0x00–       0x08–       0x10–       0x18–       g circumsta       UL instructed       a divided       DIV instructed | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an A<br>cion results<br>-by-zero co<br>ructions in                     | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas                 | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.               | s greater                 |

| Bit2:<br>Bit1: | These bitsRS100110V: OverfiThis bit iscauses a sthan 255),by the ADIF1: User FThis is a b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>Tlag 1.<br>it-addressa                 | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause<br>SUBB, MUL, ar<br>able, general pu  | Addr       0x00–       0x08–       0x10–       0x18–       g circumsta       UL instructed       a divided       DIV instructed | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an A<br>cion results<br>-by-zero co<br>ructions in                     | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas                 | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.               | s greater                 |

|                | These bitsRS10011OV: OverfiThis bit iscauses a sthan 255),by the ADIF1: User FThis is a bPARITY: F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | select wh<br>RS0<br>0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 un<br>sign-chang<br>or a DIV in<br>D, ADDC,<br>flag 1.<br>it-addressa<br>'arity Flag. | Register Bank<br>0<br>1<br>2<br>3<br>der the followin<br>e overflow, a M<br>nstruction cause<br>SUBB, MUL, ar<br>able, general pu  | g circumsta<br>UL instructes a divide-<br>d DIV instructor                                                                      | ess<br>0x07<br>0x0F<br>0x17<br>0x1F<br>ances: an <i>I</i><br>ion results<br>-by-zero co<br>ructions in<br>for use un | ADD, ADDC<br>in an overfl<br>andition. The<br>all other cas<br>der software | C, or SUBB i<br>low (result is<br>e OV bit is c<br>ses.<br>e control. | s greater<br>cleared to ( |

## SFR Definition 8.4. PSW: Program Status Word

## SFR Definition 8.5. ACC: Accumulator

| R/W<br>ACC.7 | R/W<br>ACC.6                | R/W<br>ACC.5 | R/W<br>ACC.4 | R/W<br>ACC.3 | R/W<br>ACC.2 | R/W<br>ACC.1 | R/W<br>ACC.0   | Reset Value  |

|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|----------------|--------------|

| Bit7         | Bit6                        | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0           | SFR Address: |

| Bitt         | Eno                         | 2.10         | Bitt         | 2.10         | BILL         |              | t addressable) |              |

|              | ACC: Accum<br>This register |              | mulator for  | arithmetic o | operations.  |              |                |              |

## SFR Definition 8.11. IT01CF: INT0/INT1 Configuration

| R/W           | R/W                           | R/W            | R/W           | R/W            | R/W            | R/W            | R/W          | Reset Value         |

|---------------|-------------------------------|----------------|---------------|----------------|----------------|----------------|--------------|---------------------|

| IN1PL         | IN1SL2                        | IN1SL1         | IN1SL0        | IN0PL          | IN0SL2         | IN0SL1         | IN0SL0       | 0000001             |

| Bit7          | Bit6                          | Bit5           | Bit4          | Bit3           | Bit2           | Bit1           | Bit0         | SFR Address<br>0xE4 |

| Note: Re      | fer to SFR Defin              | nition 17.1 fo | or INT0/1 edg | ge- or level-s | ensitive inter | rupt selection | n.           |                     |

| <b>5:17</b> . |                               | Delevity       |               |                |                |                |              |                     |

| Bit7:         | IN1PL: /INT1<br>0: /INT1 inpu |                | 0)4/          |                |                |                |              |                     |

|               | 1: /INT1 inpu                 |                |               |                |                |                |              |                     |

| Bits6–4:      | IN1SL2-0: /II                 |                | •             | Bits           |                |                |              |                     |

|               | These bits se                 |                |               |                | /INT1. Note    | e that this p  | in assionm   | ent is inde-        |

|               | pendent of th                 |                |               |                |                |                |              |                     |

|               | peripheral that               | at has beer    | n assigned t  | he Port pir    | via the Cro    | ssbar. The     | Crossbar v   | vill not            |

|               | assign the Po                 |                |               |                |                | the selected   | d pin (accoi | mplished by         |

|               | setting to '1'                | the corresp    | onding bit i  | n register F   | POSKIP).       |                |              |                     |

|               | IN1SL2-0                      | /INT           | 1 Port Pin    |                |                |                |              |                     |

|               | 000                           |                | P0.0          |                |                |                |              |                     |

|               | 001                           |                | P0.1          |                |                |                |              |                     |

|               | 010                           |                | P0.2          |                |                |                |              |                     |

|               | 011                           |                | P0.3          |                |                |                |              |                     |

|               | 100                           |                | P0.4          |                |                |                |              |                     |

|               | 101                           |                | P0.5          |                |                |                |              |                     |

|               | 110                           |                | P0.6          |                |                |                |              |                     |

|               | 111                           |                | P0.7          |                |                |                |              |                     |

|               |                               |                |               |                |                |                |              |                     |

| Bit3:         | INOPL: /INTO                  |                |               |                |                |                |              |                     |

|               | 0: /INT0 inter                |                |               |                |                |                |              |                     |

| D:4-0.0.      | 1: /INT0 inter                |                |               | Dite           |                |                |              |                     |

| Bits2–0:      | INT0SL2-0: /<br>These bits se |                |               |                |                | a that this n  | in accianm   | ont is indo         |

|               | pendent of th                 |                |               |                |                |                |              |                     |

|               | peripheral that               |                |               |                |                |                |              |                     |

|               | assign the Po                 |                | •             |                |                |                |              |                     |

|               | setting to '1'                |                |               |                |                |                | • •          |                     |

|               |                               | (1) 1          |               |                |                |                |              |                     |

|               | IN0SL2-0                      | /IN I          | 0 Port Pin    |                |                |                |              |                     |

|               | 000                           |                | P0.0          |                |                |                |              |                     |

|               | 001                           |                | P0.1          |                |                |                |              |                     |

|               | 010                           | _              | P0.2          |                |                |                |              |                     |

|               | 011                           |                | P0.3          |                |                |                |              |                     |

|               | 100                           | _              | P0.4          |                |                |                |              |                     |

|               | 101                           |                | P0.5          |                |                |                |              |                     |

|               | 110                           | _              | P0.6          |                |                |                |              |                     |

|               | 111                           |                | P0.7          |                |                |                |              |                     |

### 8.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.