Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                  |

| Number of I/O              | 25                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25К х 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 17x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 28-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 28-QFN (5x5)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f313 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

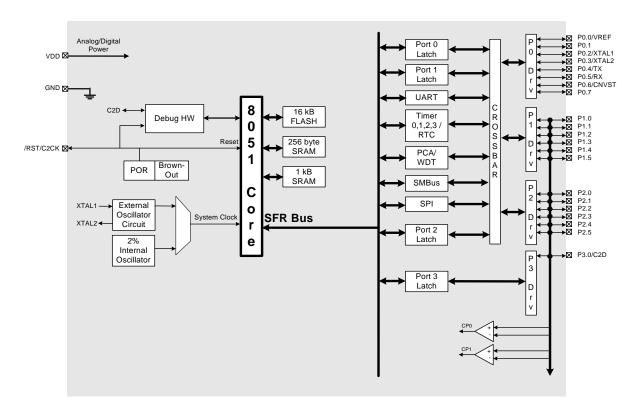

Figure 1.8. C8051F317 Block Diagram

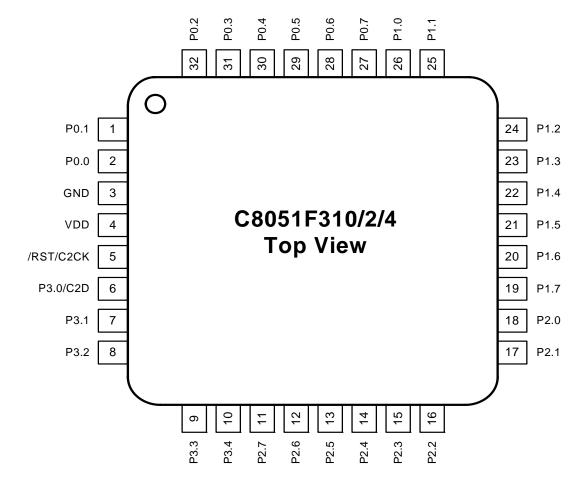

Figure 4.1. LQFP-32 Pinout Diagram (Top View)

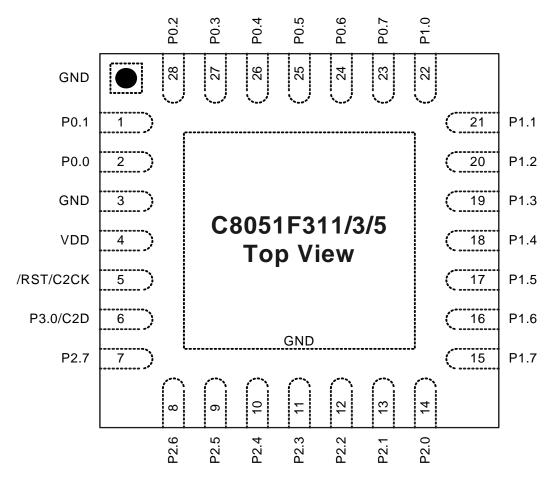

Figure 4.3. QFN-28 Pinout Diagram (Top View)

| SFR Definition 5.3. ADC0CF: ADC0 Configuration | า |

|------------------------------------------------|---|

|------------------------------------------------|---|

| R/W                                                                                                                                                                                                                                                                                                                | R/W<br>4 AD0SC3 | R/W<br>AD0SC2 | R/W<br>AD0SC1 | R/W<br>AD0SC0 | R/W<br>AD0LJST | R/W<br>- | R/W  | Reset Value          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|---------------|---------------|----------------|----------|------|----------------------|

| Bit7                                                                                                                                                                                                                                                                                                               | Bit6            | Bit5          | Bit4          | Bit3          | Bit2           | Bit1     | Bit0 | SFR Address:<br>0xBC |

| Bits7–3: AD0SC4–0: ADC0 SAR Conversion Clock Period Bits.<br>SAR Conversion clock is derived from system clock by the following equation, where<br>AD0SC refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock require-<br>ments are given in Table 5.1.<br>$AD0SC = \frac{SYSCLK}{CLK_{SAR}} - 1$ |                 |               |               |               |                |          |      |                      |

| Bit2:<br>Bits1–0:                                                                                                                                                                                                                                                                                                  |                 |               |               |               |                |          |      |                      |

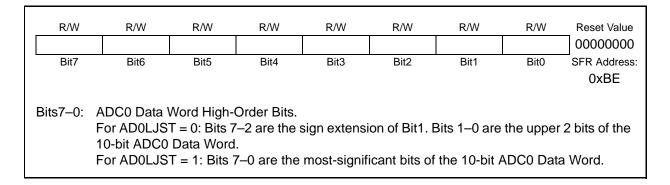

### SFR Definition 5.4. ADC0H: ADC0 Data Word MSB

## SFR Definition 5.5. ADC0L: ADC0 Data Word LSB

| R/W                                                                                                                                                                                                                             | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--------------|--|--|

| Bit7                                                                                                                                                                                                                            | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |  |

|                                                                                                                                                                                                                                 |      |      |      |      |      |      |      | 0xBD         |  |  |

| Bits7–0: ADC0 Data Word Low-Order Bits.<br>For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.<br>For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will always<br>read '0'. |      |      |      |      |      |      |      |              |  |  |

| Mnemonic                                                                | Description                                                                | Bytes | Clock<br>Cycles |  |  |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-----------------|--|--|

| XCH A, @Ri                                                              | Exchange indirect RAM with A<br>Exchange low nibble of indirect RAM with A | 1     | 2               |  |  |

| XCHD A, @Ri                                                             | 1                                                                          | 2     |                 |  |  |

|                                                                         | Boolean Manipulation                                                       |       |                 |  |  |

| CLR C                                                                   | Clear Carry                                                                |       |                 |  |  |

| CLR bit                                                                 | Clear direct bit                                                           | 2     | 2               |  |  |

| SETB C                                                                  | Set Carry                                                                  | 1     | 1               |  |  |

| SETB bit                                                                | Set direct bit                                                             | 2     | 2               |  |  |

| CPL C                                                                   | Complement Carry                                                           | 1     | 1               |  |  |

| CPL bit                                                                 | Complement direct bit                                                      | 2     | 2               |  |  |

| ANL C, bit                                                              | AND direct bit to Carry                                                    | 2     | 2               |  |  |

| ANL C, /bit                                                             | AND complement of direct bit to Carry                                      | 2     | 2               |  |  |

| ORL C, bit                                                              | OR direct bit to carry                                                     | 2     | 2               |  |  |

| ORL C, /bit                                                             | OR complement of direct bit to Carry                                       | 2     | 2               |  |  |

| MOV C, bit                                                              | Move direct bit to Carry                                                   | 2     | 2               |  |  |

| MOV bit, C                                                              | Move Carry to direct bit                                                   | 2     | 2               |  |  |

| JC rel                                                                  | Jump if Carry is set                                                       | 2     | 2/3             |  |  |

| JNC rel                                                                 | Jump if Carry is not set                                                   | 2     | 2/3             |  |  |

| JB bit, rel                                                             | Jump if direct bit is set                                                  | 3     | 3/4             |  |  |

| JNB bit, rel                                                            | Jump if direct bit is not set                                              | 3     | 3/4             |  |  |

| JBC bit, rel                                                            | Jump if direct bit is set and clear bit                                    | 3     | 3/4             |  |  |

|                                                                         | Program Branching                                                          | 1     | 1               |  |  |

| ACALL addr11                                                            | Absolute subroutine call                                                   | 2     | 3               |  |  |

| LCALL addr16                                                            | Long subroutine call                                                       | 3     | 4               |  |  |

| RET                                                                     | Return from subroutine                                                     | 1     | 5               |  |  |

| RETI                                                                    | Return from interrupt                                                      | 1     | 5               |  |  |

| AJMP addr11                                                             | Absolute jump                                                              | 2     | 3               |  |  |

| LJMP addr16                                                             | Long jump                                                                  | 3     | 4               |  |  |

| SJMP rel                                                                | Short jump (relative address)                                              | 2     | 3               |  |  |

| JMP @A+DPTR                                                             | Jump indirect relative to DPTR                                             | 1     | 3               |  |  |

| JZ rel                                                                  | Jump if A equals zero                                                      | 2     | 2/3             |  |  |

| JNZ rel                                                                 | Jump if A does not equal zero                                              | 2     | 2/3             |  |  |

| CJNE A, direct, rel                                                     | Compare direct byte to A and jump if not equal                             | 3     | 3/4             |  |  |

| CJNE A, #data, rel                                                      | Compare immediate to A and jump if not equal                               | 3     | 3/4             |  |  |

| CJNE Rn, #data, rel<br>CJNE Rn, #data, rel                              |                                                                            | 3     | 3/4             |  |  |

| CJNE @Ri, #data, rel Compare immediate to indirect and jump if no equal |                                                                            | 3     | 4/5             |  |  |

| DJNZ Rn, rel                                                            | Decrement Register and jump if not zero                                    | 2     | 2/3             |  |  |

| DJNZ direct, rel                                                        | Decrement direct byte and jump if not zero                                 | 3     | 3/4             |  |  |

| NOP                                                                     | No operation                                                               | 1     | 1               |  |  |

## Table 8.1. CIP-51 Instruction Set Summary (Continued)

## 9.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read '1', signifying the MCD as the reset source; otherwise, this bit reads '0'. Writing a '1' to the MCDRSF bit enables the Missing Clock Detector; writing a '0' disables it. The state of the RST pin is unaffected by this reset.

### 9.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the RST pin is unaffected by this reset.

### 9.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in **Section "18.3. Watchdog Timer Mode" on page 212**; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to '1'. The state of the RST pin is unaffected by this reset.

#### 9.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to '1' and a MOVX write operation targets an address above address 0x3DFF for C8051F310/1 or 0x1FFF for C8051F312/3/4/5.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0x3DFF for C8051F310/1 or 0x1FFF for C8051F312/3/4/5.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x3DFF for C8051F310/1 or 0x1FFF for C8051F312/3/4/5.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "10.3. Security Options" on page 113).

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overrightarrow{RST}$  pin is unaffected by this reset.

#### 9.8. Software Reset

Software may force a reset by writing a '1' to the SWRSF bit (RSTSRC.4). The SWRSF bit will read '1' following a software forced reset. The state of the RST pin is unaffected by this reset.

## 10. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the C2 interface or by software using the MOVX instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operation is not required. Code execution is stalled during a Flash write/erase operation. Refer to Table 10.1 for complete Flash memory electrical characteristics.

## 10.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see **Section "20. C2 Interface" on page 223**.

To ensure the integrity of Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  Monitor be enabled in any system that includes code that writes and/or erases Flash memory from software.

#### 10.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 10.2.

#### 10.1.2. Flash Erase Procedure

The Flash memory can be programmed from software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. **A byte location to be programmed should be erased before a new value is written.** The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- Step 1. Disable interrupts (recommended).

- Step 2. Set the PSEE bit (register PSCTL).

- Step 3. Set the PSWE bit (register PSCTL).

- Step 4. Write the first key code to FLKEY: 0xA5.

- Step 5. Write the second key code to FLKEY: 0xF1.

- Step 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 10.2 summarizes the Flash security features of the C8051F31x devices.

| Action                                                                     | C2 Debug                | User Firmware executing from: |                   |  |  |

|----------------------------------------------------------------------------|-------------------------|-------------------------------|-------------------|--|--|

|                                                                            | Interface               | an unlocked page              | a locked page     |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)        | Permitted               | Permitted                     | Permitted         |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)          | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)        | Permitted               | Permitted                     | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)         | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                     | Permitted               | Permitted                     | Permitted         |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                      | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                | Permitted               | Flash Error Reset             | Flash Error Reset |  |  |

| Erase page containing Lock Byte - Unlock all pages (if any page is locked) | C2 Device<br>Erase Only | Flash Error Reset             | Flash Error Reset |  |  |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)            | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)          | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Read, Write or Erase Reserved Area                                         | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

## Table 10.2. Flash Security Summary

C2 Device Erase - Erases all Flash pages including the page containing the Lock Byte.

Flash Error Reset - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

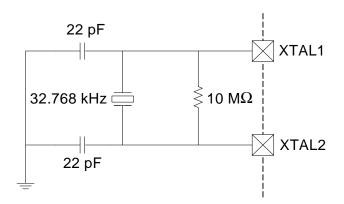

## 12.4. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 12.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 12.4. For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- Step 1. Force the XTAL1 and XTAL2 pins low by writing 0s to the port latch.

- Step 2. Configure XTAL1 and XTAL2 as analog inputs.

- Step 3. Enable the external oscillator.

- Step 4. Wait at least 1 ms.

- Step 5. Poll for XTLVLD => '1'.

- Step 6. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

**Note:** The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal data sheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 12.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 12.2.

Figure 12.2. 32.768 kHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

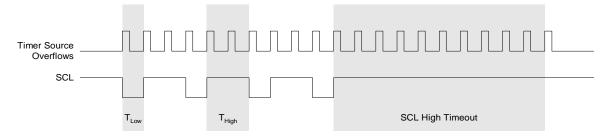

Figure 14.4 shows the typical SCL generation described by Equation 14.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 14.1.

Figure 14.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 14.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                     | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                             | T <sub>low</sub> – 4 system clocks |                       |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                           | OR                                 | 3 system clocks       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                             | 1 system clock + s/w delay*        |                       |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                           | 11 system clocks                   | 12 system clocks      |  |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. The s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                    |                       |  |  |  |  |  |

Table 14.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see **Section "14.3.3. SCL Low Timeout" on page 148**). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 14.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

#### 14.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 14.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER and TXMODE indicate the master/slave state and transmit/receive modes, respectively.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a '1' to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a '1' to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 14.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

Table 14.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 14.4 for SMBus status decoding using the SMB0CN register.

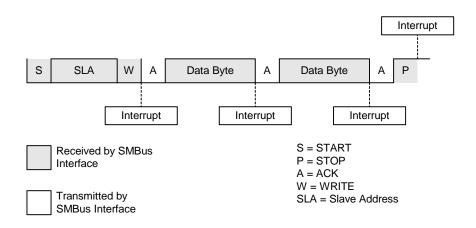

#### 14.5.3. Slave Receiver Mode

Serial data is received on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received. Software must write the ACK bit after each received byte to ACK or NACK the received byte. The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 14.7 shows a typical Slave Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 14.7. Typical Slave Receiver Sequence

### 14.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the table below, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. Note that the shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed but do not conform to the SMBus specification.

|                    | Valu                       | es F  | Read                                                                                 | ł                                                                                            |                                                                         |                                                                                             | Values<br>Written |     |     |

|--------------------|----------------------------|-------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------|-----|-----|

| Mode               | Status<br>Vector           | ACKRQ | ARBLOST                                                                              | Current SMbus State Typical Response Options                                                 |                                                                         |                                                                                             | STA               | STO | ACK |

|                    | 1110                       | 0     | 0                                                                                    | Х                                                                                            | A master START was generated.                                           | Load slave address + R/W into<br>SMB0DAT.                                                   | 0                 | 0   | х   |

|                    |                            |       | _                                                                                    | •                                                                                            | A master data or address byte                                           | Set STA to restart transfer.                                                                | 1                 | 0   | Х   |

| tter               |                            | 0     | 0                                                                                    | 0                                                                                            | was transmitted; NACK received.                                         | Abort transfer.                                                                             | 0                 | 1   | Х   |

| ansmi              |                            |       |                                                                                      |                                                                                              |                                                                         | Load next data byte into<br>SMB0DAT.                                                        | 0                 | 0   | Х   |

| . Tra              | 1100                       |       |                                                                                      |                                                                                              |                                                                         | End transfer with STOP.                                                                     | 0                 | 1   | Х   |

| Master Transmitter | A m<br>B 0 0 1 was<br>rece | 1     | A master data or address byte<br>was transmitted; ACK<br>received.                   | End transfer with STOP and start another transfer.                                           | 1                                                                       | 1                                                                                           | х                 |     |     |

| ~                  |                            |       |                                                                                      | Send repeated START.                                                                         | 1                                                                       | 0                                                                                           | Х                 |     |     |

|                    |                            |       | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). | 0                                                                                            | 0                                                                       | x                                                                                           |                   |     |     |

|                    |                            |       |                                                                                      |                                                                                              |                                                                         | Acknowledge received byte; Read SMB0DAT.                                                    | 0                 | 0   | 1   |

|                    |                            |       |                                                                                      |                                                                                              |                                                                         | Send NACK to indicate last byte, and send STOP.                                             | 0                 | 1   | 0   |

| iver               |                            |       |                                                                                      |                                                                                              | Send NACK to indicate last byte,<br>and send STOP followed by<br>START. | 1                                                                                           | 1                 | 0   |     |

| Rece               | 1000                       | 1     | 0                                                                                    | х                                                                                            | A master data byte was<br>received; ACK requested.                      | Send ACK followed by repeated START.                                                        | 1                 | 0   | 1   |

| Master Receiver    |                            |       |                                                                                      |                                                                                              | received, AON requested.                                                | Send NACK to indicate last byte,<br>and send repeated START.                                | 1                 | 0   | 0   |

| 2                  |                            |       |                                                                                      |                                                                                              |                                                                         | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0                 | 0   | 1   |

|                    |                            |       |                                                                                      | Send NACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0                                                                       | 0                                                                                           | 0                 |     |     |

|                   | Valu             | es F                        | Read    | ł   |                                                                   |                                                                  |     | /alue<br>Vritte |     |

|-------------------|------------------|-----------------------------|---------|-----|-------------------------------------------------------------------|------------------------------------------------------------------|-----|-----------------|-----|

| Mode              | Status<br>Vector | ACKRQ                       | ARBLOST | ACK | Current SMbus State                                               | Typical Response Options                                         | STA | STO             | ACK |

| er.               |                  | 0                           | 0       | 0   | A slave byte was transmitted;<br>NACK received.                   | No action required (expecting STOP condition).                   | 0   | 0               | х   |

| smitte            | 0100             | 0                           | 0       | 1   | A slave byte was transmitted;<br>ACK received.                    | Load SMB0DAT with next data byte to transmit.                    | 0   | 0               | х   |

| Slave Transmitter |                  | 0                           | 1       | Х   | A Slave byte was transmitted; error detected.                     | No action required (expecting<br>Master to end transfer).        | 0   | 0               | х   |

| Slav              | 0101             | 0                           | x       | x   | A STOP was detected while<br>an addressed Slave Transmit-<br>ter. | No action required (transfer com-<br>plete).                     | 0   | 0               | х   |

|                   |                  |                             |         |     | A slave address was                                               | Acknowledge received address.                                    | 0   | 0               | 1   |

|                   |                  | 1                           | 0       | Х   | received; ACK requested.                                          | Do not acknowledge received address.                             | 0   | 0               | 0   |

|                   | 0010             |                             |         |     |                                                                   | Acknowledge received address.                                    | 0   | 0               | 1   |

|                   | 0010             | 1                           | 1       | х   | slave address received; ACK                                       | Do not acknowledge received address.                             | 0   | 0               | 0   |

|                   |                  |                             |         |     | requested.                                                        | Reschedule failed transfer; do not acknowledge received address. | 1   | 0               | 0   |

| <u>ب</u>          | 0010             | 0                           | 1       | х   | Lost arbitration while attempt-                                   | Abort failed transfer.                                           | 0   | 0               | Х   |

| eive              | 0010             | 0                           | 1       | ^   | ing a repeated START.                                             | Reschedule failed transfer.                                      | 1   | 0               | Х   |

| Slave Receiver    |                  | 1                           | 1       | Х   | Lost arbitration while attempt-<br>ing a STOP.                    | No action required (transfer com-<br>plete/aborted).             | 0   | 0               | 0   |

| Slave             | 0001             | 0                           | 0       | х   | A STOP was detected while<br>an addressed slave receiver.         | No action required (transfer com-<br>plete).                     | 0   | 0               | х   |

|                   |                  | 0                           | 1       | х   | Lost arbitration due to a                                         | Abort transfer.                                                  | 0   | 0               | Х   |

|                   |                  | 0                           |         | ^   | detected STOP.                                                    | Reschedule failed transfer.                                      |     | 0               | Х   |

|                   |                  | 1                           | 0       | x   | A slave byte was received;                                        | Acknowledge received byte; Read SMB0DAT.                         | 0   | 0               | 1   |

|                   | 0000             | 1                           |         |     | ACK requested.                                                    | Do not acknowledge received byte.                                | 0   | 0               | 0   |

|                   |                  | 1                           | 1       | х   | Lost arbitration while transmit-                                  | Abort failed transfer.                                           | 0   | 0               | 0   |

|                   |                  | ting a data byte as master. |         |     | ting a data byte as master.                                       | Reschedule failed transfer.                                      | 1   | 0               | 0   |

## Table 14.4. SMBus Status Decoding (Continued)

| R/W   | R                                                                                   | R/W           | R/W            | R/W           | R/W            | R/W          | R/W           | Reset Value      |  |  |

|-------|-------------------------------------------------------------------------------------|---------------|----------------|---------------|----------------|--------------|---------------|------------------|--|--|

| SOMOD |                                                                                     | MCE0          | REN0           | TB80          | RB80           | TI0          | RI0           | 0100000          |  |  |

| Bit7  | Bit6                                                                                | Bit5          | Bit4           | Bit3          | Bit2           | Bit1         | Bit0          | Bit Addressable  |  |  |

|       |                                                                                     |               |                |               |                |              | SFR Addres    | s: 0x98          |  |  |

| Bit7: | SOMODE: S                                                                           | Serial Port ( | ) Operatior    | Mode.         |                |              |               |                  |  |  |

|       | S0MODE: Serial Port 0 Operation Mode.<br>This bit selects the UART0 Operation Mode. |               |                |               |                |              |               |                  |  |  |

|       | 0: 8-bit UAF                                                                        |               | •              |               |                |              |               |                  |  |  |

|       | 1: 9-bit UAF                                                                        | RT with Vari  | able Baud      | Rate.         |                |              |               |                  |  |  |

| Bit6: | UNUSED. F                                                                           | Read = 1b.    | Write = dor    | n't care.     |                |              |               |                  |  |  |

| Bit5: | MCE0: Mult                                                                          | iprocessor    | Communic       | ation Enab    | le.            |              |               |                  |  |  |

|       | The function                                                                        | n of this bit | is depende     | ent on the S  | erial Port 0   | Operation    | Mode.         |                  |  |  |

|       | S0MODE =                                                                            | 0: Checks     | for valid sto  | op bit.       |                |              |               |                  |  |  |

|       | 0: L                                                                                | ogic level o  | of stop bit is | s ignored.    |                |              |               |                  |  |  |

|       | 1: F                                                                                | RIO will only | be activate    | ed if stop bi | t is logic lev | /el 1.       |               |                  |  |  |

|       | S0MODE =                                                                            | 1: Multipro   | cessor Cor     | nmunicatio    | ns Enable.     |              |               |                  |  |  |

|       | 0: L                                                                                | ogic level o  | of ninth bit i | s ignored.    |                |              |               |                  |  |  |

|       | 1: F                                                                                | RIO is set ar | nd an interr   | upt is gene   | rated only v   | when the ni  | nth bit is lo | ogic 1.          |  |  |

| Bit4: | REN0: Rec                                                                           |               |                |               |                |              |               |                  |  |  |

|       | This bit ena                                                                        |               |                | T receiver.   |                |              |               |                  |  |  |

|       | 0: UART0 r                                                                          |               |                |               |                |              |               |                  |  |  |

|       | 1: UART0 r                                                                          |               |                |               |                |              |               |                  |  |  |

| Bit3: | TB80: Ninth                                                                         |               |                |               |                |              |               |                  |  |  |

|       | •                                                                                   |               |                | •             |                |              |               | JART Mode. It    |  |  |

|       | is not used                                                                         |               |                | Set or clea   | red by soft    | ware as req  | uired.        |                  |  |  |

| Bit2: | RB80: Ninth                                                                         |               |                |               |                |              |               |                  |  |  |

|       | RB80 is ass                                                                         |               | alue of the    | STOP bit      | in Mode 0; i   | t is assigne | d the valu    | e of the 9th     |  |  |

|       | data bit in M                                                                       |               |                |               |                |              |               |                  |  |  |

| Bit1: | TIO: Transm                                                                         |               | •              |               |                |              |               |                  |  |  |

|       |                                                                                     |               |                |               |                |              | ``            | he 8th bit in 8- |  |  |

|       |                                                                                     |               |                |               |                |              |               | en the UARTO     |  |  |

|       |                                                                                     |               | •              |               |                | ector to the | UAR I 0 in    | terrupt service  |  |  |

| D'/O  | routine. This                                                                       |               |                | nanually by   | / software.    |              |               |                  |  |  |

| Bit0: | RI0: Receiv                                                                         |               | •              |               |                |              |               |                  |  |  |

|       |                                                                                     |               |                |               |                |              |               | at the STOP bi   |  |  |

|       |                                                                                     | ,             |                | •             |                | •            |               | uses the CPU     |  |  |

|       |                                                                                     | UNE UARTU     | merrupts       | ervice rout   | ine. This dit  | must be Cl   | eared mai     | nually by soft-  |  |  |

|       | ware.                                                                               |               |                |               |                |              |               |                  |  |  |

## SFR Definition 15.1. SCON0: Serial Port 0 Control

## 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. Note that the setting of NSSMD bits affects the pinout of the device. When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 129 for general purpose port I/O and crossbar information.

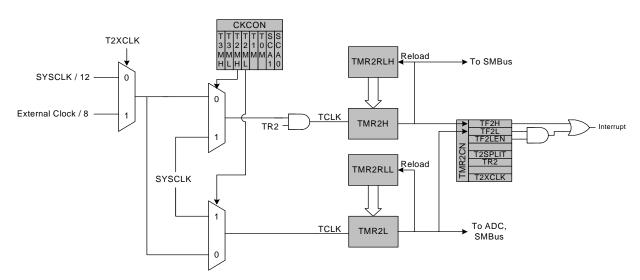

#### 17.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 17.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock      |

|------|--------|------------------|

|      |        | Source           |

| 0    | 0      | SYSCLK/12        |

| 0    | 1      | External Clock/8 |

| 1    | Х      | SYSCLK           |

| T2ML | T2XCLK | TMR2L Clock      |  |  |

|------|--------|------------------|--|--|

|      |        | Source           |  |  |

| 0    | 0      | SYSCLK/12        |  |  |

| 0    | 1      | External Clock/8 |  |  |

| 1    | Х      | SYSCLK           |  |  |

Note: External clock divided by 8 is synchronized with the system clock, and the external clock must be less than or equal to the system clock to operate in this mode.

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 17.5. Timer 2 8-Bit Mode Block Diagram

## SFR Definition 17.8. TMR2CN: Timer 2 Control

| R/W      | R/W                                                                                                                                                                                    | R/W                                                                               | R/W          | R/W           | R/W            | R/W          | R/W            | Reset Value  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------|---------------|----------------|--------------|----------------|--------------|--|--|

| TF2H     | TF2L                                                                                                                                                                                   | TF2LEN                                                                            | -            | T2SPLIT       | TR2            | -            | T2XCLK         | 00000000     |  |  |

| Bit7     | Bit6                                                                                                                                                                                   | Bit5                                                                              | Bit4         | Bit3          | Bit2           | Bit1         | Bit0           | SFR Address: |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                | (bi          | t addressable) | 0xC8         |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                |              |                |              |  |  |

| Bit7:    | TF2H: Timer                                                                                                                                                                            |                                                                                   |              |               |                |              |                |              |  |  |

|          | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode,                                                                                                |                                                                                   |              |               |                |              |                |              |  |  |

|          |                                                                                                                                                                                        | occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is |              |               |                |              |                |              |  |  |

|          | enabled, set                                                                                                                                                                           |                                                                                   |              |               |                |              |                |              |  |  |

| <b>.</b> | TF2H is not                                                                                                                                                                            |                                                                                   | •            | •             | and must I     | be cleared l | by software    |              |  |  |

| Bit6:    | TF2L: Timer                                                                                                                                                                            |                                                                                   |              | •             |                |              | 00 14/1        | 4.1.1.1.1.1. |  |  |

|          | Set by hardv                                                                                                                                                                           |                                                                                   |              |               |                |              |                |              |  |  |

|          | set, an interr                                                                                                                                                                         |                                                                                   |              |               |                |              |                |              |  |  |

|          | will set when<br>ically cleared                                                                                                                                                        | •                                                                                 |              | s regardless  | or the rim     | er z mode.   | This bit is n  | iot automat- |  |  |

| Bit5:    | TF2LEN: Tin                                                                                                                                                                            |                                                                                   |              | nt Enable     |                |              |                |              |  |  |

| Dito.    | This bit enab                                                                                                                                                                          |                                                                                   |              |               | errupts If T   | F2I FN is s  | et and Time    | ar 2 inter-  |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                |              |                |              |  |  |

|          | rupts are enabled, an interrupt will be generated when the low byte of Timer 2 overflows.<br>This bit should be cleared when operating Timer 2 in 16-bit mode.                         |                                                                                   |              |               |                |              |                |              |  |  |

|          | 0: Timer 2 Lo                                                                                                                                                                          |                                                                                   |              | •             |                |              |                |              |  |  |

|          | 1: Timer 2 Lo                                                                                                                                                                          |                                                                                   |              |               |                |              |                |              |  |  |

| Bit4:    | UNUSED. R                                                                                                                                                                              | ead = 0b. W                                                                       | /rite = don' | t care.       |                |              |                |              |  |  |

| Bit3:    | T2SPLIT: Tir                                                                                                                                                                           | ner 2 Split N                                                                     | lode Enab    | le.           |                |              |                |              |  |  |

|          | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.<br>0: Timer 2 operates in 16-bit auto-reload mode.                                                        |                                                                                   |              |               |                |              |                |              |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                |              |                |              |  |  |

|          | 1: Timer 2 operates as two 8-bit auto-reload timers.                                                                                                                                   |                                                                                   |              |               |                |              |                |              |  |  |

| Bit2:    | Bit2: TR2: Timer 2 Run Control.<br>This bit enables/disables Timer 2. In 8-bit mode, this bit enables/disables TMR2H                                                                   |                                                                                   |              |               |                |              |                |              |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               | e, this bit er | nables/disa  | bles TMR2      | H only;      |  |  |

|          | TMR2L is alv<br>0: Timer 2 di                                                                                                                                                          |                                                                                   | ed in this m | iode.         |                |              |                |              |  |  |

|          | 1: Timer 2 di                                                                                                                                                                          |                                                                                   |              |               |                |              |                |              |  |  |

| Bit1:    |                                                                                                                                                                                        |                                                                                   | /rito - don' | t care        |                |              |                |              |  |  |

| Bit0:    |                                                                                                                                                                                        |                                                                                   |              |               |                |              |                |              |  |  |

| Dito.    | This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit                                                                                          |                                                                                   |              |               |                |              |                |              |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                |              |                |              |  |  |

|          | selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock<br>Select bits (T2MH and T2ML in register CKCON) may still be used to select between the |                                                                                   |              |               |                |              |                |              |  |  |

|          | external clock and the system clock for either timer.                                                                                                                                  |                                                                                   |              |               |                |              |                |              |  |  |

|          | 0: Timer 2 ex                                                                                                                                                                          |                                                                                   |              |               |                | ided by 12.  |                |              |  |  |

|          | 1: Timer 2 ex                                                                                                                                                                          | xternal clock                                                                     | selection    | is the extern | al clock div   | vided by 8.  | Note that th   | e external   |  |  |

|          |                                                                                                                                                                                        |                                                                                   |              |               |                | ,            |                |              |  |  |

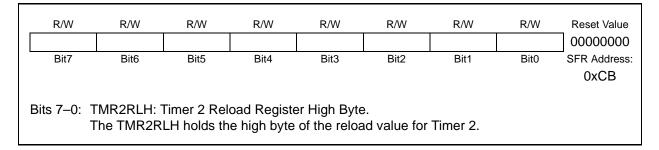

## SFR Definition 17.9. TMR2RLL: Timer 2 Reload Register Low Byte

| R/W                                                                                                                 | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value          |  |

|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|----------------------|--|

| Bit7                                                                                                                | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xCA |  |

| Bits 7–0: TMR2RLL: Timer 2 Reload Register Low Byte.<br>TMR2RLL holds the low byte of the reload value for Timer 2. |      |      |      |      |      |      |      |                      |  |

## SFR Definition 17.10. TMR2RLH: Timer 2 Reload Register High Byte

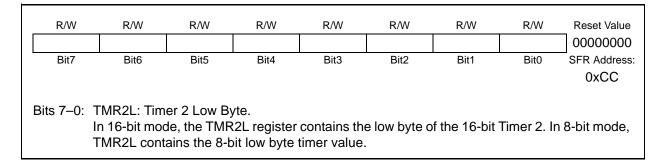

## SFR Definition 17.11. TMR2L: Timer 2 Low Byte

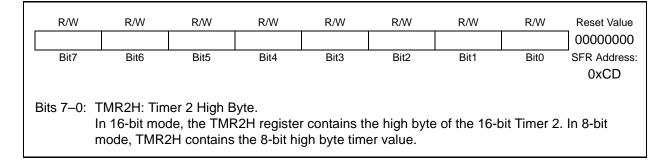

## SFR Definition 17.12. TMR2H Timer 2 High Byte

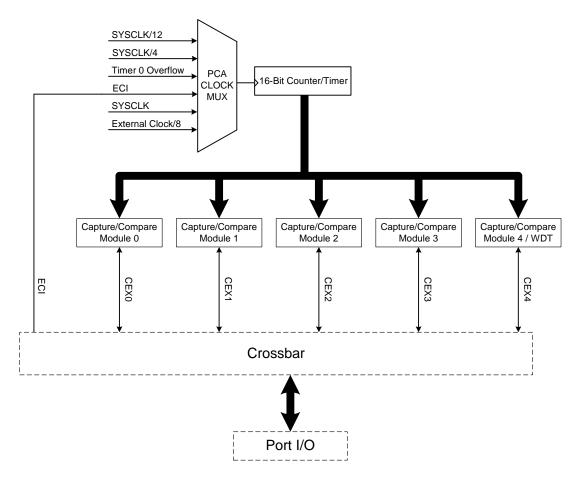

## 18. Programmable Counter Array