Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 29                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f314-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

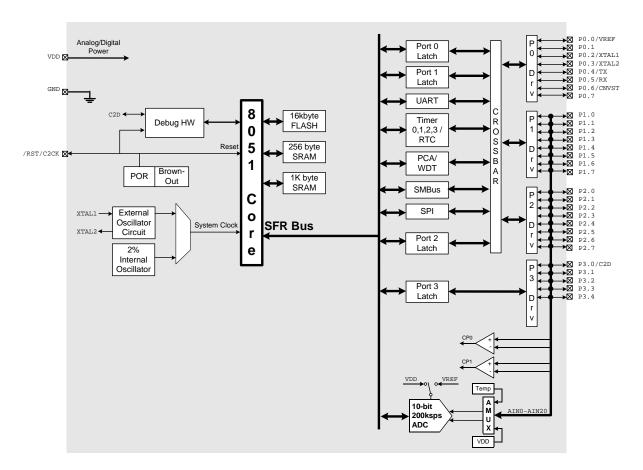

Figure 1.1. C8051F310 Block Diagram

### 3. Global DC Electrical Characteristics

#### Table 3.1. Global DC Electrical Characteristics

-40°C to +85°C, 25 MHz System Clock unless otherwise specified.

| Parameter                                      | Conditions                                     | Min            | Тур     | Max  | Units  |

|------------------------------------------------|------------------------------------------------|----------------|---------|------|--------|

| Digital Supply Voltage                         |                                                | $V_{RST}^{1}$  | 3.0     | 3.6  | V      |

| Digital Supply RAM Data Retention Voltage      |                                                | —              | 1.5     | _    | V      |

| Specified Operating Temperature<br>Range       |                                                | -40            | _       | +85  | °C     |

| SYSCLK (system clock frequency)                |                                                | 0 <sup>2</sup> | _       | 25   | MHz    |

| Tsysl (SYSCLK low time)                        |                                                | 18             |         |      | ns     |

| Tsysh (SYSCLK high time)                       |                                                | 18             | —       |      | ns     |

| Digital Supply Current—CPU Act                 | ive (Normal Mode, fetching instruc             | tions fro      | om Flas | h)   |        |

| I <sub>DD</sub> (Note 3)                       | V <sub>DD</sub> = 3.0 V, F = 25 MHz            | _              | 7.8     | 8.6  | mA     |

|                                                | V <sub>DD</sub> = 3.0 V, F = 1 MHz             | —              | 0.38    | _    | mA     |

|                                                | V <sub>DD</sub> = 3.0 V, F = 80 kHz            | —              | 31      |      | μA     |

|                                                | V <sub>DD</sub> = 3.6 V, F = 25 MHz            | —              | 10.7    | 12.1 | mA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3,    | F = 25 MHz                                     | _              | 67      | _    | %/V    |

| Note 4)                                        | F = 1 MHz                                      | _              | 62      | —    | %/V    |

| I <sub>DD</sub> Frequency Sensitivity (Note 3, | $V_{DD}$ = 3.0 V, F $\leq$ 15 MHz, T = 25 °C   | _              | 0.39    | _    | mA/MHz |

| Note 5)                                        | $V_{DD}$ = 3.0 V, F > 15 MHz, T = 25 °C        | —              | 0.21    |      | mA/MHz |

|                                                | $V_{DD}$ = 3.6 V, F $\leq$ 15 MHz, T = 25 °C   | —              | 0.55    |      | mA/MHz |

| ••                                             | V <sub>DD</sub> = 3.6 V, F > 15 MHz, T = 25 °C | _              | 0.27    |      | mA/MHz |

#### Notes:

- 1. Given in Table 9.1 on page 110.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data, not production tested.

- 4. Active and Inactive I<sub>DD</sub> at voltages and frequencies other than those specified can be calculated using the I<sub>DD</sub> Supply Sensitivity. For example, if the V<sub>DD</sub> is 3.3 V instead of 3.0 V at 25 MHz: I<sub>DD</sub> = 7.8 mA typical at 3.0 V and f = 25 MHz. From this, I<sub>DD</sub> = 7.8 mA + 0.67 x (3.3 V 3.0 V) = 8 mA at 3.3 V and f = 25 MHz.

- 5. I<sub>DD</sub> can be estimated for frequencies ≤ 15 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for > 15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 20 MHz,  $I_{DD}$  = 7.8 mA – (25 MHz – 20 MHz) x 0.21 mA/MHz = 6.75 mA.

Idle I<sub>DD</sub> can be estimated for frequencies ≤ 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 4.8 mA – (25 MHz – 5 MHz) x 0.15 mA/MHz = 1.8 mA.

# C8051F310/1/2/3/4/5/6/7

Other electrical characteristics tables are found in the data sheet section corresponding to the associated peripherals. For more information on electrical characteristics for a specific peripheral, refer to the page indicated in Table 3.2.

| Peripheral Electrical Characteristics                         | Page No. |

|---------------------------------------------------------------|----------|

| ADC0 Electrical Characteristics                               | 65       |

| External Voltage Reference Circuit Electrical Characteristics | 68       |

| Comparator Electrical Characteristics                         | 78       |

| Reset Electrical Characteristics                              | 110      |

| Flash Electrical Characteristics                              | 112      |

| Internal Oscillator Electrical Characteristics                | 123      |

| Port I/O DC Electrical Characteristics                        | 143      |

#### Table 3.2. Electrical Characteristics Quick Reference

## 5. 10-Bit ADC (ADC0, C8051F310/1/2/3/6 only)

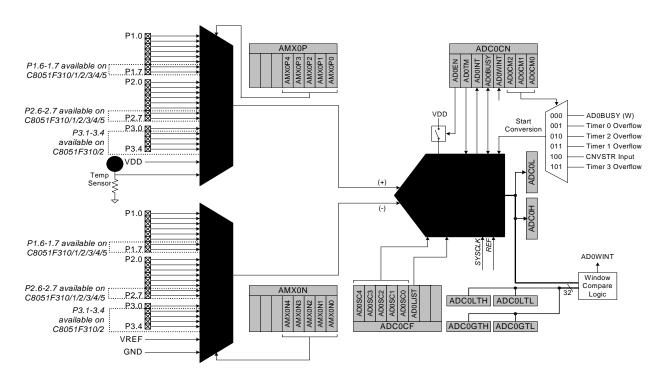

The ADC0 subsystem for the C8051F310/1/2/3/6 consists of two analog multiplexers (referred to collectively as AMUX0) with 25 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure P1.0–P3.4, the Temperature Sensor output, or  $V_{DD}$  with respect to P1.0–P3.4, VREF, or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

#### 5.1. Analog Multiplexer

AMUX0 selects the positive and negative inputs to the ADC. Any of the following may be selected as the positive input: P1.0-P3.4, the on-chip temperature sensor, or the positive power supply ( $V_{DD}$ ). Any of the following may be selected as the negative input: P1.0-P3.4, VREF, or GND. When GND is selected as the negative input, ADC0 operates in Single-ended Mode; all other times, ADC0 operates in Differential Mode. The ADC0 input channels are selected in the AMX0P and AMX0N registers as described in SFR Definition 5.1 and SFR Definition 5.2.

The conversion code format differs between Single-ended and Differential modes. The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.0). When in Single-ended Mode, conversion codes are represented as 10-bit unsigned integers.

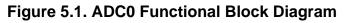

### 6. Voltage Reference (C8051F310/1/2/3/6 only)

The voltage reference MUX on C8051F310/1/2/3/6 devices is configurable to use an externally connected voltage reference, or the power supply voltage (see Figure 6.1). The REFSL bit in the Reference Control register (REF0CN) selects the reference source. For an external source, REFSL should be set to '0'; For  $V_{DD}$  as the reference source, REFSL should be set to '1'.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and Internal Oscillator. This bit is forced to logic 1 when any of the aforementioned peripherals is enabled. The bias generator may be enabled manually by writing a '1' to the BIASE bit in register REF0CN; see SFR Definition 6.1 for REF0CN register details. The electrical specifications for the voltage reference circuit are given in Table 6.1.

**Important Note About the VREF Input:** Port pin P0.0 is used as the external VREF input. When using an external voltage reference, P0.0 should be configured as analog input and skipped by the Digital Crossbar. To configure P0.0 as analog input, set to '0' Bit0 in register P0MDIN. To configure the Crossbar to skip P0.0, set to '1' Bit0 in register P0SKIP. Refer to **Section "13. Port Input/Output" on page 129** for complete Port I/O configuration details.

The temperature sensor connects to the highest order input of the ADC0 positive input multiplexer (see **Section "5.1. Analog Multiplexer" on page 51** for details). The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

Figure 6.1. Voltage Reference Functional Block Diagram

# C8051F310/1/2/3/4/5/6/7

The Comparator output can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and its supply current falls to less than 100 nA. See **Section "13.1. Priority Crossbar Decoder" on page 131** for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 7.1.

The Comparator response time may be configured in software via the CPTnMD registers (see SFR Definition 7.3 and SFR Definition 7.6). Selecting a longer response time reduces the Comparator supply current. See Table 7.1 for complete timing and current consumption specifications.

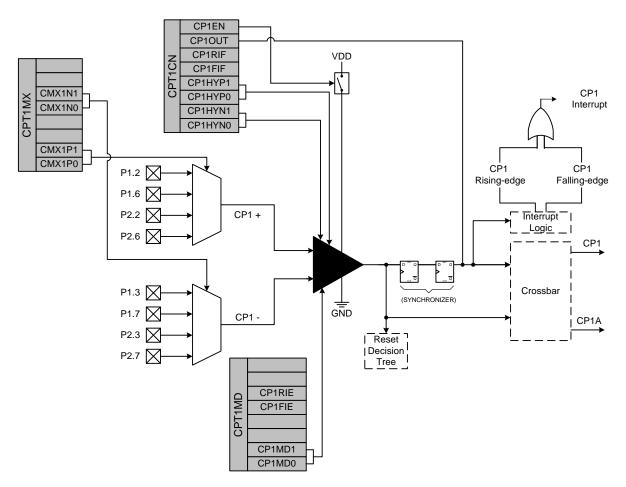

Figure 7.2. Comparator1 Functional Block Diagram

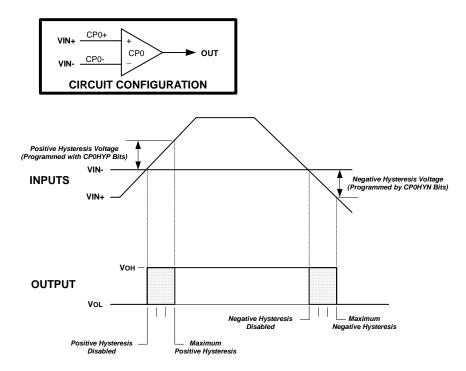

Figure 7.3. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPTnCN (for n = 0 or 1). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3-0 in the Comparator Control Register CPTnCN (shown in SFR Definition 7.1 and SFR Definition 7.4). The amount of negative hysteresis voltage is determined by the settings of the CPnHYN bits. As shown in Table 7.1, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CPnHYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "8.3. Interrupt Handler" on page 93**). The CPnFIF flag is set to logic 1 upon a Comparator falling-edge interrupt, and the CPnRIF flag is set to logic 1 upon the Comparator rising-edge interrupt. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.

The output state of the Comparator can be obtained at any time by reading the CPnOUT bit. The Comparator is enabled by setting the CPnEN bit to logic 1, and is disabled by clearing this bit to logic 0.

Note that false rising edges and falling edges can be detected when the comparator is first powered-on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 7.1 on page 78.

| Register       | Address          | Description                                        | Page |

|----------------|------------------|----------------------------------------------------|------|

| SFRs are liste | ed in alphabetic | al order. All undefined SFR locations are reserved |      |

| ACC            | 0xE0             | Accumulator                                        | 92   |

| ADC0CF         | 0xBC             | ADC0 Configuration                                 | 59   |

| ADC0CN         | 0xE8             | ADC0 Control                                       | 60   |

| ADC0GTH        | 0xC4             | ADC0 Greater-Than Compare High                     | 61   |

| ADC0GTL        | 0xC3             | ADC0 Greater-Than Compare Low                      | 61   |

| ADC0H          | 0xBE             | ADC0 High                                          | 59   |

| ADC0L          | 0xBD             | ADC0 Low                                           | 59   |

| ADC0LTH        | 0xC6             | ADC0 Less-Than Compare Word High                   | 62   |

| ADC0LTL        | 0xC5             | ADC0 Less-Than Compare Word Low                    | 62   |

| AMX0N          | 0xBA             | AMUX0 Negative Channel Select                      | 58   |

| AMX0P          | 0xBB             | AMUX0 Positive Channel Select                      | 57   |

| В              | 0xF0             | B Register                                         | 93   |

| CKCON          | 0x8E             | Clock Control                                      | 193  |

| CLKSEL         | 0xA9             | Clock Select                                       | 123  |

| CPT0CN         | 0x9B             | Comparator0 Control                                | 72   |

| CPT0MD         | 0x9D             | Comparator0 Mode Selection                         | 74   |

| CPT0MX         | 0x9F             | Comparator0 MUX Selection                          | 73   |

| CPT1CN         | 0x9A             | Comparator1 Control                                | 75   |

| CPT1MD         | 0x9C             | Comparator1 Mode Selection                         | 77   |

| CPT1MX         | 0x9E             | Comparator1 MUX Selection                          | 76   |

| DPH            | 0x83             | Data Pointer High                                  | 91   |

| DPL            | 0x82             | Data Pointer Low                                   | 90   |

| EIE1           | 0xE6             | Extended Interrupt Enable 1                        | 99   |

| EIP1           | 0xF6             | Extended Interrupt Priority 1                      | 100  |

| EMI0CN         | 0xAA             | External Memory Interface Control                  | 119  |

| FLKEY          | 0xB7             | Flash Lock and Key                                 | 117  |

| FLSCL          | 0xB6             | Flash Scale                                        | 117  |

| IE             | 0xA8             | Interrupt Enable                                   | 97   |

| IP             | 0xB8             | Interrupt Priority                                 | 98   |

| IT01CF         | 0xE4             | INT0/INT1 Configuration                            | 101  |

| OSCICL         | 0xB3             | Internal Oscillator Calibration                    | 122  |

| OSCICN         | 0xB2             | Internal Oscillator Control                        | 122  |

| OSCXCN         | 0xB1             | External Oscillator Control                        | 125  |

| P0             | 0x80             | Port 0 Latch                                       | 136  |

| POMDIN         | 0xF1             | Port 0 Input Mode Configuration                    | 136  |

| POMDOUT        | 0xA4             | Port 0 Output Mode Configuration                   | 137  |

| POSKIP         | 0xD4             | Port 0 Skip                                        | 137  |

| P1             | 0x90             | Port 1 Latch                                       | 138  |

| P1MDIN         | 0xF2             | Port 1 Input Mode Configuration                    | 138  |

| P1MDOUT        | 0xA5             | Port 1 Output Mode Configuration                   | 139  |

| P1SKIP         | 0xD5             | Port 1 Skip                                        | 139  |

| P2             | 0xA0             | Port 2 Latch                                       | 140  |

| P2MDIN         | 0xF3             | Port 2 Input Mode Configuration                    | 140  |

| P2MDOUT        | 0xA6             | Port 2 Output Mode Configuration                   | 141  |

#### Table 8.3. Special Function Registers

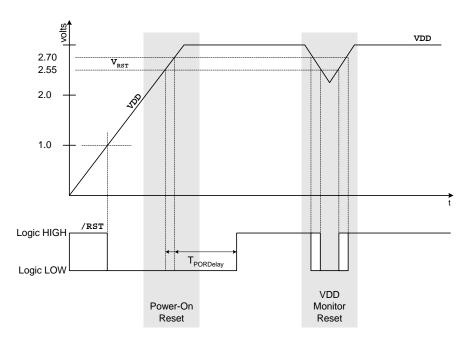

#### 9.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. An additional delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 9.2. plots the power-on and V<sub>DD</sub> monitor reset timing. For valid ramp times (less than 1 ms), the power-on reset delay (T<sub>PORDelav</sub>) is typically less than 0.3 ms.

Note: The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is disabled following a power-on reset.

Figure 9.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

#### 9.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 9.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads '1', the data may no longer be valid. The  $V_{DD}$  monitor is disabled after power-on resets; however its defined state (enabled/disabled) is not altered by

- 10. Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 11. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 10.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in AN201, "Writing to Flash from Firm-ware", available from the Silicon Laboratories web site.

| R/W                        | R/W                                                                                                                                                                                                                             | R/W                                                                                                                                                                       | R/W                                                                                                                                                | R/W                                                                                                                                            | R/W                                                                                      | R/W                                                                    | R/W                                                                | Reset Value                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|

| -                          | -                                                                                                                                                                                                                               | -                                                                                                                                                                         | -                                                                                                                                                  | -                                                                                                                                              | -                                                                                        | PSEE                                                                   | PSWE                                                               | 0000000                                                   |

| Bit7                       | Bit6                                                                                                                                                                                                                            | Bit5                                                                                                                                                                      | Bit4                                                                                                                                               | Bit3                                                                                                                                           | Bit2                                                                                     | Bit1                                                                   | Bit0                                                               | SFR Address:                                              |

|                            |                                                                                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                |                                                                                          |                                                                        |                                                                    | 0x8F                                                      |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED: Re<br>PSEE: Progr<br>Setting this b<br>to be erased<br>Flash memori<br>tion addresse<br>0: Flash prog<br>1: Flash prog<br>PSWE: Prog<br>Setting this b<br>write instruct<br>0: Writes to F<br>1: Writes to F<br>memory. | am Store E<br>bit (in combi<br>. If this bit is<br>ry using the<br>ed by the N<br>gram memo<br>gram memo<br>ram Store N<br>bit allows we<br>ion. The Fla<br>Flash program | rase Enabl<br>nation with<br>s logic 1 an<br>MOVX inst<br>IOVX instru-<br>ory erasure<br>Write Enabl<br>riting a byte<br>ash location<br>am memory | e<br>PSWE) allo<br>d Flash writ<br>struction will<br>action. The v<br>disabled.<br>enabled.<br>e<br>of data to t<br>n should be<br>y disabled. | ows an entir<br>es are enat<br>erase the e<br>value of the<br>he Flash pr<br>erased befo | oled (PSWE<br>entire page<br>data byte w<br>ogram men<br>ore writing o | is logic 1)<br>that contain<br>written does<br>nory using<br>data. | , a write to<br>ns the loca-<br>s not matter.<br>the MOVX |

#### SFR Definition 10.1. PSCTL: Program Store R/W Control

116

#### 14.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 14.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 14.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

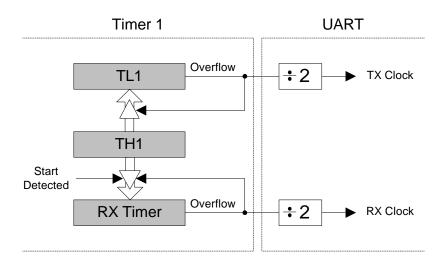

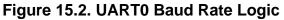

#### 15.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 15.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see **Section "17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 189**). The Timer 1 reload value should be set so that over-flows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 15.1.

#### Equation 15.1. UART0 Baud Rate

$$UartBaudRate = \frac{T1_{CLK}}{(256 - T1H)} \times \frac{1}{2}$$

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in **Section "17. Timers" on page 187**. A quick reference for typical baud rates and system clock frequencies is given in Table 15.1 through Table 15.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

|                |                              | Frequency: 24.5 MHz  |                                  |                       |                                     |      |                                  |  |  |  |  |  |

|----------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|--|--|

|                | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |  |  |  |  |  |

|                | 230400                       | -0.32%               | 106                              | SYSCLK                | XX                                  | 1    | 0xCB                             |  |  |  |  |  |

|                | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                  | 1    | 0x96                             |  |  |  |  |  |

|                | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                  | 1    | 0x2B                             |  |  |  |  |  |

| from<br>Ssc.   | 28800                        | -0.32%               | 848                              | SYSCLK / 4            | 01                                  | 0    | 0x96                             |  |  |  |  |  |

| < froi<br>Osc. | 14400                        | 0.15%                | 1704                             | SYSCLK / 12           | 00                                  | 0    | 0xB9                             |  |  |  |  |  |

|                | 9600                         | -0.32%               | 2544                             | SYSCLK / 12           | 00                                  | 0    | 0x96                             |  |  |  |  |  |

| SYSCL          | 2400                         | -0.32%               | 10176                            | SYSCLK / 48           | 10                                  | 0    | 0x96                             |  |  |  |  |  |

| SY<br>Int      | 1200                         | 0.15%                | 20448                            | SYSCLK / 48           | 10                                  | 0    | 0x2B                             |  |  |  |  |  |

# Table 15.1. Timer Settings for Standard Baud RatesUsing the Internal Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in **Section 17.1**.

# Table 15.2. Timer Settings for Standard Baud RatesUsing an External 25 MHz Oscillator

|                      |                              |                      | Fre                              | quency: 25.0 M        | lHz                                 |      |                                  |

|----------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                      | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |

|                      | 230400                       | -0.47%               | 108                              | SYSCLK                | XX                                  | 1    | 0xCA                             |

|                      | 115200                       | 0.45%                | 218                              | SYSCLK                | XX                                  | 1    | 0x93                             |

|                      | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |

| from<br>Osc.         | 28800                        | 0.45%                | 872                              | SYSCLK / 4            | 01                                  | 0    | 0x93                             |

|                      | 14400                        | -0.01%               | 1736                             | SYSCLK / 4            | 01                                  | 0    | 0x27                             |

| XLK<br>Jal           | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |

| SYSCLK<br>External   | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                  | 0    | 0x93                             |

| S ≺                  | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                  | 0    | 0x27                             |

| ε.                   | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                  | 0    | 0xE5                             |

| < from<br>Osc.       | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                  | 0    | 0xCA                             |

|                      | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                  | 0    | 0x93                             |

| SYSCLK<br>Internal C | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

#### SFR Definition 16.2. SPI0CN: SPI0 Control

| R/W<br>SPIF | R/W<br>WCOL                                                                                                          | R/W<br>MODF                                                                                        | R/W<br>RXOVRN                                                                         | R/W<br>NSSMD1                                                               | R/W                                            | R<br>TXBMT                | R/W<br>SPIEN                | Reset Value<br>00000110 |

|-------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------|---------------------------|-----------------------------|-------------------------|

| Bit7        | Bit6                                                                                                                 | Bit5                                                                                               | Bit4                                                                                  | Bit3                                                                        | Bit2                                           | Bit1                      | Bit0                        | Bit                     |

|             |                                                                                                                      |                                                                                                    |                                                                                       |                                                                             |                                                |                           | SFR Addres                  | Addressable<br>s: 0xF8  |

| Bit 7:      | SPIF: SPI0 I<br>This bit is se<br>setting this b<br>automatically                                                    | t to logic 1<br>it causes th                                                                       | by hardwar<br>ne CPU to v                                                             | ector to the                                                                | SPI0 interru                                   | upt service               |                             |                         |

| Bit 6:      | WCOL: Write<br>This bit is se<br>the SPI0 dat<br>cleared by se                                                       | e Collision İ<br>t to logic 1<br>a register v                                                      | -lag.<br>by hardwar                                                                   | e (and gene                                                                 | erates a SPI                                   | 0 interrupt)              |                             |                         |

| Bit 5:      | MODF: Mod<br>This bit is se<br>collision is de<br>matically clear                                                    | t to logic 1<br>etected (NS<br>ared by har                                                         | by hardwar<br>SS is low, M<br>dware. It m                                             | STEN = 1,<br>just be clea                                                   | and NSSMD<br>red by softwa                     | D[1:0] = 01)              |                             |                         |

| Bit 4:      | RXOVRN: R<br>This bit is se<br>fer still holds<br>shifted into the<br>be cleared b                                   | t to logic 1<br>unread da<br>ne SPI0 shi                                                           | by hardwar<br>ta from a pr                                                            | e (and gene<br>evious tran                                                  | erates a SPI<br>sfer and the                   | last bit of t             | he current                  | transfer is             |

| Bits 3–2:   | NSSMD1–N<br>Selects betw<br>(See Section<br>Slave Mode<br>00: 3-Wire S<br>01: 4-Wire S<br>1x: 4-Wire S<br>assume the | SSMD0: SI<br>reen the fol<br>n "16.2. SP<br>Operation<br>lave or 3-w<br>lave or Mul<br>ingle-Maste | lowing NSS<br>PIO Master I<br>" on page<br>ire Master I<br>ti-Master M<br>er Mode. NS | operation (<br><b>Mode Oper</b><br><b>177</b> ).<br>Mode. NSS<br>ode (Defau | ation" on pa<br>signal is not<br>lt). NSS is a | t routed to a lways an ir | a port pin.<br>put to the o | device.                 |

| Bit 1:      | TXBMT: Tran<br>This bit will b<br>data in the tr<br>indicating that                                                  | nsmit Buffe<br>be set to log<br>ansmit buff                                                        | r Empty.<br>jic 0 when r<br>er is transfe                                             | erred to the                                                                | SPI shift reg                                  | jister, this b            |                             |                         |

| Bit 0:      | SPIEN: SPIC<br>This bit enab<br>0: SPI disabl<br>1: SPI enabl                                                        | les/disable<br>ed.                                                                                 | s the SPI.                                                                            |                                                                             |                                                |                           |                             |                         |

## C8051F310/1/2/3/4/5/6/7

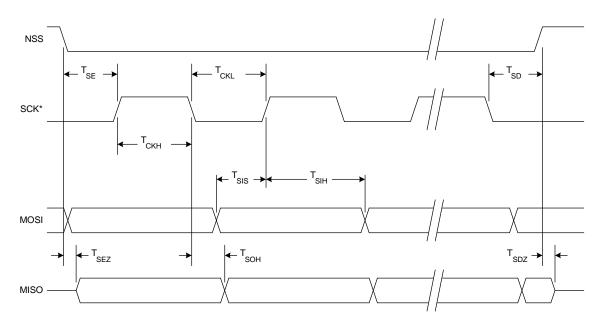

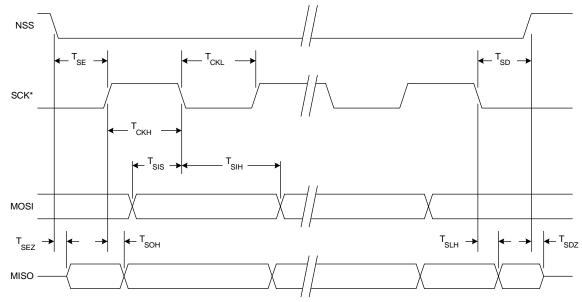

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

#### Figure 16.10. SPI Slave Timing (CKPHA = 0)

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

#### Figure 16.11. SPI Slave Timing (CKPHA = 1)

#### 17. Timers

Each MCU includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload.

| Timer 0 and Timer 1 Modes: | Timer 2 Modes:                    | Timer 3 Modes:                    |  |

|----------------------------|-----------------------------------|-----------------------------------|--|

| 13-bit counter/timer       | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |  |

| 16-bit counter/timer       |                                   |                                   |  |

| 8-bit counter/timer        |                                   |                                   |  |

| with auto-reload           | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |  |

| Two 8-bit counter/timers   |                                   |                                   |  |

| (Timer 0 only)             |                                   |                                   |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M-T0M) and the Clock Scale bits (SCA1-SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 17.3 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock's frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

#### 17.1. Timer 0 and Timer 1

Each timer is implemented as 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (SFR Definition 8.7. "IE: Interrupt Enable" on page 97); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register. Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1-T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 17.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

| SFR Definition | 17.1. | TCON: | Timer | Control |

|----------------|-------|-------|-------|---------|

|----------------|-------|-------|-------|---------|

| R/W   | R/W                          | R/W          | R/W          | R/W          | R/W            | R/W          | R/W           | Reset Valu   |

|-------|------------------------------|--------------|--------------|--------------|----------------|--------------|---------------|--------------|

| TF1   | TR1                          | TF0          | TR0          | IE1          | IT1            | IE0          | IT0           | 0000000      |

| Bit7  | Bit6                         | Bit5         | Bit4         | Bit3         | Bit2           | Bit1         | Bit0          | SFR Addre    |

|       |                              |              |              |              |                | (bi          | t addressable | e) 0x88      |

|       |                              |              |              |              |                |              |               |              |

| Sit7: | TF1: Timer 1                 |              | -            |              | flan ann ba    |              |               | h            |

|       | Set by hardw                 |              |              |              |                |              |               |              |

|       | matically clea               |              |              | ctors to the | i imer i int   | errupt servi | ce routine    | •            |

|       | 0: No Timer<br>1: Timer 1 ha |              |              |              |                |              |               |              |

| Bit6: | TR1: Timer 1                 |              |              |              |                |              |               |              |

| nio.  | 0: Timer 1 di                |              | 101.         |              |                |              |               |              |

|       | 1: Timer 1 er                |              |              |              |                |              |               |              |

| Bit5: | TF0: Timer 0                 |              | Flag         |              |                |              |               |              |

|       | Set by hardw                 |              | -            | rflows. This | s flag can be  | e cleared by | / software    | but is auto  |

|       | matically clea               |              |              |              |                |              |               |              |

|       | 0: No Timer (                |              |              |              |                |              |               |              |

|       | 1: Timer 0 ha                | as overflow  | ed.          |              |                |              |               |              |

| Bit4: | TR0: Timer C                 | Run Conti    | rol.         |              |                |              |               |              |

|       | 0: Timer 0 di                | sabled.      |              |              |                |              |               |              |

|       | 1: Timer 0 er                | nabled.      |              |              |                |              |               |              |

| Bit3: | IE1: External                | •            |              |              |                |              |               |              |

|       | This flag is s               |              |              |              |                |              |               |              |

|       | cleared by so                |              |              |              |                |              |               |              |

|       | rupt 1 service               |              |              |              | -              |              | nen /INT1     | is active as |

|       | defined by bi                |              | -            | 1CF (see S   | FR Definitio   | on 8.11).    |               |              |

| Bit2: | IT1: Interrupt               |              |              |              |                |              |               |              |

|       | This bit select              |              |              |              |                |              |               |              |

|       | is configured 8.11).         | active low   | or high by t |              |                | ICF registe  | el (See SF    |              |

|       | 0: /INT1 is le               | vel triggere | hd           |              |                |              |               |              |

|       | 1: /INT1 is ed               |              |              |              |                |              |               |              |

| Bit1: | IE0: External                | 0 00         |              |              |                |              |               |              |

|       | This flag is se              | •            |              | n edae/leve  | el of type de  | fined by IT( | ) is detecte  | ed. It can b |

|       | cleared by so                |              |              |              |                |              |               |              |

|       | rupt 0 service               |              |              |              |                |              |               |              |

|       | defined by bi                |              |              |              |                |              |               |              |

| BitO: | IT0: Interrupt               | t 0 Type Se  | lect.        |              |                |              |               |              |

|       | This bit selec               |              |              |              |                |              |               |              |

|       | is configured                | active low   | or high by t | he IN0PL b   | oit in registe | r IT01CF (s  | ee SFR D      | efinition    |

|       | 8.11).                       |              |              |              |                |              |               |              |

|       | 0: /INT0 is le               |              |              |              |                |              |               |              |

|       | 1: /INT0 is ed               |              |              |              |                |              |               |              |

|       |                              | age triggere | ed.          |              |                |              |               |              |

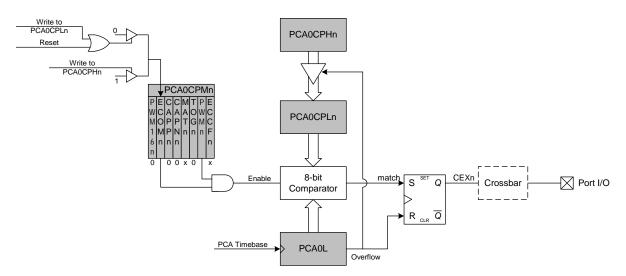

#### 18.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 18.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. The duty cycle for 8-Bit PWM Mode is given by Equation 18.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

#### Equation 18.2. 8-Bit PWM Duty Cycle

$DutyCycle = \frac{(256 - PCA0CPHn)}{256}$

Using Equation 18.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 18.8. PCA 8-Bit PWM Mode Diagram

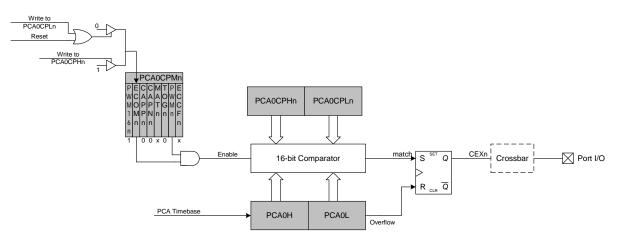

#### 18.2.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. The duty cycle for 16-Bit PWM Mode is given by Equation 18.3.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

#### Equation 18.3. 16-Bit PWM Duty Cycle

$DutyCycle = \frac{(65536 - PCA0CPn)}{65536}$

Using Equation 18.3, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 18.9. PCA 16-Bit PWM Mode

#### 18.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

| R/W   | R/W                                              | R/W              | R/W           | R/W           | R/W          | R/W          | R/W           | Reset Value  |

|-------|--------------------------------------------------|------------------|---------------|---------------|--------------|--------------|---------------|--------------|

| CF    | CR                                               |                  | CCF4          | CCF3          | CCF2         | CCF1         | CCF0          | 00000000     |

| Bit7  | Bit6                                             | Bit5             | Bit4          | Bit3          | Bit2         | Bit1         | Bit0          | SFR Address  |

|       |                                                  |                  |               |               |              | (bi          | t addressable | ) 0xD8       |

|       |                                                  | ·                |               |               |              |              |               |              |

| Bit7: | CF: PCA Co                                       |                  |               | 0             |              | 0 FFF        | -             |              |

|       | Set by hardw                                     |                  |               |               |              |              |               |              |

|       | Counter/Tim                                      |                  | · · ·         | •             |              |              |               |              |

|       | to the PCA in<br>must be clear                   | •                |               | . This dillis | not automa   | lucally clea | red by hard   | iware and    |

| Bit6: | CR: PCA Co                                       |                  |               | ol            |              |              |               |              |

| Dito. | This bit enab                                    |                  |               |               | her          |              |               |              |

|       | 0: PCA Cour                                      |                  |               |               |              |              |               |              |

|       | 1: PCA Cour                                      | nter/Timer       | enabled.      |               |              |              |               |              |

| Bit5: | UNUSED. R                                        | ead = 0b, \      | Write = don't | care.         |              |              |               |              |

| Bit4: | CCF4: PCA                                        |                  |               |               |              |              |               |              |

|       | This bit is se                                   |                  |               |               |              |              |               |              |

|       | enabled, set                                     | •                |               |               |              |              |               | outine. This |

| D'/O  | bit is not aut                                   |                  | •             |               | d must be o  | cleared by s | software.     |              |

| Bit3: | CCF3: PCA                                        |                  | •             |               |              |              |               |              |

|       | This bit is se<br>enabled, set                   |                  |               |               | •            |              |               |              |

|       | bit is not aut                                   | •                |               |               |              |              |               |              |

| Bit2: | CCF2: PCA                                        |                  |               |               |              |              | sonware.      |              |

|       | This bit is se                                   |                  | •             |               | ipture occur | rs. When th  | e CCF2 int    | errupt is    |

|       | enabled, set                                     |                  |               |               | •            |              |               |              |

|       | bit is not aut                                   | -                |               |               |              |              |               |              |

| Bit1: | CCF1: PCA                                        | Module 1 (       | Capture/Con   | npare Flag.   |              |              |               |              |

|       | This bit is se                                   |                  |               |               |              |              |               |              |

|       | enabled, set                                     | -                |               |               |              |              |               | outine. This |

| Dire  | bit is not aut                                   |                  |               |               | d must be o  | cleared by s | software.     |              |

| Bit0: | CCF0: PCA                                        |                  | •             | •             |              |              |               |              |

|       |                                                  | ببالم سما برمائد |               |               |              |              |               | a record in  |

|       | This bit is se                                   |                  |               |               |              |              |               |              |

|       | This bit is se<br>enabled, set<br>bit is not aut | ting this bit    | causes the    | CPU to vec    | tor to the P | CA interrup  | ot service re |              |

#### SFR Definition 18.1. PCA0CN: PCA Control