#### Silicon Labs - C8051F314 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 29                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f314 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 18.7. PCA0CPHn: PCA Capture Module High Byte      | . 219 |

|------------------------------------------------------------------|-------|

| C2 Register Definition 20.1. C2ADD: C2 Address                   | . 223 |

| C2 Register Definition 20.2. DEVICEID: C2 Device ID              | . 223 |

| C2 Register Definition 20.3. REVID: C2 Revision ID               | . 224 |

| C2 Register Definition 20.4. FPCTL: C2 Flash Programming Control | . 224 |

| C2 Register Definition 20.5. FPDAT: C2 Flash Programming Data    | . 224 |

NOTES:

| Name | Pi        | n Number  | s       | Turne            | Description                                                 |

|------|-----------|-----------|---------|------------------|-------------------------------------------------------------|

| Name | 'F310/2/4 | 'F311/3/5 | 'F316/7 | Туре             | Description                                                 |

| P1.5 | 21        | 17        | 13      | D I/O or<br>A In | Port 1.5. See <b>Section 13</b> for a complete description. |

| P1.6 | 20        | 16        |         | D I/O or<br>A In | Port 1.6. See <b>Section 13</b> for a complete description. |

| P1.7 | 19        | 15        |         | D I/O or<br>A In | Port 1.7. See <b>Section 13</b> for a complete description. |

| P2.0 | 18        | 14        | 12      | D I/O or<br>A In | Port 2.0. See <b>Section 13</b> for a complete description. |

| P2.1 | 17        | 13        | 11      | D I/O or<br>A In | Port 2.1. See <b>Section 13</b> for a complete description. |

| P2.2 | 16        | 12        | 10      | D I/O or<br>A In | Port 2.2. See <b>Section 13</b> for a complete description. |

| P2.3 | 15        | 11        | 9       | D I/O or<br>A In | Port 2.3. See <b>Section 13</b> for a complete description. |

| P2.4 | 14        | 10        | 8       | D I/O or<br>A In | Port 2.4. See <b>Section 13</b> for a complete description. |

| P2.5 | 13        | 9         | 7       | D I/O or<br>A In | Port 2.5. See <b>Section 13</b> for a complete description. |

| P2.6 | 12        | 8         |         | D I/O or<br>A In | Port 2.6. See <b>Section 13</b> for a complete description. |

| P2.7 | 11        | 7         |         | D I/O or<br>A In | Port 2.7. See <b>Section 13</b> for a complete description. |

| P3.1 | 7         |           |         | D I/O or<br>A In | Port 3.1. See <b>Section 13</b> for a complete description. |

| P3.2 | 8         |           |         | D I/O or<br>A In | Port 3.2. See <b>Section 13</b> for a complete description. |

| P3.3 | 9         |           |         | D I/O or<br>A In | Port 3.3. See <b>Section 13</b> for a complete description. |

| P3.4 | 10        |           |         | D I/O or<br>A In | Port 3.4. See <b>Section 13</b> for a complete description. |

Table 4.1. Pin Definitions for the C8051F31x (Continued)

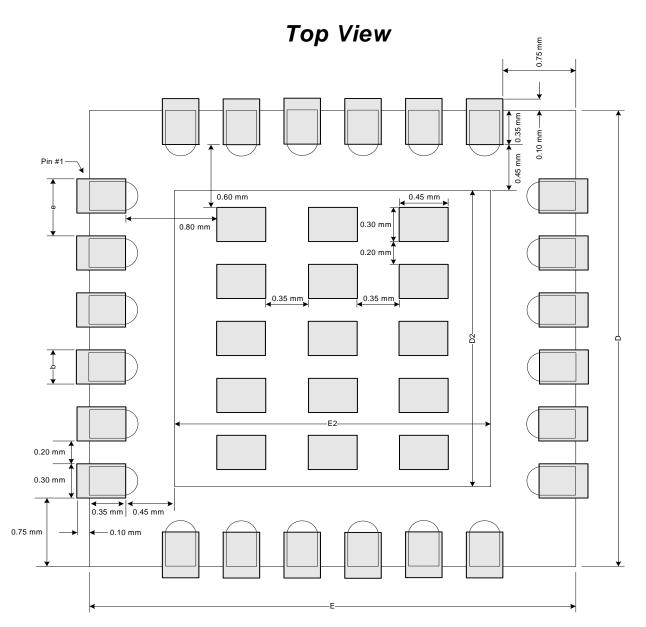

Figure 4.10. QFN-24 Solder Paste Recommendation

| Mnemonic           | Description                              | Bytes | Clock<br>Cycles |

|--------------------|------------------------------------------|-------|-----------------|

| ORL A, direct      | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri         | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data       | OR immediate to A                        | 2     | 2               |

| ORL direct, A      | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data  | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn          | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct      | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri         | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data       | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A      | Exclusive-OR A to direct byte            | 2     | 2               |

| XRL direct, #data  | Exclusive-OR immediate to direct byte    | 3     | 3               |

| CLR A              | Clear A                                  | 1     | 1               |

| CPL A              | Complement A                             | 1     | 1               |

| RL A               | Rotate A left                            | 1     | 1               |

| RLC A              | Rotate A left through Carry              | 1     | 1               |

| RR A               | Rotate A right                           | 1     | 1               |

| RRC A              | Rotate A right through Carry             | 1     | 1               |

| SWAP A             | Swap nibbles of A                        | 1     | 1               |

|                    | Data Transfer                            |       |                 |

| MOV A, Rn          | Move Register to A                       | 1     | 1               |

| MOV A, direct      | Move direct byte to A                    | 2     | 2               |

| MOV A, @Ri         | Move indirect RAM to A                   | 1     | 2               |

| MOV A, #data       | Move immediate to A                      | 2     | 2               |

| MOV Rn, A          | Move A to Register                       | 1     | 1               |

| MOV Rn, direct     | Move direct byte to Register             | 2     | 2               |

| MOV Rn, #data      | Move immediate to Register               | 2     | 2               |

| MOV direct, A      | Move A to direct byte                    | 2     | 2               |

| MOV direct, Rn     | Move Register to direct byte             | 2     | 2               |

| MOV direct, direct | Move direct byte to direct byte          | 3     | 3               |

| MOV direct, @Ri    | Move indirect RAM to direct byte         | 2     | 2               |

| MOV direct, #data  | Move immediate to direct byte            | 3     | 3               |

| MOV @Ri, A         | Move A to indirect RAM                   | 1     | 2               |

| MOV @Ri, direct    | Move direct byte to indirect RAM         | 2     | 2               |

| MOV @Ri, #data     | Move immediate to indirect RAM           | 2     | 2               |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant           | 3     | 3               |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A        | 1     | 3               |

| MOVC A, @A+PC      | Move code byte relative PC to A          | 1     | 3               |

| MOVX A, @Ri        | Move external data (8-bit address) to A  | 1     | 3               |

| MOVX @Ri, A        | Move A to external data (8-bit address)  | 1     | 3               |

| MOVX A, @DPTR      | Move external data (16-bit address) to A | 1     | 3               |

| MOVX @DPTR, A      | Move A to external data (16-bit address) | 1     | 3               |

| PUSH direct        | Push direct byte onto stack              | 2     | 2               |

| POP direct         | Pop direct byte from stack               | 2     | 2               |

| XCH A, Rn          | Exchange Register with A                 | 1     | 1               |

| XCH A, direct      | Exchange direct byte with A              | 2     | 2               |

## Table 8.1. CIP-51 Instruction Set Summary (Continued)

### SFR Definition 8.6. B: B Register

|   | R/W<br>B.7 | R/W<br>B.6                    | R/W<br>B.5 | R/W<br>B.4  | R/W<br>B.3 | R/W<br>B.2    | R/W<br>B.1                            | R/W<br>B.0             | Reset Value<br>00000000 |

|---|------------|-------------------------------|------------|-------------|------------|---------------|---------------------------------------|------------------------|-------------------------|

| L | Bit7       | Bit6                          | Bit5       | Bit4        | Bit3       | Bit2          | Bit1<br>(bit                          | Bit0<br>t addressable) | SFR Address:<br>0xF0    |

|   | Bits7–0:   | B: B Registe<br>This register |            | a second ad | ccumulator | for certain a | , , , , , , , , , , , , , , , , , , , | ,                      |                         |

#### 8.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 14 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Note: Any instruction that clears the EA bit should be immediately followed by an instruction that has two or more opcode bytes. For example:

```

// in 'C':

EA = 0; // clear EA bit

EA = 0; // ... followed by another 2-byte opcode

; in assembly:

CLR EA ; clear EA bit

CLR EA ; ... followed by another 2-byte opcode

```

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the EA bit will return a '0' inside the interrupt service routine. When the "CLR EA" opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI)

any other reset source. For example, if the  $V_{DD}$  monitor is enabled and a software reset is performed, the  $V_{DD}$  monitor will still be enabled after the reset.

**Important Note:** The  $V_{DD}$  monitor must be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for configuring the  $V_{DD}$  monitor as a reset source is shown below:

- Step 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = '1').

- Step 2. Wait for the V<sub>DD</sub> monitor to stabilize (see Table 9.1 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines that erase or write Flash memory.

- Step 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = '1').

See Figure 9.2 for  $V_{DD}$  monitor timing; note that the reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 9.1 for complete electrical characteristics of the  $V_{DD}$  monitor.

| SFR Definition 9.1. VDM0CN: | V <sub>DD</sub> Monitor Control |

|-----------------------------|---------------------------------|

|-----------------------------|---------------------------------|

| R/W      | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R                                                                                                                  | R                                                        | R                                        | R                            | R            | R    | Reset Value |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------|------------------------------|--------------|------|-------------|--|--|--|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                    |                                                          | Reserved                                 |                              |              |      | Variable    |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit5                                                                                                               | Bit4                                                     | Bit3                                     | Bit2                         | Bit1         | Bit0 | J vanabio   |  |  |  |

| Diti     | SFR Address: 0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                    |                                                          |                                          |                              |              |      |             |  |  |  |

| Bit7:    | Bit7: VDMEN: V <sub>DD</sub> Monitor Enable.<br>This bit is turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system<br>resets until it is also selected as a reset source in register RSTSRC (Figure 9.2). The V <sub>DD</sub><br>Monitor must be allowed to stabilize before it is selected as a reset source. <b>Selecting the</b><br>V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset.<br>See Table 9.1 for the minimum V <sub>DD</sub> Monitor turn-on time. |                                                                                                                    |                                                          |                                          |                              |              |      |             |  |  |  |

| Bit6:    | 0: $V_{DD}$ Monit<br>1: $V_{DD}$ Monit<br>$V_{DD}$ STAT: V<br>This bit indic<br>0: $V_{DD}$ is at c<br>1: $V_{DD}$ is abo                                                                                                                                                                                                                                                                                                                                                                                                                                   | tor Disabled<br>for Enabled<br>f <sub>DD</sub> Status.<br>ates the cu<br>for below the<br>pove the V <sub>DD</sub> | I.<br>rrent power<br>V <sub>DD</sub> monit<br>monitor th | supply stat<br>tor threshold<br>reshold. | us (V <sub>DD</sub> Mo<br>d. | onitor outpu | t).  |             |  |  |  |

| Bits5–0: | Reserved. R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ead = Varia                                                                                                        | ble. Write =                                             | don't care                               |                              |              |      |             |  |  |  |

### 9.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 9.1 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

- 10. Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 11. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 10.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in AN201, "Writing to Flash from Firm-ware", available from the Silicon Laboratories web site.

| R/W                        | R/W                                                                                                                                                                                                                             | R/W                                                                                                                                                                       | R/W                                                                                                                                                | R/W                                                                                                                                            | R/W                                                                                      | R/W                                                                    | R/W                                                                | Reset Value                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|

| -                          | -                                                                                                                                                                                                                               | -                                                                                                                                                                         | -                                                                                                                                                  | -                                                                                                                                              | -                                                                                        | PSEE                                                                   | PSWE                                                               | 0000000                                                   |

| Bit7                       | Bit6                                                                                                                                                                                                                            | Bit5                                                                                                                                                                      | Bit4                                                                                                                                               | Bit3                                                                                                                                           | Bit2                                                                                     | Bit1                                                                   | Bit0                                                               | SFR Address:                                              |

|                            |                                                                                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                |                                                                                          |                                                                        |                                                                    | 0x8F                                                      |

| Bits7–2:<br>Bit1:<br>Bit0: | UNUSED: Re<br>PSEE: Progr<br>Setting this b<br>to be erased<br>Flash memori<br>tion addresse<br>0: Flash prog<br>1: Flash prog<br>PSWE: Prog<br>Setting this b<br>write instruct<br>0: Writes to F<br>1: Writes to F<br>memory. | am Store E<br>bit (in combi<br>. If this bit is<br>ry using the<br>ed by the N<br>gram memo<br>gram memo<br>ram Store N<br>bit allows we<br>ion. The Fla<br>Flash program | rase Enabl<br>nation with<br>s logic 1 an<br>MOVX inst<br>IOVX instru-<br>ory erasure<br>Write Enabl<br>riting a byte<br>ash location<br>am memory | e<br>PSWE) allo<br>d Flash writ<br>struction will<br>action. The v<br>disabled.<br>enabled.<br>e<br>of data to t<br>n should be<br>y disabled. | ows an entir<br>es are enat<br>erase the e<br>value of the<br>he Flash pr<br>erased befo | oled (PSWE<br>entire page<br>data byte w<br>ogram men<br>ore writing o | is logic 1)<br>that contain<br>written does<br>nory using<br>data. | , a write to<br>ns the loca-<br>s not matter.<br>the MOVX |

### SFR Definition 10.1. PSCTL: Program Store R/W Control

116

## 13. Port Input/Output

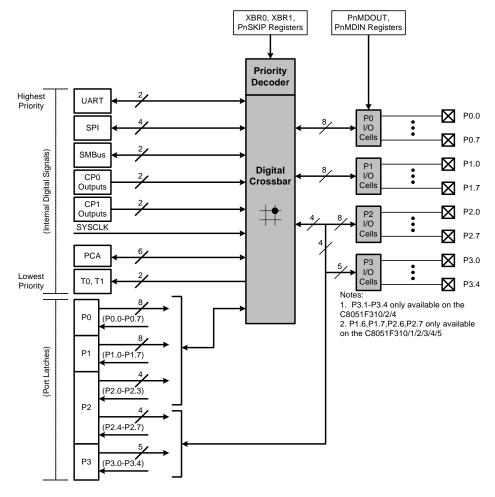

Digital and analog resources are available through 29 I/O pins (C8051F310/2/4), or 25 I/O pins (C8051F311/3/5), or 21 I/O pins (C8051F316/7). Port pins are organized as three byte-wide Ports and one 5-bit-wide (C8051F310/2/4) or 1-bit-wide (C8051F311/3/5) Port. In the C8051F316/7, the port pins are organized as one byte-wide Port, two 6-bit-wide Ports and one 1-bit-wide Port. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input; Port pins P0.0-P2.3 can be assigned to one of the internal digital resources as shown in Figure 13.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. The state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 13.3 and Figure 13.4). The registers XBR0 and XBR1, defined in SFR Definition 13.1 and SFR Definition 13.2, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 13.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1,2,3). Complete Electrical Specifications for Port I/O are given in Table 13.1 on page 143.

| R/W      | R/W                                                                                                                           | R/W                                                                                                 | R/W                                       | R/W                          | R/W        | R/W      | R/W  | Reset Value  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|------------|----------|------|--------------|--|--|

| P0.7     | P0.6                                                                                                                          | P0.5                                                                                                | P0.4                                      | P0.3                         | P0.2       | P0.1     | P0.0 | 11111111     |  |  |

| Bit7     | Bit6                                                                                                                          | Bit5                                                                                                | Bit4                                      | Bit3                         | Bit2       | Bit1     | Bit0 | SFR Address: |  |  |

|          | (bit addressable) 0x80                                                                                                        |                                                                                                     |                                           |                              |            |          |      |              |  |  |

| Bits7–0: | P0.[7:0]<br>Write - Outpo<br>0: Logic Low<br>1: Logic High<br>Read - Alwa<br>pin when con<br>0: P0.n pin is<br>1: P0.n pin is | <ul> <li>Output.</li> <li>h Output (hi<br/>ys reads '1'<br/>nfigured as<br/>s logic low.</li> </ul> | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | ponding PC | )MDOUT.n | ,    | reads Port   |  |  |

## SFR Definition 13.3. P0: Port0

### SFR Definition 13.4. POMDIN: Port0 Input Mode

| R/W      | R/W                                            | R/W              | R/W  | R/W           | R/W          | R/W           | R/W         | Reset Value |

|----------|------------------------------------------------|------------------|------|---------------|--------------|---------------|-------------|-------------|

|          |                                                |                  |      |               |              |               |             | 11111111    |

| Bit7     | Bit6                                           | Bit5             | Bit4 | Bit3          | Bit2         | Bit1          | Bit0        | SFR Address |

|          |                                                |                  |      |               |              |               |             | 0xF1        |

| Bits7–0: | Analog Input<br>Port pins con<br>receiver disa | figured as bled. |      | its have thei | ir weak pull | up, digital d | lriver, and | digital     |

| R/W      | R/W                                                                                                                            | R/W                                                              | R/W                                       | R/W                          | R/W         | R/W          | R/W  | Reset Value  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|--------------|------|--------------|--|--|--|

| P2.7     | P2.6                                                                                                                           | P2.5                                                             | P2.4                                      | P2.3                         | P2.2        | P2.1         | P2.0 | 11111111     |  |  |  |

| Bit7     | Bit6                                                                                                                           | Bit5                                                             | Bit4                                      | Bit3                         | Bit2        | Bit1         | Bit0 | SFR Address: |  |  |  |

|          | (bit addressable) 0xA0                                                                                                         |                                                                  |                                           |                              |             |              |      |              |  |  |  |

| Bits7–0: | P2.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alway<br>pin when cor<br>0: P2.n pin is<br>1: P2.n pin is | Output.<br>Output (hi<br>/s reads '1<br>figured as<br>logic low. | gh impedaı<br>if selected<br>digital inpu | nce if corres<br>as analog i | sponding P2 | 2MDOUT.n     | ,    | reads Port   |  |  |  |

| Note:    | Only P2.0–P2                                                                                                                   | 5 are assoc                                                      | iated with Po                             | ort pins on th               | e C8051F31  | 6/7 devices. |      |              |  |  |  |

|          |                                                                                                                                |                                                                  |                                           |                              |             |              |      |              |  |  |  |

## SFR Definition 13.11. P2: Port2

## SFR Definition 13.12. P2MDIN: Port2 Input Mode

| R/W      | R/W                                                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value                      |  |  |  |

|----------|--------------------------------------------------------------------------------|------|------|------|------|------|------|----------------------------------|--|--|--|

| Bit7     | Bit6                                                                           | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | BitO | 11111111<br>SFR Address:<br>0xF3 |  |  |  |

| Bits7–0: |                                                                                |      |      |      |      |      |      |                                  |  |  |  |

| Note:    | Note: Only P2.0–P2.5 are associated with Port pins on the C8051F316/7 devices. |      |      |      |      |      |      |                                  |  |  |  |

|          |                                                                                |      |      |      |      |      |      |                                  |  |  |  |

### 14.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- The I2C-Bus and How to Use It (including specifications), Philips Semiconductor.

- The I2C-Bus Specification—Version 2.0, Philips Semiconductor.

- System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### 14.2. SMBus Configuration

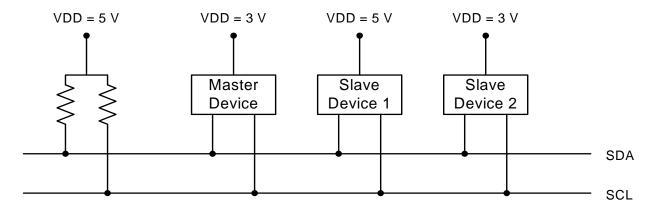

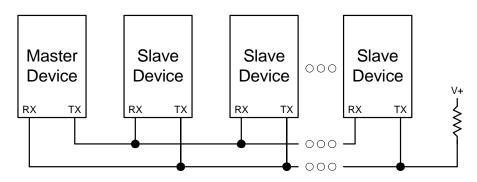

Figure 14.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 14.2. Typical SMBus Configuration

#### 14.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

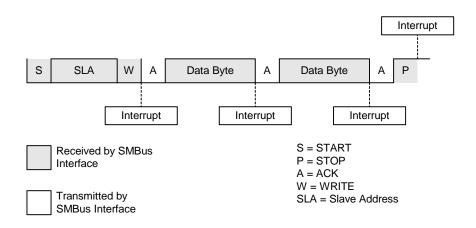

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 14.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

#### 14.5.3. Slave Receiver Mode

Serial data is received on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode when a START followed by a slave address and direction bit (WRITE in this case) is received. Upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are received. Software must write the ACK bit after each received byte to ACK or NACK the received byte. The interface exits Slave Receiver Mode after receiving a STOP. Note that the interface will switch to Slave Transmitter Mode if SMB0DAT is written while an active Slave Receiver. Figure 14.7 shows a typical Slave Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 14.7. Typical Slave Receiver Sequence

#### 14.5.4. Slave Transmitter Mode

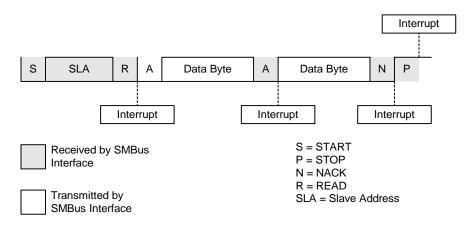

Serial data is transmitted on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Transmitter Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until a START is detected. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 14.8 shows a typical Slave Transmitter sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

Figure 14.8. Typical Slave Transmitter Sequence

|                   | Values Read      |       |         |     |                                                                          |                                                                  |     | Values<br>Written |     |  |

|-------------------|------------------|-------|---------|-----|--------------------------------------------------------------------------|------------------------------------------------------------------|-----|-------------------|-----|--|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                      | Typical Response Options                                         | STA | STO               | ACK |  |

| Slave Transmitter | 0100             | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                          | No action required (expecting STOP condition).                   | 0   | 0                 | х   |  |

|                   |                  | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                           | Load SMB0DAT with next data byte to transmit.                    | 0   | 0                 | х   |  |

| e Trar            |                  | 0     | 1       | Х   | A Slave byte was transmitted; error detected.                            | No action required (expecting<br>Master to end transfer).        | 0   | 0                 | х   |  |

| Slav              | 0101             | 0     | x       | x   | A STOP was detected while<br>an addressed Slave Transmit-<br>ter.        | No action required (transfer com-<br>plete).                     | 0   | 0                 | х   |  |

|                   | 0010             | 1     | 0       | x   | A slave address was                                                      | Acknowledge received address.                                    | 0   | 0                 | 1   |  |

|                   |                  |       |         |     | received; ACK requested.                                                 | Do not acknowledge received address.                             | 0   | 0                 | 0   |  |

|                   |                  |       | 1       | x   | Lost arbitration as master;<br>slave address received; ACK<br>requested. | Acknowledge received address.                                    |     | 0                 | 1   |  |

|                   |                  | 1     |         |     |                                                                          | Do not acknowledge received address.                             | 0   | 0                 | 0   |  |

|                   |                  |       |         |     |                                                                          | Reschedule failed transfer; do not acknowledge received address. | 1   | 0                 | 0   |  |

| 5                 | 0010             | 0     | 1       | х   |                                                                          | Abort failed transfer.                                           | 0   | 0                 | Х   |  |

| eive              |                  |       |         |     | ing a repeated START.                                                    | Reschedule failed transfer.                                      | 1   | 0                 | Х   |  |

| Slave Receiver    | 0001             | 1     | 1       | Х   | Lost arbitration while attempt-<br>ing a STOP.                           | No action required (transfer com-<br>plete/aborted).             | 0   | 0                 | 0   |  |

| Slave             |                  | 0     | 0       | х   | A STOP was detected while<br>an addressed slave receiver.                | No action required (transfer com-<br>plete).                     | 0   | 0                 | х   |  |

|                   |                  | 0     | 1       | х   | Lost arbitration due to a                                                | Abort transfer.                                                  | 0   | 0                 | Х   |  |

|                   |                  | 0     |         |     | detected STOP.                                                           | Reschedule failed transfer.                                      | 1   | 0                 | Х   |  |

|                   | 0000             | 1     | 0       | x   | A slave byte was received;                                               | Acknowledge received byte; Read SMB0DAT.                         |     | 0                 | 1   |  |

|                   |                  | 1     | 0       |     | ACK requested.                                                           | Do not acknowledge received byte.                                | 0   | 0                 | 0   |  |

|                   |                  | 1     | 1       | x   | Lost arbitration while transmit-                                         | Abort failed transfer.                                           | 0   | 0                 | 0   |  |

|                   |                  |       |         |     | ting a data byte as master.                                              | Reschedule failed transfer.                                      | 1   | 0                 | 0   |  |

## Table 14.4. SMBus Status Decoding (Continued)

#### 15.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 15.6. UART Multi-Processor Mode Interconnect Diagram

### 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. Note that the setting of NSSMD bits affects the pinout of the device. When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 129 for general purpose port I/O and crossbar information.

#### 17.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 17.5. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| T3MH | T3XCLK | TMR3H Clock      |  |

|------|--------|------------------|--|

|      |        | Source           |  |

| 0    | 0      | SYSCLK/12        |  |

| 0    | 1      | External Clock/8 |  |

| 1    | Х      | SYSCLK           |  |

| T3ML | T3XCLK | TMR3L Clock<br>Source |

|------|--------|-----------------------|

| 0    | 0      | SYSCLK/12             |

| 0    | 1      | External Clock/8      |

| 1    | Х      | SYSCLK                |

Note: External clock divided by 8 is synchronized with the system clock, and the external clock must be less than or equal to the system clock to operate in this mode.

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 17.7. Timer 3 8-Bit Mode Block Diagram

#### 18.2. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

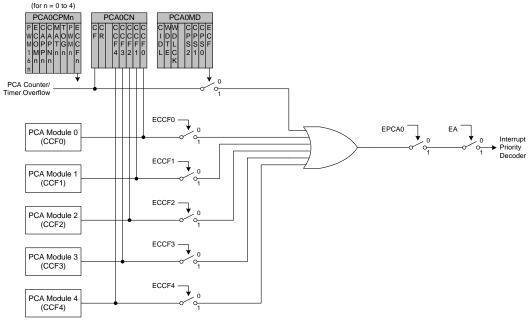

Table 18.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note: PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 18.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM           | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                                |

|----------|----------------|------|------|-----|-----|-----|------|-----------------------------------------------|

| Х        | Х              | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge<br>on CEXn |

| Х        | Х              | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn    |

| Х        | Х              | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn    |

| Х        | 1              | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                                |

| Х        | 1              | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                             |

| Х        | 1              | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                              |

| 0        | 1              | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                   |

| 1        | 1              | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator                  |

| X = Don' | X = Don't Care |      |      |     |     |     |      |                                               |

### Table 18.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

NOTES: