Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f315-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 18.2.3.High-Speed Output Mode                  | 208 |

|------------------------------------------------|-----|

| 18.2.4. Frequency Output Mode                  | 209 |

| 18.2.5.8-Bit Pulse Width Modulator Mode        |     |

| 18.2.6.16-Bit Pulse Width Modulator Mode       | 211 |

| 18.3.Watchdog Timer Mode                       | 212 |

| 18.3.1.Watchdog Timer Operation                |     |

| 18.3.2.Watchdog Timer Usage                    | 213 |

| 18.4.Register Descriptions for PCA             |     |

| 19. Revision Specific Behavior                 |     |

| 19.1.Revision Identification                   |     |

| 19.2.Reset Behavior                            | 221 |

| 19.2.1.Weak Pullups on GPI <u>O P</u> ins      | 221 |

| 19.2.2.V <sub>DD</sub> Monitor and the RST Pin |     |

| 19.3.PCA Counter                               |     |

| 20. C2 Interface                               |     |

| 20.1.C2 Interface Registers                    |     |

| -                                              | 225 |

| -                                              | 226 |

|                                                | 228 |

|                                                |     |

NOTES:

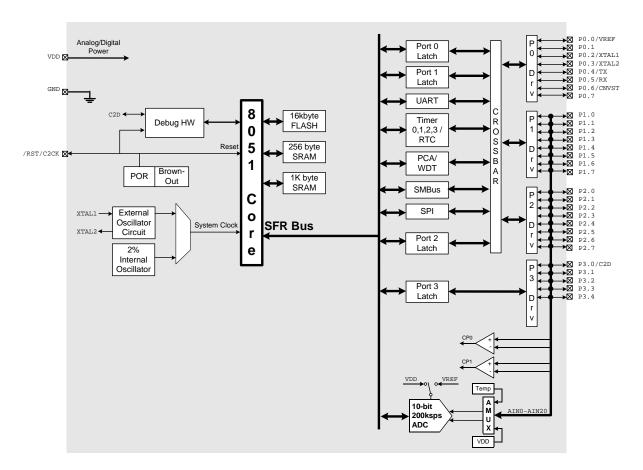

### 1. System Overview

C8051F31x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- True 10-bit 200 ksps 25-channel single-ended/differential ADC with analog multiplexer (C8051F310/1/2/3/6)

- Precision programmable 25 MHz internal oscillator

- 16 kB (C8051F310/1/6/7) or 8 kB (C8051F312/3/4/5) of on-chip Flash memory

- 1280 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- On-chip Voltage Comparators (2)

- 29/25/21 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  monitor, Watchdog Timer, and clock oscillator, the C8051F31x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system programming and debugging without occupying package pins.

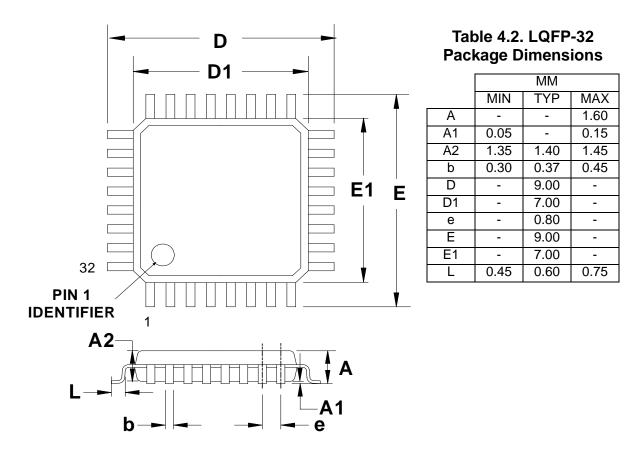

Each device is specified for 2.7-to-3.6 V operation over the industrial temperature range (–45 to +85 °C). The Port I/O and RST pins are tolerant of input signals up to 5 V. The C8051F31x are available in 32-pin LQFP, 28-pin QFN, and 24-pin QFN packages. See Table 1.1 for ordering part numbers. Note: QFN packages are also referred to as MLP or MLF packages.

Figure 1.1. C8051F310 Block Diagram

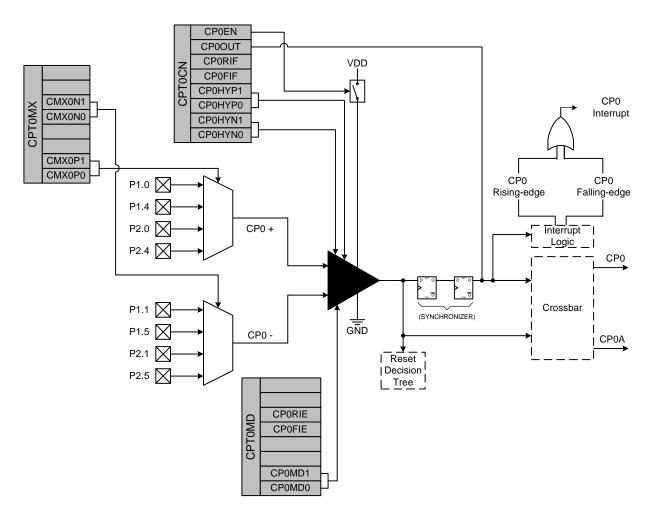

### 1.8. Comparators

C8051F31x devices include two on-chip voltage comparators that are enabled/disabled and configured via user software. Port I/O pins may be configured as comparator inputs via a selection mux. Two comparator outputs may be routed to a Port pin if desired: a latched output and/or an unlatched (asynchronous) output. Comparator response time is programmable, allowing the user to select between high-speed and low-power modes. Positive and negative hysteresis are also configurable.

Comparator interrupts may be generated on rising, falling, or both edges. When in IDLE mode, these interrupts may be used as a "wake-up" source. Comparator0 may also be configured as a reset source. Figure 1.16 shows he Comparator0 block diagram.

Figure 1.16. Comparator0 Block Diagram

Figure 4.2. LQFP-32 Package Diagram

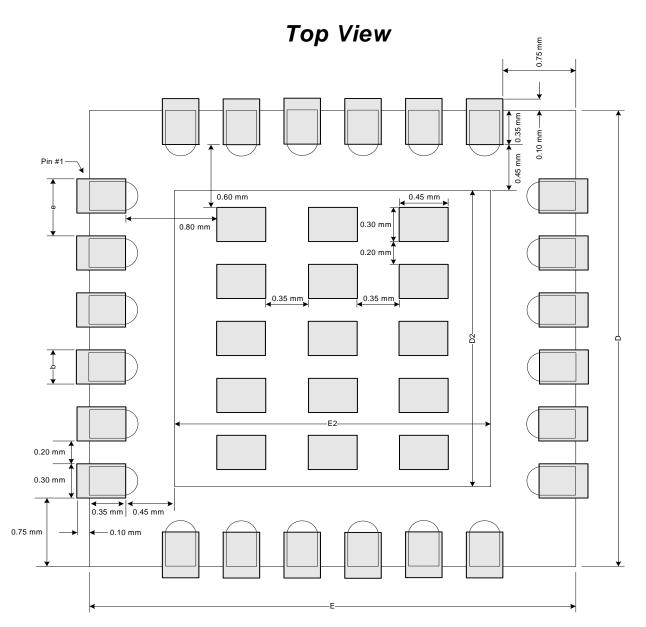

Figure 4.10. QFN-24 Solder Paste Recommendation

#### 5.3. Modes of Operation

ADC0 has a maximum conversion speed of 200 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register (system clock divided by (AD0SC + 1) for  $0 \le AD0SC \le 31$ ).

#### 5.3.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2-0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a '1' to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

- 6. A Timer 3 overflow

Writing a '1' to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See **Section "17. Timers" on page 187** for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to '1' Bit6 in register P0SKIP. See **Section "13. Port Input/Output" on page 129** for details on Port I/O configuration.

CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 8.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access external data memory (Note: the C8051F31x does not support external data or program memory). In the CIP-51, the MOVX write instruction is used to accesses external RAM and the on-chip program memory space implemented as re-programmable Flash memory. The Flash access feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 111** for further details.

| Mnemonic          |                                          |   |   |  |  |

|-------------------|------------------------------------------|---|---|--|--|

|                   | Arithmetic Operations                    | • |   |  |  |

| ADD A, Rn         | Add register to A                        | 1 | 1 |  |  |

| ADD A, direct     | Add direct byte to A                     | 2 | 2 |  |  |

| ADD A, @Ri        | Add indirect RAM to A                    | 1 | 2 |  |  |

| ADD A, #data      | Add immediate to A                       | 2 | 2 |  |  |

| ADDC A, Rn        | Add register to A with carry             | 1 | 1 |  |  |

| ADDC A, direct    | Add direct byte to A with carry          | 2 | 2 |  |  |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1 | 2 |  |  |

| ADDC A, #data     | Add immediate to A with carry            | 2 | 2 |  |  |

| SUBB A, Rn        | Subtract register from A with borrow     | 1 | 1 |  |  |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2 | 2 |  |  |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1 | 2 |  |  |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2 | 2 |  |  |

| INC A             | Increment A                              | 1 | 1 |  |  |

| INC Rn            | Increment register                       | 1 | 1 |  |  |

| INC direct        | Increment direct byte                    | 2 | 2 |  |  |

| INC @Ri           | Increment indirect RAM                   | 1 | 2 |  |  |

| DEC A             | Decrement A                              | 1 | 1 |  |  |

| DEC Rn            | Decrement register                       | 1 | 1 |  |  |

| DEC direct        | Decrement direct byte                    | 2 | 2 |  |  |

| DEC @Ri           | Decrement indirect RAM                   | 1 | 2 |  |  |

| INC DPTR          | Increment Data Pointer                   | 1 | 1 |  |  |

| MUL AB            | Multiply A and B                         | 1 | 4 |  |  |

| DIV AB            | Divide A by B                            | 1 | 8 |  |  |

| DA A              | Decimal adjust A                         | 1 | 1 |  |  |

|                   | Logical Operations                       |   |   |  |  |

| ANL A, Rn         | AND Register to A                        | 1 | 1 |  |  |

| ANL A, direct     | AND direct byte to A                     | 2 | 2 |  |  |

| ANL A, @Ri        | AND indirect RAM to A                    | 1 | 2 |  |  |

| ANL A, #data      | AND immediate to A                       | 2 | 2 |  |  |

| ANL direct, A     | AND A to direct byte                     | 2 | 2 |  |  |

| ANL direct, #data | AND immediate to direct byte             | 3 | 3 |  |  |

| ORL A, Rn         | OR Register to A                         | 1 | 1 |  |  |

### Table 8.1. CIP-51 Instruction Set Summary

| Mnemonic             | Description                                         | Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock<br>Cycles |  |  |

|----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| XCH A, @Ri           | Exchange indirect RAM with A                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

|                      | Boolean Manipulation                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |

| CLR C                | Clear Carry                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1               |  |  |

| CLR bit              | Clear direct bit                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| SETB C               | Set Carry                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1               |  |  |

| SETB bit             | Set direct bit                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| CPL C                | Complement Carry                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1               |  |  |

| CPL bit              | Complement direct bit                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| ANL C, bit           | AND direct bit to Carry                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| ORL C, bit           | OR direct bit to carry                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| MOV C, bit           | Move direct bit to Carry                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| MOV bit, C           | Move Carry to direct bit                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2               |  |  |

| JC rel               | Jump if Carry is set                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2/3             |  |  |

| JNC rel              | Jump if Carry is not set                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2/3             |  |  |

| JB bit, rel          | Jump if direct bit is set                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| JNB bit, rel         | Jump if direct bit is not set                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

|                      | Program Branching                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |  |  |

| ACALL addr11         | Absolute subroutine call                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3               |  |  |

| LCALL addr16         | Long subroutine call                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4               |  |  |

| RET                  | Return from subroutine                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5               |  |  |

| RETI                 | Return from interrupt                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5               |  |  |

| AJMP addr11          | Absolute jump                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3               |  |  |

| LJMP addr16          | Long jump                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4               |  |  |

| SJMP rel             | Short jump (relative address)                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3               |  |  |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3               |  |  |

| JZ rel               | Jump if A equals zero                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2/3             |  |  |

| JNZ rel              | Jump if A does not equal zero                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2/3             |  |  |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | ct RAM with A1bble of indirect RAM with A1lean Manipulation1212121ct bit2Carry1act bit2Carry2of direct bit to Carry2of act bit2of direct bit to Carry2of direct bit to Carry2of act bit2set3is set3is set3is set3is set and clear bit3oroutine1rrupt1call2call3outine1call2call3ive address)2ative to DPTR1zero2ot equal zero2oyte to A and jump if not equal3iate to Register and jump if not3iate to indirect and jump if not3iate to indirect and jump if not3 | 4/5             |  |  |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2/3             |  |  |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3/4             |  |  |

| NOP                  | No operation                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1               |  |  |

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

#### 10.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- Step 1. Disable interrupts (recommended).

- Step 2. Erase the 512-byte Flash page containing the target location, as described in **Section 10.1.2**.

- Step 3. Set the PSWE bit (register PSCTL).

- Step 4. Clear the PSEE bit (register PSCTL).

- Step 5. Write the first key code to FLKEY: 0xA5.

- Step 6. Write the second key code to FLKEY: 0xF1.

- Step 7. Using the MOVX instruction, write a single data byte to the desired location within the 512 byte sector.

Steps 5–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

#### **Table 10.1. Flash Electrical Characteristics**

| Parameter                   | Conditions                        | Min    | Тур   | Max | Units       |

|-----------------------------|-----------------------------------|--------|-------|-----|-------------|

| Flash Size                  | C8051F310/1/6/7                   | 16384* | _     |     | bytes       |

| FIASIT SIZE                 | C8051F312/3/4/5                   | 8192   | _     |     | Dytes       |

| Endurance                   |                                   | 20 k   | 100 k |     | Erase/Write |

| Erase Cycle Time            | 25 MHz System Clock               | 10     | 15    | 20  | ms          |

| Write Cycle Time            | 25 MHz System Clock               | 40     | 55    | 70  | μs          |

| Note: 512 bytes at location | ons 0x3E00 (C8051F310/1) are rese | rved.  |       |     | •           |

$V_{DD} = 2.7$  to 3.6 V; -40 to +85 °C unless otherwise specified.

#### 10.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

## 13. Port Input/Output

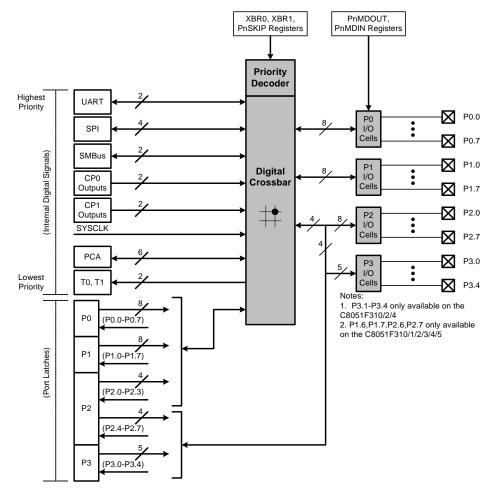

Digital and analog resources are available through 29 I/O pins (C8051F310/2/4), or 25 I/O pins (C8051F311/3/5), or 21 I/O pins (C8051F316/7). Port pins are organized as three byte-wide Ports and one 5-bit-wide (C8051F310/2/4) or 1-bit-wide (C8051F311/3/5) Port. In the C8051F316/7, the port pins are organized as one byte-wide Port, two 6-bit-wide Ports and one 1-bit-wide Port. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input; Port pins P0.0-P2.3 can be assigned to one of the internal digital resources as shown in Figure 13.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. The state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 13.3 and Figure 13.4). The registers XBR0 and XBR1, defined in SFR Definition 13.1 and SFR Definition 13.2, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 13.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1,2,3). Complete Electrical Specifications for Port I/O are given in Table 13.1 on page 143.

Figure 13.1. Port I/O Functional Block Diagram

|         | P0                                    |   |   |   |   |   | P1 |   |   |   |           |             |        |   |   | P2                     |   |   |   |   |   |                                                                                                                 |   |   |

|---------|---------------------------------------|---|---|---|---|---|----|---|---|---|-----------|-------------|--------|---|---|------------------------|---|---|---|---|---|-----------------------------------------------------------------------------------------------------------------|---|---|

|         |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| PIN I/O | 0                                     | 1 | 2 | 3 | 4 | 5 | 6  | 7 | 0 | 1 | 2         | 3           | 4      | 5 | 6 | 7                      | 0 | 1 | 2 | 3 | 4 | 5                                                                                                               | 6 |   |

| ТХО     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| RX0     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| SCK     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| MISO    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| MOSI    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| NSS*    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| SDA     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| SCL     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| CP0     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| CP0A    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | e de la come |   |   |

| CP1     |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | lable                                                                                                           |   |   |

| CP1A    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | Signals Unavailable                                                                                             |   |   |

| SYSCLK  |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | ň                                                                                                               |   |   |

| CEX0    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | nals                                                                                                            |   |   |

| CEX1    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | Sig                                                                                                             |   |   |

| CEX2    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| CEX3    |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| CEX4    |                                       |   | 1 |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   | 1 |                                                                                                                 |   |   |

| ECI     |                                       |   | 1 |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   | ]                                                                                                               |   |   |

| то      |                                       |   | 1 |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   |   |

| T1      |                                       |   |   |   |   |   |    |   |   |   |           |             |        |   |   |                        |   |   |   |   |   |                                                                                                                 |   | ] |

|         | 0 0 <u>1 1</u> 0 0 0 0<br>POSKIP[0:7] |   |   |   |   |   |    | 0 | 0 | 0 | 0<br>P1SK | 0<br>IP[0:7 | 0<br>] | 0 | 0 | 0 0 0 0<br>P2SKIP[0:3] |   |   |   |   |   |                                                                                                                 |   |   |

SF Signals Special Function Signals are not assigned by the Crossbar. When these signals are enabled, the Crossbar must be manually configured to skip their corresponding port pins.

\*Note: NSS is only pinned out in 4-wire SPI mode.

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

### Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

#### 14.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "14.5. SMBus Transfer Modes" on page 157** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "14.4.2. SMB0CN Control Register" on page 153**; Table 14.4 provides a quick SMB0CN decoding reference.

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in **Section "14.4.1. SMBus Configura**tion Register" on page 150.

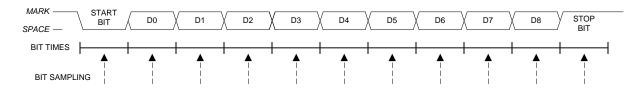

#### 15.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to '1'. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to '1'.

Figure 15.5. 9-Bit UART Timing Diagram

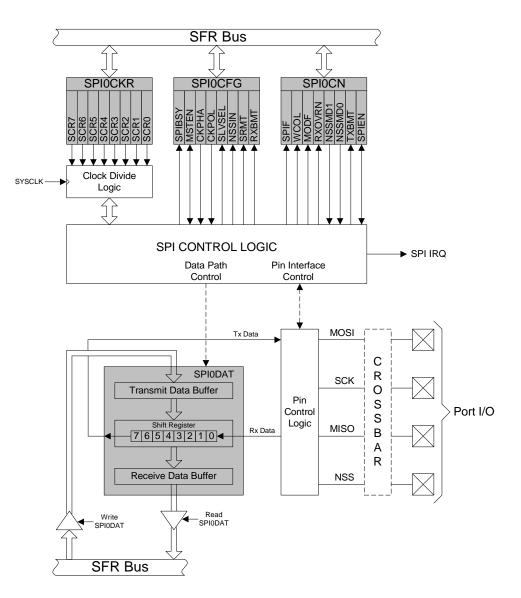

## 16. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

NOTES:

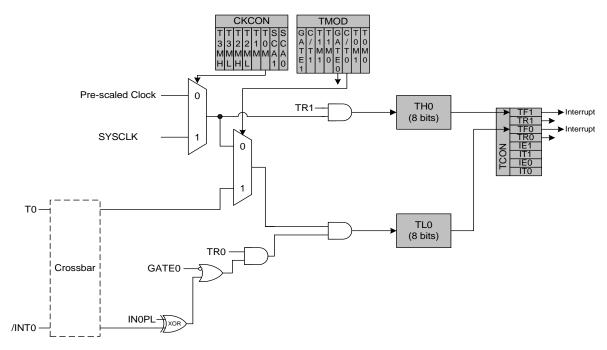

#### 17.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 17.3. T0 Mode 3 Block Diagram

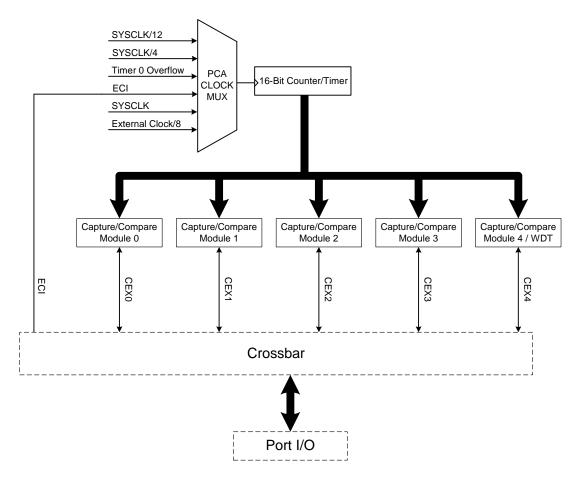

### 18. Programmable Counter Array

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and five 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Crossbar Decoder" on page 131 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "18.2. Capture/Compare Modules" on page 205). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 18.1

**Important Note:** The PCA Module 4 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See **Section 18.3** for details.

Figure 18.1. PCA Block Diagram

NOTES: