Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 25                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 28-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 28-QFN (5x5)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f315 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| 1. | System Overview                                                           |    |

|----|---------------------------------------------------------------------------|----|

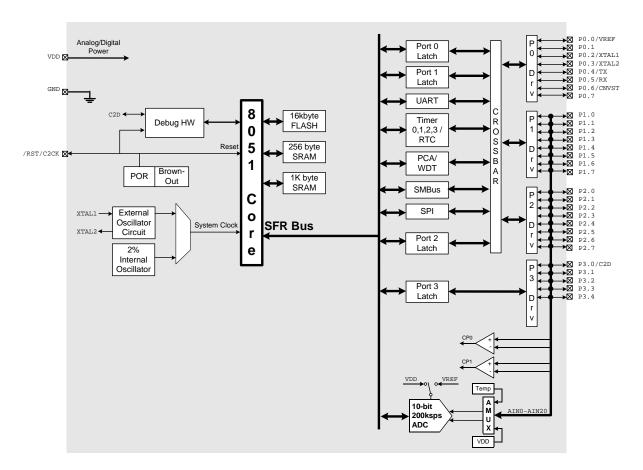

|    | Figure 1.1. C8051F310 Block Diagram                                       | 19 |

|    | Figure 1.2. C8051F311 Block Diagram                                       | 20 |

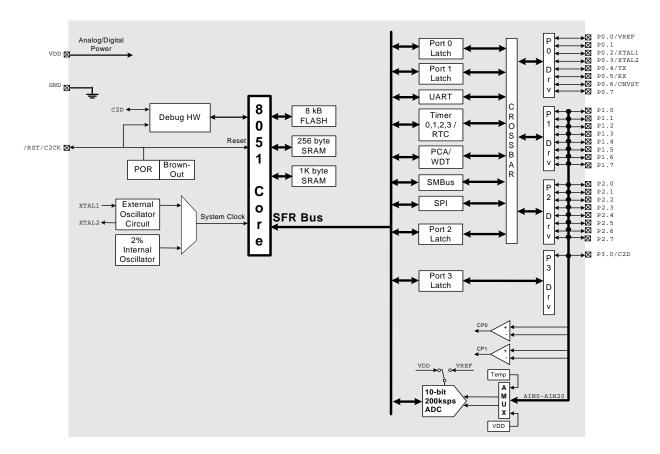

|    | Figure 1.3. C8051F312 Block Diagram                                       | 21 |

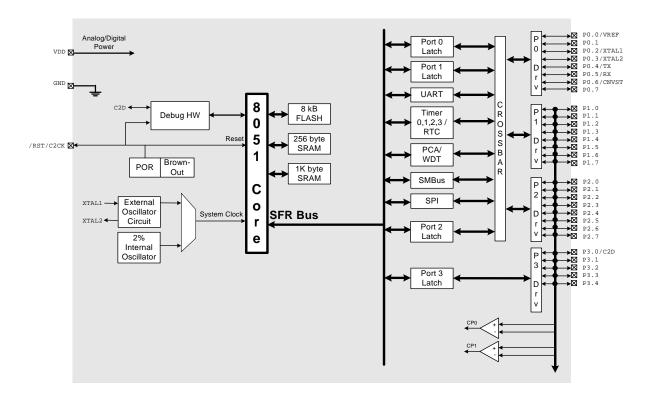

|    | Figure 1.4. C8051F313 Block Diagram                                       | 22 |

|    | Figure 1.5. C8051F314 Block Diagram                                       | 23 |

|    | Figure 1.6. C8051F315 Block Diagram                                       |    |

|    | Figure 1.7. C8051F316 Block Diagram                                       | 25 |

|    | Figure 1.8. C8051F317 Block Diagram                                       | 26 |

|    | Figure 1.9. Comparison of Peak MCU Execution Speeds                       |    |

|    | Figure 1.10. On-Chip Clock and Reset                                      |    |

|    | Figure 1.11. On-Board Memory Map                                          | 29 |

|    | Figure 1.12. Development/In-System Debug Diagram                          |    |

|    | Figure 1.13. Digital Crossbar Diagram                                     |    |

|    | Figure 1.14. PCA Block Diagram                                            |    |

|    | Figure 1.15. 10-Bit ADC Block Diagram                                     |    |

|    | Figure 1.16. Comparator0 Block Diagram                                    |    |

| 2. | Absolute Maximum Ratings                                                  |    |

| 3. | Global DC Electrical Characteristics                                      |    |

| 4. | Pinout and Package Definitions                                            |    |

|    | Figure 4.1. LQFP-32 Pinout Diagram (Top View)                             | 41 |

|    | Figure 4.2. LQFP-32 Package Diagram                                       | 42 |

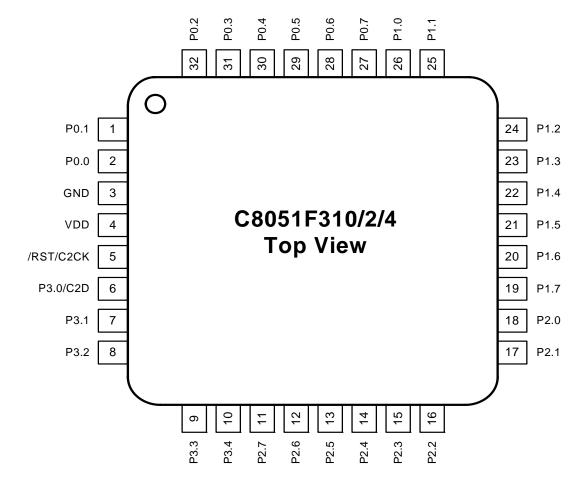

|    | Figure 4.3. QFN-28 Pinout Diagram (Top View)                              | 43 |

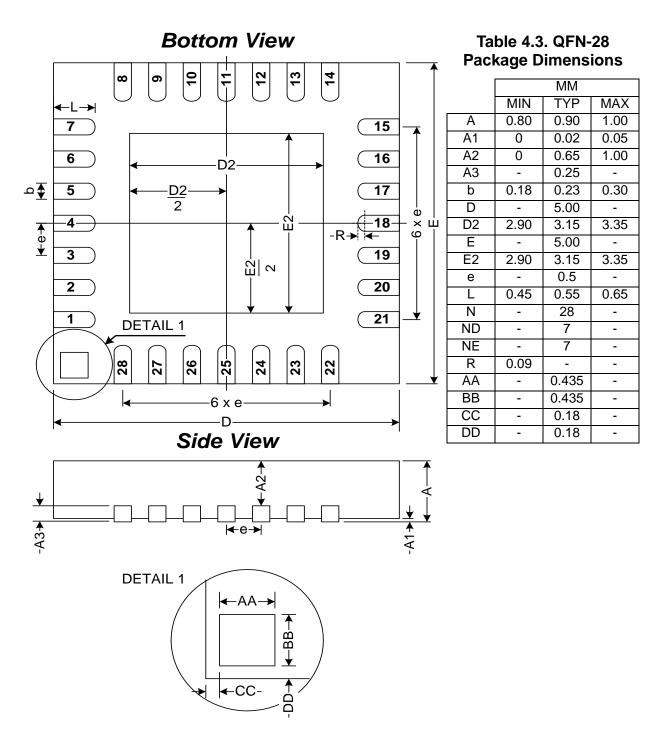

|    | Figure 4.4. QFN-28 Package Drawing                                        | 44 |

|    | Figure 4.5. Typical QFN-28 Landing Diagram                                | 45 |

|    | Figure 4.6. QFN-28 Solder Paste Recommendation                            | 46 |

|    | Figure 4.7. QFN-24 Pinout Diagram (Top View)                              | 47 |

|    | Figure 4.8. QFN-24 Package Drawing                                        | 48 |

|    | Figure 4.9. Typical QFN-24 Landing Diagram                                | 49 |

|    | Figure 4.10. QFN-24 Solder Paste Recommendation                           | 50 |

| 5. | 10-Bit ADC (ADC0, C8051F310/1/2/3/6 only)                                 |    |

|    | Figure 5.1. ADC0 Functional Block Diagram                                 |    |

|    | Figure 5.2. Typical Temperature Sensor Transfer Function                  |    |

|    | Figure 5.3. Temperature Sensor Error with 1-Point Calibration             |    |

|    | Figure 5.4. 10-Bit ADC Track and Conversion Example Timing                |    |

|    | Figure 5.5. ADC0 Equivalent Input Circuits                                |    |

|    | Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data |    |

|    | Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data  |    |

|    | Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data |    |

|    | Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data  | 64 |

| 6. | Voltage Reference (C8051F310/1/2/3/6 only)                                |    |

|    | Figure 6.1. Voltage Reference Functional Block Diagram                    | 67 |

Figure 1.1. C8051F310 Block Diagram

Figure 1.4. C8051F313 Block Diagram

Figure 1.5. C8051F314 Block Diagram

### 1.1. CIP-51<sup>™</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F31x family utilizes Silicon Laboratories' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The CIP-51 core offers all the peripherals included with a standard 8052, including four 16-bit counter/timers, a full-duplex UART with extended baud rate configuration, an enhanced SPI port, 1280 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 29/25/21 I/O pins.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

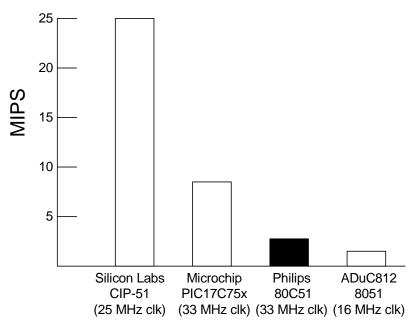

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.9 shows a comparison of peak throughputs for various 8-bit microcontroller cores with their maximum system clocks.

Figure 1.9. Comparison of Peak MCU Execution Speeds

Other electrical characteristics tables are found in the data sheet section corresponding to the associated peripherals. For more information on electrical characteristics for a specific peripheral, refer to the page indicated in Table 3.2.

| Peripheral Electrical Characteristics                         | Page No. |

|---------------------------------------------------------------|----------|

| ADC0 Electrical Characteristics                               | 65       |

| External Voltage Reference Circuit Electrical Characteristics | 68       |

| Comparator Electrical Characteristics                         | 78       |

| Reset Electrical Characteristics                              | 110      |

| Flash Electrical Characteristics                              | 112      |

| Internal Oscillator Electrical Characteristics                | 123      |

| Port I/O DC Electrical Characteristics                        | 143      |

#### Table 3.2. Electrical Characteristics Quick Reference

Figure 4.1. LQFP-32 Pinout Diagram (Top View)

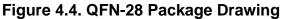

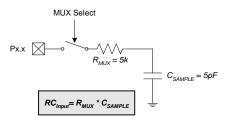

#### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. In low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time requirements.

### **Equation 5.1. ADC0 Settling Time Requirements**

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (10).

**Differential Mode**

### Figure 5.5. ADC0 Equivalent Input Circuits

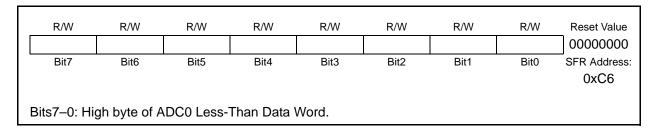

### SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte

### SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte

|   | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |

|---|------------------------------------------------|------|------|------|------|------|------|------|--------------|--|

|   |                                                |      |      |      |      |      |      |      | 0000000      |  |

|   | Bit7                                           | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |

|   |                                                |      |      |      |      |      |      |      | 0xC5         |  |

|   |                                                |      |      |      |      |      |      |      |              |  |

| E | Bits7–0: Low byte of ADC0 Less-Than Data Word. |      |      |      |      |      |      |      |              |  |

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 10.2 summarizes the Flash security features of the C8051F31x devices.

| Action                                                                     | C2 Debug                | User Firmware executing from: |                   |  |  |

|----------------------------------------------------------------------------|-------------------------|-------------------------------|-------------------|--|--|

|                                                                            | Interface               | an unlocked page              | a locked page     |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)        | Permitted               | Permitted                     | Permitted         |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)          | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)        | Permitted               | Permitted                     | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)         | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                     | Permitted               | Permitted                     | Permitted         |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                      | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                | Permitted               | Flash Error Reset             | Flash Error Reset |  |  |

| Erase page containing Lock Byte - Unlock all pages (if any page is locked) | C2 Device<br>Erase Only | Flash Error Reset             | Flash Error Reset |  |  |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)            | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)          | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Read, Write or Erase Reserved Area                                         | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

### Table 10.2. Flash Security Summary

C2 Device Erase - Erases all Flash pages including the page containing the Lock Byte.

Flash Error Reset - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

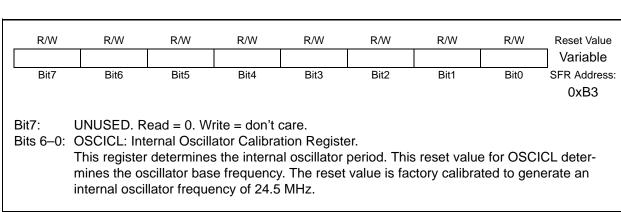

### SFR Definition 12.1. OSCICL: Internal Oscillator Calibration

### SFR Definition 12.2. OSCICN: Internal Oscillator Control

|    | R/W R R/W R/W R/W R/W R/W |                                                                                                                                                                                        |                                                                                                                                                                  |                                                                                                                                        |                                                                                                               |                                                    |       |       |          |

|----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|----------|

| IO | SCEN                      | IFRDY                                                                                                                                                                                  |                                                                                                                                                                  |                                                                                                                                        |                                                                                                               |                                                    | IFCN1 | IFCN0 | 11000000 |

|    | Bit7                      | it7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0                                                                                                                                                 |                                                                                                                                                                  |                                                                                                                                        |                                                                                                               |                                                    |       |       |          |

|    |                           |                                                                                                                                                                                        |                                                                                                                                                                  |                                                                                                                                        |                                                                                                               |                                                    |       |       | 0xB2     |

|    | 6:<br>55–2:<br>51–0:      | IOSCEN: Int<br>0: Internal O<br>1: Internal O<br>IFRDY: Inter<br>0: Internal O<br>1: Internal O<br>UNUSED. R<br>IFCN1-0: Inter<br>00: SYSCLK<br>01: SYSCLK<br>10: SYSCLK<br>11: SYSCLK | scillator Dis<br>scillator Ena<br>nal Oscillator<br>scillator is r<br>scillator is r<br>ead = 0000<br>ernal Oscilla<br>derived fro<br>derived fro<br>derived fro | abled.<br>abled.<br>or Frequence<br>ot running<br>unning at p<br>b, Write = c<br>ator Freque<br>m Internal<br>m Internal<br>m Internal | cy Ready Fl<br>at programmed<br>lon't care.<br>ncy Control<br>Oscillator di<br>Oscillator di<br>Oscillator di | Bits.<br>vided by 8.<br>vided by 4.<br>vided by 2. |       |       |          |

| SFR  | Definition | 13.15. | P3: Port3 |  |

|------|------------|--------|-----------|--|

| •••• |            |        |           |  |

| R/W      | R/W<br>P3.6                                                                                                                                                                                                                                                                                                                                                                                                           | R/W<br>P3.5 | R/W<br>P3.4 | R/W<br>P3.3 | R/W<br>P3.2 | R/W<br>P3.1 | R/W<br>P3.0    | Reset Value    |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|----------------|----------------|--|--|--|--|

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit5        | Bit4        | Bit3        | Bit2        | Bit1        | Bit0           | SFR Address:   |  |  |  |  |

| Bits7–0: |                                                                                                                                                                                                                                                                                                                                                                                                                       |             |             |             |             |             |                |                |  |  |  |  |

|          | <ul> <li>Bits7–0: P3.[7:0]</li> <li>Write - Output appears on I/O pins.</li> <li>0: Logic Low Output.</li> <li>1: Logic High Output (high impedance if corresponding P3MDOUT.n bit = 0).</li> <li>Read - Always reads '1' if selected as analog input in register P3MDIN. Directly reads Port pin when configured as digital input.</li> <li>0: P3.n pin is logic low.</li> <li>1: P3.n pin is logic high.</li> </ul> |             |             |             |             |             |                |                |  |  |  |  |

| Note:    | Only P3.0–P3<br>Port pin on C8                                                                                                                                                                                                                                                                                                                                                                                        |             |             | •           | 051F310/2/4 | devices; On | ly P3.0 is ass | ociated with a |  |  |  |  |

### SFR Definition 13.16. P3MDIN: Port3 Input Mode

| R/W   | R/W                                                   | R/W | R/W | R/W | R/W          | R/W         | R/W           | Reset Value    |  |  |  |

|-------|-------------------------------------------------------|-----|-----|-----|--------------|-------------|---------------|----------------|--|--|--|

| -     | -                                                     | -   |     |     |              |             |               | 11111111       |  |  |  |

| Bit7  | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Addres<br>0xF4 |     |     |     |              |             |               |                |  |  |  |

|       |                                                       |     |     |     |              |             |               |                |  |  |  |

| Note: | Only P3.0–P3<br>Port pin on C8                        |     |     |     | 3051F310/2/4 | devices; Or | nly P3.0 is a | ssociated with |  |  |  |

### SFR Definition 13.17. P3MDOUT: Port3 Output Mode

| R              | 2/W<br>-    | R/W<br>-                                                                                                                                     | R/W<br>-                                   | R/W                          | R/W                       | R/W            | R/W           | R/W       | Reset Value<br>00000000   |  |  |  |  |  |  |  |

|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------|---------------------------|----------------|---------------|-----------|---------------------------|--|--|--|--|--|--|--|

| E              | Bit7        | Bit6                                                                                                                                         | Bit5                                       | Bit4                         | Bit3                      | Bit2           | Bit1          | Bit0      | Bit0 SFR Address:<br>0xA7 |  |  |  |  |  |  |  |

| Bits7<br>Bits4 | .–0: (<br>t | JNUSED. R<br>Output Confi<br>er P3MDIN<br>0: Correspor<br>1: Correspor                                                                       | guration Bi<br>is logic 0.<br>nding P3.n ( | ts for P3.4–<br>Output is op | P3.0 (respe<br>ben-drain. | ectively): igr | nored if corr | esponding | bit in regis-             |  |  |  |  |  |  |  |

| Note:          |             | Only P3.0–P3.4 are associated with Port pins on C8051F310/2/4 devices; Only P3.0 is associated with a Port pin on C8051F311/3/5/6/7 devices. |                                            |                              |                           |                |               |           |                           |  |  |  |  |  |  |  |

### Table 13.1. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified

| Parameters            | Conditions                                   | Min                   | Тур            | Max | Units |

|-----------------------|----------------------------------------------|-----------------------|----------------|-----|-------|

|                       | I <sub>OH</sub> = −3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7 | —              |     |       |

| Output High Voltage   | $I_{OH} = -10 \ \mu A$ , Port I/O push-pull  | V <sub>DD</sub> – 0.1 | —              | —   | V     |

|                       | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                     | $V_{DD} - 0.8$ | —   |       |

|                       | I <sub>OL</sub> = 8.5 mA                     |                       | —              | 0.6 |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 μA                      | —                     | —              | 0.1 | V     |

|                       | I <sub>OL</sub> = 25 mA                      | —                     | 1.0            | _   |       |

| Input High Voltage    |                                              | 2.0                   | —              | _   | V     |

| Input Low Voltage     |                                              |                       | —              | 0.8 | V     |

|                       | Weak Pullup Off                              |                       | —              | ±1  |       |

| Input Leakage Current | Weak Pullup On, V <sub>IN</sub> = 0 V        | —                     | 25             | 40  | μA    |

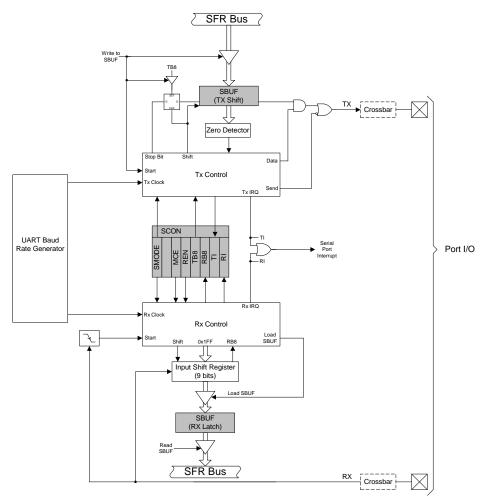

### 15. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in **Section "15.1. Enhanced Baud Rate Generation" on page 164**). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

|                              | Frequency: 11.0592 MHz       |                      |                                  |                       |                                     |      |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |

|                              | 230400                       | 0.00%                | 48                               | SYSCLK                | XX                                  | 1    | 0xE8                             |

|                              | 115200                       | 0.00%                | 96                               | SYSCLK                | XX                                  | 1    | 0xD0                             |

|                              | 57600                        | 0.00%                | 192                              | SYSCLK                | XX                                  | 1    | 0xA0                             |

| from<br>Osc.                 | 28800                        | 0.00%                | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |

| $\sim$                       | 14400                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                  | 0    | 0xE0                             |

| SYSCLK<br>External           | 9600                         | 0.00%                | 1152                             | SYSCLK / 12           | 00                                  | 0    | 0xD0                             |

|                              | 2400                         | 0.00%                | 4608                             | SYSCLK / 12           | 00                                  | 0    | 0x40                             |

|                              | 1200                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                  | 0    | 0xA0                             |

|                              | 230400                       | 0.00%                | 48                               | EXTCLK / 8            | 11                                  | 0    | 0xFD                             |

| SYSCLK from<br>Internal Osc. | 115200                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                  | 0    | 0xFA                             |

|                              | 57600                        | 0.00%                | 192                              | EXTCLK / 8            | 11                                  | 0    | 0xF4                             |

|                              | 28800                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |

|                              | 14400                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                  | 0    | 0xD0                             |

|                              | 9600                         | 0.00%                | 1152                             | EXTCLK / 8            | 11                                  | 0    | 0xB8                             |

# Table 15.5. Timer Settings for Standard Baud RatesUsing an External 11.0592 MHz Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

| Table 15.6. Timer Settings for Standard Baud Rates |

|----------------------------------------------------|

| Using an External 3.6864 MHz Oscillator            |

|                              | Frequency: 3.6864 MHz        |                        |                                  |                       |                                     |      |                                  |

|------------------------------|------------------------------|------------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud<br>Rate%<br>Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                  | 16                               | SYSCLK                | XX                                  | 1    | 0xF8                             |

|                              | 115200                       | 0.00%                  | 32                               | SYSCLK                | XX                                  | 1    | 0xF0                             |

|                              | 57600                        | 0.00%                  | 64                               | SYSCLK                | XX                                  | 1    | 0xE0                             |

| from<br>Osc.                 | 28800                        | 0.00%                  | 128                              | SYSCLK                | XX                                  | 1    | 0xC0                             |

|                              | 14400                        | 0.00%                  | 256                              | SYSCLK                | XX                                  | 1    | 0x80                             |

| SYSCLK<br>External (         | 9600                         | 0.00%                  | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |

|                              | 2400                         | 0.00%                  | 1536                             | SYSCLK / 12           | 00                                  | 0    | 0xC0                             |

|                              | 1200                         | 0.00%                  | 3072                             | SYSCLK / 12           | 00                                  | 0    | 0x80                             |

| SYSCLK from<br>Internal Osc. | 230400                       | 0.00%                  | 16                               | EXTCLK/8              | 11                                  | 0    | 0xFF                             |

|                              | 115200                       | 0.00%                  | 32                               | EXTCLK / 8            | 11                                  | 0    | 0xFE                             |

|                              | 57600                        | 0.00%                  | 64                               | EXTCLK / 8            | 11                                  | 0    | 0xFC                             |

|                              | 28800                        | 0.00%                  | 128                              | EXTCLK / 8            | 11                                  | 0    | 0xF8                             |

|                              | 14400                        | 0.00%                  | 256                              | EXTCLK / 8            | 11                                  | 0    | 0xF0                             |

|                              | 9600                         | 0.00%                  | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in **Section 17.1**.

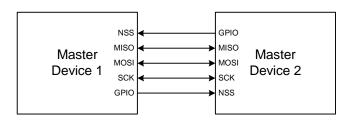

Figure 16.2. Multiple-Master Mode Connection Diagram

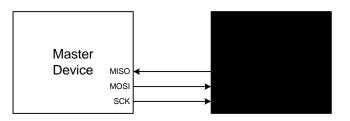

Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram

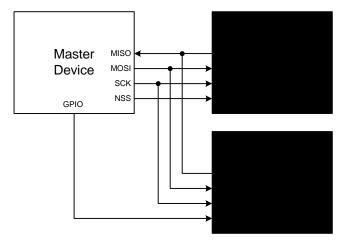

Figure 16.4. 4-Wire Single Master and Slave Mode Connection Diagram

#### 17.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

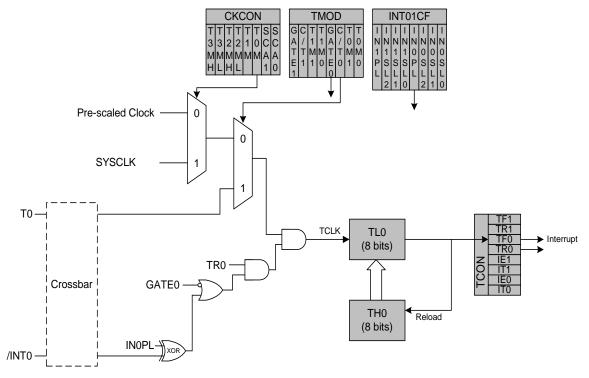

#### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see **Section "8.3.2. External Interrupts" on page 95** for details on the external input signals /INT0 and /INT1).

Figure 17.2. T0 Mode 2 Block Diagram

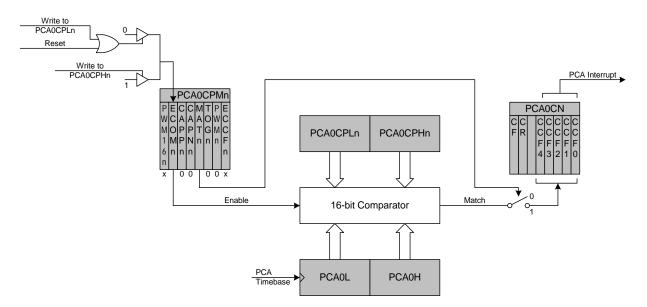

#### 18.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 18.5. PCA Software Timer Mode Diagram

### **19. Revision Specific Behavior**

This chapter contains behavioral differences between C8051F310/1 "REV A" and "REV B" or later devices. These differences do not affect the functionality or performance of most systems and are described below.

#### **19.1.** Revision Identification

The Lot ID Code on the top side of the device package can be used for decoding device revision information. On C8051F310 devices, the revision letter is the second-to-last letter of the Lot ID Code. On C8051F311 devices, the revision letter is the last letter of the Lot ID Code. Figure 19.1 shows how to find the Lot ID Code on the top side of the device package.

```

C8051F310 Package Marking

C8051F310

T2ABGFAC

^ indicates REV A

0227 EP

```

| C8051F311 Package Marking |                 |  |

|---------------------------|-----------------|--|

| CYG                       |                 |  |

| F311                      |                 |  |

| ABGF <b>A</b>             | indicates REV A |  |

### Figure 19.1. Reading Package Marking

#### 19.2. Reset Behavior

The reset behavior of C8051F310/1 "REV A" devices is different than "REV B" and later devices. The differences affect the state of the RST pin during a V<sub>DD</sub> Monitor reset and GPIO pins during any device reset.

#### 19.2.1. Weak Pullups on GPIO Pins

On "REV A" devices, GPIO pins are tri-stated with weak pullups **disabled** during the assertion phase of any reset. The pullups are enabled immediately following reset de-assertion.

On "REV B" and later devices, GPIO pins are tri-stated with weak pullups **enabled** during and after the assertion phase of any reset.

#### 19.2.2. $V_{DD}$ Monitor and the RST Pin

On "REV A" devices, a  $V_{DD}$  Monitor reset does not affect the state of the  $\overline{RST}$  pin.

On "REV B" and later devices, a  $V_{DD}$  Monitor reset will pull the  $\overline{RST}$  pin low for the duration of the brownout condition.