Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 15                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c717-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |

|-------|---------------------------------------------|

|       | and digit borrow bit, respectively, in sub- |

|       | traction. See the SUBLW and SUBWF           |

|       | instructions for examples.                  |

### REGISTER 2-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                          | R/W-0                              | R/W-0        | R-1           | R-1          | R/W-x        | R/W-x          | R/W-x       |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|---------------|--------------|--------------|----------------|-------------|--|--|

|         | IRP                                                                                                                                                                                                                                            | RP1                                | RP0          | TO            | PD           | Z            | DC             | С           |  |  |

|         | bit 7                                                                                                                                                                                                                                          |                                    |              |               |              |              |                | bit 0       |  |  |

|         |                                                                                                                                                                                                                                                |                                    |              |               |              |              |                |             |  |  |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)                                                                                                                                                                                   |                                    |              |               |              |              |                |             |  |  |

|         | 1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                       |                                    |              |               |              |              |                |             |  |  |

| bit 6-5 |                                                                                                                                                                                                                                                | Register Ban                       |              | s (used for o | lirect addre | ssing)       |                |             |  |  |

|         |                                                                                                                                                                                                                                                | 3 (180h - 1F<br>2 (100h - 17       |              |               |              |              |                |             |  |  |

|         |                                                                                                                                                                                                                                                | 1 (80h - FFh                       |              |               |              |              |                |             |  |  |

|         | 00 <b>= Bank</b>                                                                                                                                                                                                                               | 0 (00h - 7Fh                       | )            |               |              |              |                |             |  |  |

|         |                                                                                                                                                                                                                                                | is 128 bytes                       | i            |               |              |              |                |             |  |  |

| bit 4   | TO: Time-c                                                                                                                                                                                                                                     |                                    |              | tion of at t  |              | ion          |                |             |  |  |

|         | -                                                                                                                                                                                                                                              | ower-up, CLI                       |              |               |              | ION          |                |             |  |  |

| bit 3   | PD: Power                                                                                                                                                                                                                                      | -down bit                          |              |               |              |              |                |             |  |  |

|         |                                                                                                                                                                                                                                                | ower-up or b                       |              |               | n            |              |                |             |  |  |

|         | -                                                                                                                                                                                                                                              | cution of the                      | SLEEP inst   | ruction       |              |              |                |             |  |  |

| bit 2   | Z: Zero bit                                                                                                                                                                                                                                    |                                    | h            |               |              |              |                |             |  |  |

|         |                                                                                                                                                                                                                                                | sult of an arit<br>sult of an arit |              |               |              | 0            |                |             |  |  |

| bit 1   | <ul> <li>0 = The result of an arithmetic or logic operation is not zero</li> <li>DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)</li> </ul>                                         |                                    |              |               |              |              | the polarity   |             |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>                                                                                       |                                    |              |               |              |              |                |             |  |  |

| bit 0   | C: Carry/bo                                                                                                                                                                                                                                    | orrow bit (AD                      | DWF, ADDLW   | , SUBLW, SU   | JBWF instru  | ictions)     |                |             |  |  |

|         | •                                                                                                                                                                                                                                              | -out from the                      | •            |               |              |              |                |             |  |  |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                          |                                    |              |               |              |              |                |             |  |  |

|         | Note:                                                                                                                                                                                                                                          | For borrow.                        | the polarity | is reversed.  | A subtract   | ion is execu | ted bv addin   | a the two's |  |  |

|         | Note: For borrow, the polarity is reversed. A subtraction is executed by adding the two' complement of the second operand. For rotate (RRF, RLF) instructions, this bit i loaded with either the high or low order bit of the source register. |                                    |              |               |              |              |                |             |  |  |

|         | I                                                                                                                                                                                                                                              |                                    |              |               |              | e source reg |                |             |  |  |

|         | Legend:                                                                                                                                                                                                                                        |                                    |              |               |              |              |                |             |  |  |

|         | R = Reada                                                                                                                                                                                                                                      | ble bit                            | W = W        | ritable bit   | U = Unir     | nplemented   | bit, read as ' | 0'          |  |  |

|         | - n = Value                                                                                                                                                                                                                                    | at POR                             | '1' = Bi     | t is set      | '0' = Bit    | is cleared   | x = Bit is u   | nknown      |  |  |

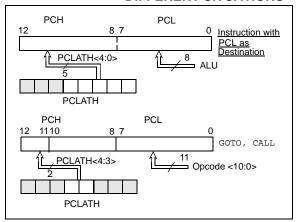

# 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register occur through the PCLATH register.

### 2.3.1 PROGRAM MEMORY PAGING

PIC16C717/770/771 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. A return instruction pops a PC address off the stack onto the PC register. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

# 2.4 Stack

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

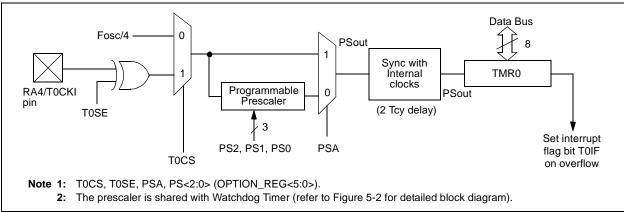

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 5-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

# 5.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

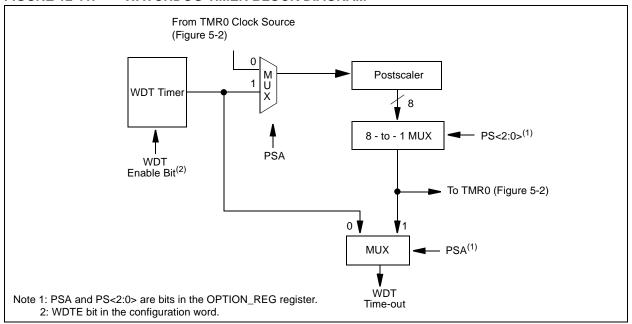

## 5.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 5-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS<2:0> bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

## FIGURE 5-1: TIMER0 BLOCK DIAGRAM

### 8.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only an ECCP interrupt is generated (if enabled).

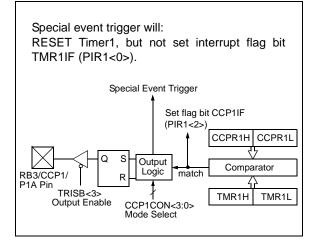

### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of ECCP resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of ECCP module will also start an A/D conversion if the A/D module is enabled.

**Note:** The special event trigger will not set the interrupt flag bit TMR1IF (PIR1<0>).

### FIGURE 8-2:

### COMPARE MODE OPERATION BLOCK DIAGRAM

# TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Name    | Bit 7                                                                       | Bit 6                                                                                          | Bit 5       | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0      | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------|-------------|---------|--------|--------|------------|-------------------------|---------------------------------|

| INTCON  | GIE                                                                         | PEIE                                                                                           | TOIE        | INTE        | RBIE    | T0IF   | INTF   | RBIF       | 0000 000x               | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup>                                                        | ADIF                                                                                           | RCIF        | TXIF        | SSPIF   | CCP1IF | TMR2IF | TMR1IF     | 0000 0000               | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup>                                                        | ADIE                                                                                           | RCIE        | TXIE        | SSPIE   | CCP1IE | TMR2IE | TMR1IE     | 0000 0000               | 0000 0000                       |

| TRISB   | PORTB Data Direction Register                                               |                                                                                                |             |             |         |        |        | 1111 1111  | 1111 1111               |                                 |

| TMR1L   | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                                                                                                |             |             |         |        |        |            | XXXX XXXX               | uuuu uuuu                       |

| TMR1H   | Holding regi                                                                | Holding register for the Most Significant Byte of the 16-bit TMR1register xxxx xxxx uuuuu uuuu |             |             |         |        |        | uuuu uuuu  |                         |                                 |

| T1CON   | -                                                                           | —                                                                                              | T1CKPS<br>1 | T1CKP<br>S0 | T1OSCEN | T1SYNC | TMR1CS | TMR1O<br>N | 00 0000                 | uu uuuu                         |

| CCPR1L  | Capture/Compare/PWM register1 (LSB)                                         |                                                                                                |             |             |         |        |        | XXXX XXXX  | uuuu uuuu               |                                 |

| CCPR1H  | Capture/Compare/PWM register1 (MSB)                                         |                                                                                                |             |             |         |        |        |            | xxxx xxxx               | uuuu uuuu                       |

| CCP1CON | PWM1M1                                                                      | PWM1M0                                                                                         | DC1B1       | DC1B0       | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0     | 0000 0000               | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, RB3/CCP1/P1A pin is continuously active, and RB7/T1OSI/P1D pin is modulated. In the Reverse mode, RB6/T1OSO/T1CKI/P1C pin is continuously active, and RB5/SDO/P1B pin is modulated.

P1A, P1B, P1C and P1D outputs are multiplexed with PORTB<3> and PORTB<5:7> data latches. TRISB<3> and TRISB<5:7> bits must be cleared to make the P1A, P1B, P1C, and P1D pins output.

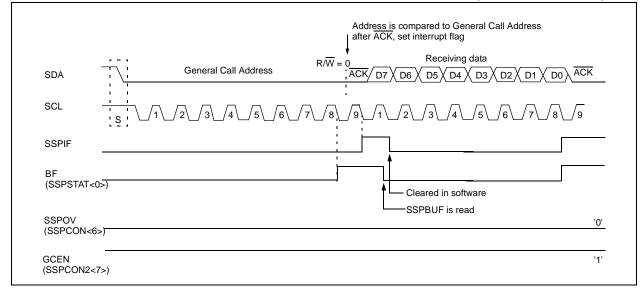

### 9.2.3 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is set (SSPCON2<7> is set). Following a START bit detect, eight bits are shifted into the SSPSR, and the address is compared against SSPADD. It is also compared to the general call address, fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

If the general call address is sampled with GCEN set and the slave configured in 10-bit Address mode, the second half of the address is not necessary. The UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 9-12).

### FIGURE 9-12: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7- OR 10-BIT MODE)

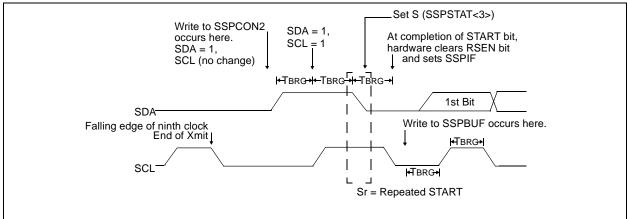

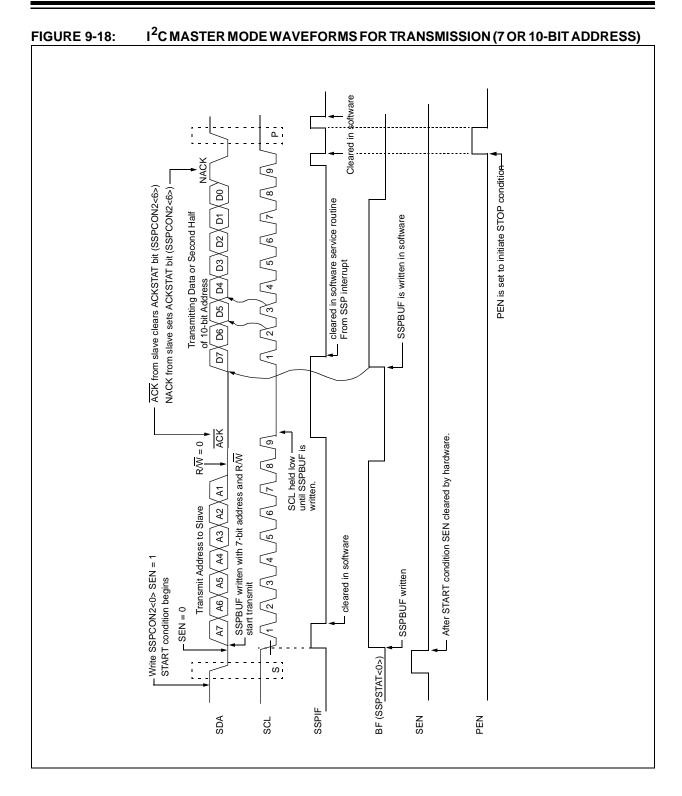

## 9.2.11 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is set high while the  $I^2C$  module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG period. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG period while SCL is high. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. Following this, the baud rate generator is reloaded with the contents of SSPAD<6:0> and begins counting. When the BRG times out a third time, the RSEN bit in the SSPCON2 register is automatically cleared and SCL is pulled low. The SSPIF flag is set, which indicates the Restart sequence is complete.

- Note 1: If RSEN is set while another event is in progress, it will not take effect. Queuing of events is not allowed.

- 2: A bus collision during the Repeated START condition occurs if either of the following is true:

- a) SDA is sampled low when SCL goes from low to high.

- b) SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit transition to true, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then perform one of the following:

- Transmit an additional eight bits of address (if the user transmitted the first half of a 10-bit address with  $R/\overline{W} = 0$ ),

- Transmit eight bits of data (if the user transmitted a 7-bit address with R/W = 0), or

- Receive eight bits of data (if the user transmitted either the first half of a 10-bit address or a 7-bit address with R/W = 1).

### 9.2.11.1 WCOL STATUS FLAG

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated START condition is complete.

## FIGURE 9-17: REPEAT START CONDITION WAVEFORM

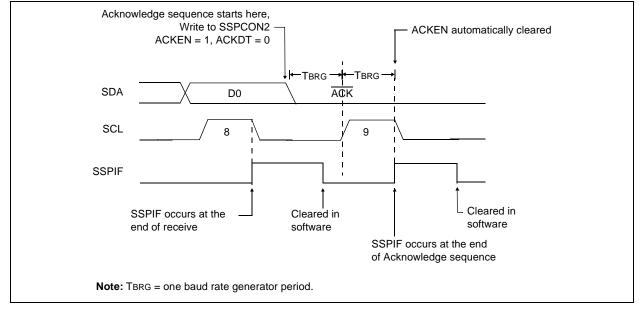

# 9.2.14 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit ACKDT (SSPCON2<5>) is presented on the SDA pin. If the user wishes to generate an Acknowledge (ACK), then the ACKDT bit should be cleared. Otherwise, the user should set the ACKDT bit (NACK) before starting an Acknowledge sequence. The baud rate generator is then loaded from SSPADD<6:0> and counts for one rollover period (TBRG). The SCL pin is then de-asserted (pulled high). When the SCL pin is sampled high (clock

arbitration), the baud rate generator is reloaded and counts for another TBRG. At the completion of the TBRG period, the following events occur (see Figure 9-20):

- The SCL pin is pulled low.

- The ACKEN bit is automatically cleared.

- The baud rate generator is turned off.

- The MSSP module goes into IDLE mode.

### 9.2.14.1 WCOL STATUS FLAG

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

### FIGURE 9-20: ACKNOWLEDGE SEQUENCE WAVEFORM

### 11.3 Selecting the A/D Conversion Clock

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. If neither the internal VRH nor VRL are used for the A/D converter, the four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- A/D RC oscillator

If the VRH or VRL are used for the A/D converter reference, then the TAD requirement is automatically increased by a factor of 8.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

| A/D Reference<br>Source           | A/D Clock Source (TAD) |           | Device Frequency            |                             |                             |                               |  |

|-----------------------------------|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--|

|                                   | Operation              | ADCS<1:0> | 20 MHz                      | 5 MHz                       | 4 MHz                       | 1.25 MHz                      |  |

|                                   | 2 Tosc                 | 00        | 100 ns <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.6 μs                        |  |

| External VREF or<br>Analog Supply | 8 Tosc                 | 01        | 400 ns <sup>(2)</sup>       | 1.6 μs                      | 2.0 μs                      | 6.4 μs                        |  |

| Analog Supply                     | 32 Tosc                | 10        | 1.6 μs                      | 6.4 μs <sup>(3)</sup>       | 8.0 μs <sup>(3)</sup>       | 25.6 μs <sup>(3)</sup>        |  |

|                                   | A/D RC                 | 11        | 2 - 6 μs <sup>(1,4)</sup>     |  |

| Internal VRH or                   | 16 Tosc                | 00        | 800 ns <sup>(2)</sup>       | 3.2 μs <sup>(2)</sup>       | 4 μs <sup>(2)</sup>         | 12.8 μs                       |  |

| VRL                               | 64 Tosc                | 01        | 3.2 μs <sup>(2)</sup>       | 12.8 μs                     | 16 μs                       | 51.2 μs <b><sup>(3)</sup></b> |  |

|                                   | 256 Tosc               | 10        | 12.8 μs                     | 51.2 μs <sup>(3)</sup>      | 64 μs <sup>(3)</sup>        | 204.8 μs <sup>(3)</sup>       |  |

|                                   | A/D RC                 | 11        | 16 - 48 μs <sup>(4,5)</sup>   |  |

## TABLE 11-1: TAD vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

5: A/D RC clock source has a typical TAD time of 32  $\mu$ s for VDD > 3.0V.

# EXAMPLE 11-3: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

| TACQ =                                                                     | Amplifier Settling Time                  |  |  |

|----------------------------------------------------------------------------|------------------------------------------|--|--|

|                                                                            | + Holding Capacitor Charging Time        |  |  |

|                                                                            | +Temperature offset †                    |  |  |

| TACQ =                                                                     | 5 μs                                     |  |  |

|                                                                            | + Tc                                     |  |  |

|                                                                            | + [(Temp - 25°C)(0.05 μs/°C)] †          |  |  |

| Tc= Ho                                                                     | olding Capacitor Charging Time           |  |  |

| Tc = (C                                                                    | HOLD) (RIC + RSS + RS) In (1/16384)      |  |  |

| Tc = -2                                                                    | 5 pF (1 kΩ +10 kΩ + 2.5 kΩ) ln (1/16384) |  |  |

| Tc = -2                                                                    | 5 pF (13.5 kΩ) In (1/16384)              |  |  |

| Tc = -0.                                                                   | .338 (-9.704)µs                          |  |  |

| Tc = 3.3                                                                   | 3 μs                                     |  |  |

| TACQ =                                                                     | 5 μs                                     |  |  |

|                                                                            | + 3.3 μs                                 |  |  |

|                                                                            | + [(50°C - 25°C)(0.05 μs / °C)]          |  |  |

| TACQ =                                                                     | 8.3 μs + 1.25 μs                         |  |  |

| TACQ =                                                                     | 9.55 μs                                  |  |  |

| † The temperature coefficient is only required for<br>temperatures > 25°C. |                                          |  |  |

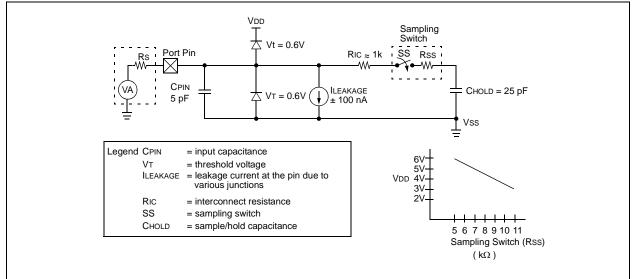

## FIGURE 11-5: ANALOG INPUT MODEL

# 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This oscillator is independent from the processor clock. If enabled, the WDT will run even if the main clock of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to

wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{TO}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by programming the configuration bit WDTE to '0' (Section 12.1).

WDT time-out period values may be found in Table 15-4. Values for the WDT prescaler may be assigned using the OPTION\_REG register.

**Note:** The SLEEP instruction clears the WDT and the postscaler, if assigned to the WDT, restarting the WDT period.

## FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h    | Config. bits <sup>(1)</sup> | _     | BODEN  | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG                  | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for the full description of the configuration word bits.

| IORLW            | Inclusive OR Literal with W                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                    |

| Operands:        | $0 \leq k \leq 255$                                                                                                         |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                                |

| Status Affected: | Z                                                                                                                           |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| MOVLW            | Move Literal to W                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                              |

| Status Affected: | None                                                                                             |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                             |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |

| Status Affected: | Z                                                                                                                                                                       |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in regis-<br>ter 'f'. |

| MOVWF            | Move W to f                                     |  |  |  |  |

|------------------|-------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVWF f                                 |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                             |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                           |  |  |  |  |

| Status Affected: | None                                            |  |  |  |  |

| Description:     | Move data from W register to reg-<br>ister 'f'. |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                        |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself. d<br>= 1 is useful to test a file register<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

NOTES:

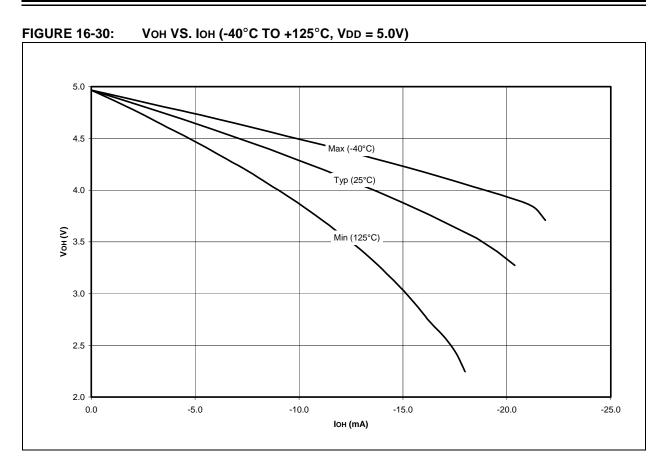

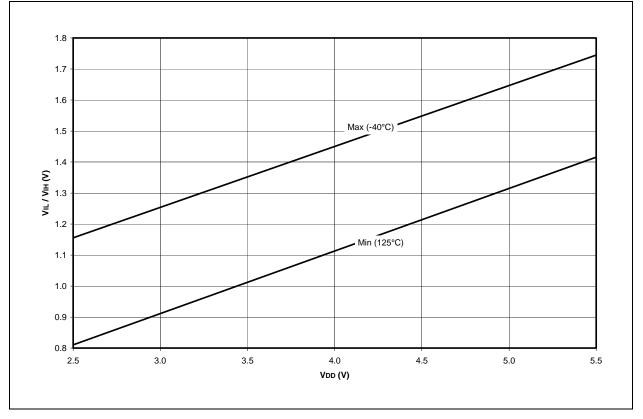

# 15.2 DC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

|                    |           |                                                                                                     |                  |         | rature (   | °C ≤     | s (unless otherwise stated)<br>TA $\leq$ +70°C for commercial          |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------|------------------|---------|------------|----------|------------------------------------------------------------------------|

| DC CHARACTERISTICS |           | $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                  |         |            |          |                                                                        |

|                    |           |                                                                                                     | Operating        | voltage |            |          | described in Section 15.1 and                                          |

|                    |           |                                                                                                     | Section 15       |         |            | .ge ae   |                                                                        |

| Param.             | Sym       | Characteristic                                                                                      | Min              | Typ†    | Max        | Units    | Conditions                                                             |

| No.                |           |                                                                                                     |                  |         |            |          |                                                                        |

|                    |           | Input Low Voltage                                                                                   |                  |         |            |          |                                                                        |

|                    | VIL       | I/O ports                                                                                           |                  |         |            |          |                                                                        |

| D030               |           | with TTL buffer                                                                                     | Vss              | —       | 0.15Vdd    | V        | For entire VDD range                                                   |

| D030A              |           |                                                                                                     | Vss              |         | 0.8V       | V        | $4.5V \le VDD \le 5.5V$                                                |

| D031               |           | with Schmitt Trigger buffer                                                                         | Vss              |         | 0.2Vdd     | V        | For entire VDD range                                                   |

| D032               |           | MCLR                                                                                                | Vss              |         | 0.2Vdd     | V        |                                                                        |

| D033               |           | OSC1 (in XT, HS, LP and EC)                                                                         | Vss              | —       | 0.3Vdd     | V        |                                                                        |

|                    |           | Input High Voltage                                                                                  |                  |         |            |          |                                                                        |

|                    | Vih       | I/O ports                                                                                           |                  |         |            |          |                                                                        |

|                    |           | with TTL buffer                                                                                     |                  |         |            |          |                                                                        |

| D040               |           |                                                                                                     | 2.0              | —       | VDD        | -        | $4.5V \le VDD \le 5.5V$                                                |

| D040A              |           |                                                                                                     | (0.25VDD         | —       | Vdd        | V        | For entire VDD range                                                   |

| D044               |           | with Coheritt Trigger huffer                                                                        | + 0.8V)          |         |            |          |                                                                        |

| D041<br>D042       |           | with Schmitt Trigger buffer                                                                         | 0.8Vdd<br>0.8Vdd |         | Vdd<br>Vdd | V<br>V   | For entire VDD range                                                   |

| D042<br>D042A      |           | OSC1 (XT, HS, LP and EC)                                                                            | 0.8VDD<br>0.7VDD |         | VDD<br>VDD | V        |                                                                        |

| D042A              | ססנוס     | PORTB weak pull-up current                                                                          | 50               | 250     | 400        | μA       | VDD = 5V, VPIN = VSS                                                   |

| 2010               |           | per pin                                                                                             | 00               | 200     | -00        | μ        |                                                                        |

|                    |           | Input Leakage Current <sup>(1,2)</sup>                                                              |                  |         |            |          |                                                                        |

| D060               | lı∟       | I/O ports (with digital functions)                                                                  |                  | _       | ±1         | μA       | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-impedance                        |

| D060A              | lıL       | I/O ports (with analog func-                                                                        |                  | _       | ±100       | nA       | $Vss \leq VPIN \leq VDD$ , Pin at hi-impedance                         |

|                    |           | tions)                                                                                              |                  |         |            |          |                                                                        |

| D061               |           | RA5/MCLR/VPP                                                                                        | —                | _       | ±5         | μA       | $Vss \leq VPIN \leq VDD$                                               |

| D063               |           | OSC1                                                                                                | _                | _       | ±5         | μA       | Vss $\leq$ VPIN $\leq$ VDD, XT, HS, LP and EC                          |

|                    |           |                                                                                                     |                  |         |            |          | osc configuration                                                      |

|                    |           | Output Low Voltage                                                                                  |                  |         |            |          |                                                                        |

| D080               | Vol       | •                                                                                                   | —                | —       | 0.6        | V        | IOL = 8.5 mA, VDD = 4.5V                                               |

|                    |           | Output High Voltage                                                                                 |                  |         |            |          |                                                                        |

| D090               |           |                                                                                                     | Vdd - 0.7        | _       |            | V        | ЮН = -3.0 mA, VDD = 4.5V                                               |

| D150*              | Vod       | Open Drain High Voltage                                                                             | —                | —       | 10.5       | V        | RA4 pin                                                                |

|                    |           | Capacitive Loading Specs on                                                                         |                  |         |            |          |                                                                        |

| D100               | 000       | Output Pins*                                                                                        |                  |         | 45         |          | In VT LIC and LD reader where the                                      |

| D100               | COS<br>C2 | OSC2 pin                                                                                            | _                | —       | 15         | pF       | In XT, HS and LP modes when exter-<br>nal clock is used to drive OSC1. |

| D101               |           | All I/O pins and OSC2 (in RC                                                                        |                  |         | 50         | pF       |                                                                        |

| D101<br>D102       | Сю        | mode) SCL, SDA in $I^2C$ mode                                                                       |                  |         | 400        | рг<br>pF |                                                                        |

| 2.02               |           |                                                                                                     | _                | _       |            |          |                                                                        |

|                    |           | VRH pin<br>VRL pin                                                                                  |                  | _       | 200<br>200 | pF<br>pF | VRH output enabled<br>VRL output enabled                               |

| *                  |           | e parameters are characterized                                                                      |                  |         | 200        | рг       |                                                                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

### 15.4.5 A/D CONVERTER MODULE

### TABLE 15-11: PIC16C770/771 AND PIC16LC770/771 A/D CONVERTER CHARACTERISTICS:

| Param.<br>No. | Sym   | Characteristic                                         | Min   | Тур†   | Max          | Units | Conditions                                                                                                                                  |

|---------------|-------|--------------------------------------------------------|-------|--------|--------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| A01           | NR    | Resolution                                             | _     |        | 12 bits      | bit   | Min. resolution for A/D is 1 mV,<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- $\leq$ VAIN $\leq$ VREF+                          |

| A03           | EIL   | Integral error                                         | —     | _      | ±2           | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>$VREF- \le VAIN \le VREF+$                                                                  |

| A04           | Edl   | Differential error                                     | _     | _      | +2<br>-1     | LSb   | No missing codes to 12 bits<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- $\leq$ VAIN $\leq$ VREF+                               |

| A06           | EOFF  | Offset error                                           | —     | _      | ±2           | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>$VREF- \le VAIN \le VREF+$                                                                  |

| A07           | Egn   | Gain Error                                             | _     | _      | ±2           | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>$VREF- \le VAIN \le VREF+$                                                                  |

| A10           | —     | Monotonicity                                           | _     | Note 3 | —            | _     | $AVSS \leq VAIN \leq VREF+$                                                                                                                 |

| A20*          | Vref  | Reference voltage<br>(VREF+ - VREF-)                   | 4.096 | _      | VDD<br>+0.3V | V     | Absolute minimum electrical spec to ensure 12-bit accuracy.                                                                                 |

| A21*          | VREF+ | Reference V High<br>(AVDD or VREF+)                    | VREF- | _      | AVdd         | V     | Min. resolution for A/D is 1 mV                                                                                                             |

| A22*          | VREF- | Reference V Low<br>(Avss or VREF-)                     | AVss  | _      | VREF+        | V     | Min. resolution for A/D is 1 mV                                                                                                             |

| A25*          | Vain  | Analog input volt-<br>age                              | Vrefl | _      | Vrefh        | V     |                                                                                                                                             |

| A30*          | Zain  | Recommended<br>impedance of ana-<br>log voltage source |       |        | 2.5          | kΩ    |                                                                                                                                             |

| A50*          | IREF  | VREF input current<br>(Note 2)                         |       | _      | 10           | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD to<br>VAIN.<br>To charge CHOLD see Section 11.0.<br>During A/D conversion cycle. |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF input current is from External VREF+, or VREF-, or AVSS, or AVDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

© 1999-2013 Microchip Technology Inc.

NOTES:

| Prescaler, Timer257                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Select (T2CKPS Bits)51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PRO MATE II Universal Device Programmer143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Program Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PCL Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PCLATH Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Interrupt Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Program Memory Map9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| READ (PMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Reset Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Program Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |