# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

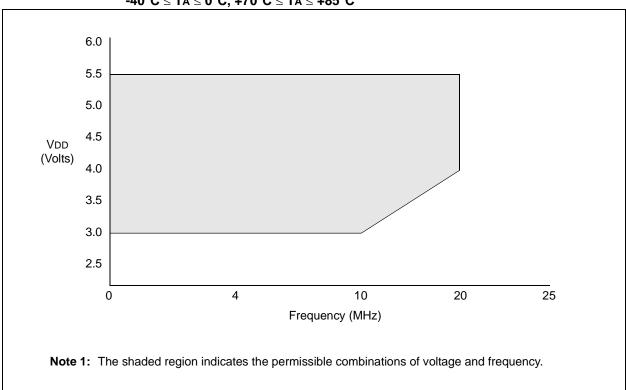

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c717-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0 Device Overview                                  | 5   |

|------------------------------------------------------|-----|

| 2.0 Memory Organization                              | 9   |

| 3.0 I/O Ports                                        |     |

| 4.0 Program Memory Read (PMR)                        | 41  |

| 5.0 Timer0 Module                                    |     |

| 6.0 Timer1 Module                                    |     |

| 7.0 Timer2 Module                                    |     |

| 8.0 Enhanced Capture/Compare/PWM (ECCP) Modules      | 53  |

| 9.0 Master Synchronous Serial Port (MSSP) Module     | 65  |

| 10.0 Voltage Reference Module and Low-voltage Detect | 101 |

| 11.0 Analog-to-Digital Converter (A/D) Module        | 105 |

| 12.0 Special Features of the CPU                     | 117 |

| 13.0 Instruction Set Summary                         | 133 |

| 14.0 Development Support                             |     |

| 15.0 Electrical Characteristics                      | 147 |

| 16.0 DC and AC Characteristics Graphs and Tables     | 179 |

| 17.0 Packaging Information                           | 197 |

| APPENDIX A: Revision History                         | 207 |

| APPENDIX B: Device Differences                       | 208 |

| Index                                                | 209 |

| On-Line Support                                      | 215 |

| Reader Response                                      |     |

| PIC16C717/770/771 Product Identification System      | 217 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the SSP bus collision and low voltage detect interrupts.

## REGISTER 2-6: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (PIE2: 8Dh)

|         | R/W-0                      | U-0            | U-0           | U-0           | R/W-0        | U-0       | U-0          | U-0    |

|---------|----------------------------|----------------|---------------|---------------|--------------|-----------|--------------|--------|

|         | LVDIE                      |                | —             | —             | BCLIE        | _         | —            |        |

|         | bit 7                      |                |               |               |              |           |              | bit 0  |

|         |                            |                |               |               |              |           |              |        |

| bit 7   | LVDIE: Lov                 | v Voltage De   | etect Interru | ot Enable bit |              |           |              |        |

|         | 1 = LVD Int<br>0 = LVD Int | •              |               |               |              |           |              |        |

|         |                            | •              |               |               |              |           |              |        |

| bit 6-4 | Unimpleme                  | ented: Read    | d as '0'      |               |              |           |              |        |

| bit 3   | BCLIE: Bus                 | s Collision Ir | nterrupt Ena  | ble bit       |              |           |              |        |

|         | 1 = Bus Co                 | llision interr | upt is enable | ed            |              |           |              |        |

|         | 0 = Bus Co                 | llision interr | upt is disabl | ed            |              |           |              |        |

| bit 2-0 | Unimpleme                  | ented: Read    | d as '0'      |               |              |           |              |        |

|         |                            |                |               |               |              |           |              |        |

|         | Legend:                    |                |               |               |              |           |              |        |

|         | R = Readal                 | ole bit        | W = W         | ritable bit   | U = Unim     | plemented | bit, read as | 0'     |

|         | - n = Value                | at POR         | '1' = Bi      | t is set      | '0' = Bit is | s cleared | x = Bit is u | nknown |

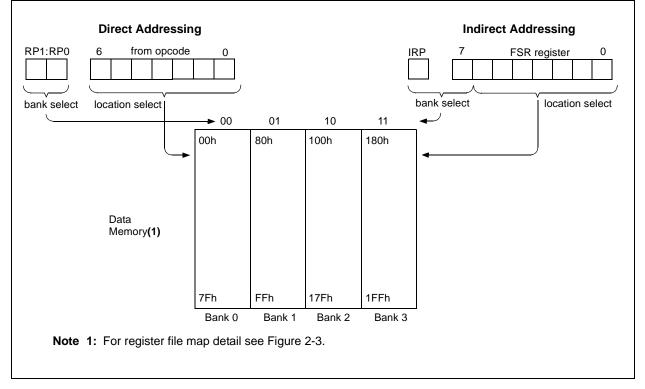

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: How to Clear RAM Using Indirect Addressing

|        | movlw | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | movwf | FSR   | ; to RAM             |

| NEXT   | clrf  | INDF  | ;clear INDF register |

|        | incf  | FSR   | ;inc pointer         |

|        | btfss | FSR,4 | ;all done?           |

|        | goto  | NEXT  | ;NO, clear next      |

| CONTIN | IUE   |       |                      |

|        | :     |       | ;YES, continue       |

|        |       |       |                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

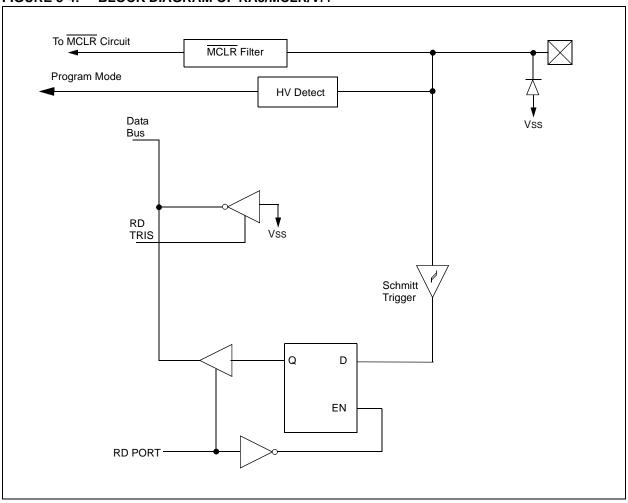

FIGURE 3-4: BLOCK DIAGRAM OF RA5/MCLR/VPP

| Name                | Function | Input<br>Type | Output<br>Type | Description                           |

|---------------------|----------|---------------|----------------|---------------------------------------|

|                     | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB0/AN4/INT         | AN4      | AN            |                | A/D input                             |

|                     | INT      | ST            |                | Interrupt input                       |

|                     | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB1/AN5/SS          | AN5      | AN            |                | A/D input                             |

|                     | SS       | ST            |                | SSP slave select input                |

|                     | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB2/SCK/SCL         | SCK      | ST            | CMOS           | Serial clock I/O for SPI              |

|                     | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C |

|                     | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB3/CCP1/P1A        | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output      |

|                     | P1A      |               | CMOS           | PWM P1A output                        |

|                     | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB4/SDI/SDA         | SDI      | ST            |                | Serial data in for SPI                |

|                     | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C  |

|                     | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB5/SDO/P1B         | SDO      |               | CMOS           | Serial data out for SPI               |

|                     | P1B      |               | CMOS           | PWM P1B output                        |

|                     | RB6      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

|                     | T1OSO    |               | XTAL           | Crystal/Resonator                     |

| RB6/T1OSO/T1CKI/P1C | T1CKI    | CMOS          |                | TMR1 clock input                      |

|                     | P1C      |               | CMOS           | PWM P1C output                        |

|                     | RB7      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB7/T1OSI/P1D       | T1OSI    | XTAL          |                | TMR1 crystal/resonator                |

|                     | P1D      |               | CMOS           | PWM P1D output                        |

TABLE 3-3: PORTB FUNCTIONS

**Note 1:** Bit programmable pull-ups.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                            | Bit 5     | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-----------|------------|-------|----------------------------------|-----------|--------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                              | RB5       | RB4    | RB3   | RB2   | RB1   | RB0   | xxxx xx11                | uuuu uull                       |

| 86h, 186h | TRISB      | PORTE | B Data Dire                      | ction Reg | jister |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                           | TOCS      | T0SE   | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

| 95h       | WPUB       | PORTE | 8 Weak Pul                       | I-up Cont | rol    |       |       |       |       | 1111 1111                | 1111 1111                       |

| 96h       | IOCB       | PORTE | ORTB Interrupt on Change Control |           |        |       |       |       |       | 1111 0000                | 1111 0000                       |

| 9Dh       | ANSEL      | _     | _                                | ANS5      | ANS4   | ANS3  | ANS2  | ANS1  | ANS0  | 11 1111                  | 11 1111                         |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

NOTES:

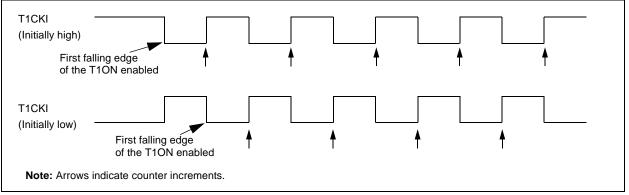

#### 6.1.1 TIMER1 COUNTER OPERATION

In this mode, Timer1 is being incremented via an external source. Increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

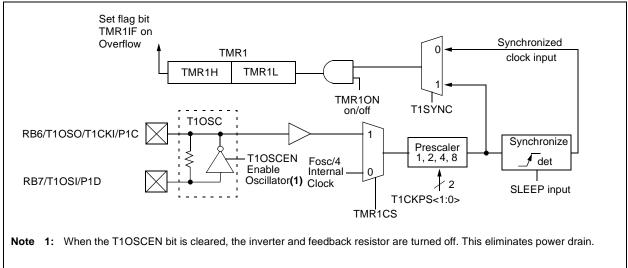

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

## 6.2 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | <b>;</b>                                                                                             | Freq                                                | C1            | C2            |  |  |  |

|----------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|---------------|--|--|--|

| LP       |                                                                                                      | 32 kHz                                              | 32 kHz 33 pF  |               |  |  |  |

|          |                                                                                                      | 100 kHz                                             | 15 pF         | 15 pF         |  |  |  |

|          |                                                                                                      | 200 kHz                                             | 15 pF         | 15 pF         |  |  |  |

| These    | va                                                                                                   | lues are for o                                      | design guida  | nce only.     |  |  |  |

| (        | Higher capacitance increases the stability<br>of oscillator but also increases the start-up<br>time. |                                                     |               |               |  |  |  |

|          | cha                                                                                                  | nce each reso<br>aracteristics, t<br>sonator/crysta | he user shoul | d consult the |  |  |  |

priate values of external components.

## 6.3 Timer1 Interrupt

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

## 6.4 Resetting Timer1 using a CCP Trigger Output

If the ECCP module is configured in Compare mode to generate a "special event trigger" (CCP1M<3:0> = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The spe | cial e | event | trigg | ers from tl | ne CC | P1  |

|-------|---------|--------|-------|-------|-------------|-------|-----|

|       | module  | will   | not   | set   | interrupt   | flag  | bit |

|       | TMR1IF  | (PIR   | 1<0>  | ).    |             |       |     |

Timer1 must be configured for either timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from ECCP, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7         | Bit 6                                                                      | Bit 5         | Bit 4           | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|---------------|----------------------------------------------------------------------------|---------------|-----------------|---------------|-------------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE           | PEIE                                                                       | TOIE          | INTE            | RBIE          | TOIF        | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | —             | ADIF                                                                       |               |                 | SSPIF         | CCP1IF      | TMR2IF | TMR1IF | -0 0000                  | -0 0000                         |

| 8Ch                   | PIE1   | —             | ADIE                                                                       |               |                 | SSPIE         | CCP1IE      | TMR2IE | TMR1IE | -0 0000                  | -0 0000                         |

| 0Eh                   | TMR1L  | Holding regis | ster for th                                                                | ne Least Sign | ificant Byte of | the 16-bit TM | R1 register |        |        | XXXX XXXX                | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding regis | Holding register for the Most Significant Byte of the 16-bit TMR1 register |               |                 |               |             |        |        | XXXX XXXX                | uuuu uuuu                       |

| 10h                   | T1CON  | _             | _                                                                          | T1CKPS1       | T1CKPS0         | T1OSCEN       | T1SYNC      | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

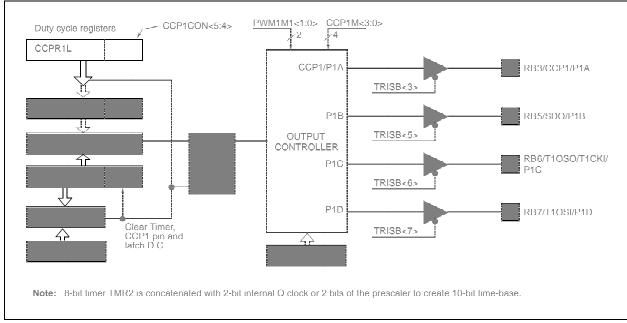

### 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the ECCP module produces up to a 10-bit resolution PWM output. Figure 8-3 shows the simplified PWM block diagram.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM PERIOD = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 PRESCALE VALUE)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 7.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output. In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, RB3/CCP1/P1A pin is continuously active, and RB7/T1OSI/P1D pin is modulated. In the Reverse mode, RB6/T1OSO/T1CKI/P1C pin is continuously active, and RB5/SDO/P1B pin is modulated.

P1A, P1B, P1C and P1D outputs are multiplexed with PORTB<3> and PORTB<5:7> data latches. TRISB<3> and TRISB<5:7> bits must be cleared to make the P1A, P1B, P1C, and P1D pins output.

## 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

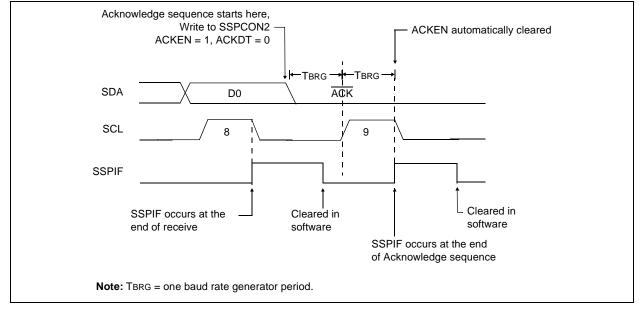

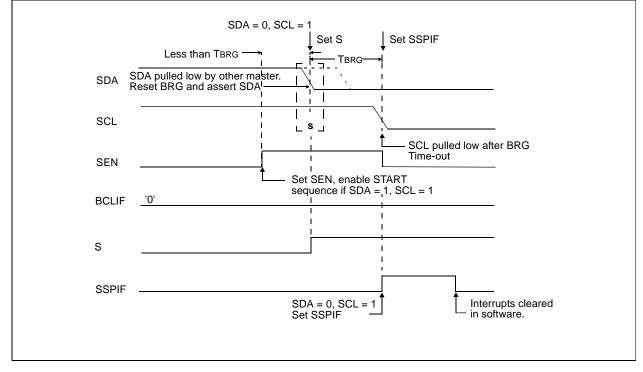

## 9.2.14 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit ACKDT (SSPCON2<5>) is presented on the SDA pin. If the user wishes to generate an Acknowledge (ACK), then the ACKDT bit should be cleared. Otherwise, the user should set the ACKDT bit (NACK) before starting an Acknowledge sequence. The baud rate generator is then loaded from SSPADD<6:0> and counts for one rollover period (TBRG). The SCL pin is then de-asserted (pulled high). When the SCL pin is sampled high (clock

arbitration), the baud rate generator is reloaded and counts for another TBRG. At the completion of the TBRG period, the following events occur (see Figure 9-20):

- The SCL pin is pulled low.

- The ACKEN bit is automatically cleared.

- The baud rate generator is turned off.

- The MSSP module goes into IDLE mode.

#### 9.2.14.1 WCOL STATUS FLAG

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-20: ACKNOWLEDGE SEQUENCE WAVEFORM

## REGISTER 11-1: A/D CONTROL REGISTER 0 (ADCON0: 1Fh).

|           | R/W-0                    | R/W-0                        | R/W-0         | R/W-0         | R/W-0       | R/W-0                          | R/W-0     | R/W-0       |

|-----------|--------------------------|------------------------------|---------------|---------------|-------------|--------------------------------|-----------|-------------|

|           | ADCS1                    | ADCS0                        | CHS2          | CHS1          | CHS0        | GO/DONE                        | CHS3      | ADON        |

|           | bit 7                    |                              |               |               |             |                                |           | bit 0       |

| bit 7-6   | ADCS<1:0                 | >: A/D Conv                  | version Cloc  | k Select bits | 6           |                                |           |             |

|           |                          | /RL and/or \                 | /RH are not   | used for A/   | D reference | e (VCFG<2:0>                   | = 000, 0  | 01, 011     |

|           | or 101):                 | 0                            |               |               |             |                                |           |             |

|           | 00 = Fosc/<br>01 = Fosc/ |                              |               |               |             |                                |           |             |

|           | 10 = Fosc/               | -                            |               |               |             |                                |           |             |

|           |                          | clock derive                 | d from a dec  | licated RC of | oscillator) |                                |           |             |

|           | If internal V            | 'RL and/or V                 | RH are used   | for A/D refe  | erence (VCI | FG<2:0>=01                     | 0, 100, 1 | 10 or 111): |

|           | 00 = Fosc/               |                              |               |               |             |                                |           |             |

|           | 01 = Fosc/               |                              |               |               |             |                                |           |             |

|           | 10 = Fosc/<br>11 = Frc/8 |                              |               |               |             |                                |           |             |

| bit 5-3,1 |                          | : Analog Ch                  | annel Selec   | t bits        |             |                                |           |             |

| <b>,</b>  |                          | annel 00 (AN                 |               |               |             |                                |           |             |

|           |                          | annel 01 (AN                 | ,             |               |             |                                |           |             |

|           |                          | annel 02 (AN                 | ,             |               |             |                                |           |             |

|           |                          | annel 03 (AN                 |               |               |             |                                |           |             |

|           |                          | annel 04 (AN                 | ,             |               |             |                                |           |             |

|           |                          | annel 05 (AN<br>erved, do no | ,             |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no<br>erved, do no |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

|           |                          | erved, do no                 |               |               |             |                                |           |             |

| bit 2     | GO/DONE:                 | A/D Conve                    | rsion Status  | bit           |             |                                |           |             |

|           | This bit                 | is automati                  | cally cleared | l by hardwa   |             | s an A/D conv<br>e A/D convers |           |             |

|           |                          | nversion cor                 | npleted/not   | in progress   |             |                                |           |             |

| bit 0     | ADON: A/E                |                              |               |               |             |                                |           |             |

|           |                          | nverter mod<br>nverter is sh |               |               | oporating a | urront                         |           |             |

|           | O = A/U COI              | nverter is sh                | UTUTT 2DO CO  | neumoe no     |             | TITEDT                         |           |             |

| Legend:       |       |                  |                      |                    |

|---------------|-------|------------------|----------------------|--------------------|

| R = Readabl   | e bit | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value a | t POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

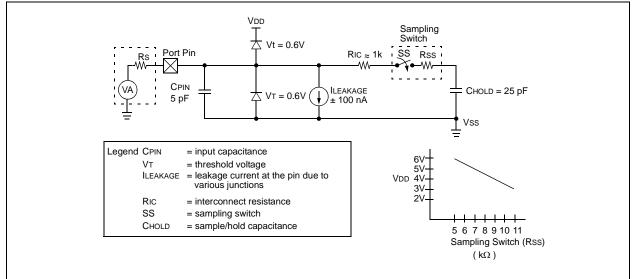

#### EXAMPLE 11-3: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

| TACQ =   | Amplifier Settling Time                                  |

|----------|----------------------------------------------------------|

|          | + Holding Capacitor Charging Time                        |

|          | +Temperature offset †                                    |

| TACQ =   | 5 μs                                                     |

|          | + Tc                                                     |

|          | + [(Temp - 25°C)(0.05 μs/°C)] †                          |

| Tc= Ho   | Iding Capacitor Charging Time                            |

| Tc = (C  | HOLD) (RIC + RSS + RS) In (1/16384)                      |

| Tc = -25 | 5 pF (1 kΩ +10 kΩ + 2.5 kΩ) In (1/16384)                 |

| Tc = -25 | 5 pF (13.5 kΩ) In (1/16384)                              |

| Tc = -0. | 338 (-9.704)μs                                           |

| Tc = 3.3 | 3 μs                                                     |

| TACQ =   | 5 µs                                                     |

|          | + 3.3 μs                                                 |

|          | + [(50°C - 25°C)(0.05 μs / °C)]                          |

| TACQ =   | 8.3 μs + 1.25 μs                                         |

| TACQ =   | 9.55 μs                                                  |

|          | perature coefficient is only required for atures > 25°C. |

#### FIGURE 11-5: ANALOG INPUT MODEL

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                         |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |

| SWAPF            | Swap Nybbles in f                                                                                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                            |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                         |  |  |  |  |  |

| Description:     | The upper and lower nybbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W regis-<br>ter. If 'd' is 1, the result is placed in<br>register 'f'. |  |  |  |  |  |

### 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

### 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

### 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

| TABLE 15-6: | ENHANCED CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP) |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

| Param.<br>No.    | Sym             | Characteristic        |                      |                             | Min                   | Тур† | Max | Units | Conditions                         |

|------------------|-----------------|-----------------------|----------------------|-----------------------------|-----------------------|------|-----|-------|------------------------------------|

| 50*              | TccL            | CCP1 input low time   | No Prescaler         |                             | 0.5Tcy + 20           | —    | _   | ns    |                                    |

|                  |                 |                       |                      | PIC16 <b>C</b> 717/770/771  | 10                    | _    | _   | ns    |                                    |

|                  |                 |                       | With Prescaler       | PIC16 <b>LC</b> 717/770/771 | 20                    | —    | _   | ns    |                                    |

| 51* TccH         | CCP1 input high | No Prescaler          | •                    | 0.5Tcy + 20                 | —                     | _    | ns  |       |                                    |

|                  |                 | time                  | With Prescaler       | PIC16 <b>C</b> 717/770/771  | 10                    | _    | _   | ns    |                                    |

|                  |                 |                       |                      | PIC16 <b>LC</b> 717/770/771 | 20                    | —    | _   | ns    |                                    |

| 52*              | TccP            | CCP1 input period     |                      |                             | <u>3Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(1, 4 or 16) |

| 53* TccR CCP1 of |                 | CCP1 output fall ti   | CP1 output fall time |                             | —                     | 10   | 25  | ns    |                                    |

|                  |                 |                       |                      | PIC16 <b>LC</b> 717/770/771 | —                     | 25   | 45  | ns    |                                    |

| 54* TccF         |                 | CCP1 output fall time |                      | PIC16 <b>C</b> 717/770/771  | —                     | 10   | 25  | ns    |                                    |

|                  |                 |                       |                      | PIC16 <b>LC</b> 717/770/771 | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.