Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 15                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                |                                                                         |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 18-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c717t-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

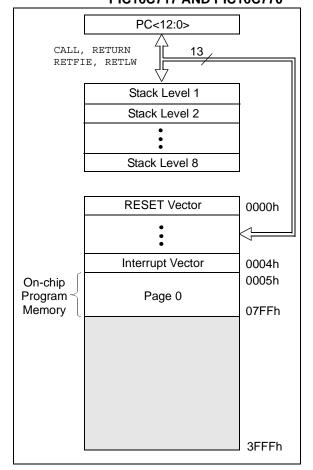

**PROGRAM MEMORY MAP**

FIGURE 2-2:

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual, (DS33023).

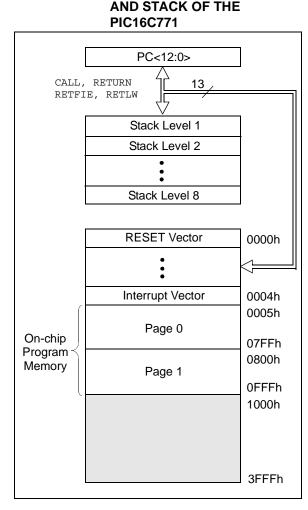

# 2.1 Program Memory Organization

The PIC16C717/770/771 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16C717 and the PIC16C770 have 2K x 14 words of program memory. The PIC16C771 has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wrap-around.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK OF THE PIC16C717 AND PIC16C770

# 2.2 Data Memory Organization

The data memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1  | RP0                                                                    | (STATUS<6:5>) |

|------|------------------------------------------------------------------------|---------------|

| = 01 | <ul> <li>Bank0</li> <li>Bank1</li> <li>Bank2</li> <li>Bank3</li> </ul> |               |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some frequently used special function registers from one bank are mirrored in another bank for code reduction and quicker access.

# 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register FSR.

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |

|-------|---------------------------------------------|

|       | and digit borrow bit, respectively, in sub- |

|       | traction. See the SUBLW and SUBWF           |

|       | instructions for examples.                  |

#### REGISTER 2-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                   | R/W-0                              | R/W-0        | R-1            | R-1          | R/W-x        | R/W-x          | R/W-x        |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|----------------|--------------|--------------|----------------|--------------|--|

|         | IRP                                                                                                                                                                                                                                                     | RP1                                | RP0          | TO             | PD           | Z            | DC             | С            |  |

|         | bit 7                                                                                                                                                                                                                                                   |                                    |              |                |              |              |                | bit 0        |  |

|         |                                                                                                                                                                                                                                                         |                                    |              |                |              |              |                |              |  |

| bit 7   |                                                                                                                                                                                                                                                         | ter Bank Sel                       |              | d for indirect | addressing   | a)           |                |              |  |

|         |                                                                                                                                                                                                                                                         | , 3 (100h - 1<br>, 1 (00h - FF     |              |                |              |              |                |              |  |

| bit 6-5 |                                                                                                                                                                                                                                                         | Register Ban                       |              | s (used for o  | lirect addre | ssing)       |                |              |  |

|         |                                                                                                                                                                                                                                                         | 3 (180h - 1F<br>2 (100h - 17       |              |                |              |              |                |              |  |

|         |                                                                                                                                                                                                                                                         | 1 (80h - FFh                       |              |                |              |              |                |              |  |

|         | 00 <b>= Bank</b>                                                                                                                                                                                                                                        | 0 (00h - 7Fh                       | )            |                |              |              |                |              |  |

|         |                                                                                                                                                                                                                                                         | is 128 bytes                       | i            |                |              |              |                |              |  |

| bit 4   | TO: Time-c                                                                                                                                                                                                                                              |                                    |              | tion of at t   |              | ion          |                |              |  |

|         | -                                                                                                                                                                                                                                                       | ower-up, CLI                       |              |                |              | ION          |                |              |  |

| bit 3   | PD: Power                                                                                                                                                                                                                                               | -down bit                          |              |                |              |              |                |              |  |

|         |                                                                                                                                                                                                                                                         | ower-up or b                       |              |                | n            |              |                |              |  |

|         | -                                                                                                                                                                                                                                                       | cution of the                      | SLEEP inst   | ruction        |              |              |                |              |  |

| bit 2   | Z: Zero bit                                                                                                                                                                                                                                             |                                    | h            |                |              |              |                |              |  |

|         |                                                                                                                                                                                                                                                         | sult of an arit<br>sult of an arit |              |                |              | 0            |                |              |  |

| bit 1   |                                                                                                                                                                                                                                                         | arry/borrow                        |              | •              |              |              | (for borrow    | the polarity |  |

|         | •                                                                                                                                                                                                                                                       | -out from the<br>ry-out from th    |              |                |              | urred        |                |              |  |

| bit 0   | C: Carry/bo                                                                                                                                                                                                                                             | orrow bit (AD                      | DWF, ADDLW   | , SUBLW, SU    | JBWF instru  | ictions)     |                |              |  |

|         | •                                                                                                                                                                                                                                                       | -out from the                      | •            |                |              |              |                |              |  |

|         | 0 = No cari                                                                                                                                                                                                                                             | ry-out from tl                     | ne Most Sigi | nificant bit o | f the result | occurred     |                |              |  |

|         | Note:                                                                                                                                                                                                                                                   | For borrow.                        | the polarity | is reversed.   | A subtract   | ion is execu | ted bv addin   | a the two's  |  |

|         | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register. |                                    |              |                |              |              |                |              |  |

|         | loaded with either the high or low order bit of the source register.                                                                                                                                                                                    |                                    |              |                |              |              |                |              |  |

|         | Legend:                                                                                                                                                                                                                                                 |                                    |              |                |              |              |                |              |  |

|         | R = Reada                                                                                                                                                                                                                                               | ble bit                            | W = W        | ritable bit    | U = Unir     | nplemented   | bit, read as ' | 0'           |  |

|         | - n = Value                                                                                                                                                                                                                                             | at POR                             | '1' = Bi     | t is set       | '0' = Bit    | is cleared   | x = Bit is u   | nknown       |  |

| Name                | Function | Input<br>Type | Output<br>Type | Description                           |

|---------------------|----------|---------------|----------------|---------------------------------------|

|                     | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB0/AN4/INT         | AN4      | AN            |                | A/D input                             |

|                     | INT      | ST            |                | Interrupt input                       |

|                     | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB1/AN5/SS          | AN5      | AN            |                | A/D input                             |

|                     | SS       | ST            |                | SSP slave select input                |

|                     | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB2/SCK/SCL         | SCK      | ST            | CMOS           | Serial clock I/O for SPI              |

|                     | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C |

|                     | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB3/CCP1/P1A        | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output      |

|                     | P1A      |               | CMOS           | PWM P1A output                        |

|                     | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB4/SDI/SDA         | SDI      | ST            |                | Serial data in for SPI                |

|                     | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C  |

|                     | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB5/SDO/P1B         | SDO      |               | CMOS           | Serial data out for SPI               |

|                     | P1B      |               | CMOS           | PWM P1B output                        |

|                     | RB6      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

|                     | T1OSO    |               | XTAL           | Crystal/Resonator                     |

| RB6/T1OSO/T1CKI/P1C | T1CKI    | CMOS          |                | TMR1 clock input                      |

|                     | P1C      |               | CMOS           | PWM P1C output                        |

|                     | RB7      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB7/T1OSI/P1D       | T1OSI    | XTAL          |                | TMR1 crystal/resonator                |

|                     | P1D      |               | CMOS           | PWM P1D output                        |

TABLE 3-3: PORTB FUNCTIONS

**Note 1:** Bit programmable pull-ups.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                             | Bit 5      | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-----------|------------|-------|-----------------------------------|------------|--------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                               | RB5        | RB4    | RB3   | RB2   | RB1   | RB0   | xxxx xx11                | uuuu uull                       |

| 86h, 186h | TRISB      | PORTE | B Data Dire                       | ction Reg  | jister |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                            | TOCS       | T0SE   | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

| 95h       | WPUB       | PORTE | 8 Weak Pul                        | Il-up Cont | rol    |       |       |       |       | 1111 1111                | 1111 1111                       |

| 96h       | IOCB       | PORTE | PORTB Interrupt on Change Control |            |        |       |       |       |       | 1111 0000                | 1111 0000                       |

| 9Dh       | ANSEL      | _     | _                                 | ANS5       | ANS4   | ANS3  | ANS2  | ANS1  | ANS0  | 11 1111                  | 11 1111                         |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

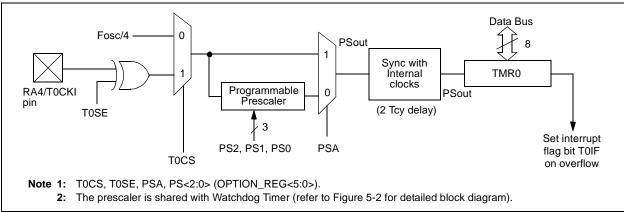

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 5-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

# 5.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

# 5.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 5-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS<2:0> bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### FIGURE 5-1: TIMER0 BLOCK DIAGRAM

# 6.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- RESET from ECCP module trigger

Timer1 has a control register, shown in Register 6-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 6-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

# 6.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- · As a synchronous counter

- · As an asynchronous counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     |     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                            |

| bit 3   | <b>T1OSCEN:</b> Timer1 Oscillator Enable Control bit<br>1 = Oscillator is enabled<br>0 = Oscillator is shut off <sup>(1)</sup>                                                                                                           |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bitTMR1CS = 1:1 = Do not synchronize external clock input0 = Synchronize external clock inputTMR1CS = 0:This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. |

| bit 1   | <b>TMR1CS:</b> Timer1 Clock Source Select bit<br>1 = External clock from pin RB6/T1OSO/T1CKI /P1C (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                                                    |

| bit 0   | TMR1ON: Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1                                                                                                                                                                          |

Note 1: The oscillator inverter and feedback resistor are turned off to eliminate power drain.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 6-1: TIMER1 CONTROL REGISTER (T1CON: 10h)

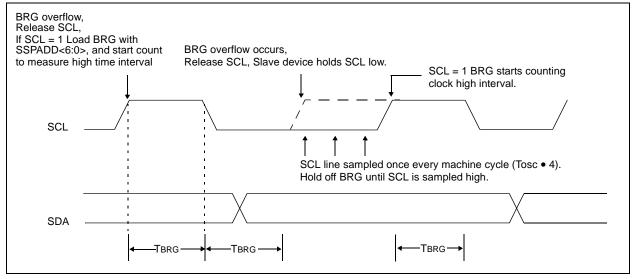

### 9.2.16 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the

SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 9-22).

#### FIGURE 9-22: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

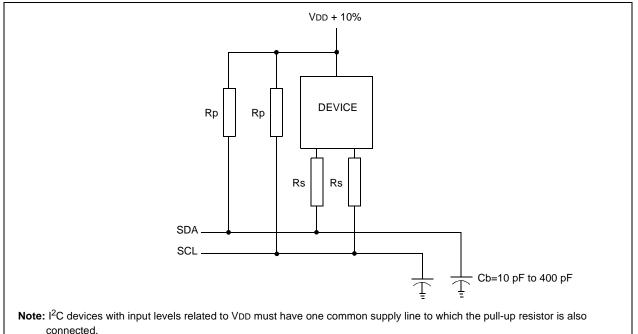

# 9.2.18 CONNECTION CONSIDERATIONS FOR I<sup>2</sup>C BUS

For Standard mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-31 depends on the following parameters

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at VoL max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA, R<sub>p min</sub> = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-31. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-31).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

#### FIGURE 9-31: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

| TABLE 9-3: | <b>REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION</b> |

|------------|-----------------------------------------------------------|

|            |                                                           |

| Address                | Name    | Bit 7 | Bit 6                                                            | Bit 5      | Bit 4       | Bit 3       | Bit 2         | Bit 1    | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|-------|------------------------------------------------------------------|------------|-------------|-------------|---------------|----------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE   | PEIE                                                             | TOIE       | INTE        | RBIE        | TOIF          | INTF     | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | —     | ADIF                                                             | —          | —           | SSPIF       | CCP1IF        | TMR2IF   | TMR1IF | -0 0000   | -0 0000   |

| 8Ch                    | PIE1    | —     | ADIE                                                             | _          | -           | SSPIE       | CCP1IE        | TMR2IE   | TMR1IE | -0 0000   | -0 0000   |

| 0Dh                    | PIR2    | LVDIF | -                                                                | _          | -           | BCLIF       | -             | —        | CCP2IF | 0 00      | 000       |

| 8Dh                    | PIE2    | LVDIE | —                                                                | —          | —           | BCLIE       | —             | —        | CCP2IE | 0 00      | 0 00      |

| 13h                    | SSPBUF  |       | Synch                                                            | ronous Ser | ial Port Re | ceive Buffe | er/Transmit F | Register |        | XXXX XXXX | uuuu uuuu |

| 14h                    | SSPCON  | WCOL  | SSPOV                                                            | SSPEN      | CKP         | SSPM3       | SSPM2         | SSPM1    | SSPM0  | 0000 0000 | 0000 0000 |

| 91h                    | SSPCON2 | GCEN  | ACKSTAT                                                          | ACKDT      | ACKEN       | RCEN        | PEN           | RSEN     | SEN    | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP   | CKE                                                              | D/A        | Р           | S           | R/W           | UA       | BF     | 0000 0000 | 0000 0000 |

| 93h                    | SSPADD  |       | Synchronous Serial Port (I <sup>2</sup> C Mode) Address Register |            |             |             |               |          |        |           | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the MSSP in I<sup>2</sup>C mode.

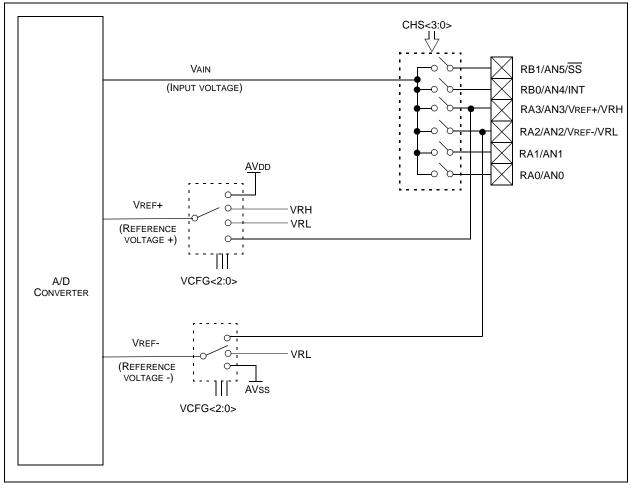

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has six inputs for the PIC16C717/770/771.

The PIC16C717 analog-to-digital converter (A/D) allows conversion of an analog input signal to a corresponding 10-bit digital value, while the A/D converter in the PIC16C770/771 allows conversion to a corresponding 12-bit digital value. The A/D module has up to 6 analog inputs, which are multiplexed into one sample and hold. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltages are software selectable to either the device's analog positive and negative supply voltages (AVDD/AVSS), the voltage level on the VREF+ and VREF- pins, or internal voltage references if enabled (VRH, VRL).

The A/D converter can be triggered by setting the GO/ DONE bit, or by the special event Compare mode of the ECCP module. When conversion is complete, the GO/DONE bit returns to '0', the ADIF bit in the PIR1 register is set, and an A/D interrupt will occur, if enabled.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result Register Low ADRESL

- A/D Result Register High ADRESH

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

# 11.1 Control Registers

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins, the voltage reference configuration and the result format. The ANSEL register, shown in Register 3-1, selects between the Analog or Digital Port Pin modes. The port pins can be configured as analog inputs or as digital I/O.

The combination of the ADRESH and ADRESL registers contain the result of the A/D conversion. The register pair is referred to as the ADRES register. When the A/D conversion is complete, the result is loaded into ADRES, the GO/DONE bit (ADCON0<2>) is cleared, and the A/D interrupt flag ADIF is set. The block diagram of the A/D module is shown in Figure 11-3. After the A/D module has been configured as desired and the analog input channels have their corresponding TRIS bits selected for port inputs, the selected channel must be acquired before conversion is started. The A/D conversion cycle can be initiated by setting the GO/DONE bit. The A/D conversion begins and lasts for 13TAD. The following steps should be followed for performing an A/D conversion:

- 1. Configure port pins:

- Configure Analog Input mode (ANSEL)

- Configure pin as input (TRISA or TRISB)

- 2. Configure the A/D module

- Configure A/D Result Format / voltage reference (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 3. Configure A/D interrupt (if required)

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

### FIGURE 11-3: A/D BLOCK DIAGRAM

- 4. Wait the required acquisition time.

- 5. START conversion

- Set GO/DONE bit (ADCON0)

- 6. Wait 13TAD until A/D conversion is complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 7. Read A/D Result registers (ADRESH and ADRESL), clear ADIF if required.

- 8. For next conversion, go to step 1, step 2 or step 3 as required.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRESH and ADRESL registers will be updated with the partially completed A/D conversion value. That is, the ADRESH and ADRESL registers will contain the value of the current incomplete conversion.

Note: Do not set the ADON bit and the GO/ DONE bit in the same instruction. Doing so will cause the GO/DONE bit to be automatically cleared.

# 11.7 Use of the ECCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCP1M<3:0> bits be programmed as 1011b and that the A/D module is enabled (ADON is set). When the trigger occurs, the GO/DONE bit will be set on Q2 to start the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is RESET to automatically repeat the A/D conversion cycle, with minimal software overhead (moving the ADRESH and ADRESL to the desired location). The appropriate analog input channel must be selected before the "special event trigger" sets the GO/DONE bit (starts a conversion cycle).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still RESET the Timer1 counter.

# 11.8 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRESH and ADRESL registers are not modified. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

# 11.9 Faster Conversion - Lower Resolution Trade-off

Not all applications require a result with 12 bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the tradeoff of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the A/D module may be halted by clearing the GO/DONE bit after the desired number of bits in the result have been converted. Once the GO/DONE bit has been cleared, all of the remaining A/D result bits are '0'. The equation to determine the time before the GO/DONE bit can be switched is as follows:

Conversion time = (N+1)TAD

Where: N = number of bits of resolution required, and 1TAD is the amplifier settling time.

Since TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D GO/DONE bit may be cleared. Table 11-4 shows a comparison of time required for a conversion with 4 bits of resolution, versus the normal 12-bit resolution conversion. The example is for devices operating at 20 MHz. The A/D clock is programmed for 32 Tosc.

#### EXAMPLE 11-4: 4-BIT vs. 12-BIT CONVERSION TIME Example

| 4-Bit Example:                  |

|---------------------------------|

| Conversion Time = $(N + 1)$ TAD |

| = (4 + 1) TAD                   |

| = (5)(1.6 μS)                   |

| = 8 µS                          |

| 12-Bit Example:                 |

| Conversion Time = $(N + 1)$ TAD |

| = (12 + 1) TAD                  |

| = (13)(1.6 μS)                  |

| = 20.8 μS                       |

|                                 |

# 15.3 AC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

# 15.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p                               | pS                                    | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------------------------|---------------------------------------|-----------|----------------------------------------|

| 2. TppS                                 |                                       | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                                       |                                       |           |                                        |

| F                                       | Frequency                             | Т         | Time                                   |

| Lowerca                                 | ase letters (pp) and their meanings:  |           |                                        |

| рр                                      |                                       |           |                                        |

| сс                                      | CCP1                                  | osc       | OSC1                                   |

| ck                                      | CLKOUT                                | rd        | RD                                     |

| CS                                      | CS                                    | rw        | RD or WR                               |

| di                                      | SDI                                   | sc        | SCK                                    |

| do                                      | SDO                                   | SS        | SS                                     |

| dt                                      | Data in                               | tO        | TOCKI                                  |

| io                                      | I/O port                              | t1        | T1CKI                                  |

| mc                                      | MCLR                                  | wr        | WR                                     |

| Upperca                                 | ase letters and their meanings:       |           |                                        |

| S                                       |                                       |           |                                        |

| F                                       | Fall                                  | Р         | Period                                 |

| Н                                       | High                                  | R         | Rise                                   |

| I                                       | Invalid (Hi-impedance)                | V         | Valid                                  |

| L                                       | Low                                   | Z         | Hi-impedance                           |

| <b>I<sup>2</sup>C</b> (I <sup>2</sup> C | specifications only)                  |           |                                        |

| AA                                      | output access                         |           |                                        |

| BUF                                     | Bus free                              |           |                                        |

| High                                    | High                                  |           |                                        |

| Low                                     | Low                                   |           |                                        |

| Tcc:st (                                | I <sup>2</sup> C specifications only) | ·         |                                        |

| CC                                      | 1                                     |           |                                        |

| HD                                      | Hold                                  | SU        | Setup                                  |

| ST                                      |                                       |           |                                        |

| DAT                                     | DATA input hold                       | STO       | STOP condition                         |

|                                         | •                                     |           |                                        |

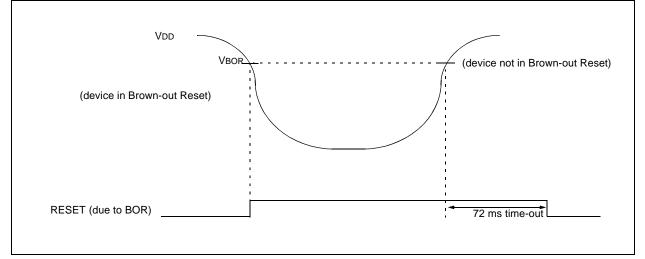

# TABLE 15-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30*              | TMCL  | MCLR Pulse Width (low)                                 | 2   | —         | —   | μs    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32*              | Tost  | Oscillation Start-up Timer Period                      |     | 1024 Tosc |     | —     | Tosc = OSC1 period       |

| 33*              | TPWRT | Power up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34*              | TIOZ  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | —         | 2.1 | μs    |                          |

| 35*              | TBOR  | Brown-out Reset pulse width                            | 100 | —         | —   | μS    | $VDD \le VBOR (D005)$    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# FIGURE 15-9: BROWN-OUT RESET CHARACTERISTICS

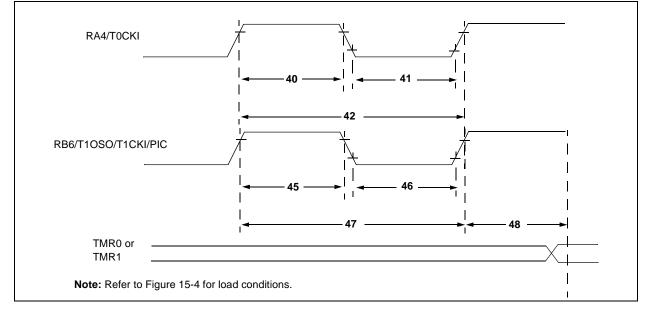

### FIGURE 15-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param.<br>No. | Sym               | Characteristic                                 |                            |                             | Min                                              | Тур† | Мах   | Units | Conditions                         |  |

|---------------|-------------------|------------------------------------------------|----------------------------|-----------------------------|--------------------------------------------------|------|-------|-------|------------------------------------|--|

| 40*           | Tt0H              | T0CKI High Pulse W                             | /idth                      | No Prescaler                | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |  |

|               |                   |                                                |                            | With Prescaler              | 10                                               | _    | _     | ns    | parameter 42                       |  |

| 41*           | Tt0L              |                                                |                            | No Prescaler                | 0.5Tcy + 20                                      | —    | —     | ns    | Must also meet                     |  |

|               |                   |                                                |                            | With Prescaler              | 10                                               | —    | —     | ns    | parameter 42                       |  |

| 42*           | Tt0P T0CKI Period |                                                |                            | No Prescaler                | TCY + 40                                         | —    | —     | ns    |                                    |  |

|               |                   |                                                |                            | With Prescaler              | Greater of:<br>20 or <u>TcY + 40</u><br>N        | _    | —     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*           | Tt1H              | T1CKI High Time                                | Synchronous, F             | Prescaler = 1               | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |  |

|               |                   | -                                              | Synchronous,               | PIC16C717/770/771           | 15                                               | —    | —     | ns    | parameter 47                       |  |

|               |                   |                                                | Prescaler =<br>2,4,8       | PIC16 <b>LC</b> 717/770/771 | 25                                               | -    | —     | ns    |                                    |  |

|               |                   |                                                | Asynchronous               | PIC16C717/770/771           | 30                                               | —    | _     | ns    |                                    |  |

|               |                   |                                                |                            | PIC16LC717/770/771          | 50                                               | —    | —     | ns    |                                    |  |

| 46*           | Tt1L              | T1CKI Low Time                                 | Synchronous, Prescaler = 1 |                             | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |  |

|               |                   |                                                | Synchronous,               | PIC16 <b>C</b> 717/770/771  | 15                                               | —    | —     | ns    | parameter 47                       |  |

|               |                   |                                                | Prescaler =<br>2,4,8       | PIC16 <b>LC</b> 717/770/771 | 25                                               | —    | —     | ns    |                                    |  |

|               |                   |                                                | Asynchronous               | PIC16 <b>C</b> 717/770/771  | 30                                               | —    | —     | ns    |                                    |  |

|               |                   |                                                |                            | PIC16LC717/770/771          | 50                                               | —    | —     | ns    |                                    |  |

| 47*           | Tt1P              | T1CKI input period                             | Synchronous                | PIC16 <b>C</b> 717/770/771  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | —    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|               |                   |                                                |                            | PIC16 <b>LC</b> 717/770/771 | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N | —    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|               |                   |                                                | Asynchronous               | PIC16C717/770/771           | 60                                               | —    | —     | ns    |                                    |  |

|               |                   |                                                |                            | PIC16LC717/770/771          | 100                                              | —    | —     | ns    |                                    |  |

|               | Ft1               | Timer1 oscillator inp<br>(oscillator enabled b |                            |                             | DC                                               | —    | 50    | kHz   |                                    |  |

| 48            | Tcke2tmr          | 1 Delay from external                          | clock edge to tim          | ner increment               | 2Tosc                                            | - 1  | 7Tosc | —     |                                    |  |

| TABLE 15-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

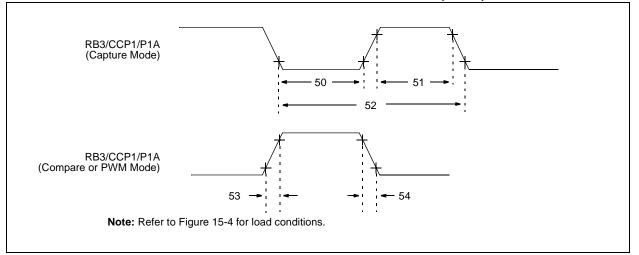

#### FIGURE 15-11: ENHANCED CAPTURE/COMPARE/PWM TIMINGS (ECCP)

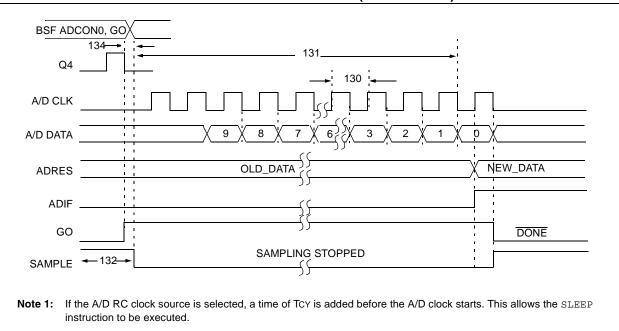

#### FIGURE 15-17: PIC16C717 A/D CONVERSION TIMING (SLEEP MODE)

#### TABLE 15-16: PIC16C717 AND PIC16LC717 A/D CONVERSION REQUIREMENT (SLEEP MODE)

| Parameter<br>No.    | Sym  | Characteristic                                            | Min      | Тур†         | Max | Units | Conditions                                                                                                                                                                                                               |

|---------------------|------|-----------------------------------------------------------|----------|--------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D clock period                                          | 3.0      | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (A/D RC mode)<br>At VDD = 3.0V                                                                                                                                                                            |

|                     |      |                                                           | 2.0      | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                                            |

| 131*                | ΤΟΝΥ | Conversion time (not including acquisition time) (Note 1) | _        | 11Tad        | _   | _     |                                                                                                                                                                                                                          |

| 132*                | TACQ | Acquisition Time                                          | (Note 2) | 11.5         | _   | μs    |                                                                                                                                                                                                                          |

|                     |      |                                                           | 5*       | _            | _   | μS    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1LSb (i.e.,<br>1mV @ 4.096V) from the last sam-<br>pled voltage (as stated on CHOLD). |

| 134*                | TGO  | Q4 to A/D clock start                                     |          | Tosc/2 + Tcy |     | _     | If the A/D RC clock source is<br>selected, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 11.6 for minimum conditions.

3: These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

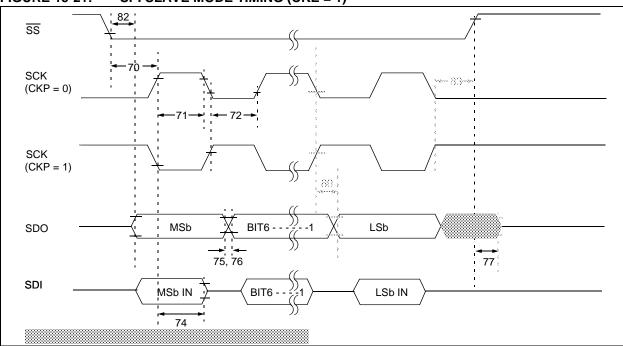

#### FIGURE 15-21: SPI SLAVE MODE TIMING (CKE = 1)

# TABLE 15-20: SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                                                        | Min                            | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|-----------------------------------------------------------------------|--------------------------------|--------------|-----|-------|------------|--------|

| 70*           | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү                            | —            |     | ns    |            |        |

| 71*           | TscH                  | SCK input high time                                                   | SCK input high time Continuous |              | —   | _     | ns         |        |

| 71A*          |                       | (Slave mode)                                                          | Single Byte                    | 40           | —   | _     | ns         | Note 1 |

| 72*           | TscL                  | SCK input low time                                                    | Continuous                     | 1.25Tcy + 30 | —   | _     | ns         |        |

| 72A*          |                       | (Slave mode)                                                          | Single Byte                    | 40           | —   |       | ns         | Note 1 |

| 73A*          | Тв2в                  | Last clock edge of Byte1 to edge of Byte2                             | 1.5Tcy + 40                    | -            | —   | ns    | Note 1     |        |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input                                           | 100                            | -            | —   | ns    |            |        |

| 75*           | TdoR                  | SDO data output rise time                                             | PIC16 <b>C</b> XXX             | _            | 10  | 25    | ns         |        |

|               |                       |                                                                       | PIC16LCXXX                     |              | 20  | 45    | ns         |        |

| 76*           | TdoF                  | SDO data output fall time                                             |                                | _            | 10  | 25    | ns         |        |

| 77*           | TssH2doZ              | SS↑ to SDO output hi-impe                                             | dance                          | 10           | —   | 50    | ns         |        |

| 78*           | TscR                  | SCK output rise time (Mas-                                            | PIC16 <b>C</b> XXX             | _            | 10  | 25    | ns         |        |

|               |                       | ter mode)                                                             | PIC16LCXXX                     | _            | 20  | 45    | ns         |        |

| 79*           | TscF                  | SCK output fall time (Maste                                           | r mode)                        | _            | 10  | 25    | ns         |        |

| 80*           | TscH2doV,             | SDO data output valid after                                           | PIC16 <b>C</b> XXX             | _            | _   | 50    | ns         |        |

|               | TscL2doV              | SCK edge                                                              | PIC16LCXXX                     | _            | —   | 100   | ns         |        |

| 82*           | TssL2doV              | SDO data output valid after                                           | PIC16CXXX                      | _            | _   | 50    | ns         |        |

|               |                       | SS↓ edge                                                              | PIC16LCXXX                     | _            | _   | 100   | ns         |        |

| 83*           | TscH2ssH,<br>TscL2ssH | $\overline{\text{SS}}$ $\uparrow$ after SCK edge                      |                                | 1.5Tcy + 40  | _   |       | ns         |        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

| Param.<br>No. | Symbol  | Characteristic      |                           | Min              | Max  | Units | Conditions                        |

|---------------|---------|---------------------|---------------------------|------------------|------|-------|-----------------------------------|

| 100*          | Thigh   | Clock high time     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 101*          | TLOW    | Clock low time      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 102*          | TR      | SDA and SCL         | 100 kHz mode              | _                | 1000 | ns    | Cb is specified to be from        |

|               |         | rise time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                                   |

| 103*          | TF      | SDA and SCL         | 100 kHz mode              | _                | 300  | ns    | Cb is specified to be from        |

|               |         | fall time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns    |                                   |

| 90*           | TSU:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | Only relevant for Repeated        |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | START                             |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    | condition                         |

| 91*           | THD:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period the first clock |

|               |         | hold time           | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | pulse is generated                |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 106*          | THD:DAT | Data input          | 100 kHz mode              | 0                | —    | ns    |                                   |

|               |         | hold time           | 400 kHz mode              | 0                | 0.9  | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | —    | ns    |                                   |

| 107*          | TSU:DAT | Data input          | 100 kHz mode              | 250              | —    | ns    | Note 2                            |

|               |         | setup time          | 400 kHz mode              | 100              | —    | ns    | 1                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | -    | ns    |                                   |

| 92*           | Tsu:sto | STOP condition      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 109*          | TAA     | Output valid from   | 100 kHz mode              | _                | 3500 | ns    |                                   |

|               |         | clock               | 400 kHz mode              | —                | 1000 | ns    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | —                | —    | ns    |                                   |

| 110           | TBUF    | Bus free time       | 100 kHz mode              | 4.7 ‡            | —    | ms    | Time the bus must be free         |

|               |         |                     | 400 kHz mode              | 1.3 ‡            | —    | ms    | before a new transmission         |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD‡             | —    | ms    | can start                         |

| D102 ‡        | Cb      | Bus capacitive load |                           | —                | 400  | pF    |                                   |

# TABLE 15-22: MASTER SSP I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested. For the value required by the I<sup>2</sup>C specification, please refer to the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023).

‡ These parameters are for design guidance only and are not tested, nor characterized.

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A Fast mode  $l^2C$  bus device can be used in a Standard mode  $l^2C$  bus system, but  $(TSU:DAT) \ge 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line.

[(TR) + (TSU:DAT) = 1000 + 250 = 1250 ns], for 100 kHz mode, before the SCL line is released.

© 1999-2013 Microchip Technology Inc.

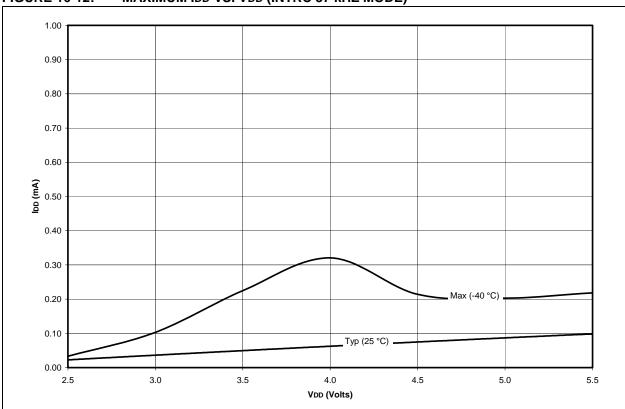

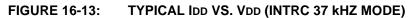

FIGURE 16-12: MAXIMUM IDD VS. VDD (INTRC 37 kHZ MODE)

© 1999-2013 Microchip Technology Inc.

# PIC16C717/770/771

© 1999-2013 Microchip Technology Inc.

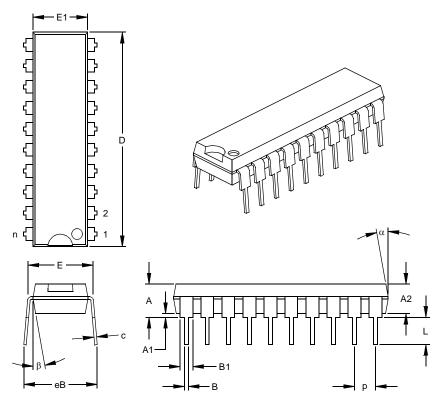

#### 20-Lead Plastic Dual In-line (P) - 300 mil (PDIP) 17.5

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

| Units            |                                                                                     | INCHES*                                                                                                                                                                                                                                                                                                                                                     |                                                        | MILLIMETERS                                            |                                                        |                                                        |  |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| Dimension Limits |                                                                                     |                                                                                                                                                                                                                                                                                                                                                             |                                                        | MIN                                                    | NOM                                                    | MAX                                                    |  |

| n                |                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 20                                                     |                                                        |  |

| р                |                                                                                     | .100                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        | 2.54                                                   |                                                        |  |

| А                | .140                                                                                | .155                                                                                                                                                                                                                                                                                                                                                        | .170                                                   | 3.56                                                   | 3.94                                                   | 4.32                                                   |  |

| A2               | .115                                                                                | .130                                                                                                                                                                                                                                                                                                                                                        | .145                                                   | 2.92                                                   | 3.30                                                   | 3.68                                                   |  |

| A1               | .015                                                                                |                                                                                                                                                                                                                                                                                                                                                             |                                                        | 0.38                                                   |                                                        |                                                        |  |

| Е                | .295                                                                                | .310                                                                                                                                                                                                                                                                                                                                                        | .325                                                   | 7.49                                                   | 7.87                                                   | 8.26                                                   |  |

| E1               | .240                                                                                | .250                                                                                                                                                                                                                                                                                                                                                        | .260                                                   | 6.10                                                   | 6.35                                                   | 6.60                                                   |  |

| D                | 1.025                                                                               | 1.033                                                                                                                                                                                                                                                                                                                                                       | 1.040                                                  | 26.04                                                  | 26.24                                                  | 26.42                                                  |  |

| L                | .120                                                                                | .130                                                                                                                                                                                                                                                                                                                                                        | .140                                                   | 3.05                                                   | 3.30                                                   | 3.56                                                   |  |

| С                | .008                                                                                | .012                                                                                                                                                                                                                                                                                                                                                        | .015                                                   | 0.20                                                   | 0.29                                                   | 0.38                                                   |  |