Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c770-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-3: REGISTER FILE MAP

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address | Δ                     | File<br>ddress |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|-----------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)     | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION REG            | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                   | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                   | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            | - I OIL               | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                 | 186h           |

|                                | 07h            |                                            | 87h            |                                            | 107h            |                       | 187h           |

|                                | 08h            |                                            | 88h            |                                            | 108h            |                       | 188h           |

|                                | 09h            |                                            | 89h            |                                            | 109h            |                       | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATL                                     | 10Ch            | PMCON1                | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADRL                                     | 10Dh            |                       | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                       | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                       | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                       | 190h           |

| TMR2                           | 11h            | SSPCON2                                    | 91h            |                                            | 111h            |                       | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                       | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                       | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                       | 194h           |

| CCPR1L                         | 15h            | WPUB                                       | 95h            |                                            | 115h            |                       | 195h           |

| CCPR1H                         | 16h            | IOCB                                       | 96h            |                                            | 116h            |                       | 196h           |

| CCP1CON                        | 17h            | P1DEL                                      | 97h            |                                            | 117h            |                       | 197h           |

|                                | 18h            |                                            | 98h            |                                            | 118h            |                       | 198h           |

|                                | 19h            |                                            | 99h            |                                            | 119h            |                       | 199h           |

|                                | 1Ah            |                                            | 9Ah            |                                            | 11Ah            |                       | 19Ah           |

|                                | 1Bh            | REFCON                                     | 9Bh            |                                            | 11Bh            |                       | 19Bh           |

|                                | 1Ch            | LVDCON                                     | 9Ch            |                                            | 11Ch            |                       | 19Ch           |

|                                | 1Dh            | ANSEL                                      | 9Dh            |                                            | 11Dh            |                       | 19Dh           |

| ADRESH                         | 1Eh            | ADRESL                                     | 9Eh            |                                            | 11Eh            |                       | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                       | 19Fh           |

|                                | 20h            |                                            | A0h            |                                            | 120h            |                       | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 |                       |                |

| 96 Bytes                       |                |                                            | EFh            |                                            | 16Fh            |                       | 1EFh           |

| -                              |                | accesses<br>70h-7Fh                        | F0h            | accesses<br>70h - 7Fh                      | 170h            | accesses<br>70h - 7Fh | 1F0h           |

| Bank 0                         | 7Fh            | Bank 1                                     | FFh            | Bank 2                                     | 17Fh            | Bank 3                | 1FFh           |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

## PIC16C717/770/771

| Address              | Name       | Bit 7                                                        | Bit 6          | Bit 5                   | Bit 4          | Bit 3        | Bit 2        | Bit 1          | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>Page: |

|----------------------|------------|--------------------------------------------------------------|----------------|-------------------------|----------------|--------------|--------------|----------------|---------|--------------------------|------------------------|

| Bank 1               |            |                                                              |                |                         |                |              |              |                |         |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressing                                                   | this location  | uses content            | s of FSR to ad | dress data m | emory (not a | a physical reg | gister) | 0000 0000                | 23                     |

| 81h                  | OPTION_REG | RBPU                                                         | INTEDG         | TOCS                    | TOSE           | PSA          | PS2          | PS1            | PS0     | 1111 1111                | 15                     |

| 82h <sup>(3)</sup>   | PCL        | Program Co                                                   | ounter's (PC)  | Least Signifi           | cant Byte      |              |              |                |         | 0000 0000                | 22                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP                                                          | RP1            | RP0                     | TO             | PD           | Z            | DC             | С       | 0001 1xxx                | 14                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect data                                                | a memory ad    | dress pointer           |                |              |              |                |         | xxxx xxxx                | 23                     |

| 85h                  | TRISA      | PORTA Dat                                                    | a Direction F  | legister                |                |              |              |                |         | 1111 1111                | 25                     |

| 86h                  | TRISB      | PORTB Dat                                                    | ta Direction F | Register                |                |              |              |                |         | 1111 1111                | 33                     |

| 87h                  | —          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 88h                  | —          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | _                      |

| 89h                  | _          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 8Ah <sup>(1,3)</sup> | PCLATH     | — — Write Buffer for the upper 5 bits of the Program Counter |                |                         |                | 0 0000       | 22           |                |         |                          |                        |

| 8Bh <b>(3)</b>       | INTCON     | GIE                                                          | PEIE           | TOIE                    | INTE           | RBIE         | T0IF         | INTF           | RBIF    | 0000 000x                | 16                     |

| 8Ch                  | PIE1       | —                                                            | ADIE           |                         | —              | SSPIE        | CCP1IE       | TMR2IE         | TMR1IE  | -0 0000                  | 17                     |

| 8Dh                  | PIE2       | LVDIE                                                        | —              |                         | —              | BCLIE        | —            | —              | —       | 0 0                      | 19                     |

| 8Eh                  | PCON       | —                                                            | —              |                         | —              | OSCF         | —            | POR            | BOR     | 1-qq                     | 21                     |

| 8Fh                  | _          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 90h                  | _          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | _                      |

| 91h                  | SSPCON2    | GCEN                                                         | ACKSTAT        | ACKDT                   | ACKEN          | RCEN         | PEN          | RSEN           | SEN     | 0000 0000                | 69                     |

| 92h                  | PR2        | Timer2 Peri                                                  | od Register    |                         |                |              |              |                |         | 1111 1111                | 52                     |

| 93h                  | SSPADD     | Synchronou                                                   | is Serial Port | (I <sup>2</sup> C mode) | Address Regist | er           |              |                |         | 0000 0000                | 76                     |

| 94h                  | SSPSTAT    | SMP                                                          | CKE            | D/A                     | Р              | S            | R/W          | UA             | BF      | 0000 0000                | 66                     |

| 95h                  | WPUB       | PORTB We                                                     | ak Pull-up C   | ontrol                  |                |              |              |                |         | 1111 1111                | 34                     |

| 96h                  | IOCB       | PORTB Inte                                                   | errupt on Cha  | ange Control            |                |              |              |                |         | 1111 0000                | 34                     |

| 97h                  | P1DEL      | PWM 1 Del                                                    | ay value       |                         |                |              |              |                |         | 0000 0000                | 62                     |

| 98h                  | —          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 99h                  | _          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 9Ah                  | —          | Unimpleme                                                    | nted           |                         |                |              |              |                |         | _                        | —                      |

| 9Bh                  | REFCON     | VRHEN                                                        | VRLEN          | VRHOEN                  | VRLOEN         | —            | —            | —              | —       | 0000                     | 102                    |

| 9Ch                  | LVDCON     | —                                                            | —              | BGST                    | LVDEN          | LVV3         | LVV2         | LVV1           | LVV0    | 00 0101                  | 101                    |

| 9Dh                  | ANSEL      | —                                                            | —              | Analog Chai             | nnel Select    |              |              |                |         | 11 1111                  | 25                     |

| 9Eh                  | ADRESL     | A/D Low By                                                   | te Result Re   | gister                  |                |              |              |                |         | xxxx xxxx                | 107                    |

| 9Fh                  | ADCON1     | ADFM                                                         | VCFG2          | VCFG1                   | VCFG0          | _            |              |                |         | 0000                     | 107                    |

#### TABLE 2-1: PIC16C717/770/771 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

**3:** These registers can be addressed from any bank.

#### EXAMPLE 3-1: Initializing PORTA

|       | -       |     |   | <b>J</b>                                                                 |

|-------|---------|-----|---|--------------------------------------------------------------------------|

| BCF   | STATUS, | RP0 | ; | Select Bank 0                                                            |

| CLRF  | PORTA   |     | ; | Initialize PORTA by                                                      |

|       |         |     | ; | clearing output                                                          |

|       |         |     | ; | data latches                                                             |

| BSF   | STATUS, | RP0 | ; | Select Bank 1                                                            |

| MOVLW | 0Fh     |     | ; | Value used to                                                            |

|       |         |     | ; | initialize data                                                          |

|       |         |     | ; | direction                                                                |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs                                                    |

|       |         |     | ; | RA<7:4> as outputs. RA<7:6>availability depends on oscillator selection. |

| MOVLW | 03      |     | ; | Set RA<1:0> as analog inputs, RA<7:2> are digital I/O                    |

| MOVWF | ANSEL   |     |   |                                                                          |

| BCF   | STATUS, | RP0 | ; | Return to Bank 0                                                         |

|       |         |     |   |                                                                          |

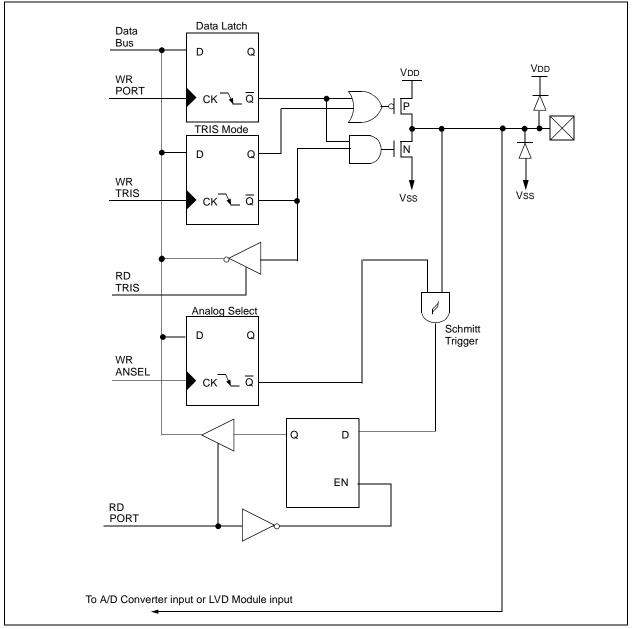

#### FIGURE 3-1: BLOCK DIAGRAM OF RA0/AN0, RA1/AN1/LVDIN

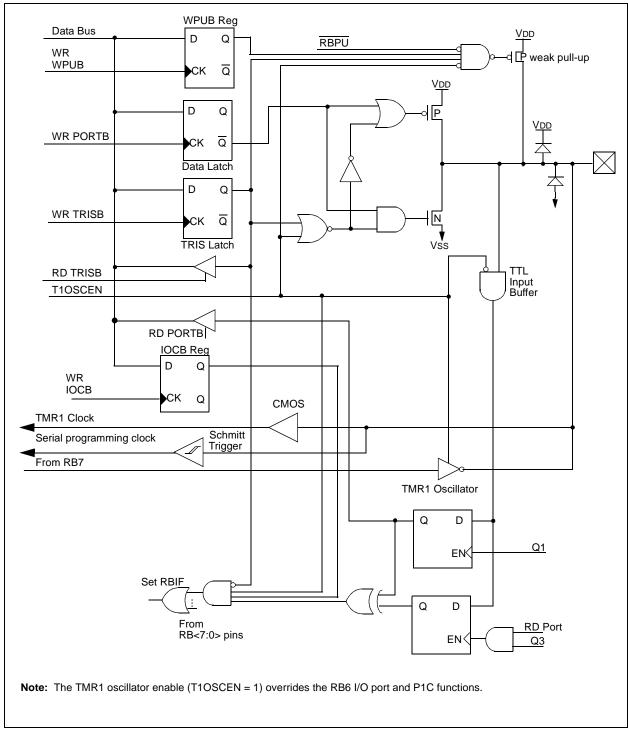

#### 3.3 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 3-2: Initializing PORTB

| BCF   | STATUS, | RP0; |                       |

|-------|---------|------|-----------------------|

| CLRF  | PORTB   | ;    | Initialize PORTB by   |

|       |         | ;    | clearing output       |

|       |         | ;    | data latches          |

| BSF   | STATUS, | RP0; | Select Bank 1         |

| MOVLW | 0xCF    | ;    | Value used to         |

|       |         | ;    | initialize data       |

|       |         | ;    | direction             |

| MOVWF | TRISB   | ;    | Set RB<3:0> as inputs |

|       |         | ;    | RB<5:4> as outputs    |

|       |         | ;    | RB<7:6> as inputs     |

| MOVLW | 0x30    | ;    | Set RB<1:0> as analog |

|       |         |      | inputs                |

| MOVWF | ANSEL   | ;    |                       |

| BCF   | STATUS, | RP0; | Return to Bank 0      |

|       |         |      |                       |

Each of the PORTB pins has an internal pull-up, which can be individually enabled from the WPUB register. A single global enable bit can turn on/off the enabled pullups. Clearing the RBPU bit, (OPTION\_REG<7>), enables the weak pull-up resistors. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset. Each of the PORTB pins, if configured as input, also has an interrupt-on-change feature, which can be individually selected from the IOCB register. The RBIE bit in the INTCON register functions as a global enable bit to turn on/off the interrupt-on-change feature. The selected inputs are compared to the old value latched on the last read of PORTB. The "mismatch" outputs are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- a) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 3-9: BLOCK DIAGRAM OF RB6/T1OSO/T1CKI/P1C

| Name                | Function | Input<br>Type | Output<br>Type | Description                           |

|---------------------|----------|---------------|----------------|---------------------------------------|

|                     | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB0/AN4/INT         | AN4      | AN            |                | A/D input                             |

|                     | INT      | ST            |                | Interrupt input                       |

|                     | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB1/AN5/SS          | AN5      | AN            |                | A/D input                             |

|                     | SS       | ST            |                | SSP slave select input                |

|                     | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB2/SCK/SCL         | SCK      | ST            | CMOS           | Serial clock I/O for SPI              |

|                     | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C |

|                     | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB3/CCP1/P1A        | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output      |

|                     | P1A      |               | CMOS           | PWM P1A output                        |

|                     | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB4/SDI/SDA         | SDI      | ST            |                | Serial data in for SPI                |

|                     | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C  |

|                     | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB5/SDO/P1B         | SDO      |               | CMOS           | Serial data out for SPI               |

|                     | P1B      |               | CMOS           | PWM P1B output                        |

|                     | RB6      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

|                     | T1OSO    |               | XTAL           | Crystal/Resonator                     |

| RB6/T1OSO/T1CKI/P1C | T1CKI    | CMOS          |                | TMR1 clock input                      |

|                     | P1C      |               | CMOS           | PWM P1C output                        |

|                     | RB7      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>     |

| RB7/T1OSI/P1D       | T1OSI    | XTAL          |                | TMR1 crystal/resonator                |

|                     | P1D      |               | CMOS           | PWM P1D output                        |

TABLE 3-3: PORTB FUNCTIONS

**Note 1:** Bit programmable pull-ups.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                            | Bit 5     | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-----------|------------|-------|----------------------------------|-----------|--------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                              | RB5       | RB4    | RB3   | RB2   | RB1   | RB0   | xxxx xx11                | uuuu uull                       |

| 86h, 186h | TRISB      | PORTE | B Data Dire                      | ction Reg | jister |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                           | TOCS      | T0SE   | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

| 95h       | WPUB       | PORTE | 8 Weak Pul                       | I-up Cont | rol    |       |       |       |       | 1111 1111                | 1111 1111                       |

| 96h       | IOCB       | PORTE | ORTB Interrupt on Change Control |           |        |       |       |       |       | 1111 0000                | 1111 0000                       |

| 9Dh       | ANSEL      | _     | _                                | ANS5      | ANS4   | ANS3  | ANS2  | ANS1  | ANS0  | 11 1111                  | 11 1111                         |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

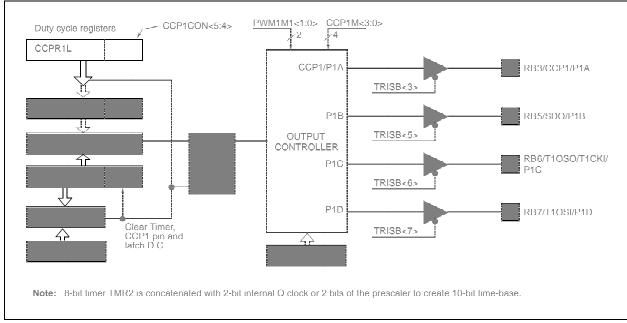

## 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the ECCP module produces up to a 10-bit resolution PWM output. Figure 8-3 shows the simplified PWM block diagram.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM PERIOD = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 PRESCALE VALUE)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 7.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.4 OUTPUT POLARITY CONFIGURATION

The CCP1M<1:0> bits in the CCP1CON register allow user to choose the logic conventions (asserted high/ low) for each of the outputs. See Register 8-1 for further details.

The PWM output polarities must be selected before the PWM outputs are enabled. Charging the polarity configuration while the PWM outputs are active is not recommended, since it may result in unpredictable operation.

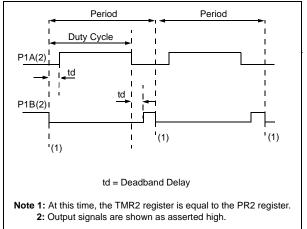

#### 8.3.5 PROGRAMMABLE DEADBAND DELAY

In half-bridge or full-bridge applications, driven by halfbridge outputs (see Figure 8-7), the power switches normally require longer time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches will be on for a short period of time, until one switch completely turns off. During this time, a very high current, called shootthrough current, will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on the power switch is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable deadband delay is available to avoid shootthrough current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 8-6 for illustration. The P1DEL register sets the amount of delay.

## REGISTER 8-2: PWM DELAY REGISTER (P1DEL: 97H)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| P1DEL7 | P1DEL6 | P1DEL5 | P1DEL4 | P1DEL3 | P1DEL2 | P1DEL1 | P1DEL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

## bit 7-0 **P1DEL<7:0>: PWM Delay Count for Half-Bridge Output Mode:** Number of Fosc/4 (Tosc•4) cycles between the P1A transition and the P1B transition.

| Legend:            |                  |                                           |

|--------------------|------------------|-------------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'        |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared $x = Bit$ is unknown |

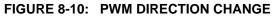

#### 8.3.6 DIRECTION CHANGE IN FULL-BRIDGE OUTPUT MODE

In the Full-Bridge Output mode, the PWM1M1 bit in the CCP1CON register allows user to control the Forward/ Reverse direction. When the application firmware changes this direction control bit, the ECCP module will assume the new direction on the next PWM cycle. The current PWM cycle still continues, however, the nonmodulated outputs, P1A and P1C signals, will transition to the new direction TOSC,  $4 \cdot TOSC$  or  $16 \cdot TOSC$  (for Timer2 prescale T2CKRS<1:0> = 00, 01 and 1x respectively) earlier, before the end of the period. During this transition cycle, the modulated outputs, P1B and P1D, will go to the inactive state. See Figure 8-10 for illustration.

Note 1: The Direction bit in the ECCP Control Register (CCP1CON<PWM1M1>) is written anytime during the PWM cycle.

2: The P1A and P1C signals switch Tosc, 4\*Tosc or 16\*Tosc, depending on the Timer2 prescaler value, earlier when changing direction. The modulated P1B and P1D signals are inactive at this time.

For more information about these SSP modes see Section 15 of the *PIC Mid-Range MCU Family Reference Manual (DS33023).*

#### 9.2.2 SLAVE MODE

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse. Then, it loads the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the  $\underline{MSSP}$  module to generate a NACK pulse in lieu of the  $\overline{ACK}$  pulse:

- a) The buffer full bit BF (SSPSTAT<0>) is set before the transfer is received.

- b) The overflow bit SSPOV (SSPCON<6>) is set before the transfer is received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF. However, both the SSPIF and SSPOV bits are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. The BF flag bit is cleared by reading the SSPBUF register. The SSPOV flag bit is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification as well as the requirements of the MSSP module are shown in timing parameters #100 and #101 of the Electrical Specifications.

#### 9.2.2.1 7-BIT ADDRESSING

Once the MSSP module has been enabled (SSPEN=1), the slave module waits for a START condition to occur. Following the START condition, eight bits are shifted into the SSPSR register. All incoming bits are sampled on the rising edge of the clock (SCL) line. The received address (register SSPSR<7:1>) is compared to the stored address (register SSPADD<7:1>). SSPSR<0> is the R/W bit and is not considered in the comparison. Comparison is made on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is transferred to the SSPBUF register on the falling edge of the eighth SCL pulse.

- b) The buffer full bit; BF is set on the falling edge of the eighth SCL pulse.

- c) An ACK pulse is generated during the ninth clock cycle.

- d) SSP interrupt flag bit; SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

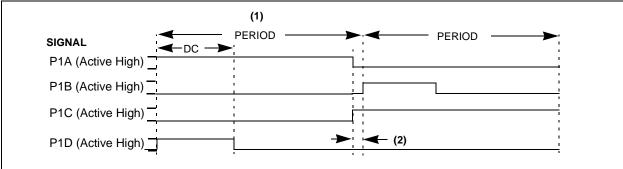

#### 9.2.2.2 10-BIT ADDRESSING

In 10-bit mode, the basic receive and transmit operations are the same as in the 7-bit mode. However, the criteria for address match are more complex.

Two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify that this is a 10-bit address. The LSb of the first received address byte is the R/W bit, which must be zero, specifying a write so the slave device will receive the second address byte. For a 10-bit address, the first byte equals '11110 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7 through 9 applicable only to the slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- Receive first (high) byte of Address with R/W bit set to 1 (bits SSPIF and BF are set). This also puts the MSSP module in the Slave-transmit mode.

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

Note: Following the Repeated START condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

|         | R/W-0                      | R/W-0                                                                                                                                                         | R/W-0                       | R/W-0                          | U-0                    | U-0          | U-0          | U-0          |  |  |  |  |

|---------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------|------------------------|--------------|--------------|--------------|--|--|--|--|

|         | VRHEN                      | VRLEN                                                                                                                                                         | VRHOEN                      | VRLOEN                         | _                      | —            | —            | _            |  |  |  |  |

|         | bit 7                      |                                                                                                                                                               |                             |                                |                        |              |              | bit 0        |  |  |  |  |

|         |                            |                                                                                                                                                               |                             |                                |                        |              |              |              |  |  |  |  |

| bit 7   | VRHEN: Vo                  | oltage Refer                                                                                                                                                  | ence High E                 | Enable bit (V                  | RH = 4.096             | V nominal)   |              |              |  |  |  |  |

|         |                            | · •                                                                                                                                                           | p reference<br>Iown referen | generator<br>ice generato      | or if unused b         | by LVD, BOI  | R, or VRL    |              |  |  |  |  |

| bit 6   | VRLEN: Vo                  | ltage Refer                                                                                                                                                   | ence Low E                  | nable bit (VF                  | RL = 2.048V            | nominal)     |              |              |  |  |  |  |

|         |                            | · •                                                                                                                                                           | p reference<br>Iown referen | generator<br>ice generato      | or if unused b         | oy LVD, BOI  | R, or VRH    |              |  |  |  |  |

| bit 5   | VRHOEN:                    | High Voltage                                                                                                                                                  | e Reference                 | Output Ena                     | ble bit <sup>(1)</sup> |              |              |              |  |  |  |  |

|         |                            |                                                                                                                                                               |                             | e is output o<br>ised internal |                        | abled (VRHE  | EN = 1)      |              |  |  |  |  |

| bit 4   | VRLOEN:                    | Low Voltage                                                                                                                                                   | Reference                   | Output Enal                    | ole bit                |              |              |              |  |  |  |  |

|         |                            | <ul> <li>1 = Enabled, VRL analog reference is output on RA2 if enabled (VRLEN = 1)</li> <li>0 = Disabled, analog reference is used internally only</li> </ul> |                             |                                |                        |              |              |              |  |  |  |  |

| bit 3-0 | Unimplemented: Read as '0' |                                                                                                                                                               |                             |                                |                        |              |              |              |  |  |  |  |

|         |                            |                                                                                                                                                               |                             | configured a<br>EL on page 2   | • •                    | outs when th | e VREF outpu | ut functions |  |  |  |  |

## REGISTER 10-2: VOLTAGE REFERENCE CONTROL REGISTER (REFCON: 9BH)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Low-voltage detection

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type RESETS only (POR, BOR), designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The INTRC and ER oscillator options save system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, Brown-out Reset and its trip point, the Power-up Timer, the watchdog timer and the devices Oscillator mode. As can be seen in Register 12-1, some additional configuration word bits have been provided for Brown-out Reset trip point selection.

## 12.3 RESET

The PIC16C717/770/771 devices have several different RESETS. These RESETS are grouped into two classifications; power-up and non-power-up. The power-up type RESETS are the Power-on and Brownout Resets which assume the device VDD was below its normal operating range for the device's configuration. The non power-up type RESETS assume normal operating limits were maintained before/during and after the RESET.

- Power-on Reset (POR)

- Programmable Brown-out Reset (PBOR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

Some registers are not affected in any RESET condition. Their status is unknown on a Power-up Reset and unchanged in any other RESET. Most other registers are placed into an initialized state upon RESET, however they are not affected by a WDT Reset during SLEEP, because this is considered a WDT Wake-up, which is viewed as the resumption of normal operation.

Several status bits have been provided to indicate which RESET occurred (see Table 12-4). See Table 12-6 for a full description of RESET states of all registers.

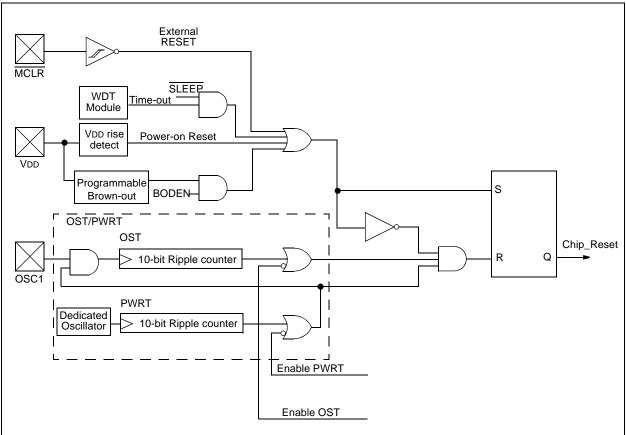

A simplified block diagram of the On-Chip Reset circuit is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

#### FIGURE 12-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked by the POR pulse. When the PWRT delay expires, the Oscillator Start-up Timer is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 12-6, Figure 12-7, Figure 12-8 and Figure 12-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 12-8). This is useful for testing purposes or to synchronize more than one PIC<sup>®</sup> microcontroller operating in parallel.

Table 12-5 shows the RESET conditions for some special function registers, while Table 12-6 shows the RESET conditions for all the registers.

#### 12.9 Power Control/STATUS Register (PCON)

The Power Control/STATUS Register, PCON, has two status bits that provide indication of which power-up type RESET occurred.

Bit0 is Brown-out Reset Status bit, BOR. The BOR bit is unknown upon a POR. BOR must be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power-up         |           | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | TPWRT + 1024Tosc | 1024Tosc  | TPWRT + 1024Tosc | 1024Tosc     |  |

| EC, ER, INTRC            | TPWRT            | _         | TPWRT            | _            |  |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |  |

|---------------------------------------|--------------------|--------------------|------------------|--|

| Power-on Reset                        | 000h               | 0001 1xxx          | 1-0x             |  |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 1-uu             |  |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 1-uu             |  |

| WDT Reset                             | 000h               | 0000 luuu          | 1-uu             |  |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | u-uu             |  |

| Brown-out Reset                       | 000h               | 0001 luuu          | 1-u0             |  |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuul Ouuu          | u-uu             |  |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuul 0uuu          | u-uu             |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

# PIC16C717/770/771

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                                   |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                            |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                            |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                        |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                     |  |  |  |  |

| Description:     | h: Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                 |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |

| SWAPF            | Swap Nybbles in f                                                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                         |  |  |  |  |

| Description:     | The upper and lower nybbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W regis-<br>ter. If 'd' is 1, the result is placed in<br>register 'f'. |  |  |  |  |

## 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>TM</sup> 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

## 14.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

## 14.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

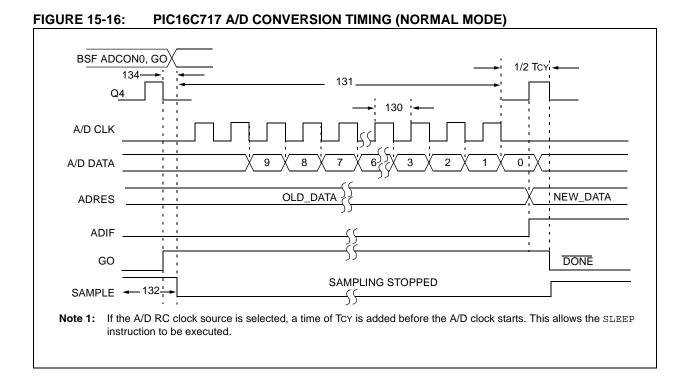

#### TABLE 15-15: PIC16C717 AND PIC16LC717 A/D CONVERSION REQUIREMENT (NORMAL MODE)

| Parameter<br>No. | Sym  | Characteristic                                                     | Min      | Тур†   | Max | Units | Conditions                                                                                                                                                                                                               |

|------------------|------|--------------------------------------------------------------------|----------|--------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <b>(3)</b>  | TAD  | A/D clock period                                                   | 1.6      | _      | —   | μS    | Tosc based, VREF $\ge 2.5V$                                                                                                                                                                                              |

|                  |      |                                                                    | 3.0      | —      | _   | μS    | Tosc based, VREF full range                                                                                                                                                                                              |

|                  |      |                                                                    | 3.0      | 6.0    | 9.0 | μs    | ADCS<1:0> = 11 (A/D RC mode)<br>At VDD = 2.5V                                                                                                                                                                            |

|                  |      |                                                                    | 2.0      | 4.0    | 6.0 | μS    | At VDD = $5.0V$                                                                                                                                                                                                          |

| 131*             | ΤΟΝΥ | Conversion time (not<br>including<br>acquisition time)<br>(Note 1) | _        | 11 Tad | _   | Tad   |                                                                                                                                                                                                                          |

| 132*             | TACQ | Acquisition Time                                                   | (Note 2) | 11.5   | —   | μS    |                                                                                                                                                                                                                          |

|                  |      |                                                                    | 5*       | _      | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1LSb (i.e.,<br>1mV @ 4.096V) from the last sam-<br>pled voltage (as stated on CHOLD). |

| 134*             | Tgo  | Q4 to A/D clock start                                              | _        | Tosc/2 | _   | _     |                                                                                                                                                                                                                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 11.6 for minimum conditions.

**3:** These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

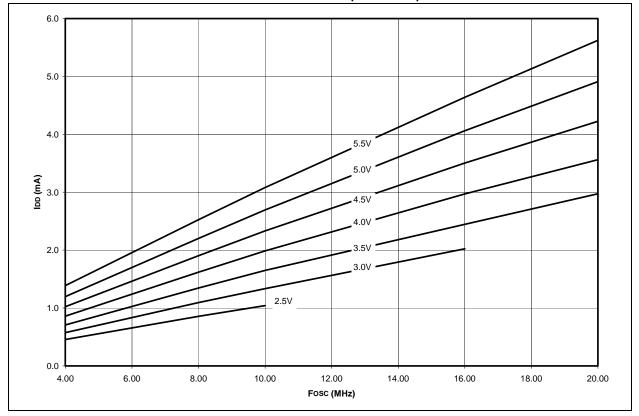

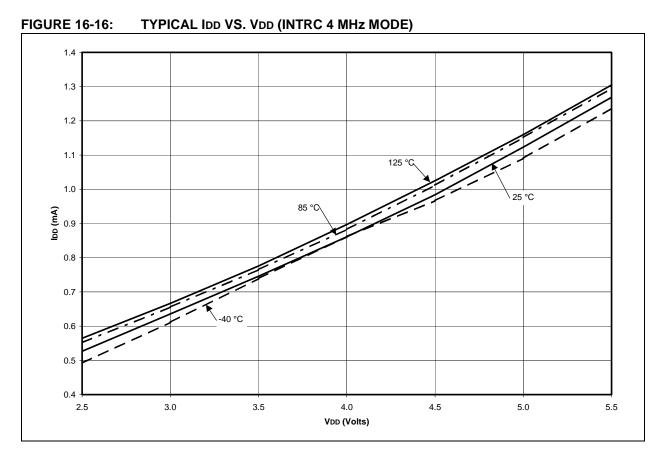

## 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

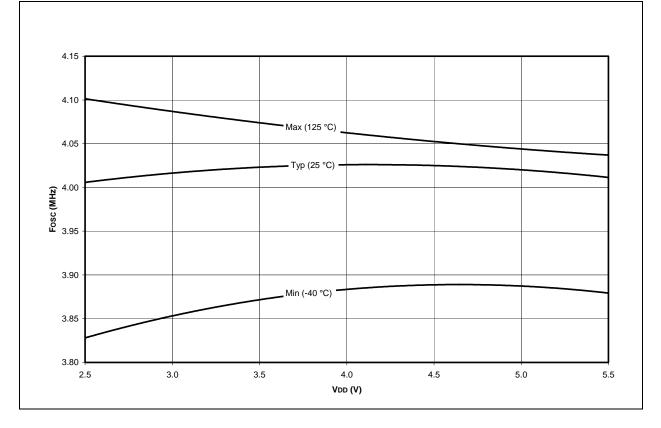

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

The FOSC IDD was determined using an external sinusoidal clock source with a peak amplitude ranging from VSS to VDD.

FIGURE 16-1: MAXIMUM IDD VS. FOSC OVER VDD (HS MODE)

FIGURE 16-17: INTERNAL RC Fosc VS. VDD OVER TEMPERATURE (4 MHz)