# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | PIC                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 15                                                                    |

| Program Memory Size        | 3.5KB (2K x 14)                                                       |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                |                                                                       |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                             |

| Data Converters            | A/D 6x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                       |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                               |

| Supplier Device Package    | 20-PDIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c770-p |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

|  | TABLE 2-1: | PIC16C717/770/771 SPECIAL FUNCTION REGISTER SUMMARY |

|--|------------|-----------------------------------------------------|

|--|------------|-----------------------------------------------------|

| Address              | Name    | Bit 7                                                                       | Bit 6           | Bit 5          | Bit 4           | Bit 3        | Bit 2         | Bit 1          | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>Page: |

|----------------------|---------|-----------------------------------------------------------------------------|-----------------|----------------|-----------------|--------------|---------------|----------------|---------|--------------------------|------------------------|

| Bank 0               |         |                                                                             |                 |                |                 |              |               |                |         |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing                                                                  | this location   | uses content   | s of FSR to ad  | dress data m | emory (not a  | a physical ree | gister) | 0000 0000                | 23                     |

| 01h                  | TMR0    | Timer0 mod                                                                  | lule's registe  | r              |                 |              |               |                |         | xxxx xxxx                | 45                     |

| 02h <sup>(3)</sup>   | PCL     | Program Co                                                                  | ounter's (PC)   | Least Signifi  | cant Byte       |              |               |                |         | 0000 0000                | 22                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                                                                         | RP1             | RP0            | TO              | PD           | Z             | DC             | С       | 0001 1xxx                | 14                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect data                                                               | a memory ad     | dress pointer  |                 |              |               |                |         | XXXX XXXX                | 23                     |

| 05h                  | PORTA   | RA7                                                                         | RA6             | RA5            | RA4             | RA3          | RA2           | RA1            | RA0     | xxxx 0000                | 25                     |

| 06h                  | PORTB   | RB7                                                                         | RB6             | RB5            | RB4             | RB3          | RB2           | RB1            | RB0     | xxxx xx11                | 33                     |

| 07h                  | -       | Unimpleme                                                                   | nted            |                |                 |              |               |                |         | -                        | _                      |

| 08h                  | _       | Unimpleme                                                                   | nted            |                |                 |              |               |                |         | _                        | _                      |

| 09h                  | _       | Unimpleme                                                                   | nted            |                |                 |              |               |                |         | _                        | _                      |

| 0Ah <sup>(1,3)</sup> | PCLATH  | —                                                                           | —               | —              | Write Buffer f  | or the upper | 5 bits of the | Program Cou    | unter   | 0 0000                   | 22                     |

| 0Bh <b>(3)</b>       | INTCON  | GIE                                                                         | PEIE            | TOIE           | INTE            | RBIE         | TOIF          | INTF           | RBIF    | 0000 000x                | 16                     |

| 0Ch                  | PIR1    | _                                                                           | ADIF            | _              | _               | SSPIF        | CCP1IF        | TMR2IF         | TMR1IF  | -00000                   | 18                     |

| 0Dh                  | PIR2    | LVDIF                                                                       | _               | _              | _               | BCLIF        | —             | _              | _       | 0                        | 20                     |

| 0Eh                  | TMR1L   | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                 |                |                 |              |               |                |         | xxxx xxxx                | 47                     |

| 0Fh                  | TMR1H   | Holding reg                                                                 | ister for the I | Most Significa | int Byte of the | 16-bit TMR1  | register      |                |         | xxxx xxxx                | 47                     |

| 10h                  | T1CON   | —                                                                           | —               | T1CKPS1        | T1CKPS0         | T1OSCEN      | T1SYNC        | TMR1CS         | TMR10N  | 00 0000                  | 47                     |

| 11h                  | TMR2    | Timer2 mod                                                                  | lule's registe  | r              |                 |              |               |                |         | 0000 0000                | 51                     |

| 12h                  | T2CON   | —                                                                           | TOUTPS3         | TOUTPS2        | TOUTPS1         | TOUTPS0      | TMR2ON        | T2CKPS1        | T2CKPS0 | -000 0000                | 51                     |

| 13h                  | SSPBUF  | Synchronou                                                                  | is Serial Port  | Receive Buf    | fer/Transmit R  | egister      |               |                |         | XXXX XXXX                | 70                     |

| 14h                  | SSPCON  | WCOL                                                                        | SSPOV           | SSPEN          | СКР             | SSPM3        | SSPM2         | SSPM1          | SSPM0   | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/Co                                                                  | mpare/PWM       | Register1 (L   | SB)             |              |               |                |         | XXXX XXXX                | 54                     |

| 16h                  | CCPR1H  | Capture/Co                                                                  | mpare/PWM       | Register1 (M   | ISB)            |              |               |                |         | XXXX XXXX                | 54                     |

| 17h                  | CCP1CON | PWM1M1                                                                      | PWM1M0          | DC1B1          | DC1B0           | CCP1M3       | CCP1M2        | CCP1M1         | CCP1M0  | 0000 0000                | 53                     |

| 18h                  | —       | Unimpleme                                                                   | nted            |                |                 |              |               |                |         | _                        | _                      |

| 19h                  | —       | Unimplemented                                                               |                 |                |                 |              |               |                |         | -                        | _                      |

| 1Ah                  | -       | Unimplemented                                                               |                 |                |                 |              |               |                |         | -                        | _                      |

| 1Bh                  | _       | Unimplemented                                                               |                 |                |                 |              |               |                |         | _                        | _                      |

| 1Ch                  | _       | Unimplemented                                                               |                 |                |                 |              |               |                |         | _                        | —                      |

| 1Dh                  | _       | Unimplemented                                                               |                 |                |                 |              |               |                |         | _                        | —                      |

| 1Eh                  | ADRESH  | A/D High B                                                                  | yte Result Re   | egister        |                 |              |               |                |         | xxxx xxxx                | 107                    |

| 1Fh                  | ADCON0  | ADCS1                                                                       | ADCS0           | CHS2           | CHS1            | CHS0         | GO/DONE       | CHS3           | ADON    | 0000 0000                | 107                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

3: These registers can be addressed from any bank.

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |

|-------|---------------------------------------------|

|       | and digit borrow bit, respectively, in sub- |

|       | traction. See the SUBLW and SUBWF           |

|       | instructions for examples.                  |

#### REGISTER 2-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

|         | R/W-0            | R/W-0                              | R/W-0        | R-1            | R-1          | R/W-x        | R/W-x          | R/W-x        |

|---------|------------------|------------------------------------|--------------|----------------|--------------|--------------|----------------|--------------|

|         | IRP              | RP1                                | RP0          | TO             | PD           | Z            | DC             | С            |

|         | bit 7            |                                    |              |                |              |              |                | bit 0        |

|         |                  |                                    |              |                |              |              |                |              |

| bit 7   |                  | ter Bank Sel                       |              | d for indirect | addressing   | a)           |                |              |

|         |                  | , 3 (100h - 1<br>, 1 (00h - FF     |              |                |              |              |                |              |

| bit 6-5 |                  | Register Ban                       |              | s (used for o  | lirect addre | ssing)       |                |              |

|         |                  | 3 (180h - 1F<br>2 (100h - 17       |              |                |              |              |                |              |

|         |                  | 1 (80h - FFh                       |              |                |              |              |                |              |

|         | 00 <b>= Bank</b> | 0 (00h - 7Fh                       | )            |                |              |              |                |              |

|         |                  | is 128 bytes                       | i            |                |              |              |                |              |

| bit 4   | TO: Time-c       |                                    |              | tion of at t   |              | ion          |                |              |

|         | -                | ower-up, CLI                       |              |                |              | ION          |                |              |

| bit 3   | PD: Power        | -down bit                          |              |                |              |              |                |              |

|         |                  | ower-up or b                       |              |                | n            |              |                |              |

|         | -                | cution of the                      | SLEEP inst   | ruction        |              |              |                |              |

| bit 2   | Z: Zero bit      |                                    | h            |                |              |              |                |              |

|         |                  | sult of an arit<br>sult of an arit |              |                |              | 0            |                |              |

| bit 1   |                  | arry/borrow                        |              | •              |              |              | (for borrow    | the polarity |

|         | •                | -out from the<br>ry-out from th    |              |                |              | urred        |                |              |

| bit 0   | C: Carry/bo      | orrow bit (AD                      | DWF, ADDLW   | , SUBLW, SU    | JBWF instru  | ictions)     |                |              |

|         | •                | -out from the                      | •            |                |              |              |                |              |

|         | 0 = No cari      | ry-out from tl                     | ne Most Sigi | nificant bit o | f the result | occurred     |                |              |

|         | Note:            | For borrow.                        | the polarity | is reversed.   | A subtract   | ion is execu | ted by addin   | a the two's  |

|         | (                | complement                         | of the seco  | nd operand     | For rotate   | (RRF, RLF    | ) instructions |              |

|         | I                | oaded with e                       |              |                |              | e source reg |                |              |

|         | Legend:          |                                    |              |                |              |              |                |              |

|         | R = Reada        | ble bit                            | W = W        | ritable bit    | U = Unir     | nplemented   | bit, read as ' | 0'           |

|         | - n = Value      | at POR                             | '1' = Bi     | t is set       | '0' = Bit    | is cleared   | x = Bit is u   | nknown       |

#### TABLE 3-1: PORTA FUNCTIONS

| Name              | Function | Input<br>Type | Output<br>Type | Description                                 |

|-------------------|----------|---------------|----------------|---------------------------------------------|

|                   | RA0      | ST            | CMOS           | Bi-directional I/O                          |

| RA0/AN0           | AN0      | AN            |                | A/D input                                   |

|                   | RA1      | ST            | CMOS           | Bi-directional I/O                          |

| RA1/AN1/LVDIN     | AN1      | AN            |                | A/D input                                   |

|                   | LVDIN    | AN            |                | LVD input reference                         |

|                   | RA2      | ST            | CMOS           | Bi-directional I/O                          |

| RA2/AN2/VREF-/VRL | AN2      | AN            |                | A/D input                                   |

| RAZ/ANZ/VREF-/VRL | VREF-    | AN            |                | Negative analog reference input             |

|                   | VRL      |               | AN             | Internal voltage reference low output       |

|                   | RA3      | ST            | CMOS           | Bi-directional I/O                          |

| RA3/AN3/VREF+/VRH | AN3      | AN            |                | A/D input                                   |

| KA3/AN3/VREF+/VRH | VREF+    | AN            |                | Positive analog reference input             |

|                   | VRH      |               | AN             | Internal voltage reference high output      |

| RA4/T0CKI         | RA4      | ST            | OD             | Bi-directional I/O                          |

|                   | TOCKI    | ST            |                | TMR0 clock input                            |

|                   | RA5      | ST            |                | Input port                                  |

| RA5/MCLR/VPP      | MCLR     | ST            |                | Master clear                                |

|                   | Vpp      | Power         |                | Programming voltage                         |

|                   | RA6      | ST            | CMOS           | Bi-directional I/O                          |

| RA6/OSC2/CLKOUT   | OSC2     |               | XTAL           | Crystal/resonator                           |

|                   | CLKOUT   |               | CMOS           | FOSC/4 output                               |

|                   | RA7      | ST            | CMOS           | Bi-directional I/O                          |

| RA7/OSC1/CLKIN    | OSC1     | XTAL          |                | Crystal/resonator                           |

|                   | CLKIN    | ST/AN         |                | External clock input/ER resistor connection |

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                                    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA                                   | RA7   | RA6   | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   | xxxx 0000                | uuuu 0000                       |

| 85h     | 85h TRISA PORTA Data Direction Register |       |       |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 9Dh     | ANSEL                                   | —     | —     | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  | 11 1111                  | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

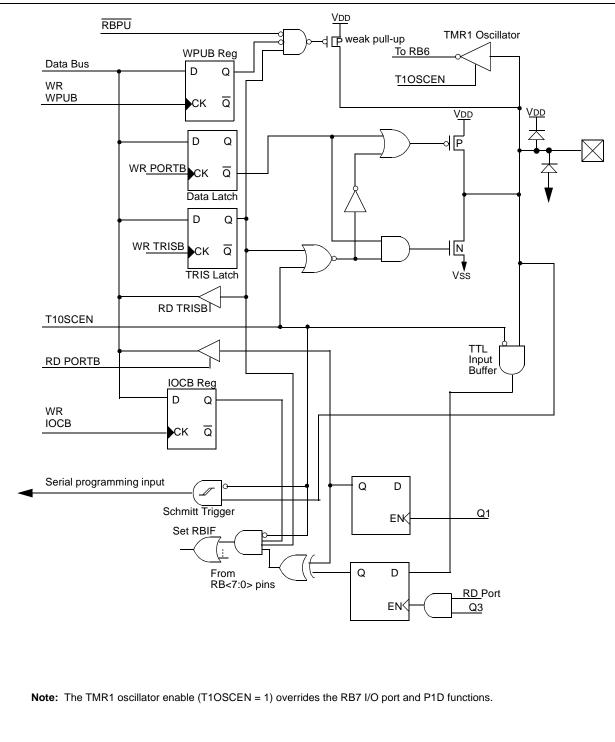

#### FIGURE 3-10: BLOCK DIAGRAM OF THE RB7/T10SI/P1D

#### 8.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only an ECCP interrupt is generated (if enabled).

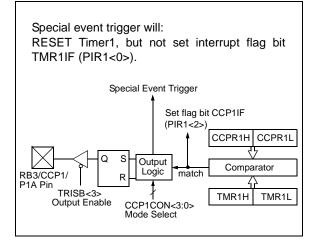

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of ECCP resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of ECCP module will also start an A/D conversion if the A/D module is enabled.

**Note:** The special event trigger will not set the interrupt flag bit TMR1IF (PIR1<0>).

#### FIGURE 8-2:

#### COMPARE MODE OPERATION BLOCK DIAGRAM

#### TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Name    | Bit 7                | Bit 6                                            | Bit 5          | Bit 4          | Bit 3          | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|----------------------|--------------------------------------------------|----------------|----------------|----------------|----------|--------|--------|-------------------------|---------------------------------|

| INTCON  | GIE                  | PEIE                                             | TOIE           | INTE           | RBIE           | T0IF     | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF                                             | RCIF           | TXIF           | SSPIF          | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE                                             | RCIE           | TXIE           | SSPIE          | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| TRISB   | PORTB Data           | a Direction Reg                                  | gister         |                |                |          |        |        | 1111 1111               | 1111 1111                       |

| TMR1L   | Holding regi         | ster for the Lea                                 | ast Significar | nt Byte of the | e 16-bit TMR1  | register |        |        | XXXX XXXX               | uuuu uuuu                       |

| TMR1H   | Holding regi         | ster for the Mo                                  | st Significan  | t Byte of the  | e 16-bit TMR1r | egister  |        |        | XXXX XXXX               | uuuu uuuu                       |

| T1CON   | -                    | T1CKPS T1CKP T1OSCEN TISYNC TMR1CS TMR10<br>1 S0 |                |                |                |          |        |        |                         | uu uuuu                         |

| CCPR1L  | Capture/Cor          | XXXX XXXX                                        | uuuu uuuu      |                |                |          |        |        |                         |                                 |

| CCPR1H  | Capture/Cor          | xxxx xxxx                                        | uuuu uuuu      |                |                |          |        |        |                         |                                 |

| CCP1CON | PWM1M1               | PWM1M0                                           | DC1B1          | DC1B0          | CCP1M3         | CCP1M2   | CCP1M1 | CCP1M0 | 0000 0000               | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

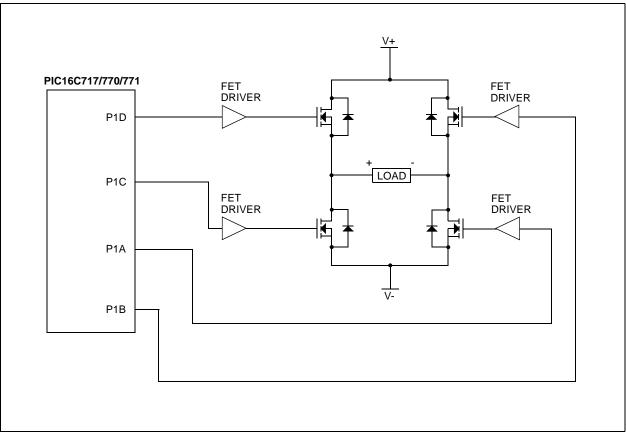

FIGURE 8-9: EXAMPLE OF FULL-BRIDGE APPLICATION

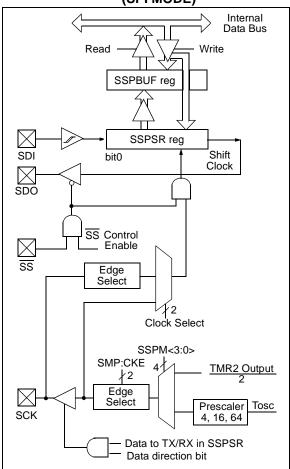

#### 9.1 SPI Mode

The SPI mode allows eight bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

#### 9.1.1 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

Figure 9-1 shows the block diagram of the MSSP module when in SPI mode.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

The MSSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer Register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF (PIR1<3>), are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSP-BUF register completed successfully.

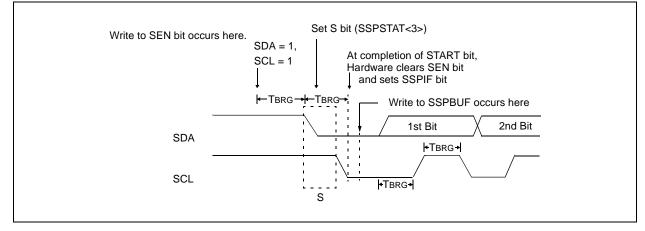

#### 9.2.10 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, indicating that the bus is available, the baud rate generator is loaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG) indicating the bus is still available, the SDA pin is driven low. The SDA transition from high to low while SCL is high is the START condition. This causes the S bit (SSPSTAT<3>) to be set. When the S bit is set, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG) the START condition is complete, concurrent with the following events:

- The SEN bit (SSPCON2<0>) is automatically cleared by hardware,

- The baud rate generator is suspended leaving the SDA line held low.

- The SSPIF flag is set.

Note: If at the beginning of START condition, the SDA and SCL pins are already sampled low, or if during the START condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs. Thus, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is RESET into its IDLE state.

#### 9.2.10.1 WCOL STATUS FLAG

If the user writes the SSPBUF when a START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower five bits of SSPCON2 is disabled until the START condition is complete.

#### FIGURE 9-16: FIRST START BIT TIMING

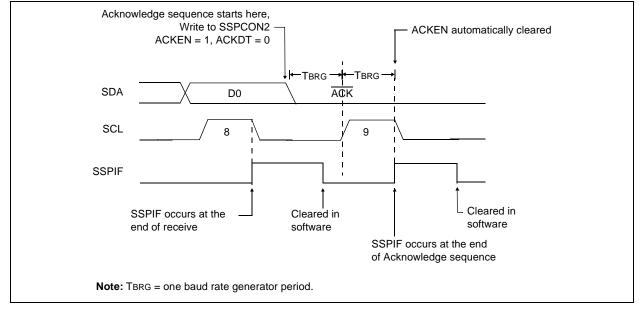

### 9.2.14 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit ACKDT (SSPCON2<5>) is presented on the SDA pin. If the user wishes to generate an Acknowledge (ACK), then the ACKDT bit should be cleared. Otherwise, the user should set the ACKDT bit (NACK) before starting an Acknowledge sequence. The baud rate generator is then loaded from SSPADD<6:0> and counts for one rollover period (TBRG). The SCL pin is then de-asserted (pulled high). When the SCL pin is sampled high (clock

arbitration), the baud rate generator is reloaded and counts for another TBRG. At the completion of the TBRG period, the following events occur (see Figure 9-20):

- The SCL pin is pulled low.

- The ACKEN bit is automatically cleared.

- The baud rate generator is turned off.

- The MSSP module goes into IDLE mode.

#### 9.2.14.1 WCOL STATUS FLAG

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-20: ACKNOWLEDGE SEQUENCE WAVEFORM

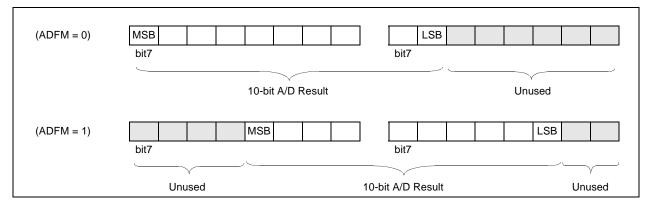

#### FIGURE 11-2: PIC16C717 10-BIT A/D RESULT FORMAT

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS and ANSEL bits selected as an input. To determine acquisition time, see Section 11.6. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

#### 11.2 Configuring the A/D Module

#### 11.2.1 CONFIGURING ANALOG PORT PINS

The ANSEL and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted. The proper ANSEL bits must be set (analog input) to disable the digital input buffer.

The A/D operation is independent of the state of the TRIS bits and the ANSEL bits.

- Note 1: When reading the PORTA register, all pins configured as analog input channels will read as '0'.

- 2: When reading the PORTB register, all pins configured as analog pins on PORTB will be read as '1'.

- **3:** Analog levels on any pin that is defined as a digital input, including the ANx pins, may cause the input buffer to consume current that is out of the devices specification.

### 11.2.2 CONFIGURING THE REFERENCE VOLTAGES

The VCFG bits in the ADCON1 register configure the A/D module reference inputs. The reference high input can come from an internal reference (VRH) or (VRL), an external reference (VREF+), or AVDD. The low reference input can come from an internal reference (VRL), an external reference (VREF-), or AVss. If an external reference is chosen for the reference high or reference low inputs, the port pin that multiplexes the incoming external references is configured as an analog input, regardless of the values contained in the A/D port configuration bits (PCFG<3:0>).

#### 11.3 Selecting the A/D Conversion Clock

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. If neither the internal VRH nor VRL are used for the A/D converter, the four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- A/D RC oscillator

If the VRH or VRL are used for the A/D converter reference, then the TAD requirement is automatically increased by a factor of 8.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

| A/D Reference<br>Source | A/D Clock | Source (TAD) | Device Frequency            |                             |                             |                               |  |  |

|-------------------------|-----------|--------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--|--|

|                         | Operation | ADCS<1:0>    | 20 MHz                      | 5 MHz                       | 4 MHz                       | 1.25 MHz                      |  |  |

|                         | 2 Tosc    | 00           | 100 ns <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.6 μs                        |  |  |

| External VREF or        | 8 Tosc    | 01           | 400 ns <sup>(2)</sup>       | 1.6 μs                      | 2.0 μs                      | 6.4 μs                        |  |  |

| Analog Supply           | 32 Tosc   | 10           | 1.6 μs                      | 6.4 μs <sup>(3)</sup>       | 8.0 μs <sup>(3)</sup>       | 25.6 μs <sup>(3)</sup>        |  |  |

|                         | A/D RC    | 11           | 2 - 6 μs <sup>(1,4)</sup>     |  |  |

| Internal VRH or         | 16 Tosc   | 00           | 800 ns <sup>(2)</sup>       | 3.2 μs <sup>(2)</sup>       | 4 μs <sup>(2)</sup>         | 12.8 μs                       |  |  |

| VRL                     | 64 Tosc   | 01           | 3.2 μs <sup>(2)</sup>       | 12.8 μs                     | 16 μs                       | 51.2 μs <b><sup>(3)</sup></b> |  |  |

|                         | 256 Tosc  | 10           | 12.8 μs                     | 51.2 μs <sup>(3)</sup>      | 64 μs <sup>(3)</sup>        | 204.8 μs <sup>(3)</sup>       |  |  |

|                         | A/D RC    | 11           | 16 - 48 μs <sup>(4,5)</sup>   |  |  |

#### TABLE 11-1: TAD vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

5: A/D RC clock source has a typical TAD time of 32  $\mu$ s for VDD > 3.0V.

#### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked by the POR pulse. When the PWRT delay expires, the Oscillator Start-up Timer is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 12-6, Figure 12-7, Figure 12-8 and Figure 12-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 12-8). This is useful for testing purposes or to synchronize more than one PIC<sup>®</sup> microcontroller operating in parallel.

Table 12-5 shows the RESET conditions for some special function registers, while Table 12-6 shows the RESET conditions for all the registers.

#### 12.9 Power Control/STATUS Register (PCON)

The Power Control/STATUS Register, PCON, has two status bits that provide indication of which power-up type RESET occurred.

Bit0 is Brown-out Reset Status bit, BOR. The BOR bit is unknown upon a POR. BOR must be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power            | -up       | Brown-out        | Wake-up from |

|--------------------------|------------------|-----------|------------------|--------------|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |

| XT, HS, LP               | TPWRT + 1024Tosc | 1024Tosc  | TPWRT + 1024Tosc | 1024Tosc     |

| EC, ER, INTRC            | TPWRT            | _         | TPWRT            | —            |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |

|---------------------------------------|--------------------|--------------------|------------------|

| Power-on Reset                        | 000h               | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 1-uu             |

| WDT Reset                             | 000h               | 0000 luuu          | 1-uu             |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | u-uu             |

| Brown-out Reset                       | 000h               | 0001 luuu          | 1-u0             |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuul Ouuu          | u-uu             |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead making this a $2Tcy$ instruction. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                        |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                                       |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                           |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                     | Syntax:          | [label] CLRWDT                                                                                                                 |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                          | Operands:        | None                                                                                                                           |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                 | Operation:       | $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$                               |  |

| Status Affected: | None                                                                                                                                                                                                        |                  | $1 \rightarrow PD$                                                                                                             |  |

| Description:     | Call Subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                         |  |

|                  | address (PC+1) is pushed onto<br>the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two cycle instruction. | Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set. |  |

NOTES:

| PIC16L0       | C717/770         | /771                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                      |     | $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$0^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                            |  |

|---------------|------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------|----------------------------|--|

| PIC16C7       | IC16C717/770/771 |                                   |                                                                                                                                                                                                                                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                                                                                                            |                            |  |

| Param.<br>No. | Sym              | Characteristic                    | Min                                                                                                                                                                                                                                         | Тур†                                                 | Max | Units                                                                                                      | Conditions                 |  |

|               | IPD              | Power-down Current <sup>(3)</sup> |                                                                                                                                                                                                                                             |                                                      |     |                                                                                                            |                            |  |

| D020D         |                  | PIC16LC7XX                        |                                                                                                                                                                                                                                             | 0.3                                                  | 2.0 | μA                                                                                                         | VDD = 3V, -40°C to 85°C    |  |

| D020E         |                  |                                   |                                                                                                                                                                                                                                             |                                                      | 5.0 |                                                                                                            | VDD = 3V, -40°C to 125°C   |  |

| D020F         |                  |                                   |                                                                                                                                                                                                                                             | 0.1                                                  | 1.5 | μA                                                                                                         | VDD = 2.5V, -40°C to 85°C  |  |

| D020G         |                  |                                   |                                                                                                                                                                                                                                             |                                                      | 3.0 |                                                                                                            | VDD = 2.5V, -40°C to 125°C |  |

| D020          |                  | PIC16C7XX                         |                                                                                                                                                                                                                                             | 1.4                                                  | 4.0 | μA                                                                                                         | VDD = 5.5V, -40°C to 85°C  |  |

| D020A         |                  |                                   |                                                                                                                                                                                                                                             |                                                      | 8.0 |                                                                                                            | VDD = 5.5V, -40°C to 125°C |  |

| D020B         |                  |                                   |                                                                                                                                                                                                                                             | 1.0                                                  | 3.5 | μΑ                                                                                                         | VDD = 4V, -40°C to 85°C    |  |

| D020C         |                  |                                   |                                                                                                                                                                                                                                             |                                                      | 6.0 |                                                                                                            | VDD = 4V, -40°C to 125°C   |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

$\frac{OSC1}{MCLR}$  = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\frac{MCLR}{MCLR}$  = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

| Param.<br>No. | Symbol  | Characteristic      |                           | Min              | Max  | Units | Conditions                        |

|---------------|---------|---------------------|---------------------------|------------------|------|-------|-----------------------------------|

| 100*          | Thigh   | Clock high time     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 101*          | TLOW    | Clock low time      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 102*          | TR      | SDA and SCL         | 100 kHz mode              | _                | 1000 | ns    | Cb is specified to be from        |

|               |         | rise time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                                   |

| 103*          | TF      | SDA and SCL         | 100 kHz mode              | _                | 300  | ns    | Cb is specified to be from        |

|               |         | fall time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns    |                                   |

| 90*           | TSU:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | Only relevant for Repeated        |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | START                             |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    | condition                         |

| 91*           | THD:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period the first clock |

|               |         | hold time           | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | pulse is generated                |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 106*          | THD:DAT | Data input          | 100 kHz mode              | 0                | —    | ns    |                                   |

|               |         | hold time           | 400 kHz mode              | 0                | 0.9  | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | —    | ns    |                                   |

| 107*          | TSU:DAT | Data input          | 100 kHz mode              | 250              | —    | ns    | Note 2                            |

|               |         | setup time          | 400 kHz mode              | 100              | —    | ns    | 1                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | -    | ns    |                                   |

| 92*           | Tsu:sto | STOP condition      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 109*          | TAA     | Output valid from   | 100 kHz mode              | _                | 3500 | ns    |                                   |

|               |         | clock               | 400 kHz mode              | —                | 1000 | ns    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | —                | —    | ns    |                                   |

| 110           | TBUF    | Bus free time       | 100 kHz mode              | 4.7 ‡            | —    | ms    | Time the bus must be free         |

|               |         |                     | 400 kHz mode              | 1.3 ‡            | —    | ms    | before a new transmission         |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD‡             | —    | ms    | can start                         |

| D102 ‡        | Cb      | Bus capacitive load |                           | —                | 400  | pF    |                                   |

#### TABLE 15-22: MASTER SSP I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested. For the value required by the I<sup>2</sup>C specification, please refer to the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023).

‡ These parameters are for design guidance only and are not tested, nor characterized.

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A Fast mode  $l^2C$  bus device can be used in a Standard mode  $l^2C$  bus system, but  $(TSU:DAT) \ge 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line.

[(TR) + (TSU:DAT) = 1000 + 250 = 1250 ns], for 100 kHz mode, before the SCL line is released.

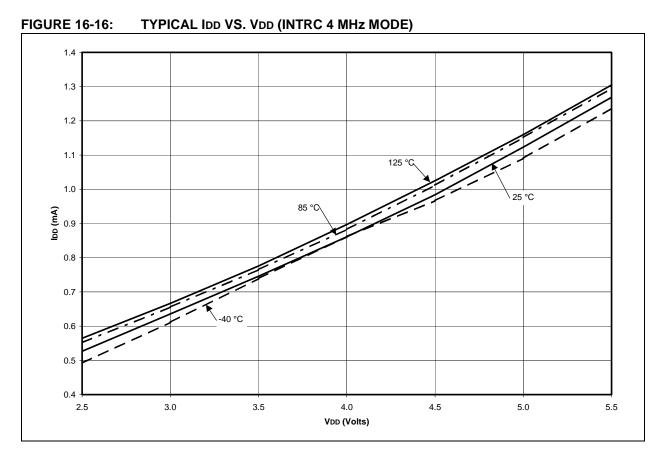

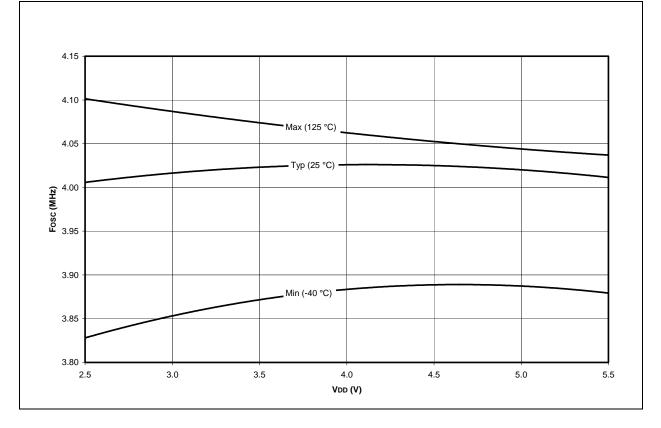

FIGURE 16-17: INTERNAL RC Fosc VS. VDD OVER TEMPERATURE (4 MHz)

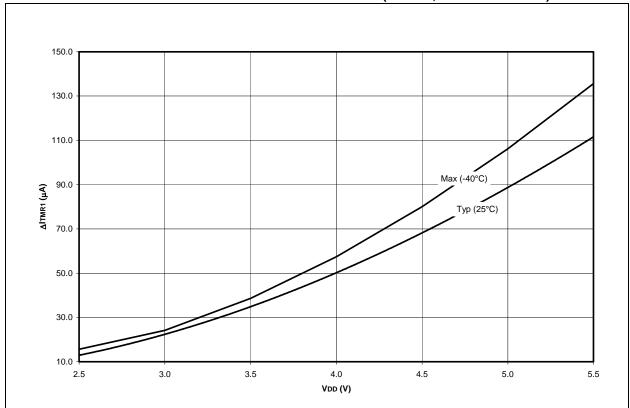

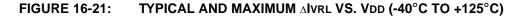

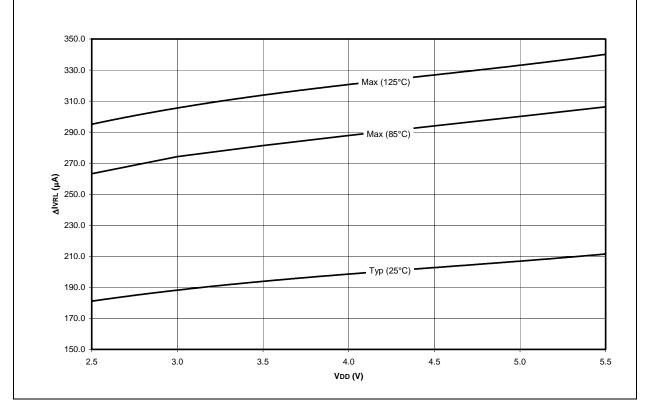

#### FIGURE 16-20: TYPICAL AND MAXIMUM AITMR1 VS. VDD (32 KHZ, -40°C TO +125°C)

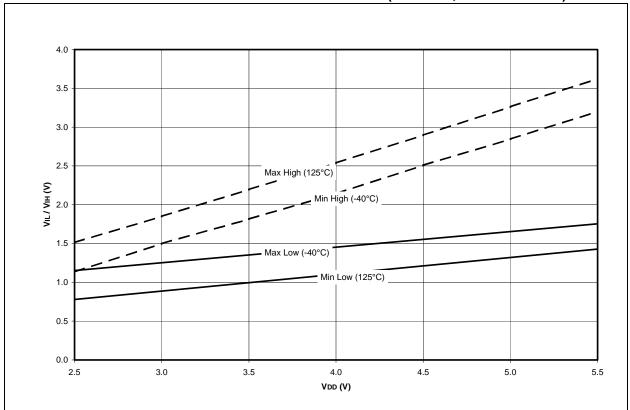

FIGURE 16-32: MINIMUM AND MAXIMUM VIH/VIL VS. VDD (ST INPUT,-40°C TO +125°C)

| Prescaler, Timer257                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select (T2CKPS Bits)51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PRO MATE II Universal Device Programmer143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Program Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PCL Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PCLATH Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Interrupt Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Paging9, 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Program Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| READ (PMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reset Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |