Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I²C, SPI                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 3.5KB (2K x 14)                                                        |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | A/D 6x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                         |

| Supplier Device Package    | 20-SSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c770-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PICmicro™ Mid-Range MCU Family Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data

sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are three devices (PIC16C717, PIC16C770 and PIC16C771) covered by this data sheet. The PIC16C717 device comes in 18/20-pin packages and the PIC16C770/771 devices come in 20-pin packages.

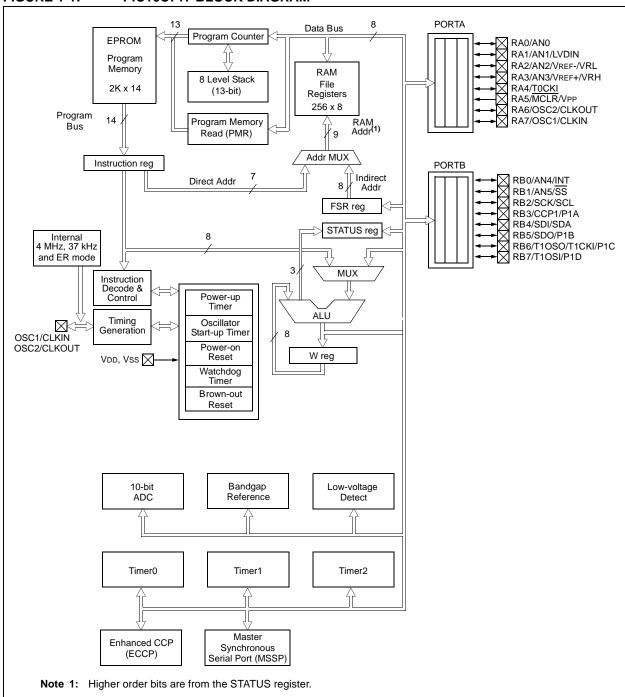

The following two figures are device block diagrams of the PIC16C717 and the PIC16C770/771.

FIGURE 1-1: PIC16C717 BLOCK DIAGRAM

TABLE 1-1: PIC16C717/770/771 PINOUT DESCRIPTION

| Name                        | Function | Input<br>Type | Output<br>Type | Description                                 |

|-----------------------------|----------|---------------|----------------|---------------------------------------------|

| DAO/ANO                     | RA0      | ST            | CMOS           | Bi-directional I/O                          |

| RA0/AN0                     | AN0      | AN            |                | A/D input                                   |

|                             | RA1      | ST            | CMOS           | Bi-directional I/O                          |

| RA1/AN1/LVDIN               | AN1      | AN            |                | A/D input                                   |

|                             | LVDIN    | AN            |                | LVD input reference                         |

|                             | RA2      | ST            | CMOS           | Bi-directional I/O                          |

| DAG/ANGA/oss A/DI           | AN2      | AN            |                | A/D input                                   |

| RA2/AN2/VREF-/VRL           | VREF-    | AN            |                | Negative analog reference input             |

|                             | VRL      |               | AN             | Internal voltage reference low output       |

|                             | RA3      | ST            | CMOS           | Bi-directional I/O                          |

| D 4 0 / 4 N 0 0 / 0 / D 1 1 | AN3      | AN            |                | A/D input                                   |

| RA3/AN3/VREF+/VRH           | VREF+    | AN            |                | Positive analog reference input             |

|                             | VRH      |               | AN             | Internal voltage reference high output      |

| DA 4/T0 O1/1                | RA4      | ST            | OD             | Bi-directional I/O                          |

| RA4/T0CKI                   | T0CKI    | ST            |                | TMR0 clock input                            |

|                             | RA5      | ST            |                | Input port                                  |

| RA5/MCLR/VPP                | MCLR     | ST            |                | Master clear                                |

|                             | VPP      | Power         |                | Programming voltage                         |

|                             | RA6      | ST            | CMOS           | Bi-directional I/O                          |

| RA6/OSC2/CLKOUT             | OSC2     |               | XTAL           | Crystal/resonator                           |

|                             | CLKOUT   |               | CMOS           | Fosc/4 output                               |

|                             | RA7      | ST            | CMOS           | Bi-directional I/O                          |

| RA7/OSC1/CLKIN              | OSC1     | XTAL          |                | Crystal/resonator                           |

|                             | CLKIN    | ST            |                | External clock input/ER resistor connection |

|                             | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB0/AN4/INT                 | AN4      | AN            |                | A/D input                                   |

|                             | INT      | ST            |                | Interrupt input                             |

|                             | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB1/AN5/SS                  | AN5      | AN            |                | A/D input                                   |

|                             | SS       | ST            |                | SSP slave select input                      |

|                             | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB2/SCK/SCL                 | SCK      | ST            | CMOS           | Serial clock I/O for SPI                    |

|                             | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C       |

|                             | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB3/CCP1/P1A                | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output            |

|                             | P1A      |               | CMOS           | PWM P1A output                              |

|                             | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB4/SDI/SDA                 | SDI      | ST            |                | Serial data in for SPI                      |

|                             | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C        |

|                             | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB5/SDO/P1B                 | SDO      |               | CMOS           | Serial data out for SPI                     |

|                             | P1B      |               | CMOS           | PWM P1B output                              |

Note 1: Bit programmable pull-ups.

2: Only in PIC16C770/771 devices.

### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

### REGISTER 2-2: OPTION REGISTER (OPTION\_REG: 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 **RBPU:** PORTB Pull-up Enable bit<sup>(1)</sup>

1 = PORTB weak pull-ups are disabled

0 = PORTB weak pull-ups are enabled by the WPUB register

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 **T0SE:** TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1 : 16    | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1:256     | 1 : 128  |

**Note 1:** Individual weak pull-up on RB pins can be enabled/disabled from the weak pull-up PORTB Register (WPUB).

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 4-2: PROGRAM MEMORY DATA HIGH (PMDATH: 10Eh)

| U-0   | U-0 | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------|-----|-------|-------|-------|-------|------|-------|

| _     | _   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9 | PMD8  |

| bit 7 |     |       |       |       |       |      | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

Legend:  $R = Readable \ bit \qquad W = Writable \ bit \qquad U = Unimplemented \ bit, \ read \ as \ '0' \\ -n = Value \ at \ POR \qquad '1' = Bit \ is \ set \qquad '0' = Bit \ is \ cleared \qquad x = Bit \ is \ unknown$

### REGISTER 4-3: PROGRAM MEMORY DATA LOW (PMDATL: 10Ch)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| PMD7  | PMD6 | PMD5 | PMD4 | PMD3 | PMD2 | PMD1 | PMD0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

### REGISTER 4-4: PROGRAM MEMORY ADDRESS HIGH (PMADRH: 10Fh)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | PMA11 | PMA10 | PMA9  | PMA8  |

| bit 7 |     |     |     |       |       |       | bit 0 |

bit 7-4 Unimplemented: Read as '0' bit 3-0 PMA<11:8>: PMR Address bits

### REGISTER 4-5: PROGRAM MEMORY ADDRESS LOW (PMADRL: 10Dh)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMA7  | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

### bit 7-0 **PMA<7:0>:** PMR Address bits

| Legend:            |                  |                                    |                    |  |

|--------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit, BF (SSPSTAT<0>), indicates when the SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

EXAMPLE 9-1: Loading the SSPBUF (SSPSR) Register

|      |       |          |     | <u>,                                     </u> |

|------|-------|----------|-----|-----------------------------------------------|

|      | BSF   | STATUS,  | RP0 | ;Specify Bank 1                               |

| LOOP | BTFSS | SSPSTAT, | BF  | ;Has data been                                |

|      |       |          |     | ;received                                     |

|      |       |          |     | ;(xmit complete)?                             |

|      | GOTO  | LOOP     |     | ; No                                          |

|      | BCF   | STATUS,  | RP0 | ;Specify Bank 0                               |

|      | MOVF  | SSPBUF,  | W   | ;Save SSPBUF                                  |

|      | MOVWF | RXDATA   |     | :in user RAM                                  |

|      | MOVF  | TXDATA,  | W   | Get next TXDATA                               |

|      | MOVWF | SSPBUF   |     | ;New data to xmit                             |

| 1    |       |          |     |                                               |

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP STATUS register (SSPSTAT) indicates the various status conditions.

#### 9.1.2 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISB<5> cleared

- SCK (Master mode) must have TRISB<2> cleared

- SCK (Slave mode) must have TRISB<2> set

- SS must have TRISB<1> set, and ANSEL<5> cleared

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

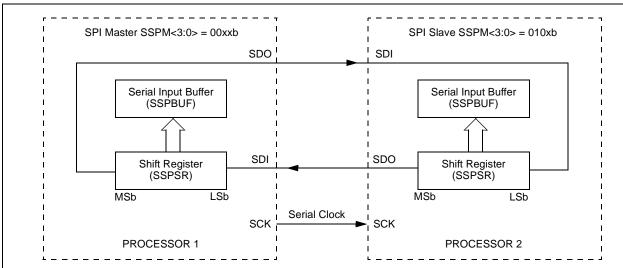

#### 9.1.3 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (SSPCON<4>), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

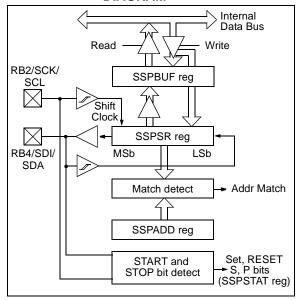

### 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware to determine when the bus is free (multimaster function). The MSSP module implements the Standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used to transfer data. They are the SCL pin (clock) and the SDA pin (data). The MSSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>). The SCL and SDA pins are "glitch" filtered when operating as inputs. This filter functions in both the 100 kHz and 400 kHz modes. When these pins operate as outputs in the 100 kHz mode, there is a slew rate control of the pin that is independent of device frequency.

Before selecting any I<sup>2</sup>C mode, the SCL and SDA pins must be programmed as inputs by setting the appropriate TRIS bits. This allows the MSSP module to configure and drive the I/O pins as required by the I<sup>2</sup>C protocol.

The MSSP module has six registers for  $I^2C$  operation. They are listed below.

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP STATUS Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows for control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) configure the MSSP as any one of the following I<sup>2</sup>C modes:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode

SCL Freq = Fosc / [4 (SSPADD + 1)]

- I<sup>2</sup>C Slave mode with START and STOP interrupts (7-bit address)

- I<sup>2</sup>C Slave mode with START and STOP interrupts (10-bit address)

- · Firmware Controlled Master mode

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit. It specifies whether the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written, and from which the transfer data is read. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled, buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is

transferred from the SSPSR register to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read a receiver overflow occurs, in which case, the SSPOV bit (SSPCON<6>) is set and the byte in the SSPSR is lost.

FIGURE 9-7: I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

### 9.2.1 UPWARD COMPATIBILITY WITH SSP MODULE

The MSSP module includes three SSP modes of operation to maintain upward compatibility with the SSP module. These modes are:

- Firmware controlled Master mode (slave idle)

- 7-bit Slave mode with START and STOP condition interrupts.

- 10-bit Slave mode with START and STOP condition interrupts.

The firmware controlled Master mode enables the START and STOP condition interrupts but all other I<sup>2</sup>C functions are generated through firmware including:

- Generating the START and STOP conditions

- Generating the SCL clock

- Supplying the SDA bits in the proper time and phase relationship to the SCL signal.

In firmware controlled Master mode, the SCL and SDA lines are manipulated by clearing and setting the corresponding TRIS bits. The output level is always low irrespective of the value(s) in the PORT register. A '1' is output by setting the TRIS bit and a '0' is output by clearing the TRIS bit

The 7-bit and 10-bit Slave modes with START and STOP condition interrupts operate identically to the MSSP Slave modes except that START and STOP conditions generate SSPIF interrupts.

### 11.3 Selecting the A/D Conversion Clock

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. If neither the internal VRH nor VRL are used for the A/D converter, the four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- A/D RC oscillator

If the VRH or VRL are used for the A/D converter reference, then the TAD requirement is automatically increased by a factor of 8.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

TABLE 11-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Reference<br>Source        | A/D Clock | Source (TAD) | Device Frequency            |                             |                             |                             |  |  |

|--------------------------------|-----------|--------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|

|                                | Operation | ADCS<1:0>    | 20 MHz                      | 5 MHz                       | 4 MHz                       | 1.25 MHz                    |  |  |

|                                | 2 Tosc    | 00           | 100 ns <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.6 μs                      |  |  |

| External VREF or Analog Supply | 8 Tosc    | 01           | 400 ns <sup>(2)</sup>       | 1.6 μs                      | 2.0 μs                      | 6.4 μs                      |  |  |

| Analog Supply                  | 32 Tosc   | 10           | 1.6 μs                      | 6.4 μs <sup>(3)</sup>       | 8.0 μs <sup>(3)</sup>       | 25.6 μs <sup>(3)</sup>      |  |  |

|                                | A/D RC    | 11           | 2 - 6 μs <sup>(1,4)</sup>   |  |  |

| Internal VRH or                | 16 Tosc   | 00           | 800 ns <sup>(2)</sup>       | 3.2 μs <sup>(2)</sup>       | 4 μs <sup>(2)</sup>         | 12.8 μs                     |  |  |

| VRL                            | 64 Tosc   | 01           | 3.2 μs <sup>(2)</sup>       | 12.8 μs                     | 16 μs                       | 51.2 μs <sup>(3)</sup>      |  |  |

|                                | 256 Tosc  | 10           | 12.8 μs                     | 51.2 μs <sup>(3)</sup>      | 64 μs <sup>(3)</sup>        | 204.8 μs <sup>(3)</sup>     |  |  |

|                                | A/D RC    | 11           | 16 - 48 μs <sup>(4,5)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

- **5:** A/D RC clock source has a typical TAD time of 32  $\mu$ s for VDD > 3.0V.

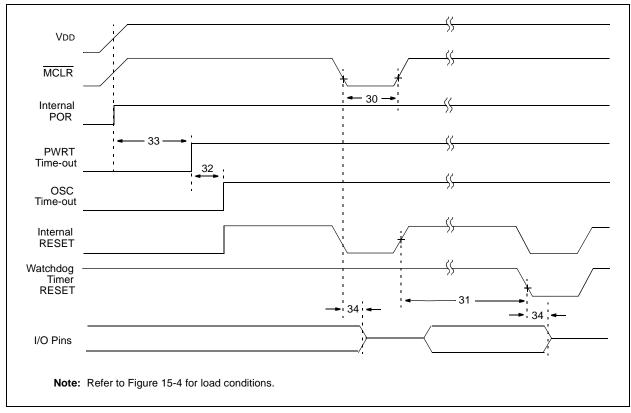

### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked by the POR pulse. When the PWRT delay expires, the Oscillator Start-up Timer is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 12-6, Figure 12-7, Figure 12-8 and Figure 12-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 12-8). This is useful for testing purposes or to synchronize more than one PIC® microcontroller operating in parallel.

Table 12-5 shows the RESET conditions for some special function registers, while Table 12-6 shows the RESET conditions for all the registers.

## 12.9 Power Control/STATUS Register (PCON)

The Power Control/STATUS Register, PCON, has two status bits that provide indication of which power-up type RESET occurred.

Bit0 is Brown-out Reset Status bit, BOR. The BOR bit is unknown upon a POR. BOR must be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power-           | -up       | Brown-out        | Wake-up from |  |  |

|--------------------------|------------------|-----------|------------------|--------------|--|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |  |

| XT, HS, LP               | TPWRT + 1024Tosc | 1024Tosc  | TPWRT + 1024Tosc | 1024Tosc     |  |  |

| EC, ER, INTRC            | Tpwrt            | _         | TPWRT            | _            |  |  |

TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |

|---------------------------------------|--------------------|--------------------|------------------|

| Power-on Reset                        | 000h               | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 1-uu             |

| WDT Reset                             | 000h               | 0000 1uuu          | 1-uu             |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | u-uu             |

| Brown-out Reset                       | 000h               | 0001 1uuu          | 1-u0             |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuu1 0uuu          | u-uu             |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuu1 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

| COMF             | Complement f                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                             |

| Operation:       | $(\bar{f}) \to (destination)$                                                                                                                  |

| Status Affected: | Z                                                                                                                                              |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                              |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [label] GOTO k                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The eleven bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two cycle instruction. |  |  |  |  |  |  |  |  |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                   |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCF f,d                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, |  |  |  |  |  |  |  |  |

|                  | a NOP is executed instead making it a 2Tcy instruction.                                                                                                                                                                               |  |  |  |  |  |  |  |  |

TABLE 14-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                 |                                              |                       |                                   | ììo2<br>≥ ≥                                |                                | atsium∃<br>ō                             | Debugger<br>∑ ⊆                   |                                                   | Program<br><u>⊏</u> ⊇                       | <u> </u>                         | <b>₽</b>                         |                                  |                                    |                                                |                        |                         |                           |                                     | # <u>0</u>                                        | ₩ E                                                 | 2                           |

|-----------------|----------------------------------------------|-----------------------|-----------------------------------|--------------------------------------------|--------------------------------|------------------------------------------|-----------------------------------|---------------------------------------------------|---------------------------------------------|----------------------------------|----------------------------------|----------------------------------|------------------------------------|------------------------------------------------|------------------------|-------------------------|---------------------------|-------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|

|                 | MPLAB® Integrated<br>Development Environment | MPLAB® C17 C Compiler | MPLAB <sup>®</sup> C18 C Compiler | MPASM™ Assembler/<br>MPLINK™ Object Linker | MPLAB® ICE In-Circuit Emulator | ICEPIC <sup>TM</sup> In-Circuit Emulator | MPLAB® ICD In-Circuit<br>Debugger | PICSTART® Plus Entry Level Development Programmer | PRO MATE® II<br>Universal Device Programmer | PICDEM™ 1 Demonstration<br>Board | PICDEM™ 2 Demonstration<br>Board | PICDEM™ 3 Demonstration<br>Board | PICDEM™ 14A Demonstration<br>Board | PICDEM <sup>TM</sup> 17 Demonstration<br>Board | KEELoo® Evaluation Kit | KEELoq® Transponder Kit | microlD™ Programmer's Kit | 125 kHz microlD™<br>Developer's Kit | 125 kHz Anticollision microlD™<br>Developer's Kit | 13.56 MHz Anticollision<br>microlD™ Developer's Kit | MCB2540 CAN Developer's Kit |

| ысізсххх        | >                                            |                       |                                   | >                                          | ە <b>ر</b>                     | >                                        |                                   | >                                                 | >                                           |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     | N.                                                |                                                     | _                           |

| PIC14000        | `                                            |                       |                                   | >                                          | >                              |                                          |                                   | `                                                 | >                                           |                                  |                                  |                                  | >                                  |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C5X        | >                                            |                       |                                   | >                                          | >                              | >                                        |                                   | >                                                 | >                                           | >                                |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C6X        | >                                            |                       |                                   | >                                          | >                              | >                                        | *                                 | >                                                 | >                                           |                                  | ₹,                               |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16CXXX       | >                                            |                       |                                   | >                                          | >                              | >                                        |                                   | >                                                 | >                                           | >                                |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16F62X       | >                                            |                       |                                   | >                                          | ** `                           |                                          |                                   | ** ^                                              | **                                          |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C7X        | >                                            |                       |                                   | >                                          | >                              | >                                        | *>                                | `                                                 | >                                           | +                                | ₹,                               |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C7XX       | >                                            |                       |                                   | >                                          | `                              | >                                        |                                   | >                                                 | >                                           |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C8X        | >                                            |                       |                                   | >                                          | `                              | >                                        |                                   | >                                                 | >                                           | >                                |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16F8XX       | >                                            |                       |                                   | >                                          | `                              |                                          | >                                 | `                                                 | >                                           |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC16C9XX       | `                                            | ,                     |                                   | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `      | `                              | >                                        |                                   | `                                                 | <u> </u>                                    | *                                |                                  | >                                |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC17C4X        | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `        | `<br>`                |                                   | `                                          | `                              |                                          |                                   | `                                                 | `                                           | `                                |                                  |                                  |                                    | `                                              |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC18CXX2       | ` <u>`</u>                                   |                       | >                                 | >                                          | >                              |                                          |                                   | >                                                 | >                                           |                                  | >                                |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     |                             |

| PIC18FXXX       | >                                            |                       | >                                 | >                                          | >                              |                                          | >                                 | >                                                 | >                                           |                                  | >                                |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     | _                           |

| SPCXX/          |                                              |                       |                                   | >                                          |                                |                                          |                                   |                                                   | >                                           |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     | _                           |

| HCSXXX<br>63CXX |                                              |                       |                                   | >                                          |                                |                                          |                                   |                                                   | >                                           |                                  |                                  |                                  |                                    |                                                | `                      | >                       |                           |                                     |                                                   |                                                     | _                           |

| WCKEXXX         |                                              |                       |                                   |                                            |                                |                                          |                                   |                                                   |                                             |                                  |                                  |                                  |                                    |                                                |                        |                         | >                         | >                                   | >                                                 | >                                                   |                             |

| WCP2510         |                                              |                       |                                   |                                            |                                |                                          |                                   |                                                   |                                             |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     | `                           |

|                 |                                              |                       |                                   |                                            |                                |                                          |                                   |                                                   |                                             |                                  |                                  |                                  |                                    |                                                |                        |                         |                           |                                     |                                                   |                                                     | Γ                           |

\* Contact the Microchip Technology Inc. web site at www.microchip.com for information on how to use the MPLAB® ICD In-Circuit Debugger (DV164001) with PIC16C62, 63, 64, 65, 72, 73, 74, 76, 77.

\*\* Contact Microchip Technology Inc. for availability date.

† Development tool is available on select devices.

DC CHARACTERISTICS

## 15.2 DC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$  +125°C for extended

Operating voltage VDD range as described in Section 15.1 and

Section 15.2.

|        | Section 15.2. |                                             |                     |     |         |          |                                                                   |  |  |  |  |  |

|--------|---------------|---------------------------------------------|---------------------|-----|---------|----------|-------------------------------------------------------------------|--|--|--|--|--|

| Param. | Sym           | Characteristic                              | Min Typ† Max Unit   |     |         | Units    | ts Conditions                                                     |  |  |  |  |  |

| No.    |               |                                             |                     |     |         |          |                                                                   |  |  |  |  |  |

|        |               | Input Low Voltage                           |                     |     |         |          |                                                                   |  |  |  |  |  |

|        | VIL           | I/O ports                                   |                     |     |         |          |                                                                   |  |  |  |  |  |

| D030   |               | with TTL buffer                             | Vss                 | _   | 0.15VDD | V        | For entire VDD range                                              |  |  |  |  |  |

| D030A  |               |                                             | Vss                 | _   | 0.8V    | V        | $4.5V \le VDD \le 5.5V$                                           |  |  |  |  |  |

| D031   |               | with Schmitt Trigger buffer                 | Vss                 | _   | 0.2Vdd  | V        | For entire VDD range                                              |  |  |  |  |  |

| D032   |               | MCLR                                        | Vss                 | _   | 0.2Vdd  | V        |                                                                   |  |  |  |  |  |

| D033   |               | OSC1 (in XT, HS, LP and EC)                 | Vss                 | _   | 0.3Vdd  | V        |                                                                   |  |  |  |  |  |

|        |               | Input High Voltage                          |                     |     |         |          |                                                                   |  |  |  |  |  |

|        | VIH           | I/O ports                                   |                     | _   |         |          |                                                                   |  |  |  |  |  |

|        |               | with TTL buffer                             |                     |     |         |          |                                                                   |  |  |  |  |  |

| D040   |               |                                             | 2.0                 | _   | Vdd     | V        | $4.5V \le VDD \le 5.5V$                                           |  |  |  |  |  |

| D040A  |               |                                             | (0.25VDD<br>+ 0.8V) | _   | VDD     | V        | For entire VDD range                                              |  |  |  |  |  |

| D041   |               | with Schmitt Trigger buffer                 | 0.8VDD              | _   | Vdd     | V        | For entire VDD range                                              |  |  |  |  |  |

| D042   |               | MCLR                                        | 0.8VDD              | _   | Vdd     | V        |                                                                   |  |  |  |  |  |

| D042A  |               | OSC1 (XT, HS, LP and EC)                    | 0.7Vdd              | _   | VDD     | V        |                                                                   |  |  |  |  |  |

| D070   | IPURB         | PORTB weak pull-up current                  | 50                  | 250 | 400     | μΑ       | VDD = 5V, VPIN = VSS                                              |  |  |  |  |  |

|        |               | per pin                                     |                     |     |         |          |                                                                   |  |  |  |  |  |

|        |               | Input Leakage Current (1,2)                 |                     |     |         |          |                                                                   |  |  |  |  |  |

| D060   |               | I/O ports (with digital functions)          | _                   | _   | ±1      | μΑ       | $Vss \le VPIN \le VDD$ , Pin at hi-impedance                      |  |  |  |  |  |

| D060A  | lıL           | I/O ports (with analog functions)           | _                   | _   | ±100    | nA       | Vss ≤ VPIN ≤ VDD, Pin at hi-impedance                             |  |  |  |  |  |

| D061   |               | RA5/MCLR/VPP                                | _                   | _   | ±5      | μΑ       | $Vss \le VPIN \le VDD$                                            |  |  |  |  |  |

| D063   |               | OSC1                                        | _                   | _   | ±5      | μА       | Vss ≤ VPIN ≤ VDD, XT, HS, LP and EC osc configuration             |  |  |  |  |  |

|        |               | Output Low Voltage                          |                     |     |         |          | 9                                                                 |  |  |  |  |  |

| D080   | Vol           | I/O ports                                   | _                   | _   | 0.6     | V        | IOL = 8.5  mA, VDD = 4.5V                                         |  |  |  |  |  |

|        |               | Output High Voltage                         |                     |     |         |          |                                                                   |  |  |  |  |  |

| D090   |               | I/O ports <sup>(2)</sup>                    | VDD - 0.7           | _   | _       | V        | IOH = -3.0 mA, VDD = 4.5V                                         |  |  |  |  |  |

| D150*  | Vod           |                                             | _                   | _   | 10.5    | V        | RA4 pin                                                           |  |  |  |  |  |

|        |               | Capacitive Loading Specs on<br>Output Pins* |                     |     |         |          |                                                                   |  |  |  |  |  |

| D100   | COS<br>C2     | OSC2 pin                                    | _                   | _   | 15      | pF       | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |  |

| D101   | Cıo           | All I/O pins and OSC2 (in RC                | _                   | _   | 50      | pF       |                                                                   |  |  |  |  |  |

| D102   |               | mode) SCL, SDA in I <sup>2</sup> C mode     | _                   | _   | 400     | pF       |                                                                   |  |  |  |  |  |

|        |               | VRH pin                                     | _                   | _   | 200     | pF       | VRH output enabled                                                |  |  |  |  |  |

|        |               | VRL pin                                     | _                   | _   | 200     | pF       | VRL output enabled                                                |  |  |  |  |  |

|        |               | i .                                         |                     |     | i       | <u> </u> | 1                                                                 |  |  |  |  |  |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>2:</sup> Negative current is defined as current sourced by the pin.

TABLE 15-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC16C717/770/771 AND PIC16LC717/770/771

| AC Chara          | cteristics | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended  Operating Voltage VDD range is described in Section and Section |      |                     |      |       |            |  |  |

|-------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|------------|--|--|

| Parameter No. Sym |            | Characteristic                                                                                                                                                                                                                                                                                                    |      | Typ <sup>(1)*</sup> | Max  | Units | Conditions |  |  |

|                   | FIRC       | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                  | 3.65 | 4.00                | 4.28 | MHz   | VDD = 5.0V |  |  |

|                   | TIKC       | Internal RC Frequency*                                                                                                                                                                                                                                                                                            | 3.55 | 4.00                | 4.31 | MHz   | VDD = 2.5V |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

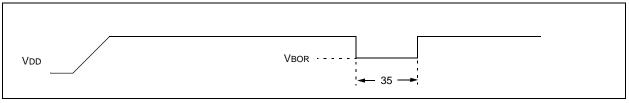

FIGURE 15-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

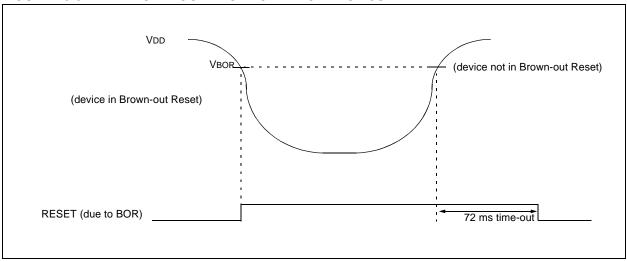

TABLE 15-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|---------------|-------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30*           | TMCL  | MCLR Pulse Width (low)                                 | 2   | _         | _   | μS    | VDD = 5V, -40°C to +85°C |

| 31*           | TWDT  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32*           | Tost  | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | _   | _     | Tosc = OSC1 period       |

| 33*           | TPWRT | Power up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34*           | TIOZ  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _         | 2.1 | μS    |                          |

| 35*           | TBOR  | Brown-out Reset pulse width                            | 100 | _         | _   | μS    | VDD ≤ VBOR (D005)        |

<sup>\*</sup> These parameters are characterized but not tested.

FIGURE 15-9: BROWN-OUT RESET CHARACTERISTICS

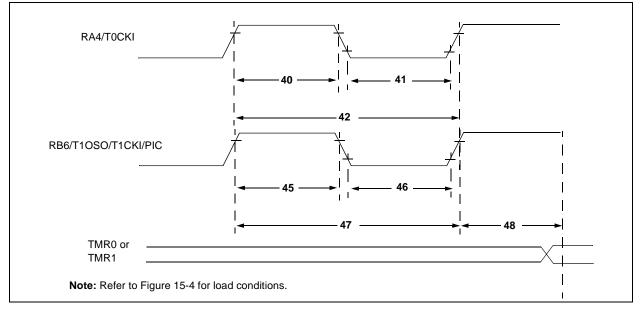

FIGURE 15-10: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

SS SCK (CKP = 0)SCK (CKP = 1)80 LSb SDO MSb 75, 76 SDI MSb IN BIT6 LSb IN

**SPI MASTER MODE TIMING (CKE = 1)** FIGURE 15-19:

TABLE 15-18: SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

Note: Refer to Figure 15-4 for load conditions.

| Param.<br>No. | Symbol                | Characteristic                           |                     | Min          | Тур† | Max | Units  | Conditions |

|---------------|-----------------------|------------------------------------------|---------------------|--------------|------|-----|--------|------------|

| 71*           | TscH                  | SCK input high time Continuous           |                     | 1.25Tcy + 30 | _    | _   | ns     |            |

| 71A*          |                       | (Slave mode)                             | Single Byte         | 40           | _    | _   | ns     | Note 1     |

| 72*           | TscL                  | SCK input low time                       | Continuous          | 1.25Tcy + 30 |      | -   | ns     |            |

| 72A*          |                       | (Slave mode)                             | Single Byte         | 40           | _    | _   | ns     | Note 1     |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inpedge           | 100                 | _            |      | ns  |        |            |

| 73A*          | Тв2в                  | Last clock edge of Byte1 edge of Byte2   | 1.5Tcy + 40         | _            | _    | ns  | Note 1 |            |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data inpu               | 100                 | _            | _    | ns  |        |            |

| 75*           | TdoR                  | SDO data output rise PIC16CX             |                     |              | 10   | 25  | ns     |            |

|               |                       | time                                     | PIC16 <b>LC</b> XXX |              | 20   | 45  | ns     |            |

| 76*           | TdoF                  | SDO data output fall time                |                     |              | 10   | 25  | ns     |            |

| 78*           | TscR                  | SCK output rise time PIC16 <b>C</b> XXX  |                     |              | 10   | 25  | ns     |            |

|               | (Master mode)         |                                          | PIC16 <b>LC</b> XXX |              | 20   | 45  | ns     |            |

| 79*           | TscF                  | SCK output fall time (Master mode)       |                     |              | 10   | 25  | ns     |            |

| 80*           | TscH2doV,             | SDO data output valid PIC16 <b>C</b> XXX |                     | _            | _    | 50  | ns     |            |

|               | TscL2doV              | after SCK edge PIC16 <b>LC</b> XXX       |                     |              | _    | 100 | ns     |            |

| 81*           | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge        |                     | Tcy          | _    | _   | ns     |            |

These parameters are characterized but not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

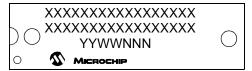

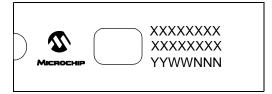

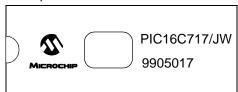

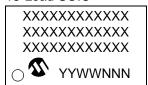

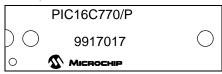

#### 17.0 PACKAGING INFORMATION

#### 17.1 **Package Marking Information**

### 18-Lead PDIP

### Example

#### 18-Lead CERDIP Windowed

### Example

### 18-Lead SOIC

### Example

#### 20-Lead PDIP

### Example

Legend: XX...XCustomer-specific information

> Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01') NNN

Alphanumeric traceability code (e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

# PIC16C717/770/771

NOTES:

### PIC16C717/770/771

| 1                                              |     | BTFSS                                          |         |

|------------------------------------------------|-----|------------------------------------------------|---------|

| I/O Ports                                      | 25  | CALL                                           |         |

| I <sup>2</sup> C                               | 76  | CLRF                                           |         |

| I <sup>2</sup> C Master Mode Reception         | 89  | CLRW                                           |         |

| I <sup>2</sup> C Master Mode Restart Condition |     | CLRWDT                                         |         |

| I <sup>2</sup> C Mode Selection                | 76  | COMF                                           |         |

| I <sup>2</sup> C Module                        |     | DECF                                           |         |

| Acknowledge Sequence timing                    | 91  | DECFSZ                                         |         |

| Addressing                                     | 77  | GOTO                                           |         |

| Baud Rate Generator                            |     | INCF                                           |         |

| Block Diagram                                  | 83  | INCFSZ                                         |         |

| BRG Block Diagram                              | 84  | IORLW                                          |         |

| BRG Reset due to SDA Collision                 |     | IORWF                                          |         |

| BRG Timing                                     |     | MOVF                                           |         |

| Bus Arbitration                                |     | MOVLW                                          |         |

| Bus Collision                                  |     | MOVWF                                          |         |

| Acknowledge                                    |     | NOP                                            |         |

| Restart Condition                              |     | RETFIE                                         |         |

| Restart Condition Timing (Case1)               | 97  | RETLW                                          |         |

| Restart Condition Timing (Case2)               |     | RETURN                                         |         |

| Start Condition                                |     | RLF                                            |         |

| Start Condition Timing                         |     | RRF                                            |         |

| Stop Condition                                 |     | SLEEP                                          |         |

| Stop Condition Timing (Case1)                  |     | SUBLW                                          |         |

| Stop Condition Timing (Case2)                  |     | SUBWF                                          |         |

| Transmit Timing                                |     | SWAPF                                          |         |

| Bus Collision timing                           |     | XORLW                                          |         |

| Clock Arbitration                              |     | XORWF                                          |         |

| Clock Arbitration Timing (Master Transmit)     |     | Summary Table                                  | 134     |

| Conditions to not give ACK Pulse               |     | INT Interrupt (RB0/INT). See Interrupt Sources | 4.0     |