Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c771-e-so |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The special function registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

TABLE 2-1: PIC16C717/770/771 SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7         | Bit 6                                                                       | Bit 5          | Bit 4          | Bit 3        | Bit 2           | Bit 1        | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>Page: |

|----------------------|---------|---------------|-----------------------------------------------------------------------------|----------------|----------------|--------------|-----------------|--------------|---------|--------------------------|------------------------|

| Bank 0               |         |               |                                                                             |                |                |              |                 |              |         |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing    | this location                                                               | uses content   | s of FSR to ad | dress data m | emory (not a    | physical req | gister) | 0000 0000                | 23                     |

| 01h                  | TMR0    | Timer0 mod    | lule's registe                                                              | r              |                |              |                 |              |         | xxxx xxxx                | 45                     |

| 02h <sup>(3)</sup>   | PCL     | Program Co    | ounter's (PC)                                                               | Least Signific | cant Byte      |              |                 |              |         | 0000 0000                | 22                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP           | RP1                                                                         | RP0            | TO             | PD           | Z               | DC           | С       | 0001 1xxx                | 14                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect data | a memory ad                                                                 | dress pointer  |                |              |                 |              |         | xxxx xxxx                | 23                     |

| 05h                  | PORTA   | RA7           | RA6                                                                         | RA5            | RA4            | RA3          | RA2             | RA1          | RA0     | xxxx 0000                | 25                     |

| 06h                  | PORTB   | RB7           | RB6                                                                         | RB5            | RB4            | RB3          | RB2             | RB1          | RB0     | xxxx xx11                | 33                     |

| 07h                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 08h                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 09h                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _             | _                                                                           | _              | Write Buffer f | or the upper | 5 bits of the I | Program Cou  | unter   | 0 0000                   | 22                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE           | PEIE                                                                        | TOIE           | INTE           | RBIE         | TOIF            | INTF         | RBIF    | 0000 000x                | 16                     |

| 0Ch                  | PIR1    | _             | ADIF                                                                        | _              | _              | SSPIF        | CCP1IF          | TMR2IF       | TMR1IF  | -00000                   | 18                     |

| 0Dh                  | PIR2    | LVDIF         | _                                                                           | _              | _              | BCLIF        | _               | _            | _       | 0 0                      | 20                     |

| 0Eh                  | TMR1L   | Holding reg   | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                |                |              |                 |              |         |                          | 47                     |

| 0Fh                  | TMR1H   | Holding reg   | ister for the I                                                             | Most Significa | nt Byte of the | 16-bit TMR1  | register        |              |         | xxxx xxxx                | 47                     |

| 10h                  | T1CON   | _             | I                                                                           | T1CKPS1        | T1CKPS0        | T1OSCEN      | T1SYNC          | TMR1CS       | TMR10N  | 00 0000                  | 47                     |

| 11h                  | TMR2    | Timer2 mod    | lule's registe                                                              | r              |                |              |                 |              |         | 0000 0000                | 51                     |

| 12h                  | T2CON   | _             | TOUTPS3                                                                     | TOUTPS2        | TOUTPS1        | TOUTPS0      | TMR2ON          | T2CKPS1      | T2CKPS0 | -000 0000                | 51                     |

| 13h                  | SSPBUF  | Synchronou    | ıs Serial Port                                                              | Receive Buf    | fer/Transmit R | egister      |                 |              |         | xxxx xxxx                | 70                     |

| 14h                  | SSPCON  | WCOL          | SSPOV                                                                       | SSPEN          | CKP            | SSPM3        | SSPM2           | SSPM1        | SSPM0   | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/Co    | mpare/PWM                                                                   | Register1 (L   | SB)            |              |                 |              |         | xxxx xxxx                | 54                     |

| 16h                  | CCPR1H  | Capture/Co    | mpare/PWM                                                                   | Register1 (M   | SB)            |              |                 |              |         | xxxx xxxx                | 54                     |

| 17h                  | CCP1CON | PWM1M1        | PWM1M0                                                                      | DC1B1          | DC1B0          | CCP1M3       | CCP1M2          | CCP1M1       | CCP1M0  | 0000 0000                | 53                     |

| 18h                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 19h                  | -       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 1Ah                  | -       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 1Bh                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 1Ch                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 1Dh                  | _       | Unimpleme     | nted                                                                        |                |                |              |                 |              |         | _                        | _                      |

| 1Eh                  | ADRESH  | A/D High By   | te Result Re                                                                | egister        |                |              |                 |              | _       | xxxx xxxx                | 107                    |

| 1Fh                  | ADCON0  | ADCS1         | ADCS0                                                                       | CHS2           | CHS1           | CHS0         | GO/DONE         | CHS3         | ADON    | 0000 0000                | 107                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

- 3: These registers can be addressed from any bank.

#### 3.3 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

**EXAMPLE 3-2:** Initializing PORTB

|       |         |      | <u> </u>              |

|-------|---------|------|-----------------------|

| BCF   | STATUS, | RP0; |                       |

| CLRF  | PORTB   | ;    | Initialize PORTB by   |

|       |         | ;    | clearing output       |

|       |         | ;    | data latches          |

| BSF   | STATUS, | RP0; | Select Bank 1         |

| MOVLW | 0xCF    | ;    | Value used to         |

|       |         | ;    | initialize data       |

|       |         | ;    | direction             |

| MOVWF | TRISB   | ;    | Set RB<3:0> as inputs |

|       |         | ;    | RB<5:4> as outputs    |

|       |         | ;    | RB<7:6> as inputs     |

| MOVLW | 0x30    | ;    | Set RB<1:0> as analog |

|       |         |      | inputs                |

| MOVWF | ANSEL   | ;    |                       |

| BCF   | STATUS, | RP0; | Return to Bank 0      |

|       |         |      |                       |

Each of the PORTB pins has an internal pull-up, which can be individually enabled from the WPUB register. A single global enable bit can turn on/off the enabled pull-ups. Clearing the RBPU bit, (OPTION\_REG<7>), enables the weak pull-up resistors. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Each of the PORTB pins, if configured as input, also has an interrupt-on-change feature, which can be individually selected from the IOCB register. The RBIE bit in the INTCON register functions as a global enable bit to turn on/off the interrupt-on-change feature. The selected inputs are compared to the old value latched on the last read of PORTB. The "mismatch" outputs are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- a) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

The RB0 pin is multiplexed with the A/D converter analog input 4 and the external interrupt input (RB0/AN4/INT). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB0 pin as Analog mode.

The RB1 pin is multiplexed with the A/D converter analog input 5 and the MSSP module slave select input (RB1/AN5/ $\overline{SS}$ ). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB1 pin as Analog mode.

Note: Upon RESET, the ANSEL register configures the RB1 and RB0 pins as analog inputs.

Both RB1 and RB0 pins will read as '1'.

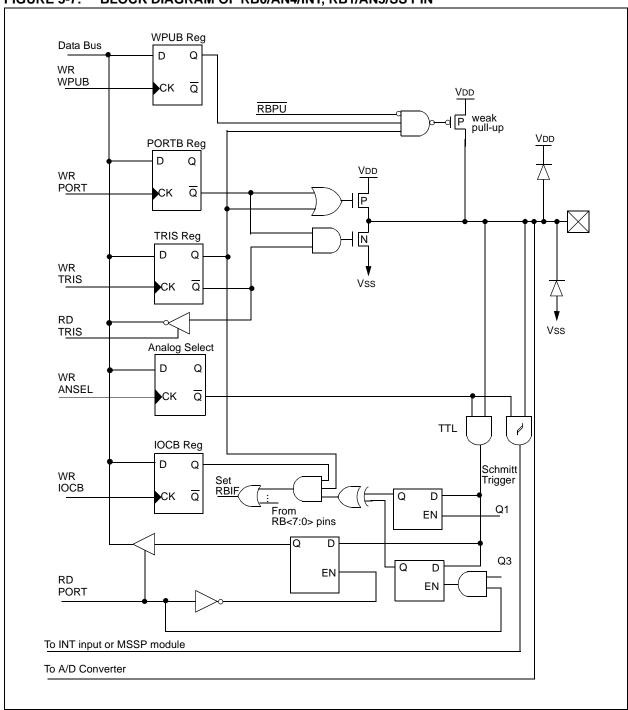

FIGURE 3-7: BLOCK DIAGRAM OF RB0/AN4/INT, RB1/AN5/SS PIN

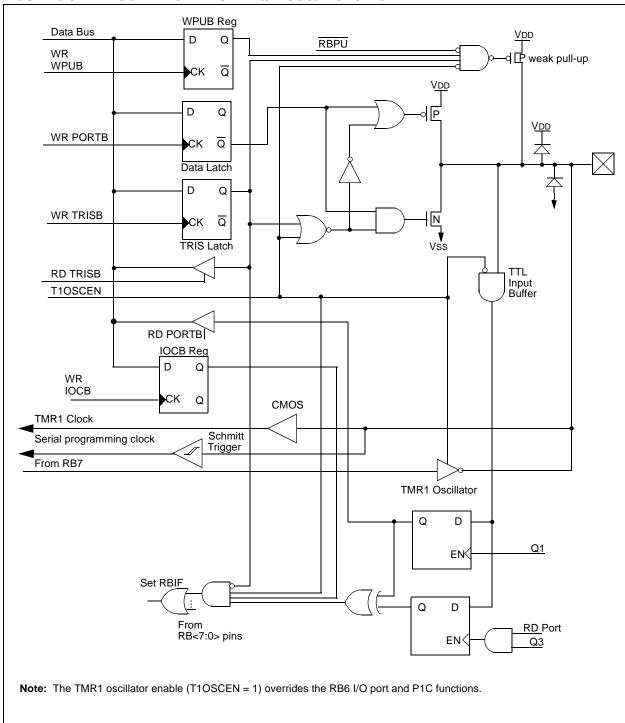

FIGURE 3-9: BLOCK DIAGRAM OF RB6/T10S0/T1CKI/P1C

#### REGISTER 4-2: PROGRAM MEMORY DATA HIGH (PMDATH: 10Eh)

| U-0   | U-0 | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------|-----|-------|-------|-------|-------|------|-------|

| _     | _   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9 | PMD8  |

| bit 7 |     |       |       |       |       |      | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

Legend:  $R = Readable \ bit \qquad W = Writable \ bit \qquad U = Unimplemented \ bit, \ read \ as \ '0' \\ -n = Value \ at \ POR \qquad '1' = Bit \ is \ set \qquad '0' = Bit \ is \ cleared \qquad x = Bit \ is \ unknown$

#### REGISTER 4-3: PROGRAM MEMORY DATA LOW (PMDATL: 10Ch)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| PMD7  | PMD6 | PMD5 | PMD4 | PMD3 | PMD2 | PMD1 | PMD0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

#### REGISTER 4-4: PROGRAM MEMORY ADDRESS HIGH (PMADRH: 10Fh)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | PMA11 | PMA10 | PMA9  | PMA8  |

| bit 7 |     |     |     |       |       |       | bit 0 |

bit 7-4 Unimplemented: Read as '0' bit 3-0 PMA<11:8>: PMR Address bits

#### REGISTER 4-5: PROGRAM MEMORY ADDRESS LOW (PMADRL: 10Dh)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMA7  | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 **PMA<7:0>:** PMR Address bits

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

TABLE 8-1: ECCP MODE - TIMER RESOURCE

| ECCP Mode | Timer Resource |

|-----------|----------------|

| Capture   | Timer1         |

| Compare   | Timer1         |

| PWM       | Timer2         |

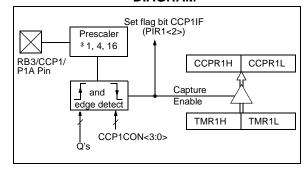

#### 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- · every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 8.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1/P1A pin is configured as   |

|-------|--------------------------------------------|

|       | an output, a write to the port can cause a |

|       | capture condition.                         |

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 8.1.4 ECCP PRESCALER

There are three prescaler settings, specified by bits CCP1M<3:0>. Whenever the ECCP module is turned off or the ECCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

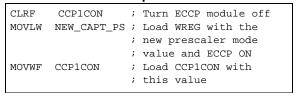

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 8-1: Changing Between Capture Prescalers

## FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- · driven High

- driven Low

- toggle output (High to Low or Low to High)

- · remains Unchanged

The action on the pin is based on the value of control bits CCP1M<3:0>. At the same time, interrupt flag bit CCP1IF is set.

Changing the ECCP mode select bits to the clear output on Match mode (CCP1M<3.0> = "1000") presets the CCP1 output latch to the logic 1 level. Changing the ECCP mode select bits to the clear output on Match mode (CCP1M<3:0> = "1001") presets the CCP1 output latch to the logic 0 level.

#### 8.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISB bit.

Note: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the port data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the ECCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

## 8.3.5 PROGRAMMABLE DEADBAND DELAY

In half-bridge or full-bridge applications, driven by half-bridge outputs (see Figure 8-7), the power switches normally require longer time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches will be on for a short period of time, until one switch completely turns off. During this time, a very high current, called shootthrough current, will flow through both power switches,

shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on the power switch is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable deadband delay is available to avoid shootthrough current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 8-6 for illustration. The P1DEL register sets the amount of delay.

#### REGISTER 8-2: PWM DELAY REGISTER (P1DEL: 97H)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| P1DEL7 | P1DEL6 | P1DEL5 | P1DEL4 | P1DEL3 | P1DEL2 | P1DEL1 | P1DEL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

bit 7-0 **P1DEL<7:0>: PWM Delay Count for Half-Bridge Output Mode:** Number of Fosc/4 (Tosc•4) cycles between the P1A transition and the P1B transition.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.3.6 DIRECTION CHANGE IN FULL-BRIDGE OUTPUT MODE

In the Full-Bridge Output mode, the PWM1M1 bit in the CCP1CON register allows user to control the Forward/Reverse direction. When the application firmware changes this direction control bit, the ECCP module will assume the new direction on the next PWM cycle. The current PWM cycle still continues, however, the non-

modulated outputs, P1A and P1C signals, will transition to the new direction TOSC, 4•TOSC or 16•TOSC (for Timer2 prescale T2CKRS<1:0> = 00, 01 and 1x respectively) earlier, before the end of the period. During this transition cycle, the modulated outputs, P1B and P1D, will go to the inactive state. See Figure 8-10 for illustration.

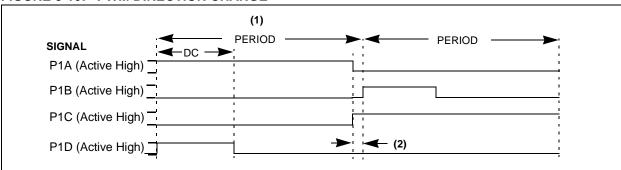

#### FIGURE 8-10: PWM DIRECTION CHANGE

Note 1: The Direction bit in the ECCP Control Register (CCP1CON<PWM1M1>) is written anytime during the PWM cycle.

2: The P1A and P1C signals switch Tosc, 4\*Tosc or 16\*Tosc, depending on the Timer2 prescaler value, earlier when changing direction. The modulated P1B and P1D signals are inactive at this time.

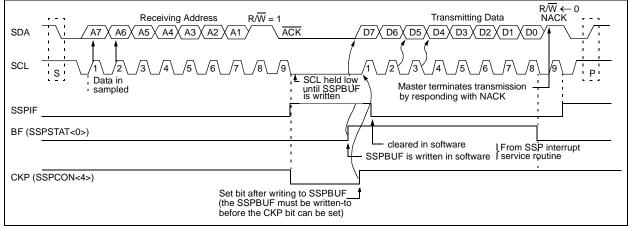

#### 9.2.2.4 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSP-STAT register is set. The received address is loaded into the SSPBUF register on the falling edge of the eighth SCL pulse. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The slave module automatically stretches the clock by holding the SCL line low so that the master will be unable to assert another clock pulse until the slave is finished preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. The CKP bit (SSPCON<4>) must then be set to release the SCL pin from the forced low condition. The eight data bits are shifted out on the falling edges of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-10).

The ACK or NACK signal from the master-receiver is latched on the rising edge of the ninth SCL input pulse. The master-receiver terminates slave transmission by

sending a NACK. If the SDA line is high (NACK), then the data transfer is complete. When the NACK is latched by the slave, the slave logic is RESET which also resets the  $R/\overline{W}$  bit to '0'. The slave module then monitors for another occurrence of the START bit. The slave firmware knows not to load another byte into the SSPBUF register by sensing that the buffer is empty (BF = 0) and the  $R/\overline{W}$  bit has gone low. If the SDA line is low (ACK), the  $R/\overline{W}$  bit remains high indicating that the next transmit data must be loaded into the SSPBUF register.

An MSSP interrupt (SSPIF flag) is generated for each data transfer byte on the falling edge of the ninth clock pulse. The SSPIF flag bit must be cleared in software. The SSPSTAT register is used to determine the status of the byte transfer.

For more information about the  $I^2C$  Slave mode, refer to Application Note AN734, "Using the PIC® SSP for Slave  $I^2C^{TM}$  Communication".

FIGURE 9-10: I<sup>2</sup>C SLAVE MODE WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### REGISTER 11-2: A/D CONTROL REGISTER 1 (ADCON1: 9Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-------|-------|-------|----------|----------|----------|----------|

| ADFM  | VCFG2 | VCFG1 | VCFG0 | Reserved | Reserved | Reserved | Reserved |

| bit 7 |       |       |       |          |          |          | bit 0    |

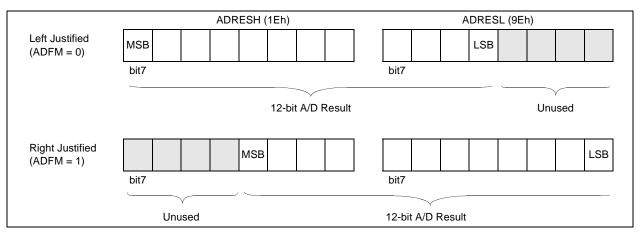

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified0 = Left justified

bit 6-4 VCFG<2:0>: Voltage Reference Configuration bits

|     | A/D VREF+                       | A/D VREF-           |

|-----|---------------------------------|---------------------|

| 000 | AV <sub>DD</sub> <sup>(1)</sup> | AVss <sup>(2)</sup> |

| 001 | External VREF+                  | External VREF-      |

| 010 | Internal VRH                    | Internal VRL        |

| 011 | External VREF+                  | AVss <sup>(2)</sup> |

| 100 | Internal VRH                    | AVss <sup>(2)</sup> |

| 101 | AVDD <sup>(1)</sup>             | External VREF-      |

| 110 | AV <sub>DD</sub> <sup>(1)</sup> | Internal VRL        |

| 111 | Internal VRL                    | AVss                |

bit 3-0 **Reserved:** Do not use.

**Note 1:** This parameter is VDD for the PIC16C717.

2: This parameter is Vss for the PIC16C717.

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

The A/D conversion results can be left justified (ADFM bit cleared), or right justified (ADFM bit set). Figure 11-1 through Figure 11-2 show the A/D result data format of the PIC16C717/770/771.

#### FIGURE 11-1: PIC16C770/771 12-BIT A/D RESULT FORMATS

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register   | Power-on Reset or<br>Brown-out Reset | MCLR Reset or<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|--------------------------------------|----------------------------|---------------------------------|

| W          | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| INDF       | 0000 0000                            | uuuu uuuu                  | uuuu uuuu                       |

| TMR0       | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| PCL        | 0000h                                | 0000h                      | PC + 1 <sup>(1)</sup>           |

| STATUS     | 0001 1xxx                            | 000q quuu <sup>(2)</sup>   | uuuq quuu <sup>(2)</sup>        |

| FSR        | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| PORTA      | xxxx 0000                            | uuuu 0000                  | uuuu uuuu                       |

| PORTB      | xxxx xx11                            | uuuu uu11                  | uuuu uuuu                       |

| PCLATH     | 0 0000                               | 0 0000                     | u uuuu                          |

| INTCON     | 0000 000x                            | 0000 000u                  | uuuu uuqq                       |

| PIR1       | -0 0000                              | -0 0000                    | -0 uuuu                         |

| PIR2       | 0 0                                  | 0 0                        | q q                             |

| TMR1L      | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| TMR1H      | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| T1CON      | 00 0000                              | uu uuuu                    | uu uuuu                         |

| TMR2       | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| T2CON      | -000 0000                            | -000 0000                  | -uuu uuuu                       |

| SSPBUF     | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| SSPCON     | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| CCPR1L     | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| CCPR1H     | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| CCP1CON    | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| ADRESH     | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| ADCON0     | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| OPTION_REG | 1111 1111                            | 1111 1111                  | uuuu uuuu                       |

| TRISA      | 1111 1111                            | 1111 1111                  | uuuu uuuu                       |

| TRISB      | 1111 1111                            | 1111 1111                  | uuuu uuuu                       |

| PIE1       | -0 0000                              | -0 0000                    | -u uuuu                         |

| PIE2       | 0 0                                  | 0 0                        | u u                             |

| PCON       | 1-qq                                 | 1-uu                       | u-uu                            |

| PR2        | 1111 1111                            | 1111 1111                  | 1111 1111                       |

| SSPADD     | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| SSPSTAT    | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| WPUB       | 1111 1111                            | 1111 1111                  | uuuu uuuu                       |

| IOCB       | 1111 0000                            | 1111 0000                  | uuuu uuuu                       |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition **Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>2:</sup> See Table 12-5 for RESET value for specific condition.

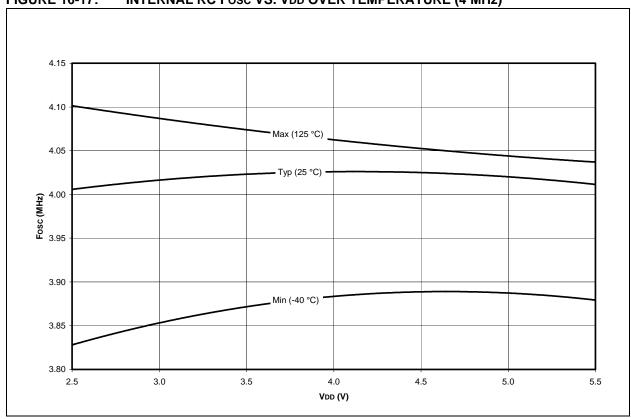

TABLE 15-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC16C717/770/771 AND PIC16LC717/770/771

| AC Chara             | cteristics | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended  Operating Voltage VDD range is described in Section and Section |      |                     |      |       |            |  |

|----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|------------|--|

| Parameter<br>No. Sym |            | Characteristic                                                                                                                                                                                                                                                                                                          | Min  | Typ <sup>(1)*</sup> | Max  | Units | Conditions |  |

| Firc                 |            | Internal Calibrated RC Frequency                                                                                                                                                                                                                                                                                        | 3.65 | 4.00                | 4.28 | MHz   | VDD = 5.0V |  |

|                      |            | Internal RC Frequency*                                                                                                                                                                                                                                                                                                  | 3.55 | 4.00                | 4.31 | MHz   | VDD = 2.5V |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

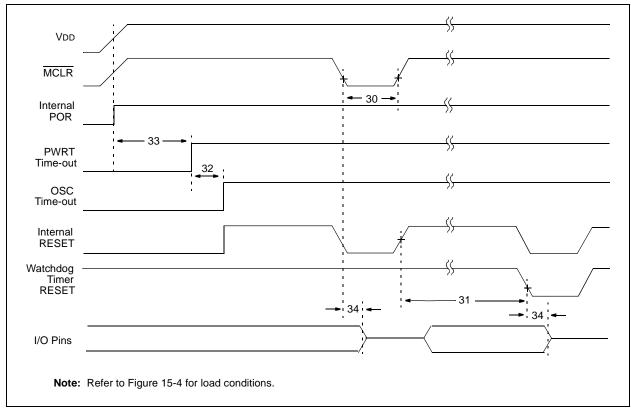

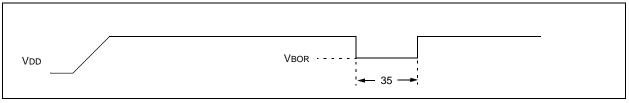

FIGURE 15-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### 15.4.3 PROGRAMMABLE BROWN-OUT RESET MODULE (PBOR)

#### TABLE 15-9: DC CHARACTERISTICS: PBOR

Standard Operating Conditions (unless otherwise stated)

Operating temperature 0°C  $\leq$  TA  $\leq$  +70°C for commercial -40°C  $\leq$  TA  $\leq$  +85°C for industrial

-40°C ≤ TA ≤ +125°C for extended

Operating voltage VDD range as described in DC Characteristics Section 15.1.

| Param.<br>No. | Characteristic |                | Symbol | Min | Тур  | Max  | Units | Conditions |

|---------------|----------------|----------------|--------|-----|------|------|-------|------------|

| D005          | BOR Voltage    | BORV<1:0> = 11 |        | 2.5 | 2.58 | 2.66 |       |            |

|               |                | BORV<1:0> = 10 | VBOR   | 2.7 | 2.78 | 2.86 | \/    |            |

|               |                | BORV<1:0> = 01 | VBOR   | 4.2 | 4.33 | 4.46 | V     |            |

|               |                | BORV<1:0> = 00 |        | 4.5 | 4.64 | 4.78 |       |            |

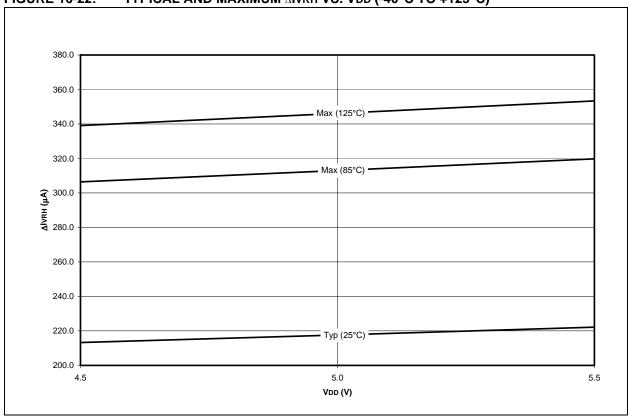

#### 15.4.4 VREF MODULE

**DC CHARACTERISTICS**

**DC CHARACTERISTICS**

#### TABLE 15-10: DC CHARACTERISTICS: VREF

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$  +125°C for extended

Operating voltage VDD range as described in DC Characteristics

Section 15.1.

| Geoloff 13.1. |         |                         |     |       |     |       |                                  |                                                              |

|---------------|---------|-------------------------|-----|-------|-----|-------|----------------------------------|--------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristic          | Min | Тур†  | Max | Units | Conditions                       |                                                              |

| D400          | VRL     | Output Voltage          | 2.0 | 2.048 | 2.1 | V     | $VDD \ge 2.7V$ ,                 | -40°C ≤ TA ≤ +85°C                                           |

|               | VRH     |                         | 4.0 | 4.096 | 4.2 | V     | $V \text{DD} \geq 4.5 \text{V},$ | $-40^{\circ}C \le TA \le +85^{\circ}C$                       |

| D400A         | VRL     | Output Voltage          | 1.9 | 2.048 | 2.2 | V     | $V \text{DD} \geq 2.7 V,$        | $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |

|               | VRH     |                         | 4.0 | 4.096 | 4.3 | V     | $V \text{DD} \geq 4.5 \text{V},$ | $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |

| D404*         | IVREFSO | External Load Source    | _   | _     | 5   | mA    |                                  |                                                              |

| D405*         | IVREFSI | External Load Sink      | _   | _     | -5  | mA    |                                  |                                                              |

| *             | CL      | External Capacitor Load | _   | _     | 200 | pF    |                                  |                                                              |

| D406*         | ∆Vout/  | VRH Load Regulation     | _   | 0.6   | 1   | mV/mA | Vdd ≥ 5V                         | ISOURCE = 0 mA to 5 mA                                       |

|               | ∆lout   |                         | _   | 1     | 4   |       |                                  | ISINK = 0 mA to 5 mA                                         |

|               |         | VRL Load Regulation     | _   | 0.6   | 1   |       | VDD ≥ 3V                         | ISOURCE = 0 mA to 5 mA                                       |

|               |         |                         | _   | 2     | 4   |       |                                  | ISINK = 0 mA to 5 mA                                         |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

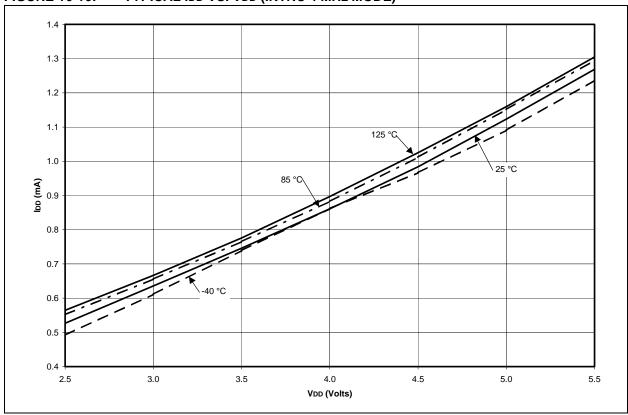

FIGURE 16-16: TYPICAL IDD VS. VDD (INTRC 4 MHz MODE)

FIGURE 16-17: INTERNAL RC FOSC VS. VDD OVER TEMPERATURE (4 MHz)

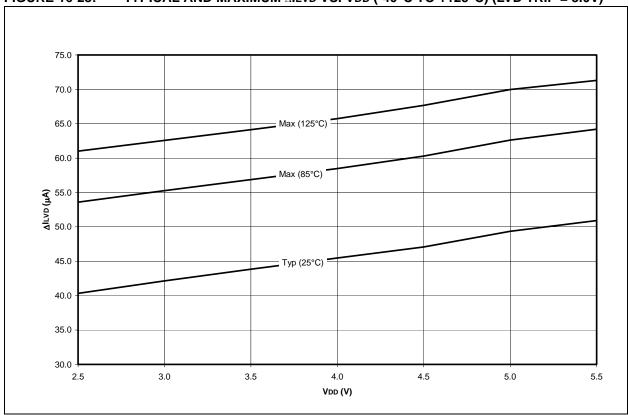

FIGURE 16-22: TYPICAL AND MAXIMUM AIVRH VS. VDD (-40°C TO +125°C)

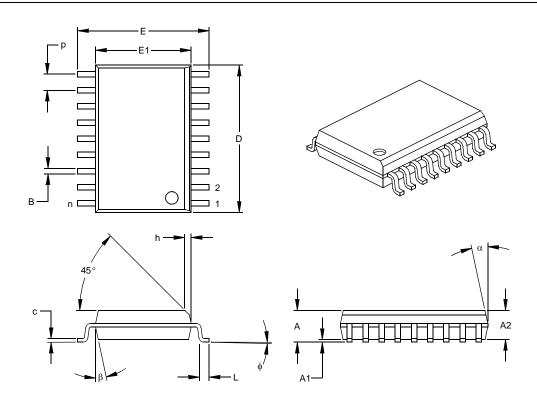

#### 17.4 18-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | INCHES* |      |      | MILLIMETERS |       |       |

|--------------------------|--------|---------|------|------|-------------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n      |         | 18   |      |             | 18    |       |

| Pitch                    | р      |         | .050 |      |             | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1     | .291    | .295 | .299 | 7.39        | 7.49  | 7.59  |

| Overall Length           | D      | .446    | .454 | .462 | 11.33       | 11.53 | 11.73 |

| Chamfer Distance         | h      | .010    | .020 | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle               | ф      | 0       | 4    | 8    | 0           | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .012 | 0.23        | 0.27  | 0.30  |

| Lead Width               | В      | .014    | .017 | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15   | 0           | 12    | 15    |

<sup>\*</sup> Controlling Parameter

#### Notes:

Note:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-013

Drawing No. C04-051

<sup>§</sup> Significant Characteristic

17.6 20-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

**DRAWING NOT AVAILABLE**

| TMR2 to PR2 Match Enable (TMR2IE Bit)17               | PICDEM 3 Low Cost PIC16CXXX                  |

|-------------------------------------------------------|----------------------------------------------|

| USART Receive Enable (RCIE Bit)17, 18                 | Demonstration Board144                       |

| Interrupts, Flag Bits                                 | PICSTART Plus Entry Level                    |

| CCP1 Flag (CCP1IF Bit)54                              | Development Programmer                       |

| Interrupt on Change (RB7:RB4) Flag                    | PIE1 Register 17                             |

| (RBIF Bit) 16, 33, 128                                | ADIE Bit                                     |

| RB0/INT Flag (INTF Bit)16                             | CCP1IE Bit 17                                |

| TMR0 Overflow Flag (T0IF Bit)16, 128                  | PSPIE Bit17                                  |

| INTRC Mode120                                         | RCIE Bit 17, 18                              |

| K                                                     | SSPIE Bit17                                  |

| KEELOQ Evaluation and Programming Tools144            | TMR1IE Bit 17                                |

|                                                       | TMR2IE Bit 17                                |

| L                                                     | PIE2 Register19                              |

| LVDCON 101                                            | Pinout Descriptions                          |

| M                                                     | PIC16C770 7                                  |

| Master Clear (MCLR)                                   | PIC16C770/7717                               |

|                                                       | PIC16C771 7                                  |

| MCLR Reset, Normal Operation                          | PIR1 Register18                              |

| MCLR Reset, SLEEP121, 123, 124                        | PIR2 Register                                |

| Memory Organization                                   | Pointer, FSR                                 |

| Data Memory9                                          | POR. See Power-on Reset                      |

| Program Memory9                                       | PORTA                                        |

| MPLAB C17 and MPLAB C18 C Compilers141                | Initialization                               |

| MPLAB ICD In-Circuit Debugger143                      | PORTA Register25                             |

| MPLAB ICE High Performance Universal In-Circuit       | TRISA Register25                             |

| Emulator with MPLAB IDE142                            | PORTA Register                               |

| MPLAB Integrated Development Environment Software 141 | PORTB                                        |

| MPLINK Object Linker/MPLIB Object Librarian142        | Initialization33                             |

| Multi-Master Communication94                          | PORTB Register                               |

| Multi-Master Mode84                                   | Pull-up Enable (RBPU Bit)                    |

| 0                                                     | RB0/INT Edge Select (INTEDG Bit)             |

| OPCODE Field Descriptions133                          | RB0/INT Pin, External                        |

| OPTION_REG Register                                   | RB7:RB4 Interrupt on Change                  |

| INTEDG Bit                                            | RB7:RB4 Interrupt on Change Enable           |

| PS Bits                                               | (RBIE Bit)                                   |

| PSA Bit                                               | ,                                            |

|                                                       | RB7:RB4 Interrupt on Change Flag             |

| RBPU Bit                                              | (RBIF Bit)                                   |

| TOCS Bit                                              | TRISB Register                               |

| TOSE Bit                                              | PORTB Register                               |

| Oscillator Configuration                              | Postscaler, Timer2                           |

| CLKOUT120                                             | Select (TOUTPS Bits)                         |

| Dual Speed Operation for ER and                       | Postscaler, WDT45                            |

| INTRC Modes                                           | Assignment (PSA Bit)                         |

| EC119, 123                                            | Block Diagram                                |

| ER119, 123                                            | Rate Select (PS Bits)                        |

| ER Mode120                                            | Switching Between Timer0 and WDT 46          |

| HS119, 123                                            | Power-down Mode. See SLEEP                   |

| INTRC 119, 123                                        | Power-on Reset (POR) 117, 121, 122, 123, 124 |

| LP119, 123                                            | Oscillator Start-up Timer (OST) 117, 122     |

| XT119, 123                                            | Power Control (PCON) Register123             |

| Oscillator, Timer1 47, 49                             | Power-down (PD Bit)14                        |

| Oscillator, WDT129                                    | Power-on Reset Circuit, External             |

| P                                                     | Power-up Timer (PWRT)117, 122                |

|                                                       | Time-out (TO Bit)14                          |

| P                                                     | Time-out Sequence                            |

| Packaging197                                          | Time-out Sequence on Power-up 125, 126       |

| Paging, Program Memory                                | PR2 Register                                 |

| Parallel Slave Port (PSP)                             | Prescaler, Capture54                         |

| Read/Write Enable (PSPIE Bit)                         | Prescaler, Timer0                            |

| PCL Register                                          | Assignment (PSA Bit)                         |

| PCLATH Register 11, 12, 13                            | Block Diagram                                |

| PCON Register 21, 123                                 | Rate Select (PS Bits)                        |

| PICDEM 1 Low Cost PIC MCU                             | Switching Between Timer0 and WDT46           |

| Demonstration Board143                                | Prescaler, Timer1                            |

| PICDEM 17 Demonstration Board144                      | Select (T1CKPS Bits)                         |

| PICDEM 2 Low Cost PIC16CXX                            | Gelect (1 10tt G Dita)47                     |

| Demonstration Board 143                               |                                              |

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1999-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769713

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.