## Microchip Technology - PIC16C771T-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c771t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name              | Function | Input<br>Type | Output<br>Type | Description                                 |

|-------------------|----------|---------------|----------------|---------------------------------------------|

| 546/4446          | RA0      | ST            | CMOS           | Bi-directional I/O                          |

| RA0/AN0           | AN0      | AN            |                | A/D input                                   |

|                   | RA1      | ST            | CMOS           | Bi-directional I/O                          |

| RA1/AN1/LVDIN     | AN1      | AN            |                | A/D input                                   |

|                   | LVDIN    | AN            |                | LVD input reference                         |

|                   | RA2      | ST            | CMOS           | Bi-directional I/O                          |

| RA2/AN2/VREF-/VRL | AN2      | AN            |                | A/D input                                   |

|                   | VREF-    | AN            |                | Negative analog reference input             |

|                   | VRL      |               | AN             | Internal voltage reference low output       |

|                   | RA3      | ST            | CMOS           | Bi-directional I/O                          |

|                   | AN3      | AN            |                | A/D input                                   |

| RA3/AN3/VREF+/VRH | VREF+    | AN            |                | Positive analog reference input             |

|                   | VRH      |               | AN             | Internal voltage reference high output      |

|                   | RA4      | ST            | OD             | Bi-directional I/O                          |

| RA4/T0CKI         | T0CKI    | ST            |                | TMR0 clock input                            |

|                   | RA5      | ST            |                | Input port                                  |

| RA5/MCLR/VPP      | MCLR     | ST            |                | Master clear                                |

|                   | Vpp      | Power         |                | Programming voltage                         |

|                   | RA6      | ST            | CMOS           | Bi-directional I/O                          |

| RA6/OSC2/CLKOUT   | OSC2     |               | XTAL           | Crystal/resonator                           |

|                   | CLKOUT   |               | CMOS           | Fosc/4 output                               |

|                   | RA7      | ST            | CMOS           | Bi-directional I/O                          |

| RA7/OSC1/CLKIN    | OSC1     | XTAL          |                | Crystal/resonator                           |

|                   | CLKIN    | ST            |                | External clock input/ER resistor connection |

|                   | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB0/AN4/INT       | AN4      | AN            |                | A/D input                                   |

|                   | INT      | ST            |                | Interrupt input                             |

|                   | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB1/AN5/SS        | AN5      | AN            |                | A/D input                                   |

|                   | SS       | ST            |                | SSP slave select input                      |

|                   | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB2/SCK/SCL       | SCK      | ST            | CMOS           | Serial clock I/O for SPI                    |

|                   | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C       |

|                   | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB3/CCP1/P1A      | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output            |

|                   | P1A      | -             | CMOS           | PWM P1A output                              |

|                   | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB4/SDI/SDA       | SDI      | ST            |                | Serial data in for SPI                      |

|                   | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C        |

|                   | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB5/SDO/P1B       | SDO      |               | CMOS           | Serial data out for SPI                     |

|                   | P1B      |               | CMOS           | PWM P1B output                              |

TABLE 1-1: PIC16C717/770/771 PINOUT DESCRIPTION

Note 1: Bit programmable pull-ups.

2: Only in PIC16C770/771 devices.

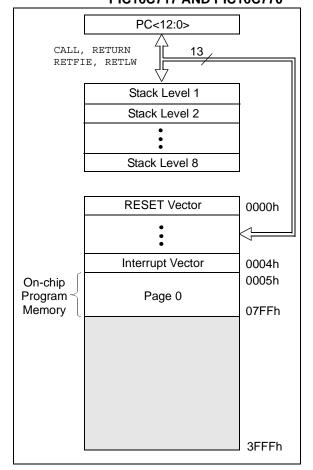

**PROGRAM MEMORY MAP**

FIGURE 2-2:

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual, (DS33023).

## 2.1 Program Memory Organization

The PIC16C717/770/771 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16C717 and the PIC16C770 have 2K x 14 words of program memory. The PIC16C771 has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wrap-around.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK OF THE PIC16C717 AND PIC16C770

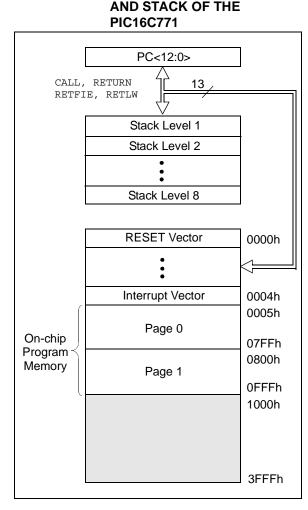

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1  | RP0                                                                    | (STATUS<6:5>) |

|------|------------------------------------------------------------------------|---------------|

| = 01 | <ul> <li>Bank0</li> <li>Bank1</li> <li>Bank2</li> <li>Bank3</li> </ul> |               |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some frequently used special function registers from one bank are mirrored in another bank for code reduction and quicker access.

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register FSR.

### FIGURE 2-3: REGISTER FILE MAP

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address | Δ                     | File<br>ddress |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|-----------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)     | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION REG            | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                   | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                   | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            | - I OIL               | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                 | 186h           |

|                                | 07h            |                                            | 87h            |                                            | 107h            |                       | 187h           |

|                                | 08h            |                                            | 88h            |                                            | 108h            |                       | 188h           |

|                                | 09h            |                                            | 89h            |                                            | 109h            |                       | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATL                                     | 10Ch            | PMCON1                | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADRL                                     | 10Dh            |                       | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                       | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                       | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                       | 190h           |

| TMR2                           | 11h            | SSPCON2                                    | 91h            |                                            | 111h            |                       | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                       | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                       | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                       | 194h           |

| CCPR1L                         | 15h            | WPUB                                       | 95h            |                                            | 115h            |                       | 195h           |

| CCPR1H                         | 16h            | IOCB                                       | 96h            |                                            | 116h            |                       | 196h           |

| CCP1CON                        | 17h            | P1DEL                                      | 97h            |                                            | 117h            |                       | 197h           |

|                                | 18h            |                                            | 98h            |                                            | 118h            |                       | 198h           |

|                                | 19h            |                                            | 99h            |                                            | 119h            |                       | 199h           |

|                                | 1Ah            |                                            | 9Ah            |                                            | 11Ah            |                       | 19Ah           |

|                                | 1Bh            | REFCON                                     | 9Bh            |                                            | 11Bh            |                       | 19Bh           |

|                                | 1Ch            | LVDCON                                     | 9Ch            |                                            | 11Ch            |                       | 19Ch           |

|                                | 1Dh            | ANSEL                                      | 9Dh            |                                            | 11Dh            |                       | 19Dh           |

| ADRESH                         | 1Eh            | ADRESL                                     | 9Eh            |                                            | 11Eh            |                       | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                       | 19Fh           |

|                                | 20h            |                                            | A0h            |                                            | 120h            |                       | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 |                       |                |

| 96 Bytes                       |                |                                            | EFh            |                                            | 16Fh            |                       | 1EFh           |

| -                              |                | accesses<br>70h-7Fh                        | F0h            | accesses<br>70h - 7Fh                      | 170h            | accesses<br>70h - 7Fh | 1F0h           |

| Bank 0                         | 7Fh            | Bank 1                                     | FFh            | Bank 2                                     | 17Fh            | Bank 3                | 1FFh           |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

#### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

## REGISTER 2-4: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (PIE1: 8Ch)

|         | U-0                                                                                                           | R/W-0                        | U-0                       | U-0          | R/W-0       | R/W-0     | R/W-0          | R/W-0  |  |

|---------|---------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|--------------|-------------|-----------|----------------|--------|--|

|         |                                                                                                               | ADIE                         | —                         | —            | SSPIE       | CCP1IE    | TMR2IE         | TMR1IE |  |

|         | bit 7                                                                                                         |                              |                           |              |             |           |                | bit 0  |  |

|         |                                                                                                               |                              |                           |              |             |           |                |        |  |

| bit 7   | Unimplem                                                                                                      | ented: Read                  | d as '0'                  |              |             |           |                |        |  |

| bit 6   | ADIE: A/D                                                                                                     | Converter In                 | nterrupt Ena              | ble bit      |             |           |                |        |  |

|         |                                                                                                               | s the A/D in<br>s the A/D in | •                         |              |             |           |                |        |  |

| bit 5-4 | Unimplem                                                                                                      | ented: Read                  | d as '0'                  |              |             |           |                |        |  |

| bit 3   | SSPIE: Syr                                                                                                    | nchronous S                  | Serial Port In            | terrupt Enab | ole bit     |           |                |        |  |

|         | <ul> <li>1 = Enables the SSP interrupt</li> <li>0 = Disables the SSP interrupt</li> </ul>                     |                              |                           |              |             |           |                |        |  |

| bit 2   | CCP1IE: C                                                                                                     | CP1 Interru                  | pt Enable bit             | t            |             |           |                |        |  |

|         |                                                                                                               | s the CCP1<br>s the CCP1     |                           |              |             |           |                |        |  |

| bit 1   | TMR2IE: T                                                                                                     | MR2 to PR2                   | 2 Match Inter             | rupt Enable  | bit         |           |                |        |  |

|         |                                                                                                               |                              | to PR2 mate<br>to PR2 mat |              |             |           |                |        |  |

| bit 0   | TMR1IE: T                                                                                                     | MR1 Overfle                  | ow Interrupt              | Enable bit   |             |           |                |        |  |

|         | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |                              |                           |              |             |           |                |        |  |

|         |                                                                                                               |                              |                           |              |             |           |                |        |  |

|         | Legend:                                                                                                       |                              |                           |              |             |           |                |        |  |

|         | R = Reada                                                                                                     | ble bit                      | W = W                     | ritable bit  | U = Unim    | plemented | bit, read as ' | 0'     |  |

|         | - n = Value                                                                                                   | at POR                       | '1' = Bi                  | t is set     | '0' = Bit i | s cleared | x = Bit is u   | nknown |  |

#### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the SSP bus collision and low voltage detect interrupts.

## REGISTER 2-6: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (PIE2: 8Dh)

|         | R/W-0       | U-0                           | U-0           | U-0           | R/W-0        | U-0       | U-0          | U-0    |  |  |

|---------|-------------|-------------------------------|---------------|---------------|--------------|-----------|--------------|--------|--|--|

|         | LVDIE       |                               | —             | —             | BCLIE        | _         | —            |        |  |  |

|         | bit 7       |                               |               |               |              |           |              | bit 0  |  |  |

|         |             |                               |               |               |              |           |              |        |  |  |

| bit 7   | LVDIE: Lov  | v Voltage De                  | etect Interru | ot Enable bit |              |           |              |        |  |  |

|         |             | 1 = LVD Interrupt is enabled  |               |               |              |           |              |        |  |  |

|         |             | 0 = LVD Interrupt is disabled |               |               |              |           |              |        |  |  |

| bit 6-4 | Unimpleme   | ented: Read                   | d as '0'      |               |              |           |              |        |  |  |

| bit 3   | BCLIE: Bus  | s Collision Ir                | nterrupt Ena  | ble bit       |              |           |              |        |  |  |

|         | 1 = Bus Co  | llision interr                | upt is enable | ed            |              |           |              |        |  |  |

|         | 0 = Bus Co  | llision interr                | upt is disabl | ed            |              |           |              |        |  |  |

| bit 2-0 | Unimpleme   | ented: Read                   | d as '0'      |               |              |           |              |        |  |  |

|         |             |                               |               |               |              |           |              |        |  |  |

|         | Legend:     |                               |               |               |              |           |              |        |  |  |

|         | R = Readal  | ole bit                       | W = W         | ritable bit   | U = Unim     | plemented | bit, read as | 0'     |  |  |

|         | - n = Value | at POR                        | '1' = Bi      | t is set      | '0' = Bit is | s cleared | x = Bit is u | nknown |  |  |

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: How to Clear RAM Using Indirect Addressing

|        | movlw | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | movwf | FSR   | ; to RAM             |

| NEXT   | clrf  | INDF  | ;clear INDF register |

|        | incf  | FSR   | ;inc pointer         |

|        | btfss | FSR,4 | ;all done?           |

|        | goto  | NEXT  | ;NO, clear next      |

| CONTIN | IUE   |       |                      |

|        | :     |       | ;YES, continue       |

|        |       |       |                      |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

## FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

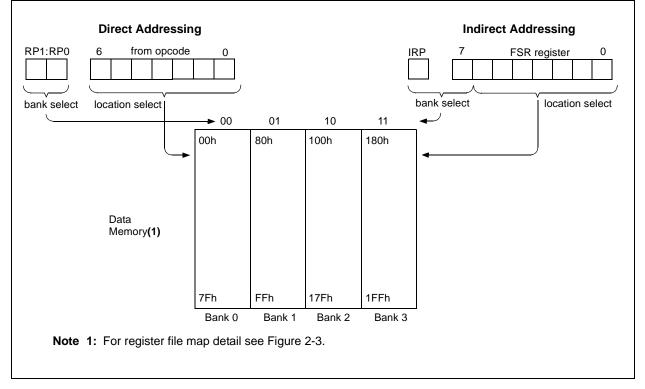

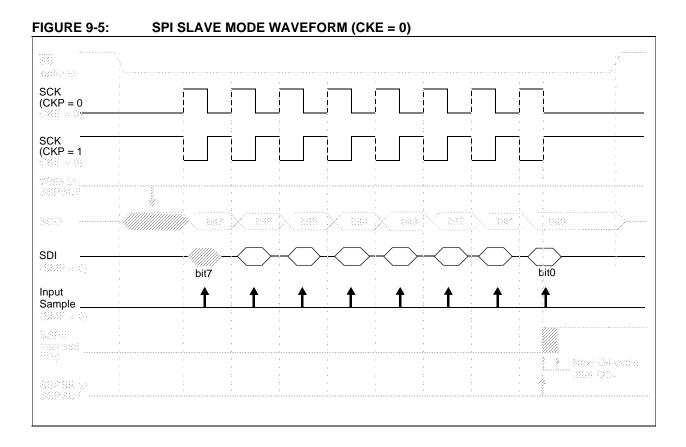

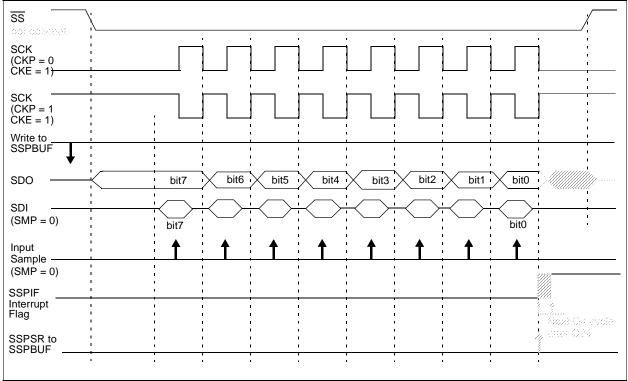

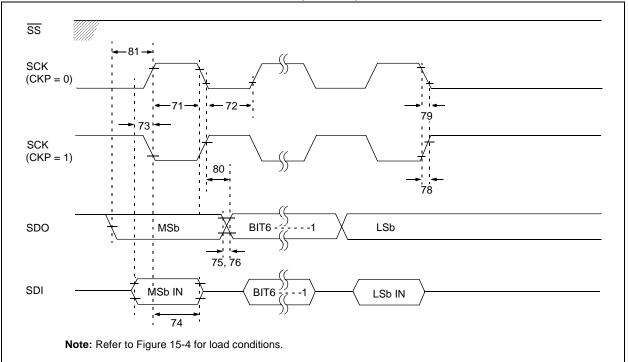

## 9.1 SPI Mode

The SPI mode allows eight bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

#### 9.1.1 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

Figure 9-1 shows the block diagram of the MSSP module when in SPI mode.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

The MSSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer Register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF (PIR1<3>), are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSP-BUF register completed successfully.

# PIC16C717/770/771

## FIGURE 9-6: SPI SLAVE MODE WAVEFORM (CKE = 1)

## 9.2.13 I<sup>2</sup>C MASTER MODE RECEPTION

In Master-receive mode, the first byte transmitted contains seven bits of address data and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. The START condition indicates the beginning of a transmission. The masterreceiver terminates slave transmission by responding to the last byte with a NACK Acknowledge and follows this with a STOP condition to indicate to other masters that the bus is free.

Master mode reception is enabled by setting the receive enable bit, RCEN (SSPCON2<3>), immediately following the Acknowledge sequence.

| Note: | The MSSP Module must be in an IDLE      |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | STATE before the RCEN bit is set or the |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.           |  |  |  |  |  |  |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the following events occur:

- The receive enable bit is automatically cleared.

- The contents of the SSPSR are loaded into the SSPBUF.

- The BF flag is set.

- The SSPIF is set.

- The baud rate generator is suspended from counting, holding SCL low.

The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception by clearing the ACKDT bit (SSPCON2<5>) and setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). A typical receive sequence would go as follows:

- a) The user generates a START Condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set at the completion of the START sequence.

- c) The user resets the SSPIF bit and loads the SSPBUF with seven bits of address in the MSbs and the LSb (R/W bit) set to '1' for receive.

- d) Address and R/W is shifted out the SDA pin until all eight bits are transmitted.

- e) The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user resets the SSPIF bit and sets the RCEN bit to enable reception.

- h) DATA is shifted into the SDA pin until all eight bits are received.

- The MSSP module sets the SSPIF bit and clears the RCEN bit at the falling edge of the eighth clock.

- j) The user resets the SSPIF bit and sets the ACKDT bit to '0' (ACK), if another byte is anticipated. Otherwise, the ACKDT bit is set to '1' (NACK) to terminate reception. The user sets ADKEN to start the Acknowledge sequence.

- k) The MSSP module sets the SSPIF bit at the completion of the Acknowledge.

- If a NACK was sent in step (j), then the user proceeds with step (m). Otherwise, reception continues by repeating steps (g) through (j).

- m) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- n) SSPIF is set when the STOP condition is complete.

#### 9.2.13.1 BF STATUS FLAG

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared by hardware when SSPBUF is read.

9.2.13.2 SSPOV STATUS FLAG

In receive operation, SSPOV is set when eight bits are received into the SSPSR and the BF flag is already set from a previous reception.

#### 9.2.13.3 WCOL STATUS FLAG

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

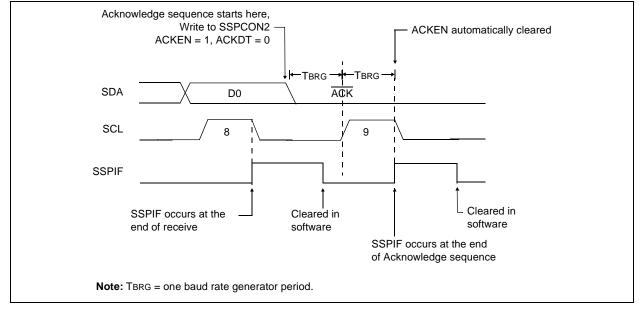

## 9.2.14 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit ACKDT (SSPCON2<5>) is presented on the SDA pin. If the user wishes to generate an Acknowledge (ACK), then the ACKDT bit should be cleared. Otherwise, the user should set the ACKDT bit (NACK) before starting an Acknowledge sequence. The baud rate generator is then loaded from SSPADD<6:0> and counts for one rollover period (TBRG). The SCL pin is then de-asserted (pulled high). When the SCL pin is sampled high (clock

arbitration), the baud rate generator is reloaded and counts for another TBRG. At the completion of the TBRG period, the following events occur (see Figure 9-20):

- The SCL pin is pulled low.

- The ACKEN bit is automatically cleared.

- The baud rate generator is turned off.

- The MSSP module goes into IDLE mode.

#### 9.2.14.1 WCOL STATUS FLAG

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-20: ACKNOWLEDGE SEQUENCE WAVEFORM

### 11.3 Selecting the A/D Conversion Clock

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. If neither the internal VRH nor VRL are used for the A/D converter, the four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- A/D RC oscillator

If the VRH or VRL are used for the A/D converter reference, then the TAD requirement is automatically increased by a factor of 8.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

| A/D Reference<br>Source           | A/D Clock | Source (TAD) |                             |                             |                             |                               |

|-----------------------------------|-----------|--------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|

|                                   | Operation | ADCS<1:0>    | 20 MHz                      | 5 MHz                       | 4 MHz                       | 1.25 MHz                      |

|                                   | 2 Tosc    | 00           | 100 ns <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.6 μs                        |

| External VREF or<br>Analog Supply | 8 Tosc    | 01           | 400 ns <sup>(2)</sup>       | 1.6 μs                      | 2.0 μs                      | 6.4 μs                        |

| Analog Supply                     | 32 Tosc   | 10           | 1.6 μs                      | 6.4 μs <sup>(3)</sup>       | 8.0 μs <sup>(3)</sup>       | 25.6 μs <sup>(3)</sup>        |

|                                   | A/D RC    | 11           | 2 - 6 μs <sup>(1,4)</sup>     |

| Internal VRH or                   | 16 Tosc   | 00           | 800 ns <sup>(2)</sup>       | 3.2 μs <sup>(2)</sup>       | 4 μs <sup>(2)</sup>         | 12.8 μs                       |

| VRL                               | 64 Tosc   | 01           | 3.2 μs <sup>(2)</sup>       | 12.8 μs                     | 16 μs                       | 51.2 μs <b><sup>(3)</sup></b> |

|                                   | 256 Tosc  | 10           | 12.8 μs                     | 51.2 μs <sup>(3)</sup>      | 64 μs <sup>(3)</sup>        | 204.8 μs <sup>(3)</sup>       |

|                                   | A/D RC    | 11           | 16 - 48 μs <sup>(4,5)</sup>   |

### TABLE 11-1: TAD vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

5: A/D RC clock source has a typical TAD time of 32  $\mu$ s for VDD > 3.0V.

| Register | Power-on Reset or<br>Brown-out Reset | MCLR Reset or<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|--------------------------------------|----------------------------|---------------------------------|

| P1DEL    | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| REFCON   | 0000                                 | 0000                       | uuuu                            |

| LVDCON   | 00 0101                              | 00 0101                    | uu uuuu                         |

| ANSEL    | 11 1111                              | 11 1111                    | uu uuuu                         |

| ADRESL   | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| ADCON1   | 0000 0000                            | 0000 0000                  | uuuu uuuu                       |

| PMDATL   | XXXX XXXX                            | uuuu uuuu                  | uuuu uuuu                       |

| PMADRL   | xxxx xxxx                            | uuuu uuuu                  | uuuu uuuu                       |

| PMDATH   | xx xxxx                              | uu uuuu                    | uu uuuu                         |

| PMADRH   | xxxx                                 | uuuu                       | uuuu                            |

| PMCON1   | 10                                   | 10                         | 10                              |

## TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition **Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

2: See Table 12-5 for RESET value for specific condition.

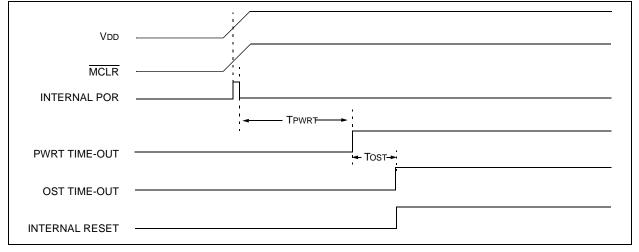

## FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

## 13.0 INSTRUCTION SET SUMMARY

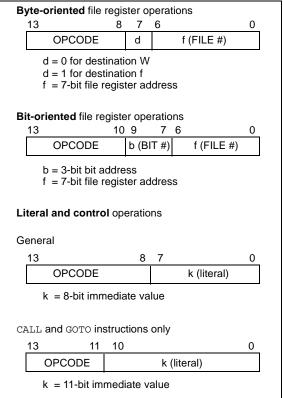

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W     | Working register (accumulator)                                                                                                                                                 |

| b     | Bit address within an 8-bit file register                                                                                                                                      |

| k     | Literal field, constant data or label                                                                                                                                          |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| PC    | Program Counter                                                                                                                                                                |

| TO    | Time-out bit                                                                                                                                                                   |

| PD    | Power-down bit                                                                                                                                                                 |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | То                                | maintain   | upward  | l compa  | tibility | with |  |

|-------|-----------------------------------|------------|---------|----------|----------|------|--|

|       | futu                              | ire PIC160 | CXXX pi | roducts, | do not   | use  |  |

|       | the OPTION and TRIS instructions. |            |         |          |          |      |  |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

| COMF             | Complement f                                                                                                                                            |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                              |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two<br>cycle instruction. |

| DECF             | Decrement f                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                               |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             |

| Status Affected: | Z                                                                                                                                               |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |

| INCF             | Increment f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                      |

| Status Affected: | Z                                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                        | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                            | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                               | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                    | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                          | Status Affected: | None                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead<br>making it a 2Tcy instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in regis-<br>ter 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead making<br>it a 2TCY instruction. |

## TABLE 15-12: PIC16C770/771 AND PIC16LC770/771 A/D CONVERSION REQUIREMENTS (NORMAL MODE)

| Parameter<br>No.    | Sym  | Characteristic                                                     | Min    | Тур†   | Мах | Units | Conditions                                                                                                                                                                                                                  |

|---------------------|------|--------------------------------------------------------------------|--------|--------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D clock period                                                   | 1.6    | —      | _   | μS    | Tosc based, VREF $\geq$ 2.5V                                                                                                                                                                                                |

|                     |      |                                                                    | 3.0    | —      | —   | μS    | Tosc based, VREF full range                                                                                                                                                                                                 |

|                     |      |                                                                    | 3.0    | 6.0    | 9.0 | μS    | ADCS<1:0> = 11<br>(A/D RC mode)<br>At VDD = 2.5V                                                                                                                                                                            |

|                     |      |                                                                    | 2.0    | 4.0    | 6.0 | μs    | At VDD = 5.0V                                                                                                                                                                                                               |

| 131*                | TCNV | Conversion time<br>(not including<br>acquisition time)<br>(Note 1) | _      | 13Tad  | —   | TAD   |                                                                                                                                                                                                                             |

| 132*                | TACQ | Acquisition Time                                                   | Note 2 | 11.5   | —   | μS    |                                                                                                                                                                                                                             |

|                     |      |                                                                    | 5*     | _      | _   | μs    | The minimum time is the ampli-<br>fier settling time. This may be<br>used if the "new" input voltage<br>has not changed by more than<br>1LSb (i.e., 1mV @ 4.096V) from<br>the last sampled voltage (as<br>stated on CHOLD). |

| 134*                | TGO  | Q4 to A/D clock start                                              | —      | Tosc/2 | —   | —     |                                                                                                                                                                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

**2:** See Section 11.6 for minimum conditions.

**3:** These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

| Param.<br>No. | Sym   | Characteristic                                       | Min   | Тур†   | Max       | Units | Conditions                                                                                                                               |

|---------------|-------|------------------------------------------------------|-------|--------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| A01           | NR    | Resolution                                           | _     | _      | 10 bits   | bit   | Min. resolution for A/D is 4.1 mV,<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- $\leq$ VAIN $\leq$ VREF+                     |

| A03           | EIL   | Integral error                                       |       | _      | ±1        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A04           | EDL   | Differential error                                   |       | _      | ±1        | LSb   | No missing codes to 10 bits<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>$VREF- \le VAIN \le VREF+$                                |

| A06           | EOFF  | Offset error                                         |       | _      | ±2        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A07           | Egn   | Gain Error                                           | _     | _      | ±1        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A10           |       | Monotonicity                                         | _     | Note 3 | —         |       | $AVSS \leq VAIN \leq VREF+$                                                                                                              |

| A20*          | Vref  | Reference voltage<br>(VREF+ - VREF-)                 | 4.096 | _      | VDD +0.3V | V     | Absolute minimum electrical spec to<br>ensure 10-bit accuracy.                                                                           |

| A21*          | VREF+ | Reference V High<br>(Avdd or VREF+)                  | VREF- | _      | AVdd      | V     | Min. resolution for A/D is 4.1 mV                                                                                                        |

| A22*          | VREF- | Reference V Low<br>(Avss or VREF-)                   | AVss  | _      | VREF+     | V     | Min. resolution for A/D is 4.1 mV                                                                                                        |

| A25*          | VAIN  | Analog input voltage                                 | VREFL | _      | VREFH     | V     |                                                                                                                                          |

| A30*          | Zain  | Recommended<br>impedance of analog<br>voltage source | _     | —      | 2.5       | kΩ    |                                                                                                                                          |

| A50*          | IREF  | VREF input current<br>(Note 2)                       |       | _      | 10        | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN.<br>To charge CHOLD see Section 11.0.<br>During A/D conversion cycle. |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from External VREF+, or VREF-, or AVSS, or AVDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

t

### TABLE 15-18: SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteristic                            | Min         | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 71*           | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | -   | _     | ns         |        |

| 71A*          |                       | (Slave mode)                              | Single Byte | 40           | —   | _     | ns         | Note 1 |

| 72*           | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | _   |       | ns         |        |

| 72A*          |                       | (Slave mode)                              | Single Byte | 40           | _   |       | ns         | Note 1 |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data in edge            | put to SCK  | 100          | _   | —     | ns         |        |

| 73A*          | Тв2в                  | Last clock edge of Byte1<br>edge of Byte2 | 1.5Tcy + 40 | —            | —   | ns    | Note 1     |        |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data inp                 | 100         | _            | _   | ns    |            |        |

| 75*           | TdoR                  | SDO data output rise                      | PIC16CXXX   | —            | 10  | 25    | ns         |        |

|               |                       | time                                      | PIC16LCXXX  |              | 20  | 45    | ns         |        |

| 76*           | TdoF                  | SDO data output fall time                 |             | —            | 10  | 25    | ns         |        |

| 78*           | TscR                  | SCK output rise time                      | PIC16CXXX   | —            | 10  | 25    | ns         |        |

|               |                       | (Master mode)                             | PIC16LCXXX  |              | 20  | 45    | ns         |        |

| 79*           | TscF                  | SCK output fall time (Master mode)        |             | —            | 10  | 25    | ns         |        |

| 80*           | TscH2doV,             | SDO data output valid PIC16CXXX           |             | _            | _   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                            | PIC16LCXXX  |              | _   | 100   | ns         |        |

| 81*           | TdoV2scH,<br>TdoV2scL | SDO data output setup to                  | SCK edge    | Тсү          |     |       | ns         |        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

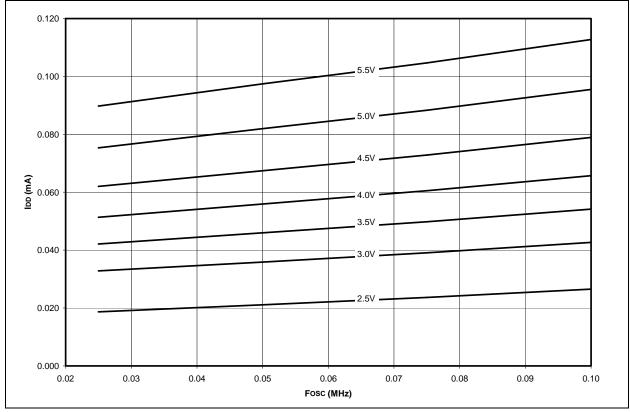

# PIC16C717/770/771

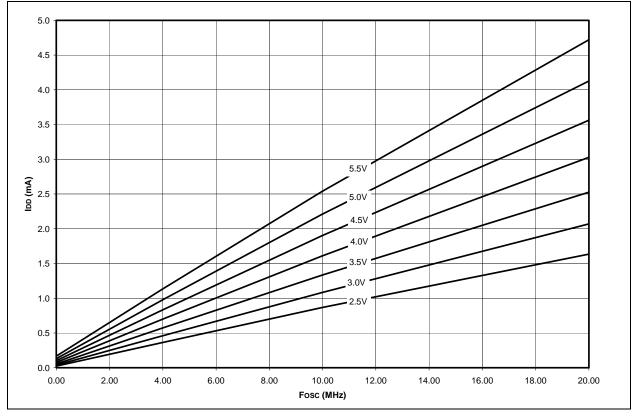

FIGURE 16-7: MAXIMUM IDD VS. FOSC OVER VDD (EC MODE)

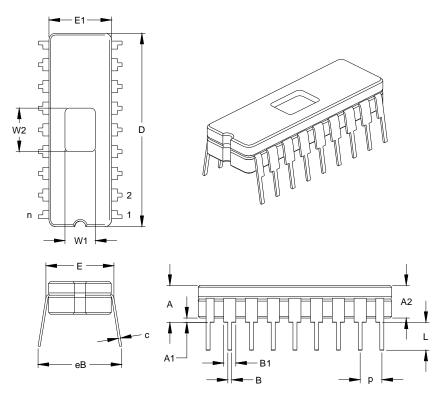

#### 18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP) 17.3

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      |      | INCHES* |       |       | MILLIMETERS |  |  |  |

|----------------------------|-------|------|------|---------|-------|-------|-------------|--|--|--|

| Dimension                  | MIN   | NOM  | MAX  | MIN     | NOM   | MAX   |             |  |  |  |

| Number of Pins             | n     |      | 18   |         |       | 18    |             |  |  |  |

| Pitch                      | р     |      | .100 |         |       | 2.54  |             |  |  |  |

| Top to Seating Plane       | Α     | .170 | .183 | .195    | 4.32  | 4.64  | 4.95        |  |  |  |

| Ceramic Package Height     | A2    | .155 | .160 | .165    | 3.94  | 4.06  | 4.19        |  |  |  |

| Standoff                   | A1    | .015 | .023 | .030    | 0.38  | 0.57  | 0.76        |  |  |  |

| Shoulder to Shoulder Width | Е     | .300 | .313 | .325    | 7.62  | 7.94  | 8.26        |  |  |  |

| Ceramic Pkg. Width         | E1    | .285 | .290 | .295    | 7.24  | 7.37  | 7.49        |  |  |  |

| Overall Length             | D     | .880 | .900 | .920    | 22.35 | 22.86 | 23.37       |  |  |  |

| Tip to Seating Plane       | L     | .125 | .138 | .150    | 3.18  | 3.49  | 3.81        |  |  |  |

| Lead Thickness             | С     | .008 | .010 | .012    | 0.20  | 0.25  | 0.30        |  |  |  |

| Upper Lead Width           | B1    | .050 | .055 | .060    | 1.27  | 1.40  | 1.52        |  |  |  |

| Lower Lead Width           | В     | .016 | .019 | .021    | 0.41  | 0.47  | 0.53        |  |  |  |

| Overall Row Spacing        | eB    | .345 | .385 | .425    | 8.76  | 9.78  | 10.80       |  |  |  |

| Window Width               | W1    | .130 | .140 | .150    | 3.30  | 3.56  | 3.81        |  |  |  |

| Window Length              | W2    | .190 | .200 | .210    | 4.83  | 5.08  | 5.33        |  |  |  |

\*Controlling Parameter JEDEC Equivalent: MO-036 Drawing No. C04-010

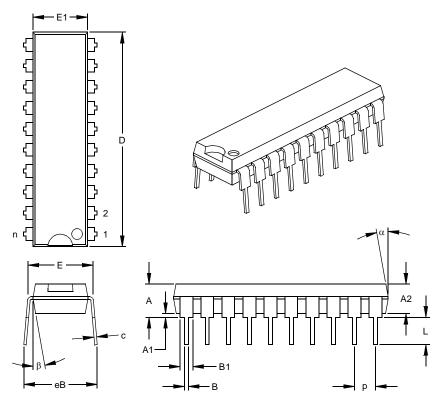

#### 20-Lead Plastic Dual In-line (P) - 300 mil (PDIP) 17.5

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

| Units            |                                                                                     | INCHES*                                                                                                                                                                                                                                                                                                                                                     |                                                        | MILLIMETERS                                            |                                                        |                                                        |  |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| Dimension Limits |                                                                                     |                                                                                                                                                                                                                                                                                                                                                             | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |  |

| n                |                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 20                                                     |                                                        |  |

| р                |                                                                                     | .100                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        | 2.54                                                   |                                                        |  |

| А                | .140                                                                                | .155                                                                                                                                                                                                                                                                                                                                                        | .170                                                   | 3.56                                                   | 3.94                                                   | 4.32                                                   |  |

| A2               | .115                                                                                | .130                                                                                                                                                                                                                                                                                                                                                        | .145                                                   | 2.92                                                   | 3.30                                                   | 3.68                                                   |  |

| A1               | .015                                                                                |                                                                                                                                                                                                                                                                                                                                                             |                                                        | 0.38                                                   |                                                        |                                                        |  |

| Е                | .295                                                                                | .310                                                                                                                                                                                                                                                                                                                                                        | .325                                                   | 7.49                                                   | 7.87                                                   | 8.26                                                   |  |

| E1               | .240                                                                                | .250                                                                                                                                                                                                                                                                                                                                                        | .260                                                   | 6.10                                                   | 6.35                                                   | 6.60                                                   |  |

| D                | 1.025                                                                               | 1.033                                                                                                                                                                                                                                                                                                                                                       | 1.040                                                  | 26.04                                                  | 26.24                                                  | 26.42                                                  |  |

| L                | .120                                                                                | .130                                                                                                                                                                                                                                                                                                                                                        | .140                                                   | 3.05                                                   | 3.30                                                   | 3.56                                                   |  |