Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc717-e-so |

Data Latch Data Bus D WR Port **√**\_ Q CK TRIS Latch N Q WR T<u>RIS</u> ск ҇⊾ ҳ Vss Vss RD T<u>RIS</u> Schmitt Trigger Input Buffer Q D ΕN RD PORT TMR0 clock input

FIGURE 3-3: BLOCK DIAGRAM OF RA4/T0CKI

To MCLR Circuit

Program Mode

HV Detect

Data

Bus

RD

TRIS

Vss

Schmitt

Trigger

RD PORT

FIGURE 3-4: BLOCK DIAGRAM OF RA5/MCLR/VPP

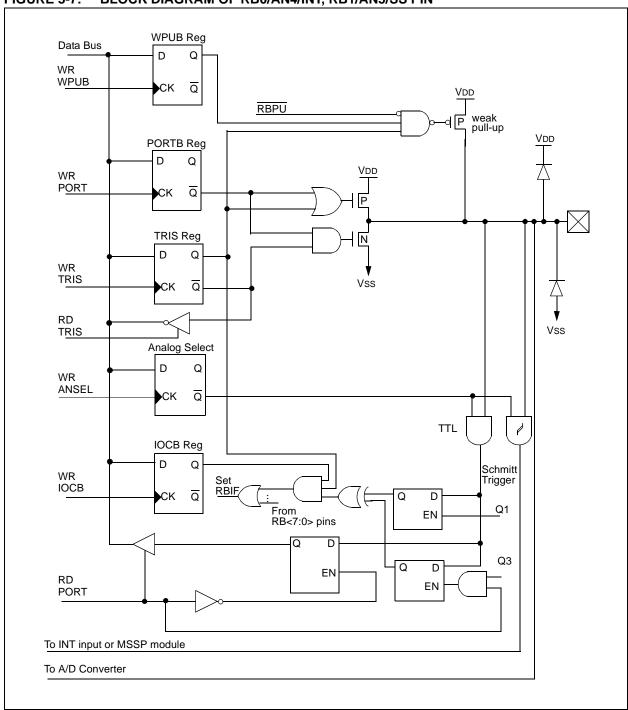

The RB0 pin is multiplexed with the A/D converter analog input 4 and the external interrupt input (RB0/AN4/INT). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB0 pin as Analog mode.

The RB1 pin is multiplexed with the A/D converter analog input 5 and the MSSP module slave select input (RB1/AN5/ $\overline{SS}$ ). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB1 pin as Analog mode.

Note: Upon RESET, the ANSEL register configures the RB1 and RB0 pins as analog inputs.

Both RB1 and RB0 pins will read as '1'.

FIGURE 3-7: BLOCK DIAGRAM OF RB0/AN4/INT, RB1/AN5/SS PIN

#### 7.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

#### 7.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 7-1: **Timer2 Block Diagram** Sets flag TMR2 output (1) bit TMR2IF Prescaler TMR2 reg 1:1, 1:4, 1:16 Postscaler 2 Comparator 1:1 to 1:16 PR2 reg Note: TMR2 register output can be software selected by the SSP Module as a baud clock.

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name                       | Bit 7           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|----------------------------|-----------------|---------|---------|---------|---------|--------|-----------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON                     | GIE             | PEIE    | TOIE    | INTE    | RBIE    | TOIF   | INTF      | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1                       |                 | ADIF    | 1       | 1       | SSPIF   | CCP1IF | TMR2IF    | TMR1IF    | -0 0000                  | -0 0000                         |

| 8Ch                   | PIE1                       | -               | ADIE    | 1       | -       | SSPIE   | CCP1IE | TMR2IE    | TMR1IE    | -0 0000                  | -0 0000                         |

| 11h                   | TMR2                       | Timer2 register |         |         |         |         |        |           | 0000 0000 | 0000 0000                |                                 |

| 12h                   | T2CON                      | _               | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1   | T2CKPS0   | -000 0000                | -000 0000                       |

| 92h                   | PR2 Timer2 Period Register |                 |         |         |         |         |        | 1111 1111 | 1111 1111 |                          |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

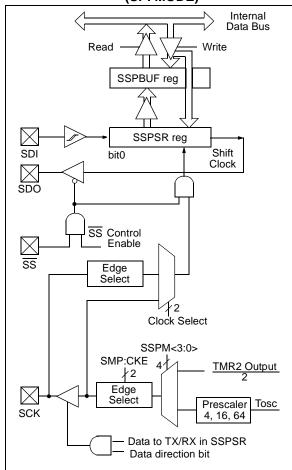

#### 9.1 SPI Mode

The SPI mode allows eight bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- · Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

#### 9.1.1 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

Figure 9-1 shows the block diagram of the MSSP module when in SPI mode.

FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

The MSSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer Register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT<0>), and the interrupt flag bit, SSPIF (PIR1<3>), are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSP-BUF register completed successfully.

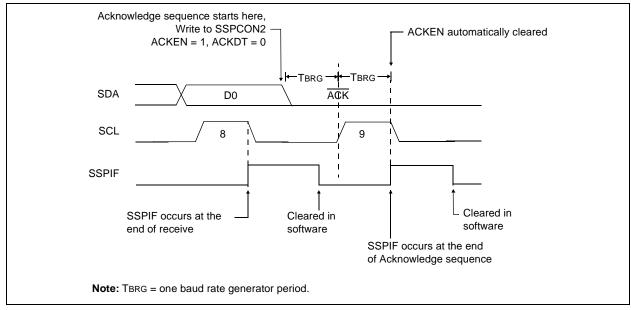

### 9.2.14 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge sequence enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit ACKDT (SSPCON2<5>) is presented on the SDA pin. If the user wishes to generate an Acknowledge (ACK), then the ACKDT bit should be cleared. Otherwise, the user should set the ACKDT bit (NACK) before starting an Acknowledge sequence. The baud rate generator is then loaded from SSPADD<6:0> and counts for one rollover period (TBRG). The SCL pin is then de-asserted (pulled high). When the SCL pin is sampled high (clock

arbitration), the baud rate generator is reloaded and counts for another TBRG. At the completion of the TBRG period, the following events occur (see Figure 9-20):

- The SCL pin is pulled low.

- · The ACKEN bit is automatically cleared.

- The baud rate generator is turned off.

- The MSSP module goes into IDLE mode.

#### 9.2.14.1 WCOL STATUS FLAG

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-20: ACKNOWLEDGE SEQUENCE WAVEFORM

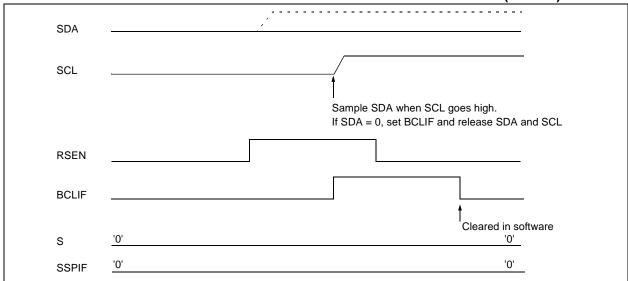

### 9.2.17.2 BUS COLLISION DURING A REPEATED START CONDITION

During a Repeated START condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the master module de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0>, and counts down to '0'. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data

'0'). If however SDA is sampled high, then the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, then a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition.

If at the end of the BRG time-out both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded, and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete (Figure 9-27).

#### FIGURE 9-28: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

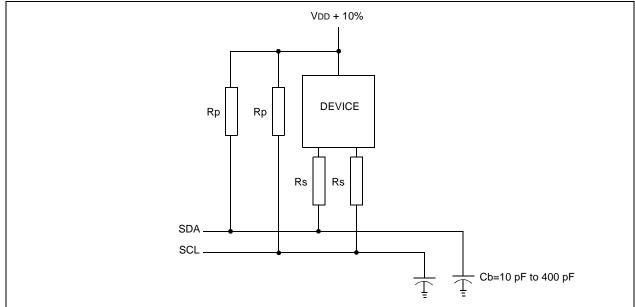

### 9.2.18 CONNECTION CONSIDERATIONS FOR I<sup>2</sup>C BUS

For Standard mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-31 depends on the following parameters

- · Supply voltage

- · Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at Vol max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_{p \ min}$  = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $\textit{R}_{p}$  is shown in Figure 9-31. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $\textit{R}_{s}$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-31).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in I<sup>2</sup>C mode (master or slave).

#### FIGURE 9-31: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

Note: I<sup>2</sup>C devices with input levels related to VDD must have one common supply line to which the pull-up resistor is also connected.

#### TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                | Name    | Bit 7 | Bit 6                                                            | Bit 5      | Bit 4       | Bit 3       | Bit 2        | Bit 1    | Bit 0     | POR, BOR  | MCLR, WDT |

|------------------------|---------|-------|------------------------------------------------------------------|------------|-------------|-------------|--------------|----------|-----------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE   | PEIE                                                             | TOIE       | INTE        | RBIE        | TOIF         | INTF     | RBIF      | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | _     | ADIF                                                             | _          | _           | SSPIF       | CCP1IF       | TMR2IF   | TMR1IF    | -0 0000   | -0 0000   |

| 8Ch                    | PIE1    | _     | ADIE                                                             | _          | _           | SSPIE       | CCP1IE       | TMR2IE   | TMR1IE    | -0 0000   | -0 0000   |

| 0Dh                    | PIR2    | LVDIF | _                                                                | _          | _           | BCLIF       | _            | _        | CCP2IF    | 0 00      | 0 00      |

| 8Dh                    | PIE2    | LVDIE | _                                                                | _          | _           | BCLIE       | _            | _        | CCP2IE    | 0 00      | 0 00      |

| 13h                    | SSPBUF  |       | Synch                                                            | ronous Ser | ial Port Re | ceive Buffe | r/Transmit F | Register |           | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL  | SSPOV                                                            | SSPEN      | CKP         | SSPM3       | SSPM2        | SSPM1    | SSPM0     | 0000 0000 | 0000 0000 |

| 91h                    | SSPCON2 | GCEN  | ACKSTAT                                                          | ACKDT      | ACKEN       | RCEN        | PEN          | RSEN     | SEN       | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP   | CKE                                                              | D/Ā        | Р           | S           | R/W          | UA       | BF        | 0000 0000 | 0000 0000 |

| 93h                    | SSPADD  |       | Synchronous Serial Port (I <sup>2</sup> C Mode) Address Register |            |             |             |              |          | 0000 0000 | 0000 0000 |           |

Legend: x = unknown, u = unchanged,  $- = unimplemented read as '0'. Shaded cells are not used by the MSSP in <math>I^2C$  mode.

#### 10.3 Low Voltage Detect (LVD)

This module is used to generate an interrupt when the supply voltage falls below a specified "trip" voltage. This module operates completely under software control. This allows a user to power the module on and off to periodically monitor the supply voltage, and thus minimize total current consumption.

The LVD module is enabled by setting the LVDEN bit in the LVDCON register. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to or less than the trip point, the module will generate an interrupt signal setting interrupt flag bit LVDIF. If interrupt enable bit LVDIE was set, then an interrupt is generated. The LVD interrupt can wake the device from SLEEP. The "trip point" voltage is software programmable to any one of 16 values, five of which are reserved (See Figure 10-1). The trip point is selected by programming the LV<3:0> bits (LVDCON<3:0>).

Note:

The LVDIF bit can not be cleared until the supply voltage rises above the LVD trip point. If interrupts are enabled, clear the LVDIE bit once the first LVD interrupt occurs to prevent reentering the interrupt service routine immediately after exiting the ISR.

Once the LV bits have been programmed for the specified trip voltage, the low-voltage detect circuitry is then enabled by setting the LVDEN (LVDCON<4>) bit.

If the bandgap reference voltage is previously unused by either the brown-out circuitry or the voltage reference circuitry, then the bandgap circuit requires a time to start-up and become stable before a low voltage condition can be reliably detected. The low-voltage interrupt flag is prevented from being set until the bandgap has reached a stable reference voltage.

When the bandgap is stable the BGST (LVDCON<5>) bit is set indicating that the low-voltage interrupt flag bit is released to be set if VDD is equal to or less than the LVD trip point.

#### 10.3.1 EXTERNAL ANALOG VOLTAGE INPUT

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when LV<3:0>=1111. When these bits are set the comparator input is multiplexed from an external input pin (RA1/AN1/LVDIN).

#### 11.4 A/D Conversions

Example 11-1 shows an example that performs an A/D conversion. The port pins are configured as analog inputs. The analog reference VREF+ is the device AVDD and the analog reference VREF- is the device AVSS. The A/D interrupt is enabled and the A/D conversion clock is TRC. The conversion is performed on the ANO channel.

#### **EXAMPLE 11-1: PERFORMING AN A/D CONVERSION**

```

STATUS, RPO

;Select Bank 1

CLRF

ADCON1

;Configure A/D Voltage Reference

MOVLW

0 \times 01

MOVWE ANSEL

disable ANO digital input buffer;

;RAO is input mode

MOVWF TRISA

PIE1, ADIE ;Enable A/D interrupt

BSF

STATUS, RPO ;Select Bank 0

BCF

MOVLW 0xC1

;RC clock, A/D is on,

;Ch 0 is selected

MOVWF ADCON0

BCF

PIR1, ADIF

;Clear A/D Int Flag

INTCON, PEIE ;Enable Peripheral

INTCON, GIE ;Enable All Interm

BSF

;Enable All Interrupts

BSF

; Ensure that the required sampling time for the

; selected input channel has lapsed. Then the

; conversion may be started.

BSF

ADCONO, GO ;Start A/D Conversion

;The ADIF bit will be

;set and the GO/DONE bit

;cleared upon completion-

;of the A/D conversion.

; Wait for A/D completion and read ADRESH: ADRESL for result.

```

#### REGISTER 12-1: CONFIGURATION WORD FOR 16C717/770/771 DEVICE

| CP                | CP                                                                                                                                              | BORV1                                                                                                                           | BORV0                                                                                                                                  | CP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CP                                                                                    | _                                                                  | BODEN                                                                                          | MCLRE                                                            | PWRTE                                                                        | WDTE                                                        | FOSC2         | FOSC1 | FOSC0 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|-------|-------|

| bit13             |                                                                                                                                                 | •                                                                                                                               |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                | •                                                                | . L                                                                          |                                                             |               |       | bit0  |

| bit 13-12,<br>9-8 | 1 =                                                                                                                                             | CP: Program Memory Code Protection  1 = Code protection off  0 = All program memory is protected <sup>(2)</sup>                 |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 11-10:        | BORV<1:0>: Brown-out Reset Voltage bits  00 = VBoR set to 4.5V  01 = VBoR set to 4.2V  10 = VBoR set to 2.7V  11 = VBOR set to 2.5V             |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 7:            | Unir                                                                                                                                            | mplement                                                                                                                        | ed: Read a                                                                                                                             | as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 6:            | 1 =                                                                                                                                             | BODEN: Brown-out Detect Reset Enable bit <sup>(1)</sup> 1 = Brown-out Detect Reset enabled  0 = Brown-out Detect Reset disabled |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 5:            | MCLRE: RA5/MCLR pin function select  1 = RA5/MCLR pin function is MCLR  0 = RA5/MCLR pin function is digital input, MCLR internally tied to VDD |                                                                                                                                 |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 4:            | 1 =                                                                                                                                             | PWRTE: Power-up Timer Enable bit <sup>(1)</sup> 1 = PWRT disabled  0 = PWRT enabled                                             |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 3:            | 1 = '                                                                                                                                           | <b>TE:</b> Watch<br>WDT enat<br>WDT disal                                                                                       |                                                                                                                                        | Enable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | it                                                                                    |                                                                    |                                                                                                |                                                                  |                                                                              |                                                             |               |       |       |

| bit 2-0:          | 000<br>001<br>010<br>011<br>100<br>101                                                                                                          | = LP osci<br>= XT osci<br>= HS osci<br>= EC: I/O<br>= INTRC<br>= INTRC<br>= ER osci                                             | Oscillator S<br>Illator: Crysillator: Crysillator: Crysillator: Crysillator: Uncolor or oscillator: Uncolor illator: I/O fillator: CLK | tal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal/Resortal | nator on F<br>nator on F<br>nator on I<br>SC2/CLK<br>on on RA<br>function<br>on RA6/O | RA6/OSC:<br>RA6/OSC<br>OUT pin,<br>6/OSC2/C<br>on RA6/C<br>SC2/CLK | 2/CLKOU <sup>*</sup><br>2/CLKOU <sup>*</sup><br>CLKIN fur<br>CLKOUT p<br>SC2/CLK<br>OUT pin, I | T and RAT T and RAT notion on I nin, I/O fur OUT pin, Resistor o | 7/OSC1/C<br>7/OSC1/C<br>RA7/OSC1<br>nction on F<br>I/O function<br>on RA7/OS | LKIN<br>LKIN<br>1/CLKIN<br>RA7/OSC<br>on on RA7<br>SC1/CLKI | 7/OSC1/C<br>N | LKIN  |       |

Note 1: Enabling Brown-out Reset automatically enables the Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled.

2: All of the  $\overline{\text{CP}}$  bits must be given the same value to enable code protection.

| eaend |  |  |

|-------|--|--|

|       |  |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR 1 = bit is set 0 = bit is cleared x = bit is unknown

### 13.1 Instruction Descriptions

| Add Literal and W                                                                                                 | P                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [label] ADDLW k                                                                                                   | S                                                                                                                                                                            |

| $0 \leq k \leq 255$                                                                                               | C                                                                                                                                                                            |

| $(W) + k \rightarrow (W)$                                                                                         |                                                                                                                                                                              |

| C, DC, Z                                                                                                          | (                                                                                                                                                                            |

| The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. | 5                                                                                                                                                                            |

|                                                                                                                   | [label] ADDLW k $0 \le k \le 255$ (W) + k $\rightarrow$ (W) C, DC, Z The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W |

| ANDWF            | AND W with f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                 |

| Operation:       | $(W) + (f) \to (destination)$                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BCF              | Bit Clear f                         |

|------------------|-------------------------------------|

| Syntax:          | [label] BCF f,b                     |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |

| Operation:       | $0 \rightarrow (f < b >)$           |

| Status Affected: | None                                |

| Description:     | Bit 'b' in register 'f' is cleared. |

|                  |                                     |

| ANDLW            | AND Literal with W                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                               |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register. |

| BSF              | Bit Set f                                                              |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] BSF f,b                                                        |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                              |

| Status Affected: | None                                                                   |

| Description:     | Bit 'b' in register 'f' is set.                                        |

| IORLW            | Inclusive OR Literal with W                                                                                      | MOVLW            | Move Literal to W                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                  | Syntax:          | [ label ] MOVLW k                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                     | Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | Z                                                                                                                | Status Affected: | None                                                                                       |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. | Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                     | MOVWF            | Move W to f                       |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                       | Syntax:          | [ label ] MOVWF f                 |  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                       | Operands:        | $0 \leq f \leq 127$               |  |

|                  | $d \in [0,1]$ (W) .OR. (f) $\rightarrow$ (destination)                                                                                                    | Operation:       | $(W) \rightarrow (f)$             |  |

| Operation:       |                                                                                                                                                           | Status Affected: | None                              |  |

| Status Affected: | Z                                                                                                                                                         | Description:     | Move data from W register to reg- |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |                  | ister 'f'.                        |  |

| MOVF             | Move f                                                                                                                                                                                                                                                   |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                       |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                       |  |

| Operation:       | $(f) \rightarrow (destination)$                                                                                                                                                                                                                          |  |

| Status Affected: | Z                                                                                                                                                                                                                                                        |  |

| Description:     | The contents of register f are moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |  |

| No Operation  |

|---------------|

| [ label ] NOP |

| None          |

| No operation  |

| None          |

| No operation. |

|               |

|               |

|               |

|               |

#### 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming™ protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

#### 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

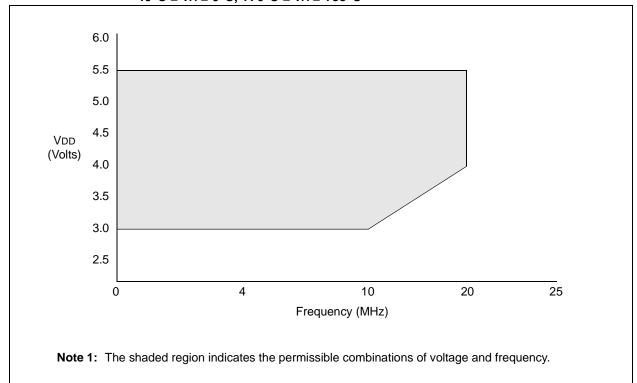

FIGURE 15-3: PIC16LC717/770/771 VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}\text{C} \leq \text{Ta} \leq 0^{\circ}\text{C}, \ +70^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$

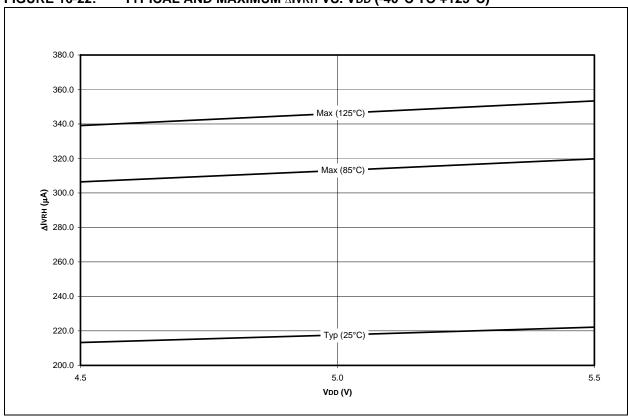

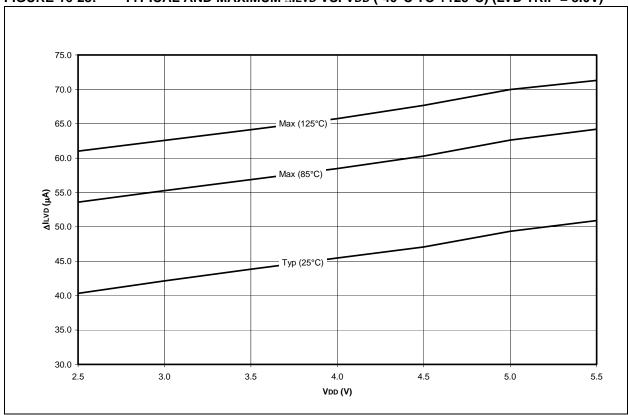

FIGURE 16-22: TYPICAL AND MAXIMUM AIVRH VS. VDD (-40°C TO +125°C)

NOTES:

### **APPENDIX A: REVISION HISTORY**

| Version | Date     | Revision Description                                                                                                                                                |  |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| А       | 09/14/99 | This is a new data sheet. However, the devices described in this data sheet are the upgrades to the devices found in the <i>PIC16C7X Data Sheet</i> , DS30390E.     |  |

| В       | 1/22/02  | Electrical Characteristics tables completed and characteristics graphs added. MSSP I <sup>2</sup> C (Section 9.2) rewritten. General minor changes and corrections. |  |

| С       | 1/28/13  | Added a note to each package outline drawing.                                                                                                                       |  |

|         |          |                                                                                                                                                                     |  |

#### **INDEX**

| Α                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------|

| A/D                                                                                                                       |

| A/D Converter Enable (ADIE Bit)17                                                                                         |

| ADCON0 Register105                                                                                                        |

| ADCON1 Register105, 107                                                                                                   |

| ADRES Register105                                                                                                         |

| Block Diagram109                                                                                                          |

| Configuring Analog Port                                                                                                   |

| Conversion time                                                                                                           |

|                                                                                                                           |

| Conversions                                                                                                               |

| converter characteristics 164, 165, 166, 170                                                                              |

| Faster Conversion - Lower Resolution Tradeoff 115                                                                         |

| Internal Sampling Switch (Rss) Impedence113                                                                               |

| Operation During Sleep116                                                                                                 |

| Sampling Requirements113                                                                                                  |

| Sampling Time113                                                                                                          |

| Source Impedance113                                                                                                       |

| Special Event Trigger (ECCP)55                                                                                            |

| A/D Conversion Clock110                                                                                                   |

| ACK77                                                                                                                     |

| Acknowledge Data bit, AKD69                                                                                               |

| Acknowledge Sequence Enable bit, AKE                                                                                      |

| Acknowledge Status bit, AKS                                                                                               |

|                                                                                                                           |

| ACKSTAT                                                                                                                   |

| ADCON0 Register                                                                                                           |

| ADCON1 Register                                                                                                           |

| ADRES105                                                                                                                  |

| ADRES Register 11, 12, 105, 116                                                                                           |

| AKD69                                                                                                                     |

| AKE69                                                                                                                     |

| AVC 60                                                                                                                    |

| AKS69                                                                                                                     |

|                                                                                                                           |

| Analog-to-Digital Converter. See A/D                                                                                      |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module                                       |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |