Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

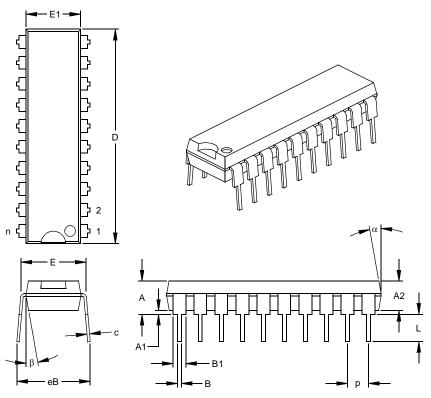

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc717-i-p |

#### 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro™ Mid-Range MCU Family Reference Manual, (DS33023).

#### 2.1 Program Memory Organization

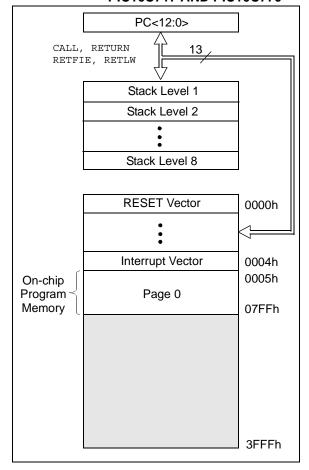

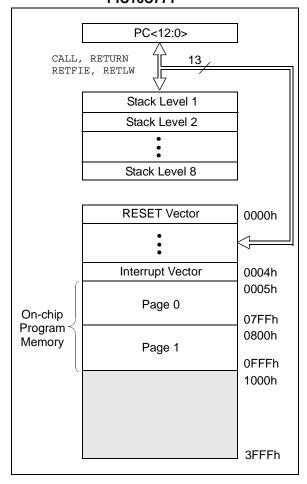

The PIC16C717/770/771 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16C717 and the PIC16C770 have 2K x 14 words of program memory. The PIC16C771 has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wrap-around.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK OF THE

PIC16C717 AND PIC16C770

FIGURE 2-2: PROGRAM MEMORY MAP AND STACK OF THE PIC16C771

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1     | RP0   | (STATUS<6:5>) |

|---------|-------|---------------|

| = 00 -  | Bank0 |               |

| = 01 -> | Bank1 |               |

| = 10 -> | Bank2 |               |

| = 11 →  | Bank3 |               |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some frequently used special function registers from one bank are mirrored in another bank for code reduction and quicker access.

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly, through the File Select Register FSR.

## 3.3 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

**EXAMPLE 3-2:** Initializing PORTB

|       |         |      | <u> </u>              |

|-------|---------|------|-----------------------|

| BCF   | STATUS, | RP0; |                       |

| CLRF  | PORTB   | ;    | Initialize PORTB by   |

|       |         | ;    | clearing output       |

|       |         | ;    | data latches          |

| BSF   | STATUS, | RP0; | Select Bank 1         |

| MOVLW | 0xCF    | ;    | Value used to         |

|       |         | ;    | initialize data       |

|       |         | ;    | direction             |

| MOVWF | TRISB   | ;    | Set RB<3:0> as inputs |

|       |         | ;    | RB<5:4> as outputs    |

|       |         | ;    | RB<7:6> as inputs     |

| MOVLW | 0x30    | ;    | Set RB<1:0> as analog |

|       |         |      | inputs                |

| MOVWF | ANSEL   | ;    |                       |

| BCF   | STATUS, | RP0; | Return to Bank 0      |

|       |         |      |                       |

Each of the PORTB pins has an internal pull-up, which can be individually enabled from the WPUB register. A single global enable bit can turn on/off the enabled pull-ups. Clearing the RBPU bit, (OPTION\_REG<7>), enables the weak pull-up resistors. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Each of the PORTB pins, if configured as input, also has an interrupt-on-change feature, which can be individually selected from the IOCB register. The RBIE bit in the INTCON register functions as a global enable bit to turn on/off the interrupt-on-change feature. The selected inputs are compared to the old value latched on the last read of PORTB. The "mismatch" outputs are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- a) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

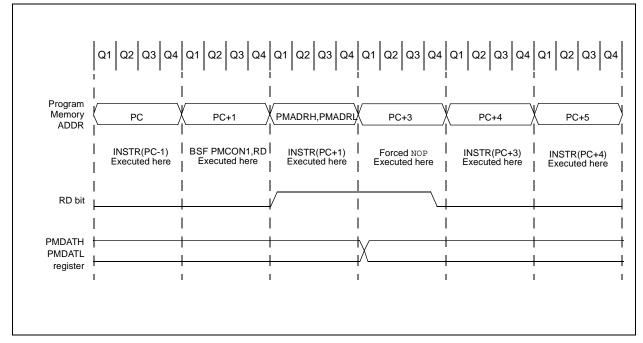

# 4.3 READING THE EPROM PROGRAM MEMORY

To read a program memory location, the user must write 2 bytes of the address to the PMADRH and PMADRL registers, then set control bit RD (PMCON1<0>). Once the read control bit is set, the Program Memory Read (PMR) controller will use the second instruction cycle after to read the data. This causes the second instruction immediately following

the "BSF PMCON1,RD" instruction to be ignored. The data is available, in the very next cycle, in the PMDATH and PMDATL registers; therefore it can be read as 2 bytes in the following instructions. PMDATH and PMDATL registers will hold this value until another Program Memory Read or until it is written to by the user.

**Note:** The two instructions that follow setting the PMCON1 read bit must be NOPs.

#### **EXAMPLE 4-1: OTP PROGRAM MEMORY Read**

```

BSF

STATUS, RP1

BCF

STATUS, RP0

; Bank 2

MS_PROG_PM_ADDR ;

MOVLW

PMADRH

MOVWF

; MS Byte of Program Memory Address to read

MOVLW

LS_PROG_PM_ADDR ;

MOVWF

PMADRL

; LS Byte of Program Memory Address to read

BSF

STATUS, RPO

; Bank 3

BSF

PMCON1, RD

; Program Memory Read

NOP

; This instruction must be an NOP

; This instruction must be an NOP

next instruction

; PMDATH: PMDATL now has the data

```

# 4.4 OPERATION DURING CODE PROTECT

When the device is code protected, the CPU can still perform the Program Memory Read function.

FIGURE 4-1: PROGRAM MEMORY READ CYCLE EXECUTION

# 8.3.4 OUTPUT POLARITY CONFIGURATION

The CCP1M<1:0> bits in the CCP1CON register allow user to choose the logic conventions (asserted high/low) for each of the outputs. See Register 8-1 for further details.

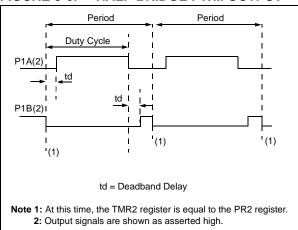

## FIGURE 8-6: HALF-BRIDGE PWM OUTPUT

The PWM output polarities must be selected before the PWM outputs are enabled. Charging the polarity configuration while the PWM outputs are active is not recommended, since it may result in unpredictable operation.

#### REGISTER 9-3: SYNC SERIAL PORT CONTROL REGISTER2 (SSPCON2: 91h)

| R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|---------|-------|-------|-------|-------|-------|-------|

| GCEN  | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit 7 |         |       |       |       |       |       | bit 0 |

- bit 7 **GCEN:** General Call Enable bit (In I<sup>2</sup>C Slave mode only)

- 1 = Enable interrupt when a general call address (0000h) is received in the SSPSR.

- 0 = General call address disabled.

- bit 6 **ACKSTAT:** Acknowledge Status bit (In I<sup>2</sup>C Master mode only)

#### In Master Transmit mode:

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

- bit 5 **ACKDT:** Acknowledge Data bit (In I<sup>2</sup>C Master mode only)

#### In Master Receive mode:

Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

- 1 = Not Acknowledge (NACK)

- $0 = Acknowledge (\overline{ACK})$

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (In I<sup>2</sup>C Master mode only).

#### In Master Receive mode:

- 1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Automatically cleared by hardware.

- 0 = Acknowledge sequence IDLE

- bit 3 **RCEN:** Receive Enable bit (In I<sup>2</sup>C Master mode only).

- 1 = Enables Receive mode for  $I^2C$

- 0 = Receive IDLE

- bit 2 **PEN:** STOP Condition Enable bit (In I<sup>2</sup>C Master mode only).

#### SCK Release Control

- ${\tt 1}$  = Initiate STOP condition on SDA and SCL pins. Automatically cleared by hardware.

- 0 = STOP condition IDLE

- bit 1 **RSEN:** Repeated START Condition Enabled bit (In I<sup>2</sup>C Master mode only)

- 1 = Initiate Repeated START condition on SDA and SCL pins. Automatically cleared by hardware.

- 0 = Repeated START condition IDLE

- bit 0 **SEN:** START Condition Enabled bit (In I<sup>2</sup>C Master mode only)

- 1 = Initiate START condition on SDA and SCL pins. Automatically cleared by hardware.

- 0 = START condition IDLE

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the IDLE mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 11-2: A/D CONTROL REGISTER 1 (ADCON1: 9Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-------|-------|-------|----------|----------|----------|----------|

| ADFM  | VCFG2 | VCFG1 | VCFG0 | Reserved | Reserved | Reserved | Reserved |

| bit 7 |       |       |       |          |          |          | bit 0    |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified0 = Left justified

bit 6-4 VCFG<2:0>: Voltage Reference Configuration bits

|     | A/D VREF+                       | A/D VREF-           |

|-----|---------------------------------|---------------------|

| 000 | AV <sub>DD</sub> <sup>(1)</sup> | AVss <sup>(2)</sup> |

| 001 | External VREF+                  | External VREF-      |

| 010 | Internal VRH                    | Internal VRL        |

| 011 | External VREF+                  | AVss <sup>(2)</sup> |

| 100 | Internal VRH                    | AVss <sup>(2)</sup> |

| 101 | AVDD <sup>(1)</sup>             | External VREF-      |

| 110 | AV <sub>DD</sub> <sup>(1)</sup> | Internal VRL        |

| 111 | Internal VRL                    | AVss                |

bit 3-0 **Reserved:** Do not use.

**Note 1:** This parameter is VDD for the PIC16C717.

2: This parameter is Vss for the PIC16C717.

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

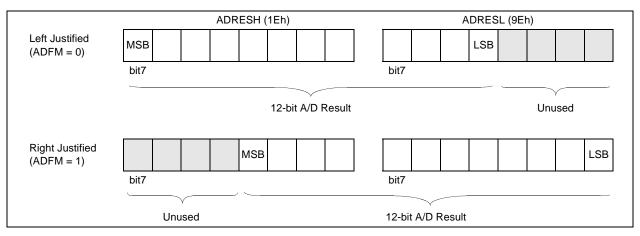

The A/D conversion results can be left justified (ADFM bit cleared), or right justified (ADFM bit set). Figure 11-1 through Figure 11-2 show the A/D result data format of the PIC16C717/770/771.

#### FIGURE 11-1: PIC16C770/771 12-BIT A/D RESULT FORMATS

# 11.3 Selecting the A/D Conversion Clock

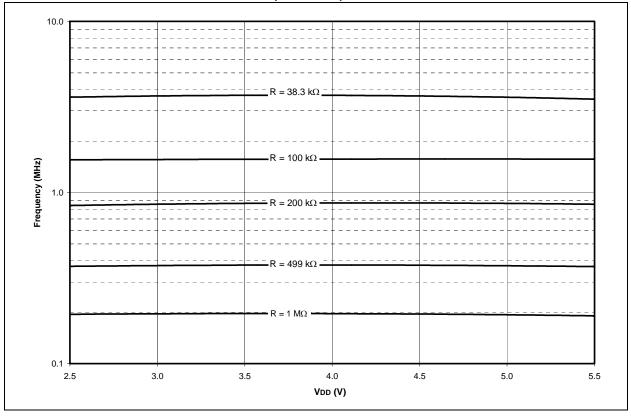

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. If neither the internal VRH nor VRL are used for the A/D converter, the four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- A/D RC oscillator

If the VRH or VRL are used for the A/D converter reference, then the TAD requirement is automatically increased by a factor of 8.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

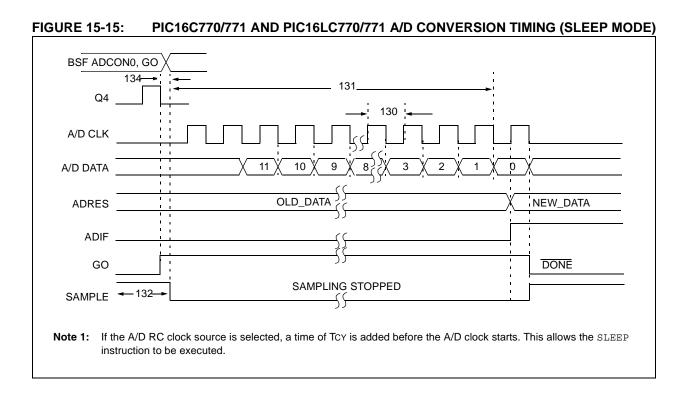

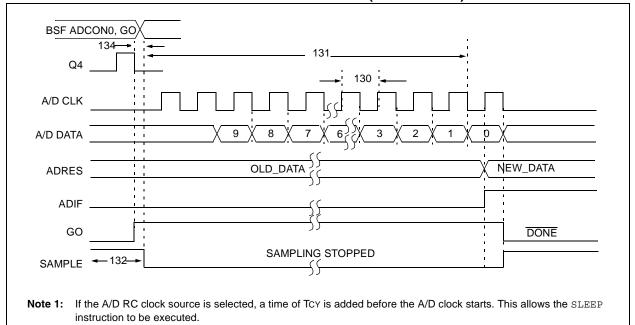

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

TABLE 11-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Reference<br>Source        | A/D Clock | Source (TAD) | Device Frequency            |                             |                             |                             |  |  |  |

|--------------------------------|-----------|--------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|

|                                | Operation | ADCS<1:0>    | 20 MHz                      | 5 MHz                       | 4 MHz                       | 1.25 MHz                    |  |  |  |

|                                | 2 Tosc    | 00           | 100 ns <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.6 μs                      |  |  |  |

| External VREF or Analog Supply | 8 Tosc    | 01           | 400 ns <sup>(2)</sup>       | 1.6 μs                      | 2.0 μs                      | 6.4 μs                      |  |  |  |

| Analog Supply                  | 32 Tosc   | 10           | 1.6 μs                      | 6.4 μs <sup>(3)</sup>       | 8.0 μs <sup>(3)</sup>       | 25.6 μs <sup>(3)</sup>      |  |  |  |

|                                | A/D RC    | 11           | 2 - 6 μs <sup>(1,4)</sup>   |  |  |  |

| Internal VRH or                | 16 Tosc   | 00           | 800 ns <sup>(2)</sup>       | 3.2 μs <sup>(2)</sup>       | 4 μs <sup>(2)</sup>         | 12.8 μs                     |  |  |  |

| VRL                            | 64 Tosc   | 01           | 3.2 μs <sup>(2)</sup>       | 12.8 μs                     | 16 μs                       | 51.2 μs <sup>(3)</sup>      |  |  |  |

|                                | 256 Tosc  | 10           | 12.8 μs                     | 51.2 μs <sup>(3)</sup>      | 64 μs <sup>(3)</sup>        | 204.8 μs <sup>(3)</sup>     |  |  |  |

|                                | A/D RC    | 11           | 16 - 48 μs <sup>(4,5)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during SLEEP.

- **5:** A/D RC clock source has a typical TAD time of 32  $\mu$ s for VDD > 3.0V.

## 11.5 A/D Converter Module Operation

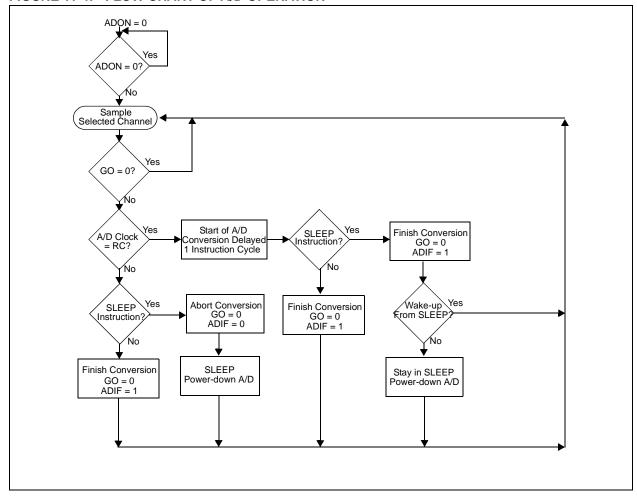

Figure 11-4 shows the flowchart of the A/D converter module.

FIGURE 11-4: FLOW CHART OF A/D OPERATION

TABLE 13-2: PIC16CXXX INSTRUCTION SET

| BYTE-ORIENTED FILE REGISTER OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mnemonic,                              |        | Description                  | Cycles |     | 14-Bit | Opcode | )    | Status   | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| ADDWF f, d Add W and f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Operands                               |        |                              |        | MSb |        |        | LSb  | Affected |       |

| ANDWF   f, d   Clear f   Clear f   Clear f   Clear f   Clear W   1   00   0001   leffe   feffe   Z   2   CLRW   - Clear W   1   00   0001   0000   0001   Z   COMF   f, d   Complement f   1   00   0001   deffe   feffe   Z   1,2   COMF   f, d   Complement f   1   00   0001   deffe   feffe   Z   1,2   COMF   f, d   Decrement f   1   00   0010   deffe   feffe   Z   1,2   DEGF   f, d   Increment f   1   00   0101   deffe   feffe   Z   1,2   DEGF   f, d   Increment f   1   00   0101   deffe   feffe   Z   1,2   Incres f   f, d   Increment f   f, d   Incr | BYTE-ORIENTED FILE REGISTER OPERATIONS |        |                              |        |     |        |        |      |          |       |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADDWF                                  |        | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff |          | ,     |

| COMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRF                                   | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| DECF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRW                                   | -      | Clear W                      | 1      | 00  | 0001   | 0000   | 0011 |          |       |

| DECFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | COMF                                   | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| INCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DECF                                   | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DECFSZ                                 | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| IORWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INCF                                   | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| MOVF         f, d         Move f         1         00         1000         defff         ffff         Z         1,2           MOVWF         f         Move W to f         1         00         1000         defff         ffff         Ffff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RLF         ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SWBWF         f, d         Subtract W from f         1         00         1100         dfff         fffff         C,DC,Z         1,2           SWAPF         f, d         Swap nybbles in f         1         00         1100         dfff         fffff         1,2           XORWF         f, d         Exclusive OR W with f         1         00         1100         dfff         fffff         Z         1,2           BSF         f, b         Bit Clear         1         01         00bb         bfff         ffff         1         1,2         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | INCFSZ                                 | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| MOVF         f, d         Move f         1         00         1000         defff         ffff         Z         1,2           MOVWF         f         Move W to f         1         00         1000         defff         ffff         Ffff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RLF         ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SWBWF         f, d         Subtract W from f         1         00         1100         dfff         fffff         C,DC,Z         1,2           SWAPF         f, d         Swap nybbles in f         1         00         1100         dfff         fffff         1,2           XORWF         f, d         Exclusive OR W with f         1         00         1100         dfff         fffff         Z         1,2           BSF         f, b         Bit Clear         1         01         00bb         bfff         ffff         1         1,2         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IORWF                                  | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| No Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MOVF                                   | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        |       |

| RLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MOVWF                                  | f      | Move W to f                  | 1      | 0.0 | 0000   | lfff   | ffff |          |       |

| RRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NOP                                    | -      | No Operation                 | 1      | 0.0 | 0000   | 0xx0   | 0000 |          |       |

| SUBWF   f, d   Subtract W from f   1   00   0010   dfff   fffff   C,DC,Z   1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RLF                                    | f, d   | Rotate Left f through Carry  | 1      | 0.0 | 1101   | dfff   | ffff | С        | 1,2   |

| SWAPF f, d XORWF f, d XORWF f, d Exclusive OR W with f         1 00 0110 dfff ffff ffff fff fff fff fff fff fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RRF                                    | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| Topic   Substract   Topic    | SUBWF                                  | f, d   | Subtract W from f            | 1      | 0.0 | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| BIT-ORIENTED FILE REGISTER OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SWAPF                                  | f, d   | Swap nybbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| BCF   f, b   Bit Clear f   1   01   00bb   bfff   ffff   1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XORWF                                  | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BIT-ORIENT                             | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BTFSC f, b BIT Test f, Skip if Clear BIT Test f, Skip if Set         1 (2) 01 10bb bfff ffff         3 3           LITERAL AND CONTROL OPERATIONS         1 (2) 01 11bb bfff ffff         3 3           ADDLW k AND literal and W AND literal with W CALL k Call subroutine         1 11 111x kkkk kkkk kkkk kkkk kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BCF                                    | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BTFSS   f, b   Bit Test f, Skip if Set   1 (2)   01   11bb   bfff   ffff   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BSF                                    | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| LITERAL AND CONTROL OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BTFSC                                  | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| ADDLW         k         Add literal and W         1         11         111x         kkkk         kkkk         C,DC,Z           ANDLW         k         AND literal with W         1         11         1001         kkkk         kkkk         Z           CALL         k         Call subroutine         2         10         0kkk         kkkk         kkkk         kkkk         CLRWDT         Clear Watchdog Timer         1         00         0000         0110         0100         TO,PD         TO,PD         GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk         kkkk         kkkk         Local Substance         Z         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         Return from interrupt         2         10         1000         0000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BTFSS                                  | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| ANDLW         k         AND literal with W         1         11         1001         kkkk         kkkk         Z           CALL         k         Call subroutine         2         10         0kkk         kkkk         kkkkk         kkkkk         kkkk         kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LITERAL AN                             | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| CALL         k         Call subroutine         2         10         0kkk         kkkk         kkkk         kkkk           CLRWDT         -         Clear Watchdog Timer         1         00         0000         0110         0100         TO,PD           GOTO         k         Go to address         2         10         1kkk         kkkk         kkkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDLW                                  | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| CLRWDT         -         Clear Watchdog Timer         1         00         0000         0110         0100         TO,PD           GOTO         k         Go to address         2         10         1kkk         kkkk         Return from interrupt         2         00         0000         0000         1001         TO,PD         Return from Subroutine         2         11         01xx         kkkk         kkkk         kkkk         Return from Subroutine         2         00         0000         0101         TO,PD         TO,PD         TO,PD         SUBLW         k         Subtract W from literal         1         11         110x         kkkk         kkkk         C,DC,Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ANDLW                                  | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |