Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc717-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C717/770/771

NOTES:

#### FIGURE 2-3: REGISTER FILE MAP

| A                              | File<br>ddress | A                                          | File<br>ddress |                                            | File<br>Address | Δ                     | File<br>ddress |

|--------------------------------|----------------|--------------------------------------------|----------------|--------------------------------------------|-----------------|-----------------------|----------------|

| Indirect addr.(*)              | 00h            | Indirect addr.(*)                          | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)     | 180h           |

| TMR0                           | 01h            | OPTION_REG                                 | 81h            | TMR0                                       | 101h            | OPTION REG            | 181h           |

| PCL                            | 02h            | PCL                                        | 82h            | PCL                                        | 102h            | PCL                   | 182h           |

| STATUS                         | 03h            | STATUS                                     | 83h            | STATUS                                     | 103h            | STATUS                | 183h           |

| FSR                            | 04h            | FSR                                        | 84h            | FSR                                        | 104h            | FSR                   | 184h           |

| PORTA                          | 05h            | TRISA                                      | 85h            |                                            | 105h            | - I OIL               | 185h           |

| PORTB                          | 06h            | TRISB                                      | 86h            | PORTB                                      | 106h            | TRISB                 | 186h           |

|                                | 07h            |                                            | 87h            |                                            | 107h            |                       | 187h           |

|                                | 08h            |                                            | 88h            |                                            | 108h            |                       | 188h           |

|                                | 09h            |                                            | 89h            |                                            | 109h            |                       | 189h           |

| PCLATH                         | 0Ah            | PCLATH                                     | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                | 18Ah           |

| INTCON                         | 0Bh            | INTCON                                     | 8Bh            | INTCON                                     | 10Bh            | INTCON                | 18Bh           |

| PIR1                           | 0Ch            | PIE1                                       | 8Ch            | PMDATL                                     | 10Ch            | PMCON1                | 18Ch           |

| PIR2                           | 0Dh            | PIE2                                       | 8Dh            | PMADRL                                     | 10Dh            |                       | 18Dh           |

| TMR1L                          | 0Eh            | PCON                                       | 8Eh            | PMDATH                                     | 10Eh            |                       | 18Eh           |

| TMR1H                          | 0Fh            |                                            | 8Fh            | PMADRH                                     | 10Fh            |                       | 18Fh           |

| T1CON                          | 10h            |                                            | 90h            |                                            | 110h            |                       | 190h           |

| TMR2                           | 11h            | SSPCON2                                    | 91h            |                                            | 111h            |                       | 191h           |

| T2CON                          | 12h            | PR2                                        | 92h            |                                            | 112h            |                       | 192h           |

| SSPBUF                         | 13h            | SSPADD                                     | 93h            |                                            | 113h            |                       | 193h           |

| SSPCON                         | 14h            | SSPSTAT                                    | 94h            |                                            | 114h            |                       | 194h           |

| CCPR1L                         | 15h            | WPUB                                       | 95h            |                                            | 115h            |                       | 195h           |

| CCPR1H                         | 16h            | IOCB                                       | 96h            |                                            | 116h            |                       | 196h           |

| CCP1CON                        | 17h            | P1DEL                                      | 97h            |                                            | 117h            |                       | 197h           |

|                                | 18h            |                                            | 98h            |                                            | 118h            |                       | 198h           |

|                                | 19h            |                                            | 99h            |                                            | 119h            |                       | 199h           |

|                                | 1Ah            |                                            | 9Ah            |                                            | 11Ah            |                       | 19Ah           |

|                                | 1Bh            | REFCON                                     | 9Bh            |                                            | 11Bh            |                       | 19Bh           |

|                                | 1Ch            | LVDCON                                     | 9Ch            |                                            | 11Ch            |                       | 19Ch           |

|                                | 1Dh            | ANSEL                                      | 9Dh            |                                            | 11Dh            |                       | 19Dh           |

| ADRESH                         | 1Eh            | ADRESL                                     | 9Eh            |                                            | 11Eh            |                       | 19Eh           |

| ADCON0                         | 1Fh            | ADCON1                                     | 9Fh            |                                            | 11Fh            |                       | 19Fh           |

|                                | 20h            |                                            | A0h            |                                            | 120h            |                       | 1A0h           |

| General<br>Purpose<br>Register |                | General<br>Purpose<br>Register<br>80 Bytes |                | General<br>Purpose<br>Register<br>80 Bytes |                 |                       |                |

| 96 Bytes                       |                |                                            | EFh            |                                            | 16Fh            |                       | 1EFh           |

| -                              |                | accesses<br>70h-7Fh                        | F0h            | accesses<br>70h - 7Fh                      | 170h            | accesses<br>70h - 7Fh | 1F0h           |

| Bank 0                         | 7Fh            | Bank 1                                     | FFh            | Bank 2                                     | 17Fh            | Bank 3                | 1FFh           |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

#### 2.2.2.8 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

The PCON register also contains the frequency select bit of the INTRC or ER oscillator.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

### REGISTER 2-8: POWER CONTROL REGISTER (PCON: 8Eh)

- n = Value at POR

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | —   | —   | OSCF  | _   | POR   | BOR   |

| bit 7 |     |     |     |       |     |       | bit 0 |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | OSCF: Oscillator Speed bit                                                                                                       |

|         | INTRC Mode                                                                                                                       |

|         | 1 = 4 MHz nominal                                                                                                                |

|         | 0 = 37 kHz nominal                                                                                                               |

|         | ER Mode                                                                                                                          |

|         | <ul> <li>1 = Oscillator frequency depends on the external resistor value on the OSC1 pin.</li> <li>0 = 37 kHz nominal</li> </ul> |

|         | All other modes                                                                                                                  |

|         | x = Ignored                                                                                                                      |

| bit 2   | Unimplemented: Read as '0'                                                                                                       |

| bit 1   | POR: Power-on Reset Status bit                                                                                                   |

|         | 1 = No Power-on Reset occurred                                                                                                   |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                            |

| bit 0   | BOR: Brown-out Reset Status bit (See Section 2.2.2.8 Note)                                                                       |

|         | 1 = No Brown-out Reset occurred                                                                                                  |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)                                          |

|         |                                                                                                                                  |

|         | Legend: q = Value depends on conditions                                                                                          |

|         | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                             |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

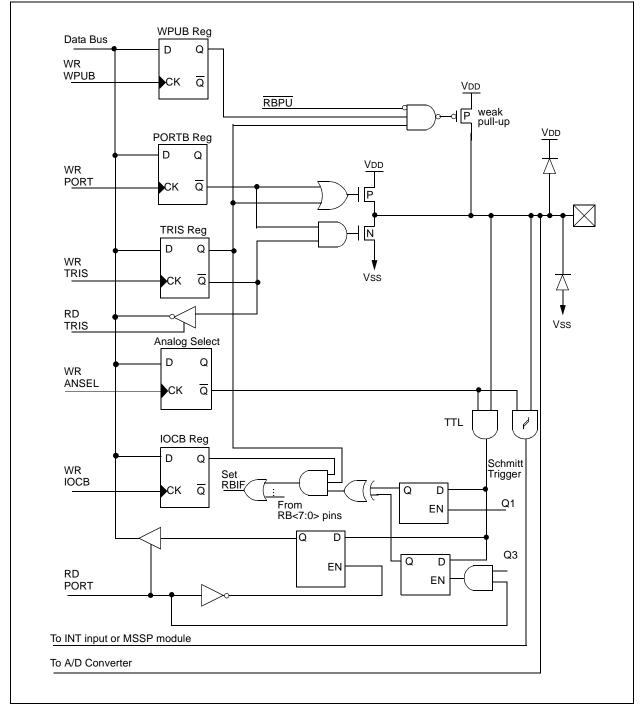

The RB0 pin is multiplexed with the A/D converter analog input 4 and the external interrupt input (RB0/AN4/ INT). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB0 pin as Analog mode. The RB1 pin is multiplexed with the A/D converter analog input 5 and the MSSP module slave select input (RB1/AN5/SS). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB1 pin as Analog mode.

Note: Upon RESET, the ANSEL register configures the RB1 and RB0 pins as analog inputs. Both RB1 and RB0 pins will read as '1'.

FIGURE 3-7: BLOCK DIAGRAM OF RB0/AN4/INT, RB1/AN5/SS PIN

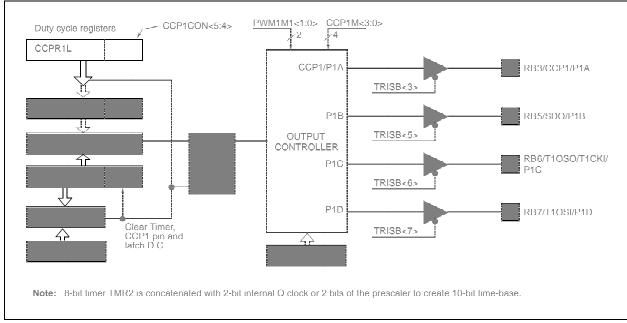

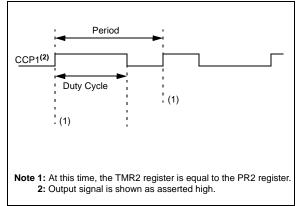

### 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the ECCP module produces up to a 10-bit resolution PWM output. Figure 8-3 shows the simplified PWM block diagram.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM PERIOD = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 PRESCALE VALUE)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 7.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

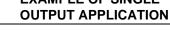

#### 8.3.3 PWM OUTPUT CONFIGURATIONS

The PWM1M1 bits in the CCP1CON register allows one of the following configurations:

- · Single output

- · Half-Bridge output

- Full-Bridge output, Forward mode

- Full-Bridge output, Reverse mode

In the Single Output mode, the RB3/CCP1/P1A pin is used as the PWM output. Since the CCP1 output is multiplexed with the PORTB<3> data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

#### FIGURE 8-4: SINGLE PWM OUTPUT

In the Half-Bridge Output mode, two pins are used as outputs. The RB3/CCP1/P1A pin has the PWM output signal, while the RB5/SDO/P1B pin has the complementary PWM output signal. This mode can be used for half-bridge applications, as shown on Figure 8-7, or for full-bridge applications, where four power switches are being modulated with two PWM signal.

Since the P1A and P1B outputs are multiplexed with the PORTB<3> and PORTB<5> data latches, the TRISB<3> and TRISB<5> bits must be cleared to configure P1A and P1B as outputs.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in bridge power devices. See Section 8.3.5 for more details of the deadband delay operations.

#### REGISTER 9-1: SYNC SERIAL PORT STATUS REGISTER (SSPSTAT: 94h)

| R/W-0                                | R/W-0                                     | R-0                        | R-0           | R-0              | R-0             | R-0              | R-0         |

|--------------------------------------|-------------------------------------------|----------------------------|---------------|------------------|-----------------|------------------|-------------|

| SMP                                  | CKE                                       | D/A                        | Р             | S                | R/W             | UA               | BF          |

| bit 7                                | •                                         |                            |               |                  |                 |                  | bit         |

| SMP: Sam                             | ple bit                                   |                            |               |                  |                 |                  |             |

| SPI Master                           |                                           |                            |               |                  |                 |                  |             |

|                                      | ata sampled a                             |                            |               |                  |                 |                  |             |

| 0 = Input d<br>SPI Slave             | ata sampled a                             | at middle of c             | ata output t  | me               |                 |                  |             |

|                                      | be cleared wi                             | hen SPI is us              | sed in Slave  | mode             |                 |                  |             |

|                                      | ter or Slave m                            |                            |               |                  |                 |                  |             |

|                                      | te control disa                           |                            |               |                  | KHz and 1 M     | Hz)              |             |

| 0= Slew ra                           | te control ena                            | bled for High              | n Speed moo   | le (400 kHz)     |                 |                  |             |

|                                      | Clock Edge S                              | elect (Figure              | 9-3, Figure   | 9-5, and Figu    | ıre 9-6)        |                  |             |

| <u>CKP = 0</u>                       |                                           |                            |               |                  |                 |                  |             |

|                                      | ansmitted on                              |                            |               |                  |                 |                  |             |

| 0 = Data tr<br><u>CKP = 1</u>        | ansmitted on                              | failing edge               | OF SCK        |                  |                 |                  |             |

|                                      | ansmitted on                              | falling edge               | of SCK        |                  |                 |                  |             |

|                                      | ansmitted on                              |                            |               |                  |                 |                  |             |

|                                      | Address bit (l2                           |                            |               |                  |                 |                  |             |

|                                      | es that the las                           |                            | • •           | nitted was da    | ta              |                  |             |

| 0 = Indicat                          | es that the las                           | st byte receiv             | ed or transn  | nitted was ad    | dress           |                  |             |

| P: STOP b                            | it                                        |                            |               |                  |                 |                  |             |

| (I <sup>2</sup> C mode               | only. This bit i                          | is cleared wh              | nen the MSS   | P module is      | disabled, SS    | PEN is cleare    | ed)         |

|                                      | es that a STO                             |                            | en detected   | last (this bit i | s '0' on RESI   | ET)              |             |

|                                      | bit was not de                            | etected last               |               |                  |                 |                  |             |

| S: START                             |                                           |                            |               | <b>_</b>         |                 |                  |             |

|                                      | only. This bit i<br>es that a STA         |                            |               |                  |                 |                  | ed)         |

|                                      | bit was not d                             |                            | en delected   | i last (this bit | IS U UII REC    | D⊏1)             |             |

|                                      | Write bit info                            |                            | mode only)    |                  |                 |                  |             |

|                                      | ds the R/W bi                             |                            |               | e last addres    | s match. This   | s bit is only va | alid from t |

|                                      | atch to the ne                            |                            |               |                  |                 |                  |             |

| <u>In I<sup>2</sup>C Slav</u>        |                                           |                            |               |                  |                 |                  |             |

| 1 = Read                             |                                           |                            |               |                  |                 |                  |             |

| 0 = Write<br>In I <sup>2</sup> C Mas | tor mode                                  |                            |               |                  |                 |                  |             |

|                                      | nit is in progre                          | 22                         |               |                  |                 |                  |             |

|                                      | nit is not in pro                         |                            |               |                  |                 |                  |             |

|                                      | bit with SEN,                             |                            | , RCEN, or a  | AKEN will inc    | licate if the N | ISSP is in ID    | LE mode     |

| UA: Updat                            | e Address (10                             | )-bit I <sup>2</sup> C mod | e only)       |                  |                 |                  |             |

| 1 = Indicate                         | es that the us                            | er needs to ι              | update the a  | ddress in the    | SSPADD re       | gister           |             |

| 0 = Addres                           | s does not ne                             | ed to be upo               | lated         |                  |                 |                  |             |

|                                      | Full Status bit                           |                            |               |                  |                 |                  |             |

|                                      | PI and I <sup>2</sup> C mo                |                            |               |                  |                 |                  |             |

|                                      | e complete, S                             |                            |               |                  |                 |                  |             |

|                                      | e not complet<br><sup>2</sup> C mode only |                            | is empty      |                  |                 |                  |             |

|                                      | ransmit in pro                            |                            | not include t | he ACK and       | STOP bits).     | SSPBUF is fu     | III         |

|                                      | ransmit compl                             |                            |               |                  |                 |                  |             |

| Locardi                              |                                           |                            |               |                  |                 |                  |             |

| Legend:                              | hla hit                                   | \\/ _ \\/                  | ritabla bit   |                  | nlamontad h     | it read as 'O'   |             |

| R = Reada                            |                                           | vv = vv                    | ritable bit   | 0 = 0.00         |                 | it, read as '0'  |             |

- n = Value at POR

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

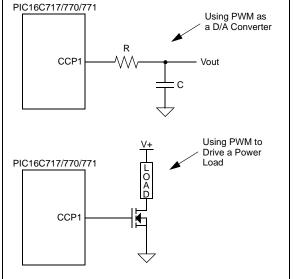

#### 9.2.11 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is set high while the  $I^2C$  module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG period. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG period while SCL is high. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. Following this, the baud rate generator is reloaded with the contents of SSPAD<6:0> and begins counting. When the BRG times out a third time, the RSEN bit in the SSPCON2 register is automatically cleared and SCL is pulled low. The SSPIF flag is set, which indicates the Restart sequence is complete.

- Note 1: If RSEN is set while another event is in progress, it will not take effect. Queuing of events is not allowed.

- 2: A bus collision during the Repeated START condition occurs if either of the following is true:

- a) SDA is sampled low when SCL goes from low to high.

- b) SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit transition to true, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then perform one of the following:

- Transmit an additional eight bits of address (if the user transmitted the first half of a 10-bit address with  $R/\overline{W} = 0$ ),

- Transmit eight bits of data (if the user transmitted a 7-bit address with R/W = 0), or

- Receive eight bits of data (if the user transmitted either the first half of a 10-bit address or a 7-bit address with R/W = 1).

#### 9.2.11.1 WCOL STATUS FLAG

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated START condition is complete.

#### FIGURE 9-17: REPEAT START CONDITION WAVEFORM

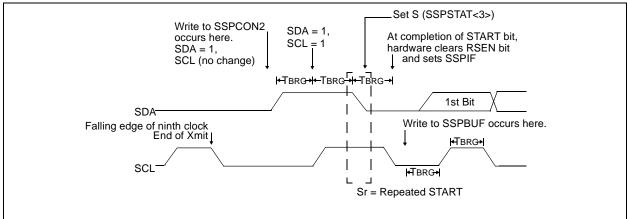

#### 9.2.16 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the

SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 9-22).

#### FIGURE 9-22: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

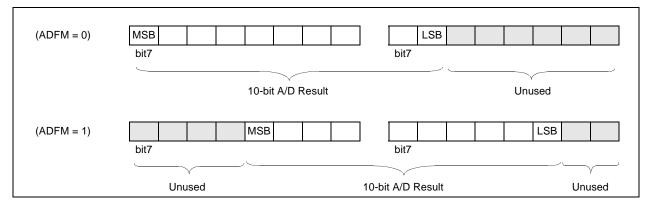

#### FIGURE 11-2: PIC16C717 10-BIT A/D RESULT FORMAT

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS and ANSEL bits selected as an input. To determine acquisition time, see Section 11.6. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

### 11.2 Configuring the A/D Module

#### 11.2.1 CONFIGURING ANALOG PORT PINS

The ANSEL and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted. The proper ANSEL bits must be set (analog input) to disable the digital input buffer.

The A/D operation is independent of the state of the TRIS bits and the ANSEL bits.

- Note 1: When reading the PORTA register, all pins configured as analog input channels will read as '0'.

- 2: When reading the PORTB register, all pins configured as analog pins on PORTB will be read as '1'.

- **3:** Analog levels on any pin that is defined as a digital input, including the ANx pins, may cause the input buffer to consume current that is out of the devices specification.

# 11.2.2 CONFIGURING THE REFERENCE VOLTAGES

The VCFG bits in the ADCON1 register configure the A/D module reference inputs. The reference high input can come from an internal reference (VRH) or (VRL), an external reference (VREF+), or AVDD. The low reference input can come from an internal reference (VRL), an external reference (VREF-), or AVss. If an external reference is chosen for the reference high or reference low inputs, the port pin that multiplexes the incoming external references is configured as an analog input, regardless of the values contained in the A/D port configuration bits (PCFG<3:0>).

| RETFIE           | Return from Interrupt  | RLF              | Rotate Left f through Carry                                                                                                                                                                                                       |

|------------------|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETFIE       | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                          |

| Operands:        | None                   | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                 |

| Operation:       | $TOS \rightarrow PC$ , |                  | d ∈ [0,1]                                                                                                                                                                                                                         |

|                  | $1 \rightarrow GIE$    | Operation:       | See description below                                                                                                                                                                                                             |

| Status Affected: | None                   | Status Affected: | С                                                                                                                                                                                                                                 |

|                  |                        | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the<br>result is placed in the W register.<br>If 'd' is 1, the result is stored back<br>in register 'f'.<br>-C Register f |

| RETLW                   | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                          |

| Operands:<br>Operation: | $0 \le k \le 255$<br>k $\rightarrow$ (W);                                                                                                                                           | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                   |

| Operation.              | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                                             |

| Status Affected:        | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                                                 |

| Description:            | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>Register f |

| RETURN           | Return from Subroutine                                                                                                                     | SLEEP            |                                                                                                                                                                                                                                    |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] RETURN                                                                                                                           | Syntax:          | [ label SLEEP                                                                                                                                                                                                                      |  |  |  |

| Operands:        | None                                                                                                                                       |                  | ]                                                                                                                                                                                                                                  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                       | Operands:        | None                                                                                                                                                                                                                               |  |  |  |

| Status Affected: | None                                                                                                                                       | Operation:       | $00h \rightarrow WDT$ ,                                                                                                                                                                                                            |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle | Status Affected: | $0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \\ \overline{TO}, \overline{PD}$                                                                                              |  |  |  |

|                  | instruction.                                                                                                                               | Description:     | The power-down status bit, $\overline{PD}$<br>is cleared. Time-out status bit,<br>$\overline{TO}$ is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |  |  |  |

See Section 12.8 for more

details.

# 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>TM</sup> 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

### 14.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 14.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 15.1 DC Characteristics: PIC16C717/770/771 (Commercial, Industrial, Extended) PIC16LC717/770/771 (Commercial, Industrial, Extended) (Continued)

|                   |     |                               |     |                                                      |             | ture (<br>-40 | ditions (unless otherwise stated)<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$0^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$0^{\circ}C \le TA \le +125^{\circ}C$ for extended |  |  |

|-------------------|-----|-------------------------------|-----|------------------------------------------------------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16C717/770/771 |     |                               |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |             |               |                                                                                                                                                                                                       |  |  |

| Param.<br>No.     | Sym | Characteristic                | Min | Тур†                                                 | Max         | Units         | Conditions                                                                                                                                                                                            |  |  |

|                   | Idd | Supply Current <sup>(2)</sup> |     |                                                      |             |               |                                                                                                                                                                                                       |  |  |

| D010D<br>D010E    |     | PIC16LC7XX                    |     | 1.0                                                  | 2.0<br>3.0  | mA            | Fosc = 10 MHz, VDD = 3V, -40°C to 85°C<br>Fosc = 10 MHz, VDD = 3V, -40°C to 125°C                                                                                                                     |  |  |

| D010G             |     |                               |     | 0.36                                                 | 1.0         | mA            | Fosc = 4 MHz, VDD = 2.5V, -40°C to 125°C                                                                                                                                                              |  |  |

| D010K             |     |                               |     | 11                                                   | 45          | μA            | Fosc = 32 kHz, VDD = 2.5V, -40°C to 125°C                                                                                                                                                             |  |  |

|                   | Idd | Supply Current <sup>(2)</sup> |     |                                                      |             |               |                                                                                                                                                                                                       |  |  |

| D010<br>D010A     |     | PIC16C7XX                     |     | 4.0                                                  | 7.5<br>12.0 | mA            | Fosc = 20 MHz, VDD = 5.5V, -40°C to 85°C<br>Fosc = 20 MHz, VDD = 5.5V, -40°C to 125°C                                                                                                                 |  |  |

| D010B<br>D010C    |     |                               |     | 2.5                                                  | 5.0<br>6.0  | mA            | Fosc = 20 MHz, VDD = 4V, -40°C to 85°C<br>Fosc = 20 MHz, VDD = 4V, -40°C to 125°C                                                                                                                     |  |  |

| D010F             |     |                               |     | 0.55                                                 | 1.5         | mA            | Fosc = 4 MHz, VDD = 4V, -40°C to 125°C                                                                                                                                                                |  |  |

| D010H<br>D010J    |     |                               |     | 30                                                   | 80<br>95    | μA            | Fosc = 32 kHz, VDD = 4V, -40°C to 85°C<br>Fosc = 32 kHz, VDD = 4V, -40°C to 125°C                                                                                                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

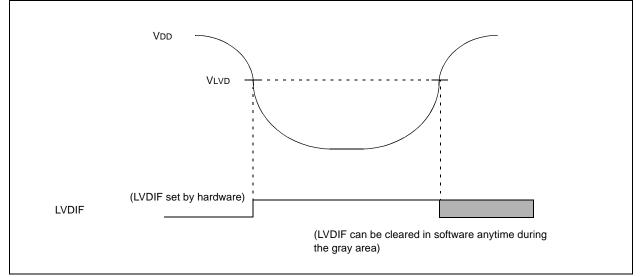

#### 15.4.2 LOW VOLTAGE DETECT MODULE (LVD)

| TABLE 15-8: | ELECTRICAL CHARACTERISTICS: LVD |

|-------------|---------------------------------|

|-------------|---------------------------------|

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC Characteristics Section 15.1. |             |            |        |     |      |      |       |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|--------|-----|------|------|-------|------------|

| Param. Characteristic No.                                                                                                                                                                                                                                                                   |             |            | Symbol | Min | Тур† | Max  | Units | Conditions |

| D420*                                                                                                                                                                                                                                                                                       | LVD Voltage | LVV = 0100 |        | 2.5 | 2.58 | 2.66 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 0101 |        | 2.7 | 2.78 | 2.86 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 0110 |        | 2.8 | 2.89 | 2.98 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 0111 |        | 3.0 | 3.1  | 3.2  | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1000 |        | 3.3 | 3.41 | 3.52 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1001 | Vlvd   | 3.5 | 3.61 | 3.72 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1010 |        | 3.6 | 3.72 | 3.84 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1011 |        | 3.8 | 3.92 | 4.04 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1100 |        | 4.0 | 4.13 | 4.26 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1101 | 1      | 4.2 | 4.33 | 4.46 | V     |            |

|                                                                                                                                                                                                                                                                                             |             | LVV = 1110 |        | 4.5 | 4.64 | 4.78 | V     |            |

These parameters are characterized but not tested.

**Note 1:** Production tested at Tamb = 25°C. Specifications over temperature limits ensured by characterization.

| Param.<br>No. | Sym   | Characteristic                                       | Min   | Тур†   | Max       | Units | Conditions                                                                                                                               |

|---------------|-------|------------------------------------------------------|-------|--------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| A01           | NR    | Resolution                                           | _     | _      | 10 bits   | bit   | Min. resolution for A/D is 4.1 mV,<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- $\leq$ VAIN $\leq$ VREF+                     |

| A03           | EIL   | Integral error                                       |       | _      | ±1        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A04           | EDL   | Differential error                                   | _     | _      | ±1        | LSb   | No missing codes to 10 bits<br>VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>$VREF- \le VAIN \le VREF+$                                |

| A06           | EOFF  | Offset error                                         |       | _      | ±2        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A07           | Egn   | Gain Error                                           | _     | _      | ±1        | LSb   | VREF+ = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                     |

| A10           |       | Monotonicity                                         | _     | Note 3 | —         |       | $AVSS \leq VAIN \leq VREF+$                                                                                                              |

| A20*          | Vref  | Reference voltage<br>(VREF+ - VREF-)                 | 4.096 | _      | VDD +0.3V | V     | Absolute minimum electrical spec to<br>ensure 10-bit accuracy.                                                                           |

| A21*          | VREF+ | Reference V High<br>(Avdd or VREF+)                  | VREF- | _      | AVdd      | V     | Min. resolution for A/D is 4.1 mV                                                                                                        |

| A22*          | VREF- | Reference V Low<br>(Avss or VREF-)                   | AVss  | _      | VREF+     | V     | Min. resolution for A/D is 4.1 mV                                                                                                        |

| A25*          | VAIN  | Analog input voltage                                 | VREFL | _      | VREFH     | V     |                                                                                                                                          |

| A30*          | Zain  | Recommended<br>impedance of analog<br>voltage source | _     | —      | 2.5       | kΩ    |                                                                                                                                          |

| A50*          | IREF  | VREF input current<br>(Note 2)                       | _     | _      | 10        | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN.<br>To charge CHOLD see Section 11.0.<br>During A/D conversion cycle. |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from External VREF+, or VREF-, or AVSS, or AVDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

t

# PIC16C717/770/771

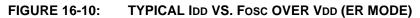

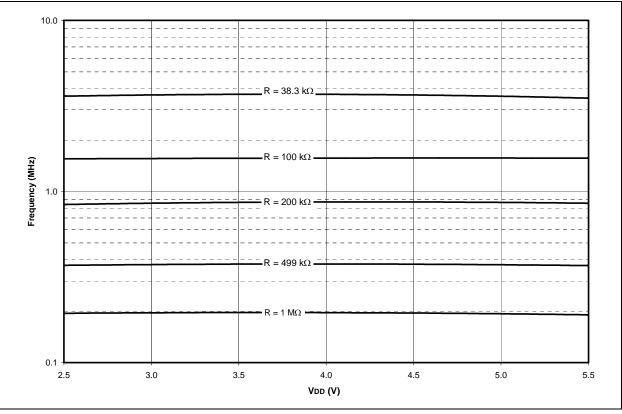

FIGURE 16-11: TYPICAL Fosc VS. VDD (ER MODE)

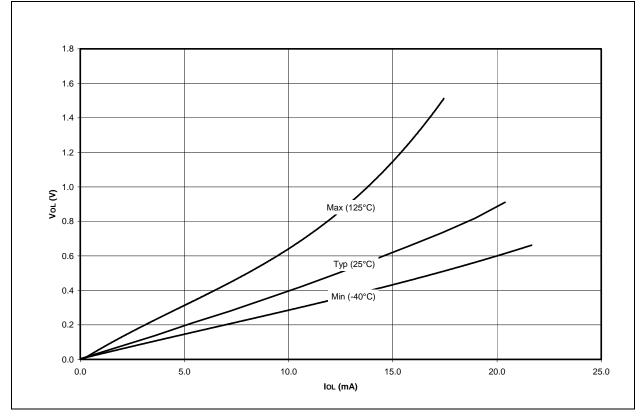

FIGURE 16-27: Vol VS. Iol (-40°C TO +125°C, VDD = 3.0V)

# PIC16C717/770/771

© 1999-2013 Microchip Technology Inc.

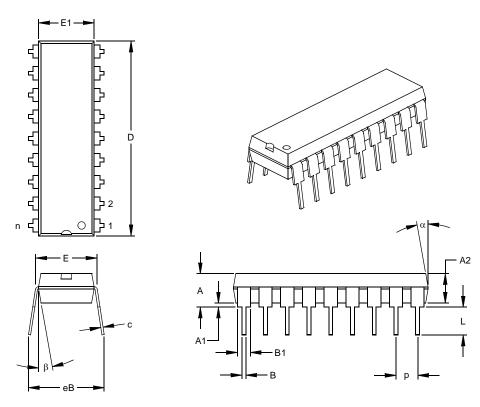

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP) 17.2

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

| Units     |                                                                                     | INCHES*                                                                                                                                                                                                                                                                                                                                               |                                                        | N                                                      | IILLIMETERS                                            |                                                        |

|-----------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| on Limits | MIN                                                                                 | NOM                                                                                                                                                                                                                                                                                                                                                   | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |

| n         |                                                                                     | 18                                                                                                                                                                                                                                                                                                                                                    |                                                        |                                                        | 18                                                     |                                                        |

| р         |                                                                                     | .100                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                        | 2.54                                                   |                                                        |

| А         | .140                                                                                | .155                                                                                                                                                                                                                                                                                                                                                  | .170                                                   | 3.56                                                   | 3.94                                                   | 4.32                                                   |

| A2        | .115                                                                                | .130                                                                                                                                                                                                                                                                                                                                                  | .145                                                   | 2.92                                                   | 3.30                                                   | 3.68                                                   |

| A1        | .015                                                                                |                                                                                                                                                                                                                                                                                                                                                       |                                                        | 0.38                                                   |                                                        |                                                        |

| E         | .300                                                                                | .313                                                                                                                                                                                                                                                                                                                                                  | .325                                                   | 7.62                                                   | 7.94                                                   | 8.26                                                   |

| E1        | .240                                                                                | .250                                                                                                                                                                                                                                                                                                                                                  | .260                                                   | 6.10                                                   | 6.35                                                   | 6.60                                                   |

| D         | .890                                                                                | .898                                                                                                                                                                                                                                                                                                                                                  | .905                                                   | 22.61                                                  | 22.80                                                  | 22.99                                                  |

| L         | .125                                                                                | .130                                                                                                                                                                                                                                                                                                                                                  | .135                                                   | 3.18                                                   | 3.30                                                   | 3.43                                                   |

| С         | .008                                                                                | .012                                                                                                                                                                                                                                                                                                                                                  | .015                                                   | 0.20                                                   | 0.29                                                   | 0.38                                                   |

| B1        | .045                                                                                | .058                                                                                                                                                                                                                                                                                                                                                  | .070                                                   | 1.14                                                   | 1.46                                                   | 1.78                                                   |

| В         | .014                                                                                | .018                                                                                                                                                                                                                                                                                                                                                  | .022                                                   | 0.36                                                   | 0.46                                                   | 0.56                                                   |

| eB        | .310                                                                                | .370                                                                                                                                                                                                                                                                                                                                                  | .430                                                   | 7.87                                                   | 9.40                                                   | 10.92                                                  |

| α         | 5                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                    | 15                                                     | 5                                                      | 10                                                     | 15                                                     |

| β         | 5                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                    | 15                                                     | 5                                                      | 10                                                     | 15                                                     |

|           | n Limits<br>n<br>P<br>A<br>A2<br>A1<br>E<br>E1<br>D<br>L<br>C<br>B1<br>B<br>eB<br>α | n         MIN           n            P            A         .140           A2         .115           A1         .015           E         .300           E1         .240           D         .890           L         .125           C         .008           B1         .045           B         .014           eB         .310           α         5 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Derwing No. CO4 007

Drawing No. C04-007

### INDEX

# Α

| A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 105                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|