Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 3.5KB (2K x 14)                                                        |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 18-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc717-p |

TABLE 1-1: PIC16C717/770/771 PINOUT DESCRIPTION (CONTINUED)

| Name                    | Function | Input<br>Type | Output<br>Type | Description                             |

|-------------------------|----------|---------------|----------------|-----------------------------------------|

|                         | RB6      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>       |

| DDC/T4.000/T4.01/J/D4.0 | T10S0    |               | XTAL           | Crystal/Resonator                       |

| RB6/T1OSO/T1CKI/P1C     | T1CKI    | CMOS          |                | TMR1 clock input                        |

|                         | P1C      |               | CMOS           | PWM P1C output                          |

|                         | RB7      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>       |

| RB7/T1OSI/P1D           | T1OSI    | XTAL          |                | TMR1 crystal/resonator                  |

|                         | P1D      |               | CMOS           | PWM P1D output                          |

| Vss                     | Vss      | Power         |                | Ground reference for logic and I/O pins |

| VDD                     | VDD      | Power         |                | Positive supply for logic and I/O pins  |

| AVss <sup>(2)</sup>     | AVss     | Power         |                | Ground reference for analog             |

| AVDD <sup>(2)</sup>     | AVDD     | Power         |                | Positive supply for analog              |

Note 1: Bit programmable pull-ups.

2: Only in PIC16C770/771 devices.

Data Latch Data Bus D WR Port **√**\_ Q CK TRIS Latch Ν Q WR T<u>RIS</u> ск ҇⊾ ҳ Vss Vss RD T<u>RIS</u> Schmitt Trigger Input Buffer Q D ΕN RD PORT TMR0 clock input

FIGURE 3-3: BLOCK DIAGRAM OF RA4/T0CKI

<u>Vdd</u> RBPU TMR1 Oscillator weak pull-up To RB6 WPUB Reg Data Bus D Q T1OSCEN WR WPUB Q CK D Q WR PORTB Q Data Latch D Q WR TRISB Ν Q CK **V**SS TRIS Latch RD TRISB T10SCEN Input RD PORTB Buffer **IOCB** Reg D WR IOCB Q Serial programming input Q D Schmitt Trigger Q1 **EK** Set RBIF Q D RB<7:0> pins RD Port EN< Q3 Note: The TMR1 oscillator enable (T1OSCEN = 1) overrides the RB7 I/O port and P1D functions.

FIGURE 3-10: BLOCK DIAGRAM OF THE RB7/T10SI/P1D

NOTES:

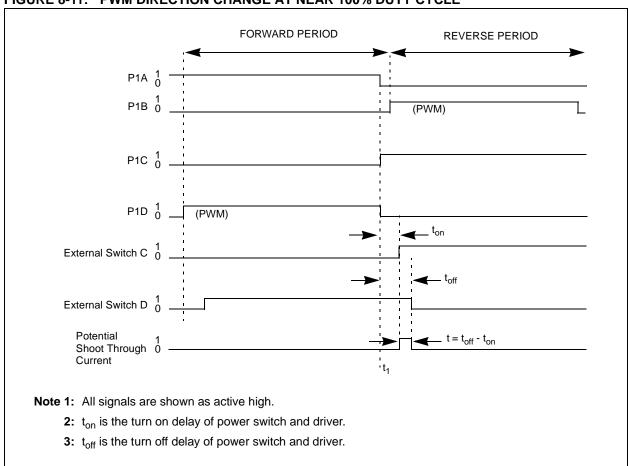

Note that in the Full-Bridge Output mode, the ECCP module does not provide any deadband delay. In general, since only one output is modulated at a time, deadband delay is not required. However, there is a situation where a deadband delay might be required. This situation occurs when all of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn off time of the power switch, including the power device and driver circuit, is greater than turn on time.

Figure 8-11 shows an example, where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the output P1A and P1D become inactive, while output P1C becomes active. In this

example, since the turn off time of the power devices is longer than the turn on time, a shoot-through current flows through the power devices, QB and QD, for the duration of t=  $t_{off}$ - $t_{on}$ . The same phenomenon will occur to power devices, QC and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for the user's application, one of the following requirements must be met:

- Avoid changing PWM output direction at or near 100% duty cycle.

- Use switch drivers that compensate for the slow turn off of the power devices. The total turn off time (t<sub>off</sub>) of the power device and the driver must be less than the turn on time (t<sub>on</sub>).

FIGURE 8-11: PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

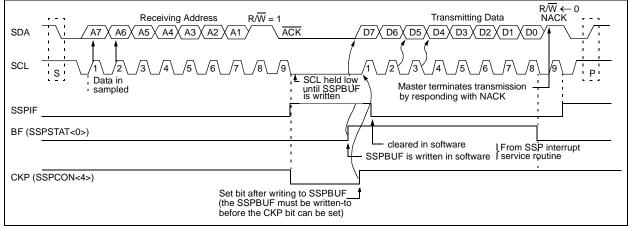

#### 9.2.2.4 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSP-STAT register is set. The received address is loaded into the SSPBUF register on the falling edge of the eighth SCL pulse. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The slave module automatically stretches the clock by holding the SCL line low so that the master will be unable to assert another clock pulse until the slave is finished preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. The CKP bit (SSPCON<4>) must then be set to release the SCL pin from the forced low condition. The eight data bits are shifted out on the falling edges of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-10).

The ACK or NACK signal from the master-receiver is latched on the rising edge of the ninth SCL input pulse. The master-receiver terminates slave transmission by

sending a NACK. If the SDA line is high (NACK), then the data transfer is complete. When the NACK is latched by the slave, the slave logic is RESET which also resets the  $R/\overline{W}$  bit to '0'. The slave module then monitors for another occurrence of the START bit. The slave firmware knows not to load another byte into the SSPBUF register by sensing that the buffer is empty (BF = 0) and the  $R/\overline{W}$  bit has gone low. If the SDA line is low (ACK), the  $R/\overline{W}$  bit remains high indicating that the next transmit data must be loaded into the SSPBUF register.

An MSSP interrupt (SSPIF flag) is generated for each data transfer byte on the falling edge of the ninth clock pulse. The SSPIF flag bit must be cleared in software. The SSPSTAT register is used to determine the status of the byte transfer.

For more information about the  $I^2C$  Slave mode, refer to Application Note AN734, "Using the PIC® SSP for Slave  $I^2C^{TM}$  Communication".

FIGURE 9-10: I<sup>2</sup>C SLAVE MODE WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

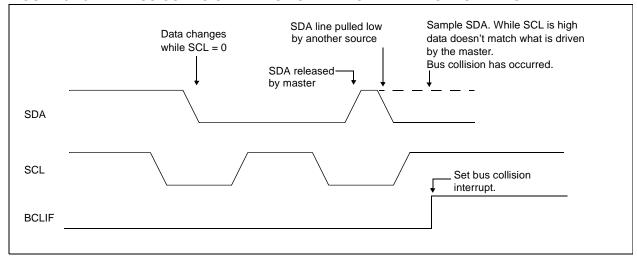

# 9.2.17 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, bus arbitration is initiated when one master outputs a '1' on SDA (by letting SDA float high) and another master asserts a '0'. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master that expected a '1' will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $\rm I^2C$  port to its IDLE state. (Figure 9-23).

A bus collision during transmit results in the following events:

- The transmission is halted.

- · The BF flag is cleared

- The SDA and SCL lines are de-asserted

- The restriction on writing to the SSPBUF during transmission is lifted.

When the user services the bus collision interrupt service routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

A bus collision during a START, Repeated START, STOP or Acknowledge condition results in the following events:

- The condition is aborted.

- The SDA and SCL lines are de-asserted.

- The respective control bits in the SSPCON2 register are cleared.

When the user services the bus collision interrupt service routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

The Master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

FIGURE 9-23: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

#### **12.3 RESET**

The PIC16C717/770/771 devices have several different RESETS. These RESETS are grouped into two classifications; power-up and non-power-up. The power-up type RESETS are the Power-on and Brownout Resets which assume the device VDD was below its normal operating range for the device's configuration. The non power-up type RESETS assume normal operating limits were maintained before/during and after the RESET.

- Power-on Reset (POR)

- Programmable Brown-out Reset (PBOR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

Some registers are not affected in any RESET condition. Their status is unknown on a Power-up Reset and unchanged in any other RESET. Most other registers are placed into an initialized state upon RESET, however they are not affected by a WDT Reset during SLEEP, because this is considered a WDT Wake-up, which is viewed as the resumption of normal operation.

Several status bits have been provided to indicate which RESET occurred (see Table 12-4). See Table 12-6 for a full description of RESET states of all registers.

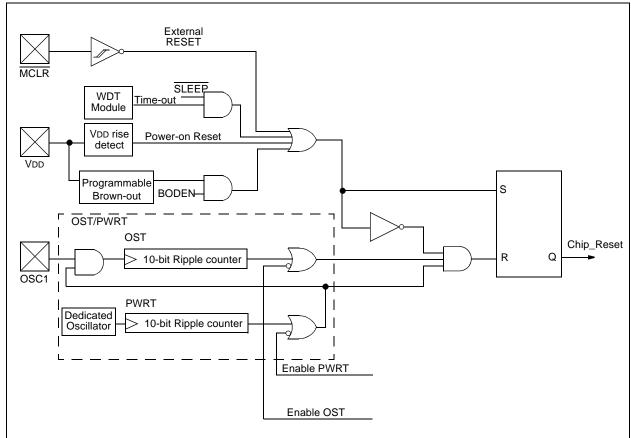

A simplified block diagram of the On-Chip Reset circuit is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

$\overline{\text{MCLR}}$  pin low.

FIGURE 12-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

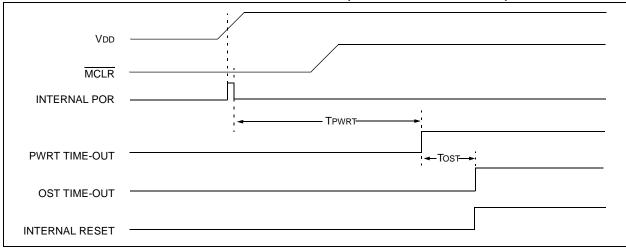

FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

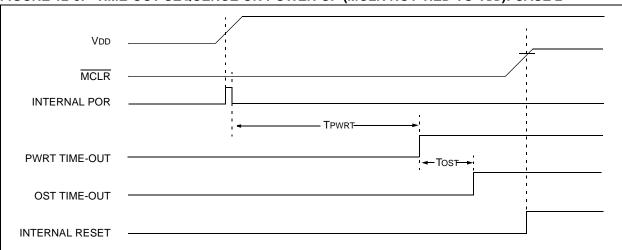

FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

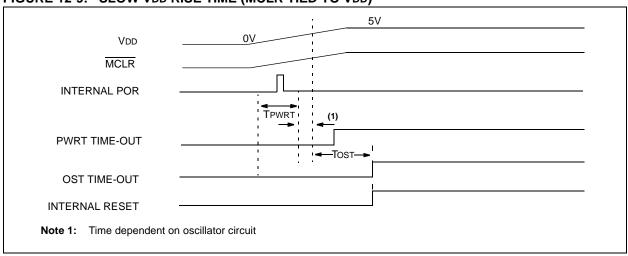

FIGURE 12-9: SLOW VDD RISE TIME (MCLR TIED TO VDD)

NOTES:

### 13.1 Instruction Descriptions

| Add Literal and W                                                                                                 | P                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [label] ADDLW k                                                                                                   | S                                                                                                                                                                            |

| $0 \leq k \leq 255$                                                                                               | C                                                                                                                                                                            |

| $(W) + k \rightarrow (W)$                                                                                         |                                                                                                                                                                              |

| C, DC, Z                                                                                                          | (                                                                                                                                                                            |

| The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. | 5                                                                                                                                                                            |

|                                                                                                                   | [label] ADDLW k $0 \le k \le 255$ (W) + k $\rightarrow$ (W) C, DC, Z The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W |

| ANDWF            | AND W with f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                 |

| Operation:       | $(W) + (f) \to (destination)$                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BCF              | Bit Clear f                         |

|------------------|-------------------------------------|

| Syntax:          | [label] BCF f,b                     |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |

| Operation:       | $0 \rightarrow (f < b >)$           |

| Status Affected: | None                                |

| Description:     | Bit 'b' in register 'f' is cleared. |

|                  |                                     |

| ANDLW            | AND Literal with W                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                               |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register. |

| BSF              | Bit Set f                                                              |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] BSF f,b                                                        |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                              |

| Status Affected: | None                                                                   |

| Description:     | Bit 'b' in register 'f' is set.                                        |

| IORLW            | Inclusive OR Literal with W                                                                                      | MOVLW            | Move Literal to W                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                                  | Syntax:          | [ label ] MOVLW k                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                     | Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | Z                                                                                                                | Status Affected: | None                                                                                       |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. | Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                     | MOVWF            | Move W to f                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                       | Syntax:          | [ label ] MOVWF f                 |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                       | Operands:        | $0 \leq f \leq 127$               |

|                  | d ∈ [0,1]                                                                                                                                                 | Operation:       | $(W) \to (f)$                     |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                  | Status Affected: | None                              |

| Status Affected: | Z                                                                                                                                                         | Description:     | Move data from W register to reg- |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. | ·                | ister 'f'.                        |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                               |

| Operation:       | $(f) \rightarrow (destination)$                                                                                                                                                                                                                                  |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register f are moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |

| No Operation  |

|---------------|

| [ label ] NOP |

| None          |

| No operation  |

| None          |

| No operation. |

|               |

|               |

|               |

|               |

TABLE 15-5: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param. | Sym       | Characteristic        |                                           |                             | Min                                | Typ† | Max   | Units | Conditions                         |  |

|--------|-----------|-----------------------|-------------------------------------------|-----------------------------|------------------------------------|------|-------|-------|------------------------------------|--|

| No.    |           |                       |                                           |                             |                                    |      |       |       |                                    |  |

| 40*    | Tt0H      |                       |                                           | No Prescaler                | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet parameter 42        |  |

|        |           |                       |                                           | With Prescaler              | 10                                 | _    | _     | ns    |                                    |  |

| 41*    | Tt0L      | T0CKI Low Pulse W     | dth                                       | No Prescaler                | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|        |           |                       |                                           | With Prescaler              | 10                                 | _    | _     | ns    | parameter 42                       |  |

| 42*    | Tt0P      | T0CKI Period          |                                           | No Prescaler                | Tcy + 40                           | _    | _     | ns    |                                    |  |

|        |           |                       |                                           |                             | Greater of:                        | _    | _     | ns    | N = prescale value                 |  |

|        |           |                       |                                           |                             | 20 or <u>Tcy + 40</u><br>N         |      |       |       | (2, 4,, 256)                       |  |

| 45*    | Tt1H      | T1CKI High Time       | Synchronous, F                            | Prescaler = 1               | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|        |           |                       | Synchronous,                              | PIC16 <b>C</b> 717/770/771  | 15                                 | _    | _     | ns    | parameter 47                       |  |

|        |           |                       | Prescaler = 2,4,8                         | PIC16 <b>LC</b> 717/770/771 | 25                                 | _    | _     | ns    |                                    |  |

|        |           |                       | ,                                         | PIC16 <b>C</b> 717/770/771  | 30                                 | _    | _     | ns    |                                    |  |

|        |           |                       |                                           | PIC16 <b>LC</b> 717/770/771 | 50                                 | _    | _     | ns    |                                    |  |

| 46*    | Tt1L      | T1CKI Low Time        | Synchronous, Prescaler = 1                |                             | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|        |           |                       | Synchronous,                              | PIC16 <b>C</b> 717/770/771  | 15                                 | _    | _     | ns    | parameter 47                       |  |

|        |           |                       | Prescaler = 2,4,8                         | PIC16 <b>LC</b> 717/770/771 | 25                                 | _    | _     | ns    |                                    |  |

|        |           |                       | Asynchronous                              | PIC16 <b>C</b> 717/770/771  | 30                                 | _    | _     | ns    |                                    |  |

|        |           |                       |                                           | PIC16 <b>LC</b> 717/770/771 | 50                                 | _    | _     | ns    |                                    |  |

| 47*    | Tt1P      | T1CKI input period    | Synchronous                               | PIC16 <b>C</b> 717/770/771  | Greater of: 30 OR TCY + 40 N       | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|        |           |                       |                                           | PIC16 <b>LC</b> 717/770/771 | Greater of:<br>50 OR TCY + 40<br>N | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|        |           |                       | Asynchronous                              | PIC16 <b>C</b> 717/770/771  | 60                                 | _    | _     | ns    |                                    |  |

|        |           |                       |                                           | PIC16 <b>LC</b> 717/770/771 | 100                                | _    | _     | ns    |                                    |  |

|        | Ft1       | Timer1 oscillator inp |                                           |                             | DC                                 | _    | 50    | kHz   |                                    |  |

|        |           | (oscillator enabled b | , ,                                       | ,                           | 2Tosc                              |      |       |       |                                    |  |

| 48     | Tcke2tmr1 | -                     | om external clock edge to timer increment |                             |                                    | _    | 7Tosc | _     |                                    |  |

These parameters are characterized but not tested.

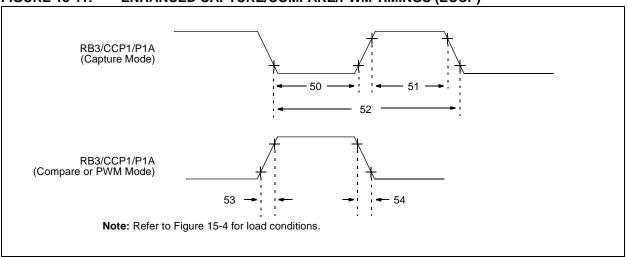

FIGURE 15-11: ENHANCED CAPTURE/COMPARE/PWM TIMINGS (ECCP)

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 15-6: ENHANCED CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Param.<br>No. | Sym  | Characteristic        |                | Min                         | Тур†           | Max | Units | Conditions |                                 |

|---------------|------|-----------------------|----------------|-----------------------------|----------------|-----|-------|------------|---------------------------------|

| 50*           | TccL | CCP1 input low        | No Prescaler   |                             | 0.5Tcy + 20    | _   |       | ns         |                                 |

|               |      | time                  | With Prescaler | PIC16 <b>C</b> 717/770/771  | 10             | _   | _     | ns         |                                 |

|               |      |                       |                | PIC16 <b>LC</b> 717/770/771 | 20             | _   | _     | ns         |                                 |

| 51*           | TccH | CCP1 input high time  | No Prescaler   |                             | 0.5Tcy + 20    | _   | _     | ns         |                                 |

|               |      |                       | With Prescaler | PIC16 <b>C</b> 717/770/771  | 10             | _   | _     | ns         |                                 |

|               |      |                       |                | PIC16 <b>LC</b> 717/770/771 | 20             | _   | _     | ns         |                                 |

| 52*           | TccP | CCP1 input period     |                |                             | 3Tcy + 40<br>N | _   | _     | ns         | N = prescale value (1, 4 or 16) |

| 53*           | TccR | CCP1 output fall time |                | PIC16 <b>C</b> 717/770/771  | _              | 10  | 25    | ns         |                                 |

|               |      |                       |                | PIC16 <b>LC</b> 717/770/771 | _              | 25  | 45    | ns         |                                 |

| 54*           | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 717/770/771  | _              | 10  | 25    | ns         |                                 |

|               |      |                       |                | PIC16 <b>LC</b> 717/770/771 | _              | 25  | 45    | ns         |                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 15.4 Analog Peripherals Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

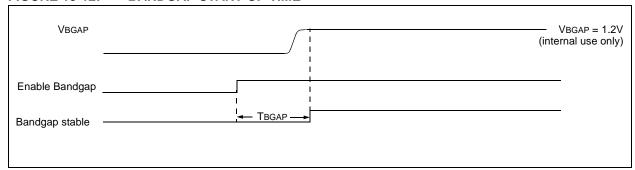

#### 15.4.1 BANDGAP MODULE

#### FIGURE 15-12: BANDGAP START-UP TIME

#### TABLE 15-7: BANDGAP START-UP TIME

| Param.<br>No. | Sym   | Characteristic        | Min | Тур† | Max | Units | Conditions                                                                                                                       |

|---------------|-------|-----------------------|-----|------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 36*           | TBGAP | Bandgap start-up time |     | 19   | 33  | μS    | Defined as the time between the instant that the bandgap is enabled and the moment that the bandgap reference voltage is stable. |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

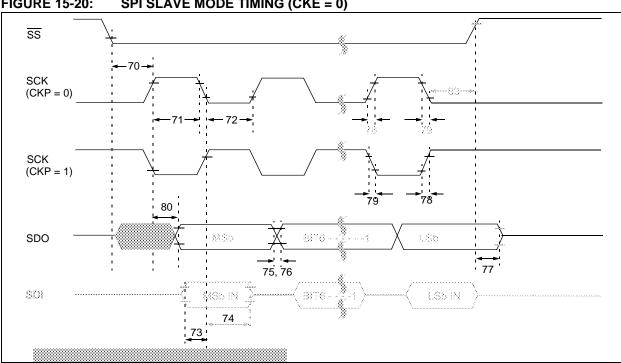

FIGURE 15-20: SPI SLAVE MODE TIMING (CKE = 0)

TABLE 15-19: SPI MODE REQUIREMENTS (SLAVE MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                           | Min                 | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|------------------------------------------|---------------------|--------------|-----|-------|------------|--------|

| 70*           | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy                 | _            | _   | ns    |            |        |

| 71*           | TscH                  | SCK input high time                      | Continuous          | 1.25Tcy + 30 | _   | _     | ns         |        |

| 71A*          |                       | (Slave mode)                             | Single Byte         | 40           | _   | _     | ns         | Note 1 |

| 72*           | TscL                  | SCK input low time                       | Continuous          | 1.25Tcy + 30 | _   | _     | ns         |        |

| 72A*          |                       | (Slave mode)                             | Single Byte         | 40           | _   | _     | ns         | Note 1 |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to          | 100                 | _            | _   | ns    |            |        |

| 73A*          | Тв2в                  | Last clock edge of Byte1 to the of Byte2 | 1.5Tcy + 40         | _            | _   | ns    | Note 1     |        |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input to           | 100                 | _            | _   | ns    |            |        |

| 75*           | TdoR                  | SDO data output rise time                | PIC16 <b>C</b> XXX  |              | 10  | 25    | ns         |        |

|               |                       |                                          | PIC16 <b>LC</b> XXX |              | 20  | 45    | ns         |        |

| 76*           | TdoF                  | SDO data output fall time                |                     |              | 10  | 25    | ns         |        |

| 77*           | TssH2doZ              | SS↑ to SDO output hi-impeda              | nce                 | 10           | _   | 50    | ns         |        |

| 78*           | TscR                  | SCK output rise time (Master             | PIC16 <b>C</b> XXX  |              | 10  | 25    | ns         |        |

|               |                       | mode)                                    | PIC16 <b>LC</b> XXX |              | 20  | 45    | ns         |        |

| 79*           | TscF                  | SCK output fall time (Master mode)       |                     | _            | 10  | 25    | ns         |        |

| 80*           | TscH2doV,             |                                          |                     |              | _   | 50    | ns         |        |

|               | TscL2doV SCK edge     |                                          | PIC16 <b>LC</b> XXX |              | _   | 100   | ns         |        |

| 83*           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                      |                     | 1.5Tcy + 40  | _   | _     | ns         |        |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Note 1: Specification 73A is only required if specifications 71A and 72A are used.

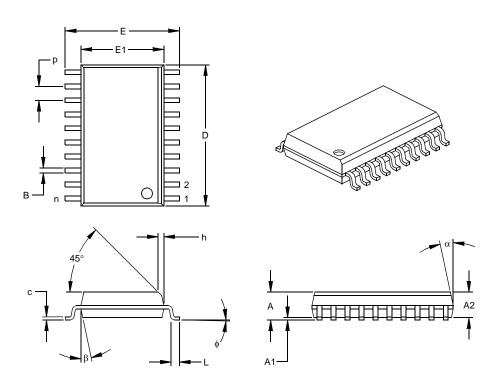

#### 20-Lead Plastic Small Outline (SO) - Wide, 300 mi (SOIC) 17.7

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |        | INCHES* |      | N    | ILLIMETERS | 3     |       |

|--------------------------|--------|---------|------|------|------------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX  | MIN        | NOM   | MAX   |

| Number of Pins           | n      |         | 20   |      |            | 20    |       |

| Pitch                    | р      |         | .050 |      |            | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104 | 2.36       | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094 | 2.24       | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012 | 0.10       | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420 | 10.01      | 10.34 | 10.67 |

| Molded Package Width     | E1     | .291    | .295 | .299 | 7.39       | 7.49  | 7.59  |

| Overall Length           | D      | .496    | .504 | .512 | 12.60      | 12.80 | 13.00 |

| Chamfer Distance         | h      | .010    | .020 | .029 | 0.25       | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050 | 0.41       | 0.84  | 1.27  |

| Foot Angle               | ф      | 0       | 4    | 8    | 0          | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .013 | 0.23       | 0.28  | 0.33  |

| Lead Width               | В      | .014    | .017 | .020 | 0.36       | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15   | 0          | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15   | 0          | 12    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-094

<sup>\*</sup> Controlling Parameter § Significant Characteristic

### **INDEX**

| A                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------|

| A/D                                                                                                                       |

| A/D Converter Enable (ADIE Bit)17                                                                                         |

| ADCON0 Register105                                                                                                        |

| ADCON1 Register105, 107                                                                                                   |

| ADRES Register105                                                                                                         |

| Block Diagram109                                                                                                          |

| Configuring Analog Port108                                                                                                |

| Conversion time115                                                                                                        |

|                                                                                                                           |

| Conversions                                                                                                               |

| converter characteristics 164, 165, 166, 170                                                                              |

| Faster Conversion - Lower Resolution Tradeoff 115                                                                         |

| Internal Sampling Switch (Rss) Impedence113                                                                               |

| Operation During Sleep116                                                                                                 |

| Sampling Requirements113                                                                                                  |

| Sampling Time113                                                                                                          |

| Source Impedance113                                                                                                       |

| Special Event Trigger (ECCP)55                                                                                            |

| A/D Conversion Clock                                                                                                      |

| ACK77                                                                                                                     |

| Acknowledge Data bit, AKD69                                                                                               |

| Acknowledge Sequence Enable bit, AKE                                                                                      |

| Acknowledge Status bit, AKS                                                                                               |

|                                                                                                                           |

| ACKSTAT                                                                                                                   |

| ADCON0 Register                                                                                                           |

| ADCON1 Register                                                                                                           |

| ADRES105                                                                                                                  |

| ADRES Register 11, 12, 105, 116                                                                                           |

| AKD69                                                                                                                     |

| AKE69                                                                                                                     |

|                                                                                                                           |

| AKS69                                                                                                                     |

| AKS                                                                                                                       |

| Analog-to-Digital Converter. See A/D                                                                                      |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module                                       |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| Analog-to-Digital Converter. See A/D Application Note AN578, "Use of the SSP Module in the I2C Multi-Master Environment." |

| C                                                   |          |

|-----------------------------------------------------|----------|

| Capture (ECCP Module)                               | 54       |

| Block Diagram                                       |          |

| CCPR1H:CCPR1L Registers                             | 54       |

| Changing Between Capture Prescalers                 |          |

| ECCP Pin Configuration                              |          |

| Software Interrupt                                  |          |

| Timer1 Mode Selection                               | 54       |

| Capture/Compare/PWM (ECCP)                          |          |

| Capture Mode. See Capture Compare Mode. See Compare |          |

| PWM Mode. See PWM                                   |          |

| CCP1CON                                             | 13       |

| CCP2CON                                             |          |

| CCPR1H Register                                     |          |

| CCPR1L Register                                     |          |

| CCPR2H Register                                     |          |

| CCPR2L Register                                     |          |

| CKE                                                 | 66       |

| CKP                                                 |          |

| Clock Polarity Select bit, CKP                      | 67       |

| Code Examples                                       |          |

| Loading the SSPBUF register                         | 71       |

| Code Protection                                     |          |

| Compare (ECCP Module)                               |          |

| Block Diagram                                       |          |

| CCPR1H:CCPR1L Registers ECCP Pin Configuration      |          |

|                                                     |          |

| Software Interrupt Special Event Trigger            |          |

| Timer1 Mode Selection                               |          |

| Configuration Bits                                  |          |

| D                                                   |          |

| _                                                   |          |

| D/A                                                 |          |

| Data Memory                                         |          |

| Bank Select (RP Bits)                               |          |

| General Purpose Registers                           |          |

| Register File Map Special Function Registers        |          |

| Data/Address bit, D/A                               |          |

| DC Characteristics                                  |          |

| PIC16C717/770/771 150,                              | 151, 153 |

| Development Support                                 |          |

| Device Differences                                  |          |

| Direct Addressing                                   |          |

| E                                                   |          |

| Enhanced Capture/Compare/PWM (ECCP)                 |          |

| CCP1                                                |          |

| CCPR1H Register                                     | 53       |

| CCPR1L Register                                     |          |

| Enable (CCP1IE Bit)                                 |          |

| Timer Resources                                     |          |

| Errata                                              |          |

| External Power-on Reset Circuit                     | 122      |

| F                                                   |          |

| Firmware Instructions                               | 133      |

| FSR Register1                                       |          |

|                                                     | .,, .    |

| G                                                   |          |

| GCE                                                 |          |

| General Call Address Sequence                       |          |

| General Call Address Support                        |          |

| General Call Enable bit, GCE                        | 69       |

| TMR2 to PR2 Match Enable (TMR2IE Bit)17               | PICDEM 3 Low Cost PIC16CXXX                  |

|-------------------------------------------------------|----------------------------------------------|

| USART Receive Enable (RCIE Bit)17, 18                 | Demonstration Board144                       |

| Interrupts, Flag Bits                                 | PICSTART Plus Entry Level                    |

| CCP1 Flag (CCP1IF Bit)54                              | Development Programmer                       |

| Interrupt on Change (RB7:RB4) Flag                    | PIE1 Register 17                             |

| (RBIF Bit)16, 33, 128                                 | ADIE Bit                                     |

| RB0/INT Flag (INTF Bit)16                             | CCP1IE Bit 17                                |

| TMR0 Overflow Flag (T0IF Bit)16, 128                  | PSPIE Bit17                                  |

| INTRC Mode120                                         | RCIE Bit 17, 18                              |

| K                                                     | SSPIE Bit17                                  |

| KEELOQ Evaluation and Programming Tools144            | TMR1IE Bit 17                                |

|                                                       | TMR2IE Bit 17                                |

| L                                                     | PIE2 Register19                              |

| LVDCON 101                                            | Pinout Descriptions                          |

| M                                                     | PIC16C770 7                                  |

| Master Clear (MCLR)                                   | PIC16C770/7717                               |

|                                                       | PIC16C771 7                                  |

| MCLR Reset, Normal Operation                          | PIR1 Register18                              |

| MCLR Reset, SLEEP121, 123, 124                        | PIR2 Register                                |

| Memory Organization                                   | Pointer, FSR                                 |

| Data Memory9                                          | POR. See Power-on Reset                      |

| Program Memory9                                       | PORTA                                        |

| MPLAB C17 and MPLAB C18 C Compilers141                | Initialization                               |

| MPLAB ICD In-Circuit Debugger143                      | PORTA Register25                             |

| MPLAB ICE High Performance Universal In-Circuit       | TRISA Register25                             |

| Emulator with MPLAB IDE142                            | PORTA Register                               |

| MPLAB Integrated Development Environment Software 141 | PORTB                                        |

| MPLINK Object Linker/MPLIB Object Librarian142        | Initialization33                             |

| Multi-Master Communication94                          | PORTB Register                               |

| Multi-Master Mode84                                   | Pull-up Enable (RBPU Bit)                    |

| 0                                                     | RB0/INT Edge Select (INTEDG Bit)             |

| OPCODE Field Descriptions133                          | RB0/INT Pin, External                        |

| OPTION_REG Register                                   | RB7:RB4 Interrupt on Change                  |

| INTEDG Bit                                            | RB7:RB4 Interrupt on Change Enable           |

| PS Bits                                               | (RBIE Bit)                                   |

| PSA Bit                                               | ,                                            |

|                                                       | RB7:RB4 Interrupt on Change Flag             |

| RBPU Bit                                              | (RBIF Bit)                                   |

| TOCS Bit                                              | TRISB Register                               |

| TOSE Bit                                              | PORTB Register                               |

| Oscillator Configuration                              | Postscaler, Timer2                           |

| CLKOUT120                                             | Select (TOUTPS Bits)                         |

| Dual Speed Operation for ER and                       | Postscaler, WDT45                            |

| INTRC Modes                                           | Assignment (PSA Bit)                         |

| EC119, 123                                            | Block Diagram                                |

| ER119, 123                                            | Rate Select (PS Bits)                        |

| ER Mode120                                            | Switching Between Timer0 and WDT 46          |

| HS119, 123                                            | Power-down Mode. See SLEEP                   |

| INTRC 119, 123                                        | Power-on Reset (POR) 117, 121, 122, 123, 124 |

| LP119, 123                                            | Oscillator Start-up Timer (OST) 117, 122     |

| XT119, 123                                            | Power Control (PCON) Register123             |

| Oscillator, Timer1 47, 49                             | Power-down (PD Bit)14                        |

| Oscillator, WDT129                                    | Power-on Reset Circuit, External             |

| P                                                     | Power-up Timer (PWRT)117, 122                |

|                                                       | Time-out (TO Bit)14                          |

| P                                                     | Time-out Sequence                            |

| Packaging197                                          | Time-out Sequence on Power-up 125, 126       |

| Paging, Program Memory                                | PR2 Register                                 |

| Parallel Slave Port (PSP)                             | Prescaler, Capture54                         |

| Read/Write Enable (PSPIE Bit)                         | Prescaler, Timer0                            |

| PCL Register                                          | Assignment (PSA Bit)                         |

| PCLATH Register 11, 12, 13                            | Block Diagram                                |

| PCON Register 21, 123                                 | Rate Select (PS Bits)                        |

| PICDEM 1 Low Cost PIC MCU                             | Switching Between Timer0 and WDT46           |

| Demonstration Board143                                | Prescaler, Timer1                            |

| PICDEM 17 Demonstration Board144                      | Select (T1CKPS Bits)                         |

| PICDEM 2 Low Cost PIC16CXX                            | Gelect (1 10tt G Dita)47                     |

| Demonstration Board 143                               |                                              |