Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc770-e-so |

#### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the SSP bus collision and low voltage detect interrupts.

### REGISTER 2-6: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (PIE2: 8Dh)

| R/W-0 | U-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-------|-----|-----|-------|

| LVDIE | _   | _   | _   | BCLIE |     |     | _     |

| bit 7 |     |     |     |       |     |     | bit 0 |

bit 7 LVDIE: Low Voltage Detect Interrupt Enable bit

1 = LVD Interrupt is enabled

0 = LVD Interrupt is disabled

bit 6-4 **Unimplemented:** Read as '0'

bit 3 BCLIE: Bus Collision Interrupt Enable bit

1 = Bus Collision interrupt is enabled0 = Bus Collision interrupt is disabled

bit 2-0 Unimplemented: Read as '0'

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

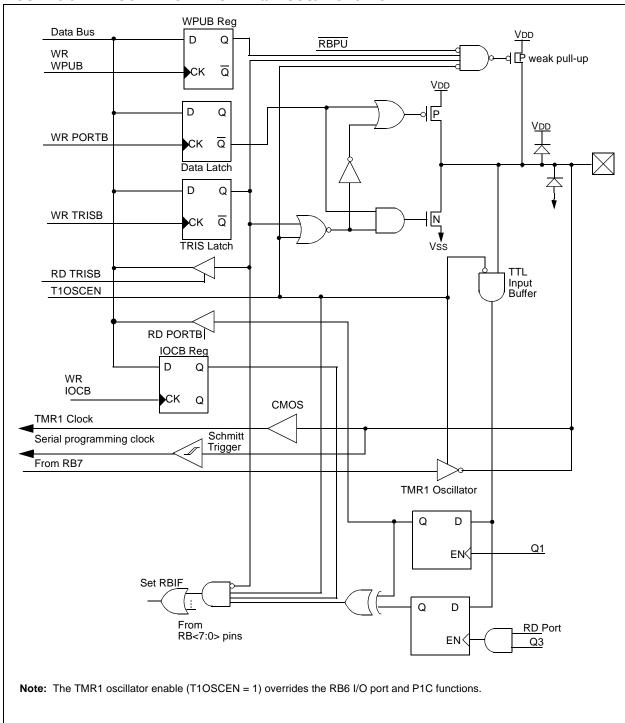

FIGURE 3-9: BLOCK DIAGRAM OF RB6/T10S0/T1CKI/P1C

<u>Vdd</u> RBPU TMR1 Oscillator weak pull-up To RB6 WPUB Reg Data Bus D Q T1OSCEN WR WPUB Q CK D Q WR PORTB Q Data Latch D Q WR TRISB Ν Q CK **V**SS TRIS Latch RD TRISB T10SCEN Input RD PORTB Buffer **IOCB** Reg D WR IOCB Q Serial programming input Q D Schmitt Trigger Q1 **EK** Set RBIF Q D RB<7:0> pins RD Port EN< Q3 Note: The TMR1 oscillator enable (T1OSCEN = 1) overrides the RB7 I/O port and P1D functions.

FIGURE 3-10: BLOCK DIAGRAM OF THE RB7/T10SI/P1D

TABLE 4-1: PROGRAM MEMORY READ REGISTER SUMMARY

| Address | Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|----------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 18Ch    | PMCON1 | Reserved | _     | _     | _     | _     | _     | _     | RD    | 10                       | 10                              |

| 10Eh    | PMDATH | _        | _     | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  | xx xxxx                  | uu uuuu                         |

| 10Ch    | PMDATL | PMD7     | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH |          |       | _     |       | PMA11 | PMA10 | PMA9  | PMA8  | xxxx                     | uuuu                            |

| 10Dh    | PMADRL | PMA7     | PMA6  | PMA5  | PMA4  | РМАЗ  | PMA2  | PMA1  | PMA0  | xxxx xxxx                | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Program Memory Read.

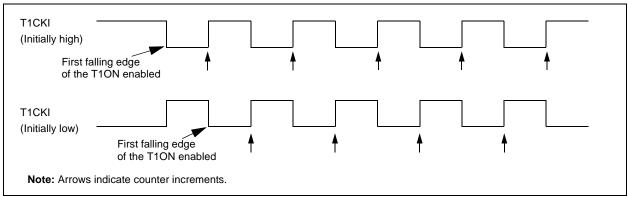

### 6.1.1 TIMER1 COUNTER OPERATION

In this mode, Timer1 is being incremented via an external source. Increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

### FIGURE 6-1: TIMER1 INCREMENTING EDGE

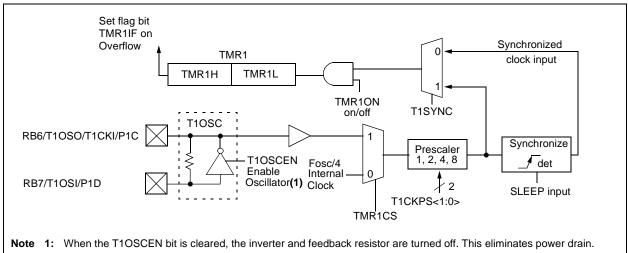

### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

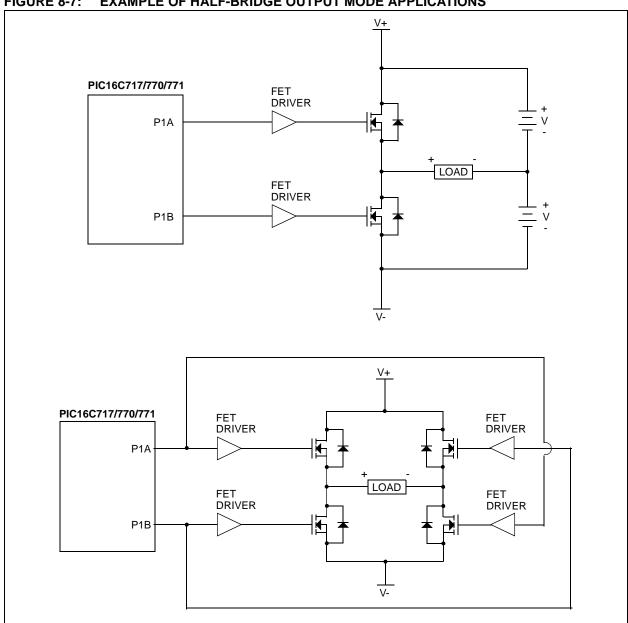

FIGURE 8-7: EXAMPLE OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

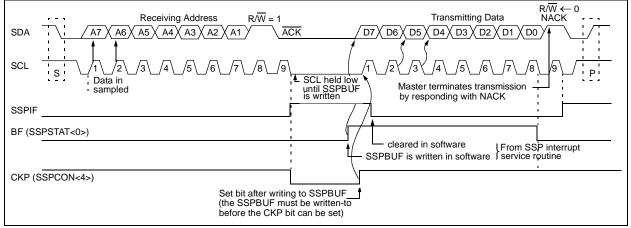

#### 9.2.2.4 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSP-STAT register is set. The received address is loaded into the SSPBUF register on the falling edge of the eighth SCL pulse. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The slave module automatically stretches the clock by holding the SCL line low so that the master will be unable to assert another clock pulse until the slave is finished preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. The CKP bit (SSPCON<4>) must then be set to release the SCL pin from the forced low condition. The eight data bits are shifted out on the falling edges of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-10).

The ACK or NACK signal from the master-receiver is latched on the rising edge of the ninth SCL input pulse. The master-receiver terminates slave transmission by

sending a NACK. If the SDA line is high (NACK), then the data transfer is complete. When the NACK is latched by the slave, the slave logic is RESET which also resets the  $R/\overline{W}$  bit to '0'. The slave module then monitors for another occurrence of the START bit. The slave firmware knows not to load another byte into the SSPBUF register by sensing that the buffer is empty (BF = 0) and the  $R/\overline{W}$  bit has gone low. If the SDA line is low (ACK), the  $R/\overline{W}$  bit remains high indicating that the next transmit data must be loaded into the SSPBUF register.

An MSSP interrupt (SSPIF flag) is generated for each data transfer byte on the falling edge of the ninth clock pulse. The SSPIF flag bit must be cleared in software. The SSPSTAT register is used to determine the status of the byte transfer.

For more information about the  $I^2C$  Slave mode, refer to Application Note AN734, "Using the PIC® SSP for Slave  $I^2C^{TM}$  Communication".

FIGURE 9-10: I<sup>2</sup>C SLAVE MODE WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

### REGISTER 11-2: A/D CONTROL REGISTER 1 (ADCON1: 9Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-------|-------|-------|----------|----------|----------|----------|

| ADFM  | VCFG2 | VCFG1 | VCFG0 | Reserved | Reserved | Reserved | Reserved |

| bit 7 |       |       |       |          |          |          | bit 0    |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified0 = Left justified

bit 6-4 VCFG<2:0>: Voltage Reference Configuration bits

|     | A/D VREF+                       | A/D VREF-           |

|-----|---------------------------------|---------------------|

| 000 | AV <sub>DD</sub> <sup>(1)</sup> | AVss <sup>(2)</sup> |

| 001 | External VREF+                  | External VREF-      |

| 010 | Internal VRH                    | Internal VRL        |

| 011 | External VREF+                  | AVss <sup>(2)</sup> |

| 100 | Internal VRH                    | AVss <sup>(2)</sup> |

| 101 | AVDD <sup>(1)</sup>             | External VREF-      |

| 110 | AV <sub>DD</sub> <sup>(1)</sup> | Internal VRL        |

| 111 | Internal VRL                    | AVss                |

bit 3-0 **Reserved:** Do not use.

**Note 1:** This parameter is VDD for the PIC16C717.

2: This parameter is Vss for the PIC16C717.

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

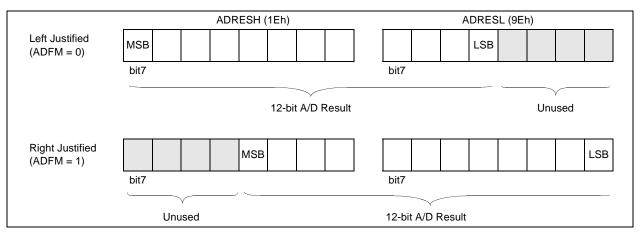

The A/D conversion results can be left justified (ADFM bit cleared), or right justified (ADFM bit set). Figure 11-1 through Figure 11-2 show the A/D result data format of the PIC16C717/770/771.

#### FIGURE 11-1: PIC16C770/771 12-BIT A/D RESULT FORMATS

### 13.0 INSTRUCTION SET SUMMARY

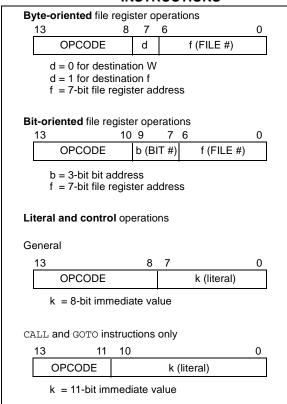

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                               |

| W     | Working register (accumulator)                                                                                                                                     |

| b     | Bit address within an 8-bit file register                                                                                                                          |

| k     | Literal field, constant data or label                                                                                                                              |

| х     | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| PC    | Program Counter                                                                                                                                                    |

| TO    | Time-out bit                                                                                                                                                       |

| PD    | Power-down bit                                                                                                                                                     |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 13-2 lists the instructions recognized by the MPASM $^{TM}$  assembler.

Figure 13-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

| COMF             | Complement f                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                             |

| Operation:       | $(\bar{f}) \to (destination)$                                                                                                                  |

| Status Affected: | Z                                                                                                                                              |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] GOTO k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch. The eleven bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two cycle instruction. |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                   |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] INCF f,d                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                          |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, |  |  |  |  |

|                  | a NOP is executed instead making it a 2Tcy instruction.                                                                                                                                                                               |  |  |  |  |

NOTES:

# 15.1 DC Characteristics: PIC16C717/770/771 (Commercial, Industrial, Extended) PIC16LC717/770/771 (Commercial, Industrial, Extended) (Continued)

| PIC16LC717/770/771 |        |                           |    | Standard Operating Conditions (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                                                                |            |          |                                                     |  |  |  |

|--------------------|--------|---------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|-----------------------------------------------------|--|--|--|

| PIC16C717/770/771  |        |                           |    | Standard Operating Conditions (unless otherwise stated) Operating temperature $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |            |          |                                                     |  |  |  |

| Param.<br>No.      |        |                           |    | Тур†                                                                                                                                                                                                                                                                                                        | Max        | Units    | Conditions                                          |  |  |  |

|                    |        | Base plus Module currer   | nt |                                                                                                                                                                                                                                                                                                             |            |          |                                                     |  |  |  |

| D021A              | IWDT   | Watchdog Timer            |    | 2                                                                                                                                                                                                                                                                                                           | 10         | μА       | VDD = 3V, -40°C to 125°C                            |  |  |  |

| D021               | IWDT   | Watchdog Timer            |    | 5                                                                                                                                                                                                                                                                                                           | 20         | μА       | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D021               | IWDT   | Watchdog Timer            |    | 5                                                                                                                                                                                                                                                                                                           | 20         | μΑ       | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D025               | IT1osc | Timer1 Oscillator         |    | 3                                                                                                                                                                                                                                                                                                           | 9          | μА       | VDD = 3V, -40°C to 125°C                            |  |  |  |

| D025               | IT1osc | Timer1 Oscillator         |    | 4                                                                                                                                                                                                                                                                                                           | 12         | μΑ       | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D025               | IT1osc | Timer1 Oscillator         |    | 4                                                                                                                                                                                                                                                                                                           | 12         | μΑ       | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D026*              | IAD    | ADC Converter             |    | 300                                                                                                                                                                                                                                                                                                         |            | μА       | VDD = 5.5V, A/D on, not converting                  |  |  |  |

| D026*              | IAD    | ADC Converter             |    | 300                                                                                                                                                                                                                                                                                                         |            | μА       | VDD = 5.5V, A/D on, not converting                  |  |  |  |

| D027               | IPLVD  | Programmable Low          |    | 55                                                                                                                                                                                                                                                                                                          | 125        | μА       | VDD = 4V, -40°C to 85°C                             |  |  |  |

| D027A              |        | Voltage Detect            |    |                                                                                                                                                                                                                                                                                                             | 150        |          | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D027               | IPLVD  | Programmable Low          |    | 55                                                                                                                                                                                                                                                                                                          | 125        | μΑ       | VDD = 4V, -40°C to 85°C                             |  |  |  |

| D027A              |        | Voltage Detect            |    |                                                                                                                                                                                                                                                                                                             | 150        |          | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D028               | IPBOR  | Programmable Brown-       |    | 55                                                                                                                                                                                                                                                                                                          | 125        | μА       | VDD = 5V, -40°C to 85°C                             |  |  |  |

| D028A              |        | out Reset                 |    |                                                                                                                                                                                                                                                                                                             | 150        |          | VDD = 5V, -40°C to 125°C                            |  |  |  |

| D028               | IPBOR  | Programmable Brown-       |    | 55                                                                                                                                                                                                                                                                                                          | 125        | μА       | VDD = 5V, -40°C to 85°C                             |  |  |  |

| D028A              | h mu   | out Reset                 |    | 200                                                                                                                                                                                                                                                                                                         | 150        | ۸        | VDD = 5V, -40°C to 125°C                            |  |  |  |

| D029<br>D029A      | Ivrh   | Voltage reference High    |    | 200                                                                                                                                                                                                                                                                                                         | 750<br>1.0 | μA<br>mA | VDD = 5V, -40°C to 85°C<br>VDD = 5V, -40°C to 125°C |  |  |  |

| D029A              | Ivrh   | Voltage reference High    |    | 200                                                                                                                                                                                                                                                                                                         | 750        | μА       | VDD = 5V, -40°C to 85°C                             |  |  |  |

| D029A              | IVINI  | Tollago folololloc Flight |    | 250                                                                                                                                                                                                                                                                                                         | 1.0        | mΑ       | VDD = 5V, -40°C to 125°C                            |  |  |  |

| D030               | IVRL   | Voltage reference Low     |    | 200                                                                                                                                                                                                                                                                                                         | 750        | μА       | VDD = 4V, -40°C to 85°C                             |  |  |  |

| D030A              |        | <b>3</b>                  |    |                                                                                                                                                                                                                                                                                                             | 1.0        | mA       | VDD = 4V, -40°C to 125°C                            |  |  |  |

| D030               | IVRL   | Voltage reference Low     |    | 200                                                                                                                                                                                                                                                                                                         | 750        | μА       | VDD = 4V, -40°C to 85°C                             |  |  |  |

| D030A              |        |                           |    |                                                                                                                                                                                                                                                                                                             | 1.0        | mA       | VDD = 4V, -40°C to 125°C                            |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

DC CHARACTERISTICS

## 15.2 DC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$  +125°C for extended

Operating voltage VDD range as described in Section 15.1 and

|        | Section 15.2. |                                             |                     |      |         |       |                                                                   |  |  |

|--------|---------------|---------------------------------------------|---------------------|------|---------|-------|-------------------------------------------------------------------|--|--|

| Param. | Sym           | Characteristic                              | Min                 | Typ† | Max     | Units | Conditions                                                        |  |  |

| No.    |               |                                             |                     |      |         |       |                                                                   |  |  |

|        |               | Input Low Voltage                           |                     |      |         |       |                                                                   |  |  |

|        | VIL           | I/O ports                                   |                     |      |         |       |                                                                   |  |  |

| D030   |               | with TTL buffer                             | Vss                 | _    | 0.15VDD |       | For entire VDD range                                              |  |  |

| D030A  |               |                                             | Vss                 | _    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                           |  |  |

| D031   |               | with Schmitt Trigger buffer                 | Vss                 | _    | 0.2VDD  | V     | For entire VDD range                                              |  |  |

| D032   |               | MCLR                                        | Vss                 | _    | 0.2VDD  | V     |                                                                   |  |  |

| D033   |               | OSC1 (in XT, HS, LP and EC)                 | Vss                 | 1    | 0.3VDD  | V     |                                                                   |  |  |

|        |               | Input High Voltage                          |                     |      |         |       |                                                                   |  |  |

|        | VIH           | I/O ports                                   |                     | _    |         |       |                                                                   |  |  |

|        |               | with TTL buffer                             |                     |      |         |       |                                                                   |  |  |

| D040   |               |                                             | 2.0                 | _    | VDD     | V     | $4.5V \le VDD \le 5.5V$                                           |  |  |

| D040A  |               |                                             | (0.25VDD<br>+ 0.8V) |      | VDD     | V     | For entire VDD range                                              |  |  |

| D041   |               | with Schmitt Trigger buffer                 | 0.8VDD              | _    | Vdd     | V     | For entire VDD range                                              |  |  |

| D042   |               | MCLR                                        | 0.8VDD              | _    | VDD     | V     |                                                                   |  |  |

| D042A  |               | OSC1 (XT, HS, LP and EC)                    | 0.7Vdd              | _    | Vdd     | V     |                                                                   |  |  |

| D070   | IPURB         | PORTB weak pull-up current                  | 50                  | 250  | 400     | μΑ    | VDD = 5V, VPIN = VSS                                              |  |  |

|        |               | per pin                                     |                     |      |         |       |                                                                   |  |  |

|        |               | Input Leakage Current (1,2)                 |                     |      |         |       |                                                                   |  |  |

| D060   |               | I/O ports (with digital functions)          | _                   | _    | ±1      | μΑ    | $Vss \le VPIN \le VDD$ , Pin at hi-impedance                      |  |  |

| D060A  | lıL           | I/O ports (with analog functions)           | _                   | -    | ±100    | nA    | Vss ≤ VPIN ≤ VDD, Pin at hi-impedance                             |  |  |

| D061   |               | RA5/MCLR/VPP                                | _                   | _    | ±5      | μΑ    | $Vss \le VPIN \le VDD$                                            |  |  |

| D063   |               | OSC1                                        | _                   | _    | ±5      | μА    | Vss ≤ VPIN ≤ VDD, XT, HS, LP and EC osc configuration             |  |  |

|        |               | Output Low Voltage                          |                     |      |         |       |                                                                   |  |  |

| D080   | Vol           | I/O ports                                   | _                   | _    | 0.6     | V     | IOL = 8.5  mA, VDD = 4.5V                                         |  |  |

|        |               | Output High Voltage                         |                     |      |         |       |                                                                   |  |  |

| D090   |               | I/O ports <sup>(2)</sup>                    | VDD - 0.7           |      |         | V     | IOH = -3.0  mA, VDD = 4.5V                                        |  |  |

| D150*  | Vod           | Open Drain High Voltage                     | _                   | 1    | 10.5    | V     | RA4 pin                                                           |  |  |

|        |               | Capacitive Loading Specs on<br>Output Pins* |                     |      |         |       |                                                                   |  |  |

| D100   | COS<br>C2     | OSC2 pin                                    | _                   | _    | 15      | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |

| D101   | Cıo           | All I/O pins and OSC2 (in RC                | _                   | _    | 50      | pF    |                                                                   |  |  |

| D102   |               | mode) SCL, SDA in I <sup>2</sup> C mode     | _                   | _    | 400     | pF    |                                                                   |  |  |

|        |               | VRH pin                                     | _                   | _    | 200     | pF    | VRH output enabled                                                |  |  |

|        |               | VRL pin                                     | _                   | _    | 200     | pF    | VRL output enabled                                                |  |  |

|        |               | •                                           |                     |      | 1       |       |                                                                   |  |  |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>2:</sup> Negative current is defined as current sourced by the pin.

### TABLE 15-6: ENHANCED CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Param.<br>No. | Sym                              | Characteristic        |                            |                             | Min            | Тур† | Max | Units | Conditions                      |

|---------------|----------------------------------|-----------------------|----------------------------|-----------------------------|----------------|------|-----|-------|---------------------------------|

| 50*           | TccL CCP1 input low No Prescaler |                       |                            | 0.5Tcy + 20                 | _              |      | ns  |       |                                 |

|               |                                  | time                  |                            | PIC16 <b>C</b> 717/770/771  | 10             | _    | _   | ns    |                                 |

|               |                                  |                       | With Prescaler             | PIC16 <b>LC</b> 717/770/771 | 20             | _    | _   | ns    |                                 |

| 51*           | TccH                             | CCP1 input high time  | No Prescaler               |                             | 0.5Tcy + 20    | _    | _   | ns    |                                 |

|               |                                  |                       | With Prescaler             | PIC16 <b>C</b> 717/770/771  | 10             | _    | _   | ns    |                                 |

|               |                                  |                       |                            | PIC16 <b>LC</b> 717/770/771 | 20             | _    | _   | ns    |                                 |

| 52*           | TccP                             | CCP1 input period     |                            |                             | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale value (1, 4 or 16) |

| 53*           | TccR CCP1 output fall time       |                       | PIC16 <b>C</b> 717/770/771 | _                           | 10             | 25   | ns  |       |                                 |

|               |                                  |                       |                            | PIC16 <b>LC</b> 717/770/771 | _              | 25   | 45  | ns    |                                 |

| 54*           | TccF                             | CCP1 output fall time |                            | PIC16 <b>C</b> 717/770/771  | _              | 10   | 25  | ns    |                                 |

|               |                                  |                       |                            | PIC16 <b>LC</b> 717/770/771 | _              | 25   | 45  | ns    |                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 15.4.3 PROGRAMMABLE BROWN-OUT RESET MODULE (PBOR)

### TABLE 15-9: DC CHARACTERISTICS: PBOR

Standard Operating Conditions (unless otherwise stated)

Operating temperature 0°C  $\leq$  TA  $\leq$  +70°C for commercial -40°C  $\leq$  TA  $\leq$  +85°C for industrial

-40°C ≤ TA ≤ +125°C for extended

Operating voltage VDD range as described in DC Characteristics Section 15.1.

| Param.<br>No. | Charac      | Symbol         | Min  | Тур | Max  | Units | Conditions |  |

|---------------|-------------|----------------|------|-----|------|-------|------------|--|

| D005          | BOR Voltage | BORV<1:0> = 11 |      | 2.5 | 2.58 | 2.66  |            |  |

|               |             | BORV<1:0> = 10 | VBOR | 2.7 | 2.78 | 2.86  | V          |  |

|               |             | BORV<1:0> = 01 | VBOR | 4.2 | 4.33 | 4.46  | V          |  |

|               |             | BORV<1:0> = 00 |      | 4.5 | 4.64 | 4.78  |            |  |

### 15.4.4 VREF MODULE

**DC CHARACTERISTICS**

**DC CHARACTERISTICS**

#### TABLE 15-10: DC CHARACTERISTICS: VREF

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$  +125°C for extended

Operating voltage VDD range as described in DC Characteristics

Section 15.1.

|               | Geoloff 15.1. |                         |     |       |     |       |                                                                                                                 |                                                             |  |

|---------------|---------------|-------------------------|-----|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| Param.<br>No. | Symbol        | Characteristic          | Min | Тур†  | Max | Units | Conditions                                                                                                      |                                                             |  |

| D400          | VRL           | Output Voltage          | 2.0 | 2.048 | 2.1 | V     | $VDD \ge 2.7V$ ,                                                                                                | -40°C ≤ TA ≤ +85°C                                          |  |

|               | VRH           |                         | 4.0 | 4.096 | 4.2 | V     | $V \text{DD} \geq 4.5 \text{V},$                                                                                | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |  |

| D400A         | VRL           | Output Voltage          | 1.9 | 2.048 | 2.2 | V     | $VDD \ge 2.7V$ , $-40^{\circ}C \le TA \le +125^{\circ}C$                                                        |                                                             |  |

|               | VRH           |                         | 4.0 | 4.096 | 4.3 | V     | $V \text{DD} \geq 4.5 \text{V}, \ \text{-}40 ^{\circ}\text{C} \leq \text{TA} \leq \text{+}125 ^{\circ}\text{C}$ |                                                             |  |

| D404*         | IVREFSO       | External Load Source    | _   | _     | 5   | mA    |                                                                                                                 |                                                             |  |

| D405*         | IVREFSI       | External Load Sink      | _   | _     | -5  | mA    |                                                                                                                 |                                                             |  |

| *             | CL            | External Capacitor Load | _   | _     | 200 | pF    |                                                                                                                 |                                                             |  |

| D406*         | ∆Vout/        | VRH Load Regulation     | _   | 0.6   | 1   | mV/mA | Vdd ≥ 5V                                                                                                        | ISOURCE = 0 mA to 5 mA                                      |  |

|               | ∆lout         |                         | _   | 1     | 4   |       |                                                                                                                 | ISINK = 0 mA to 5 mA                                        |  |

|               |               | VRL Load Regulation     | _   | 0.6   | 1   |       | VDD ≥ 3V                                                                                                        | ISOURCE = 0 mA to 5 mA                                      |  |

|               |               |                         | _   | 2     | 4   |       |                                                                                                                 | ISINK = 0 mA to 5 mA                                        |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

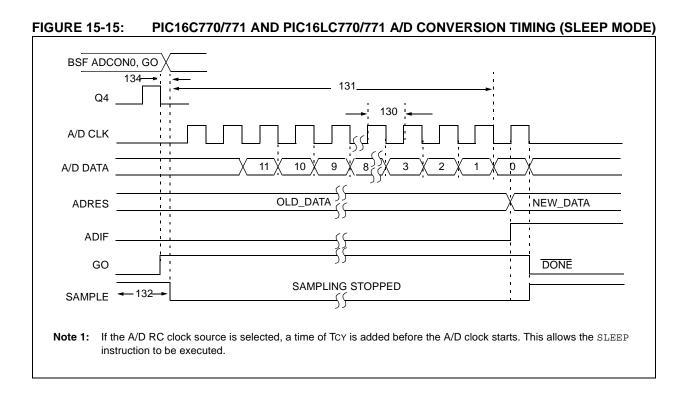

TABLE 15-13: PIC16C770/771 AND PIC16LC770/771 A/D CONVERSION REQUIREMENT (SLEEP MODE)

| Parameter<br>No.    | Sym  | Characteristic                                            | Min      | Typ†         | Max | Units | Conditions                                                                                                                                                                                              |

|---------------------|------|-----------------------------------------------------------|----------|--------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D Internal RC oscillator period                         | 3.0      | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (RC mode)<br>At VDD= 3.0V                                                                                                                                                                |

|                     |      |                                                           | 2.0      | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                           |

| 131*                | TCNV | Conversion time (not including acquisition time) (Note 1) | _        | 13TAD        | _   | _     |                                                                                                                                                                                                         |

| 132*                | TACQ | Acquisition Time                                          | (Note 2) | 11.5         |     | μS    |                                                                                                                                                                                                         |

|                     |      |                                                           | 5*       | _            | _   | μ\$   | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1LSb (i.e., 1mV @ 4.096V) from the last sampled voltage (as stated on CHOLD). |

| 134*                | TGO  | Q4 to A/D clock start                                     | _        | Tosc/2 + Tcy | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                        |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TCY cycle.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> See Section 11.6 for minimum conditions.

<sup>3:</sup> These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

SS SCK (CKP = 0)SCK (CKP = 1)80 LSb SDO MSb 75, 76 SDI MSb IN BIT6 LSb IN

**SPI MASTER MODE TIMING (CKE = 1)** FIGURE 15-19:

TABLE 15-18: SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

Note: Refer to Figure 15-4 for load conditions.

| Param.<br>No. | Symbol                | Characteristic                          |                     | Min          | Тур† | Max | Units  | Conditions |

|---------------|-----------------------|-----------------------------------------|---------------------|--------------|------|-----|--------|------------|

| 71*           | TscH                  | SCK input high time                     | Continuous          | 1.25Tcy + 30 | _    | _   | ns     |            |

| 71A*          |                       | (Slave mode)                            | Single Byte         | 40           | _    | _   | ns     | Note 1     |

| 72*           | TscL                  | SCK input low time                      | Continuous          | 1.25Tcy + 30 |      | -   | ns     |            |

| 72A*          |                       | (Slave mode)                            | Single Byte         | 40           | _    | _   | ns     | Note 1     |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inpedge          | 100                 | _            |      | ns  |        |            |

| 73A*          | Тв2в                  | Last clock edge of Byte1 edge of Byte2  | 1.5Tcy + 40         | _            | _    | ns  | Note 1 |            |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data inpu              | 100                 | _            | _    | ns  |        |            |

| 75*           | TdoR                  | SDO data output rise PIC16 <b>C</b> XXX |                     |              | 10   | 25  | ns     |            |

|               |                       | time                                    | PIC16 <b>LC</b> XXX |              | 20   | 45  | ns     |            |

| 76*           | TdoF                  | SDO data output fall time               |                     | 1            | 10   | 25  | ns     |            |

| 78*           | TscR                  | SCK output rise time                    | PIC16 <b>C</b> XXX  |              | 10   | 25  | ns     |            |

|               |                       | (Master mode)                           | PIC16 <b>LC</b> XXX |              | 20   | 45  | ns     |            |

| 79*           | TscF                  | SCK output fall time (Mas               | ter mode)           |              | 10   | 25  | ns     |            |

| 80*           | TscH2doV,             | SDO data output valid PIC16CXXX         |                     | _            | _    | 50  | ns     |            |

|               | TscL2doV              | after SCK edge PIC16 <b>LC</b> XXX      |                     |              | _    | 100 | ns     |            |

| 81*           | TdoV2scH,<br>TdoV2scL | SDO data output setup to                | SCK edge            | Tcy          | _    | _   | ns     |            |

These parameters are characterized but not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

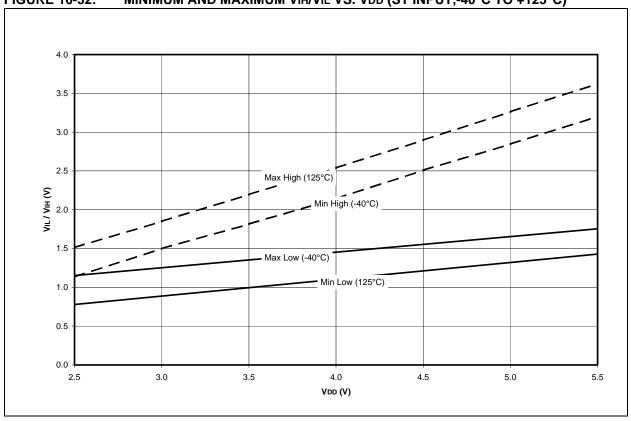

FIGURE 16-32: MINIMUM AND MAXIMUM VIH/VIL VS. VDD (ST INPUT,-40°C TO +125°C)

**APPENDIX B: DEVICE**

**DIFFERENCES**

The differences between the devices in this data sheet are listed in Table B-1.

### TABLE B-1: DEVICE DIFFERENCES

| Difference              | PIC16C717                                                           | PIC16C770                                                           | PIC16C771                                                           |

|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| Program Memory          | 2K                                                                  | 2K                                                                  | 4K                                                                  |

| A/D                     | 6 channels, 10 bits                                                 | 6 channels, 12 bits                                                 | 6 channels, 12 bits                                                 |

| Dedicated AVDD and AVSS | Not available                                                       | Available                                                           | Available                                                           |

| Packages                | 18-pin PDIP, 18-pin windowed<br>CERDIP, 18-pin SOIC,<br>20-pin SSOP | 20-pin PDIP, 20-pin<br>windowed CERDIP, 20-pin<br>SOIC, 20-pin SSOP | 20-pin PDIP, 20-pin windowed<br>CERDIP, 20-pin SOIC,<br>20-pin SSOP |