Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc770-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0 Device Overview                                  | 5   |

|------------------------------------------------------|-----|

| 2.0 Memory Organization                              | 9   |

| 3.0 I/O Ports                                        |     |

| 4.0 Program Memory Read (PMR)                        | 41  |

| 5.0 Timer0 Module                                    |     |

| 6.0 Timer1 Module                                    |     |

| 7.0 Timer2 Module                                    |     |

| 8.0 Enhanced Capture/Compare/PWM (ECCP) Modules      | 53  |

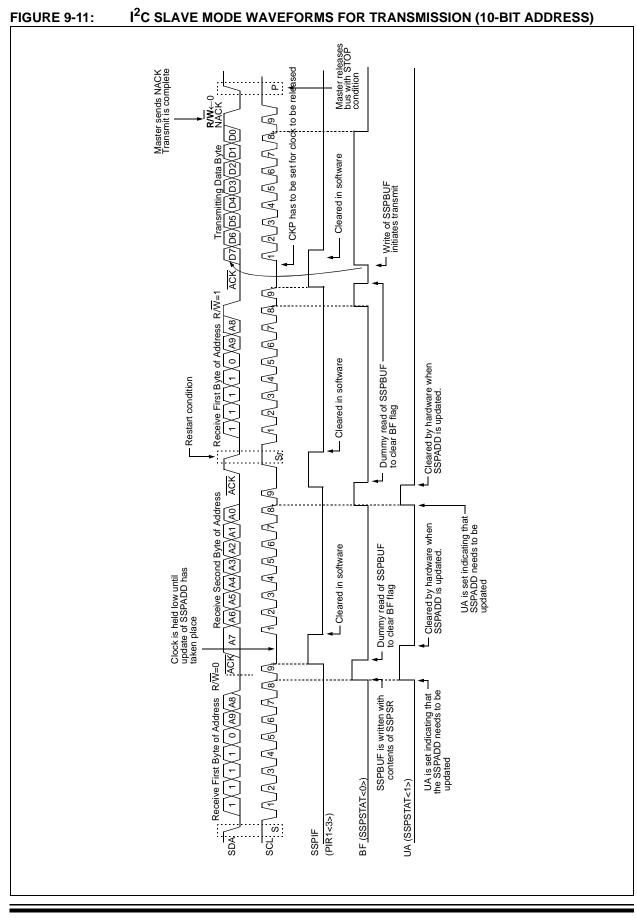

| 9.0 Master Synchronous Serial Port (MSSP) Module     | 65  |

| 10.0 Voltage Reference Module and Low-voltage Detect | 101 |

| 11.0 Analog-to-Digital Converter (A/D) Module        | 105 |

| 12.0 Special Features of the CPU                     | 117 |

| 13.0 Instruction Set Summary                         | 133 |

| 14.0 Development Support                             |     |

| 15.0 Electrical Characteristics                      | 147 |

| 16.0 DC and AC Characteristics Graphs and Tables     | 179 |

| 17.0 Packaging Information                           | 197 |

| APPENDIX A: Revision History                         | 207 |

| APPENDIX B: Device Differences                       | 208 |

| Index                                                | 209 |

| On-Line Support                                      | 215 |

| Reader Response                                      |     |

| PIC16C717/770/771 Product Identification System      | 217 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Address              | Name       | Bit 7         | Bit 6          | Bit 5                   | Bit 4           | Bit 3        | Bit 2           | Bit 1          | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>Page: |

|----------------------|------------|---------------|----------------|-------------------------|-----------------|--------------|-----------------|----------------|---------|--------------------------|------------------------|

| Bank 1               |            |               |                |                         |                 |              |                 |                |         |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressing    | this location  | uses content            | s of FSR to ad  | dress data m | emory (not a    | a physical reg | gister) | 0000 0000                | 23                     |

| 81h                  | OPTION_REG | RBPU          | INTEDG         | TOCS                    | TOSE            | PSA          | PS2             | PS1            | PS0     | 1111 1111                | 15                     |

| 82h <sup>(3)</sup>   | PCL        | Program Co    | ounter's (PC)  | Least Signifi           | cant Byte       |              |                 |                |         | 0000 0000                | 22                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP           | RP1            | RP0                     | TO              | PD           | Z               | DC             | С       | 0001 1xxx                | 14                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect data | a memory ad    | dress pointer           |                 |              |                 |                |         | xxxx xxxx                | 23                     |

| 85h                  | TRISA      | PORTA Dat     | a Direction F  | legister                |                 |              |                 |                |         | 1111 1111                | 25                     |

| 86h                  | TRISB      | PORTB Dat     | ta Direction F | Register                |                 |              |                 |                |         | 1111 1111                | 33                     |

| 87h                  | —          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 88h                  | —          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | _                      |

| 89h                  | _          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _             | _              | _                       | Write Buffer fo | or the upper | 5 bits of the I | Program Cou    | unter   | 0 0000                   | 22                     |

| 8Bh <b>(3)</b>       | INTCON     | GIE           | PEIE           | TOIE                    | INTE            | RBIE         | T0IF            | INTF           | RBIF    | 0000 000x                | 16                     |

| 8Ch                  | PIE1       | —             | ADIE           |                         | —               | SSPIE        | CCP1IE          | TMR2IE         | TMR1IE  | -0 0000                  | 17                     |

| 8Dh                  | PIE2       | LVDIE         | —              |                         | —               | BCLIE        | —               | —              | —       | 0 0                      | 19                     |

| 8Eh                  | PCON       | —             | —              |                         | —               | OSCF         | —               | POR            | BOR     | 1-qq                     | 21                     |

| 8Fh                  | _          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 90h                  | _          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | _                      |

| 91h                  | SSPCON2    | GCEN          | ACKSTAT        | ACKDT                   | ACKEN           | RCEN         | PEN             | RSEN           | SEN     | 0000 0000                | 69                     |

| 92h                  | PR2        | Timer2 Peri   | od Register    |                         |                 |              |                 |                |         | 1111 1111                | 52                     |

| 93h                  | SSPADD     | Synchronou    | is Serial Port | (I <sup>2</sup> C mode) | Address Regist  | er           |                 |                |         | 0000 0000                | 76                     |

| 94h                  | SSPSTAT    | SMP           | CKE            | D/A                     | Р               | S            | R/W             | UA             | BF      | 0000 0000                | 66                     |

| 95h                  | WPUB       | PORTB We      | ak Pull-up C   | ontrol                  |                 |              |                 |                |         | 1111 1111                | 34                     |

| 96h                  | IOCB       | PORTB Inte    | errupt on Cha  | ange Control            |                 |              |                 |                |         | 1111 0000                | 34                     |

| 97h                  | P1DEL      | PWM 1 Del     | ay value       |                         |                 |              |                 |                |         | 0000 0000                | 62                     |

| 98h                  | —          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 99h                  | _          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 9Ah                  | —          | Unimpleme     | nted           |                         |                 |              |                 |                |         | _                        | —                      |

| 9Bh                  | REFCON     | VRHEN         | VRLEN          | VRHOEN                  | VRLOEN          | —            | —               | —              | —       | 0000                     | 102                    |

| 9Ch                  | LVDCON     | —             | —              | BGST                    | LVDEN           | LVV3         | LVV2            | LVV1           | LVV0    | 00 0101                  | 101                    |

| 9Dh                  | ANSEL      | —             | —              | Analog Chai             | nnel Select     |              |                 |                |         | 11 1111                  | 25                     |

| 9Eh                  | ADRESL     | A/D Low By    | te Result Re   | gister                  |                 |              |                 |                |         | xxxx xxxx                | 107                    |

| 9Fh                  | ADCON1     | ADFM          | VCFG2          | VCFG1                   | VCFG0           | _            |                 |                |         | 0000                     | 107                    |

#### TABLE 2-1: PIC16C717/770/771 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

**3:** These registers can be addressed from any bank.

#### 2.2.2.7 PIR2 REGISTER

This register contains the SSP Bus Collision and low-voltage detect interrupt flag bits.

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PERIPHERAL INTERRUPT REGISTER 2 (PIR2: 0Dh)

|         | R/W-0                                                                                                                                                                                               | U-0           | U-0           | U-0          | R/W-0        | U-0    | U-0          | U-0         |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--------------|--------------|--------|--------------|-------------|--|--|--|

|         | LVDIF                                                                                                                                                                                               | _             | —             | —            | BCLIF        | _      | —            | _           |  |  |  |

|         | bit 7                                                                                                                                                                                               |               |               |              |              |        |              | bit 0       |  |  |  |

|         |                                                                                                                                                                                                     |               |               |              |              |        |              |             |  |  |  |

| bit 7   | LVDIF: Low Voltage Detect Interrupt Flag bit                                                                                                                                                        |               |               |              |              |        |              |             |  |  |  |

|         |                                                                                                                                                                                                     | 1,2 0         |               |              |              | 0 (    | be cleared i | n software) |  |  |  |

|         | 0 = The su                                                                                                                                                                                          | oply voltage  | is greater th | nan the spec | ified LVD vo | oltage |              |             |  |  |  |

| bit 6-4 | Unimplem                                                                                                                                                                                            | ented: Rea    | d as '0'      |              |              |        |              |             |  |  |  |

| bit 3   | BCLIF: Bus                                                                                                                                                                                          | s Collision I | nterrupt Flag | ) bit        |              |        |              |             |  |  |  |

|         | <ul> <li>1 = A bus collision has occurred while the SSP module configured in I<sup>2</sup>C Master was transmitting (must be cleared in software)</li> <li>0 = No bus collision occurred</li> </ul> |               |               |              |              |        |              |             |  |  |  |

| bit 2-0 | Unimplem                                                                                                                                                                                            | ented: Rea    | d as '0'      |              |              |        |              |             |  |  |  |

| Legend:            |                  |                                    |                    |  |  |

|--------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

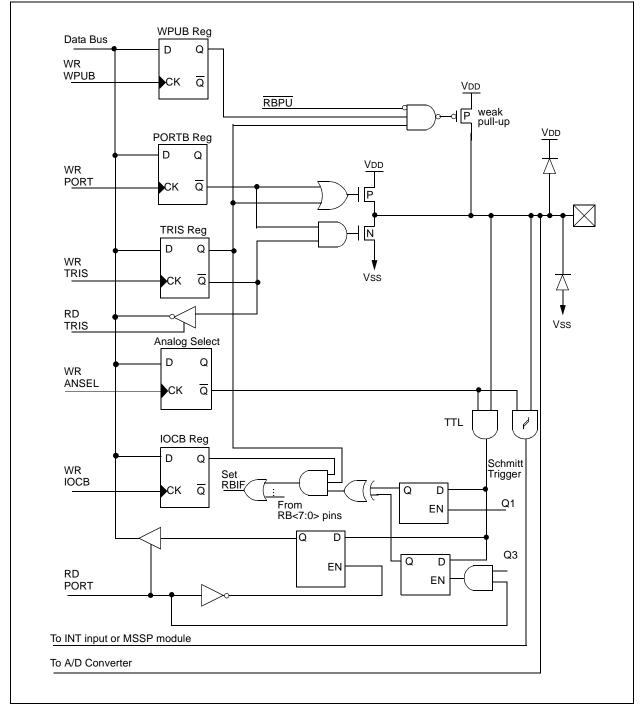

The RB0 pin is multiplexed with the A/D converter analog input 4 and the external interrupt input (RB0/AN4/ INT). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB0 pin as Analog mode. The RB1 pin is multiplexed with the A/D converter analog input 5 and the MSSP module slave select input (RB1/AN5/SS). When the pin is used as analog input, the ANSEL register must have the proper value to select the RB1 pin as Analog mode.

Note: Upon RESET, the ANSEL register configures the RB1 and RB0 pins as analog inputs. Both RB1 and RB0 pins will read as '1'.

FIGURE 3-7: BLOCK DIAGRAM OF RB0/AN4/INT, RB1/AN5/SS PIN

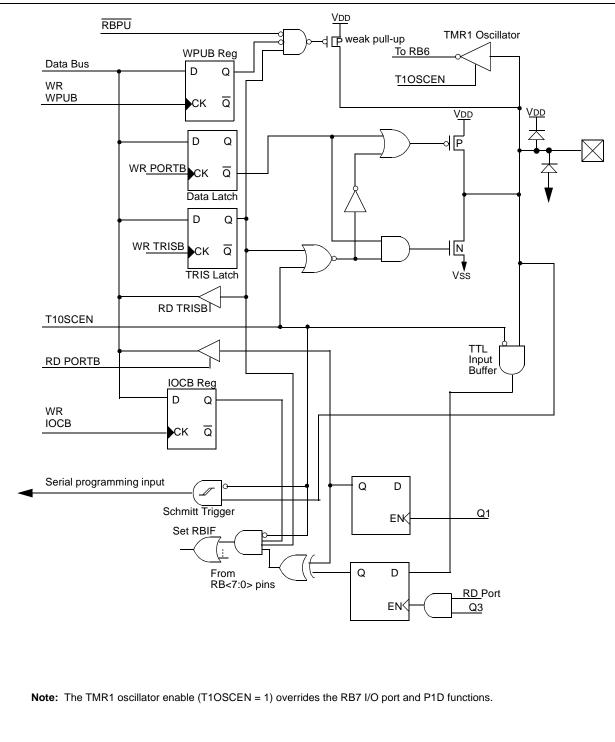

#### FIGURE 3-10: BLOCK DIAGRAM OF THE RB7/T10SI/P1D

# 4.0 PROGRAM MEMORY READ (PMR)

Program memory is readable during normal operation (full VDD range). It is indirectly addressed through the Special Function Registers:

- PMCON1

- PMDATH

- PMDATL

- PMADRH

- PMADRL

When interfacing the program memory block, the PMDATH & PMDATL registers form a 2-byte word, which holds the 14-bit data. The PMADRH & PMADRL registers form a 2-byte word, which holds the 12-bit address of the program memory location being accessed. Mid-range devices have up to 8K words of program EPROM with an address range from 0h to 3FFFh. When the device contains less memory than the full address range of the PMADRH:PMARDL registers, the Most Significant bits of the PMADRH register are ignored.

# 4.1 PMCON1 REGISTER

PMCON1 is the control register for program memory accesses.

Control bit RD initiates a read operation. This bit cannot be cleared, only set, in software. It is cleared in hardware at completion of the read operation.

#### REGISTER 4-1: PROGRAM MEMORY READ CONTROL REGISTER 1 (PMCON1: 18Ch)

| R-1                   | U-0         | U-0      | U-0 | U-0 | U-0 | U-0 | R/S-0 |  |  |  |

|-----------------------|-------------|----------|-----|-----|-----|-----|-------|--|--|--|

| Reserved              | —           | —        | —   | —   | —   | —   | RD    |  |  |  |

| bit 7                 |             |          |     |     |     |     | bit 0 |  |  |  |

|                       |             |          |     |     |     |     |       |  |  |  |

| Reserved: Read as '1' |             |          |     |     |     |     |       |  |  |  |

| Unimpleme             | ented: Read | d as '0' |     |     |     |     |       |  |  |  |

bit 0 **RD**: Read Control bit

1 = Initiates a Program memory read (read takes 2 cycles). RD is cleared in hardware.

0 = Reserved

| Legend:            |                  | S = Settable (cleared in hardware) |                    |  |  |  |

|--------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### 4.2 PMDATH AND PMDATL REGISTERS

bit 7 bit 6-1

The PMDATH:PMDATL registers are loaded with the contents of program memory addressed by the PMADRH and PMADRL registers upon completion of a Program Memory Read command.

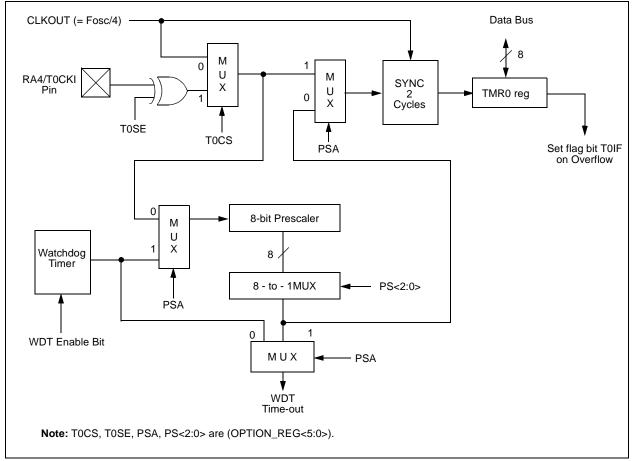

#### 5.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# 5.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER0

| Address                                 | Name       | Bit 7  | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-----------------------------------------|------------|--------|----------|-------|-------|-------|-------|-------|-----------|--------------------------|---------------------------------|

| 01h,101h                                | TMR0       | Timer0 | register |       |       |       |       |       |           | xxxx xxxx                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh                   | INTCON     | GIE    | PEIE     | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF      | 0000 000x                | 0000 000u                       |

| 81h,181h                                | OPTION_REG | RBPU   | INTEDG   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0       | 1111 1111                | 1111 1111                       |

| 85h TRISA PORTA Data Direction Register |            |        |          |       |       |       |       |       | 1111 1111 | 1111 1111                |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

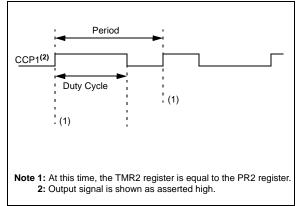

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

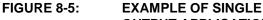

#### 8.3.3 PWM OUTPUT CONFIGURATIONS

The PWM1M1 bits in the CCP1CON register allows one of the following configurations:

- · Single output

- · Half-Bridge output

- Full-Bridge output, Forward mode

- Full-Bridge output, Reverse mode

In the Single Output mode, the RB3/CCP1/P1A pin is used as the PWM output. Since the CCP1 output is multiplexed with the PORTB<3> data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

#### FIGURE 8-4: SINGLE PWM OUTPUT

In the Half-Bridge Output mode, two pins are used as outputs. The RB3/CCP1/P1A pin has the PWM output signal, while the RB5/SDO/P1B pin has the complementary PWM output signal. This mode can be used for half-bridge applications, as shown on Figure 8-7, or for full-bridge applications, where four power switches are being modulated with two PWM signal.

Since the P1A and P1B outputs are multiplexed with the PORTB<3> and PORTB<5> data latches, the TRISB<3> and TRISB<5> bits must be cleared to configure P1A and P1B as outputs.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in bridge power devices. See Section 8.3.5 for more details of the deadband delay operations.

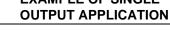

#### 9.2.4 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C slave module can receive addresses or data. When an address match or complete byte transfer occurs, it wakes the processor from SLEEP (if the SSP interrupt bit is enabled).

#### 9.2.5 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

### 9.2.6 MASTER MODE

Master mode operation supports interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is idle with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit (SSPIF) to be set (SSP Interrupt, if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

#### SSPM<3:0>, Internal Data Bus SSPADD<6:0> Read Write SSPBUF Baud Rate Generator SDA Shift clock arbitrate/WCOL detect SDA in Clock $\ge$ SSPSR (hold off clock source) MSb LSb Enable START bit, STOP bit cntl Receive Acknowledge Generate clock SCL START bit detect, STOP bit detect SCL in Set/RESET, S, P, WCOL (SSPSTAT) Vrite collision detect **Clock Arbitration** Set SSPIF. BCLIF State counter for **Bus Collision** RESET ACKSTAT, PEN (SSPCON2) end of XMIT/RCV

# FIGURE 9-13: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

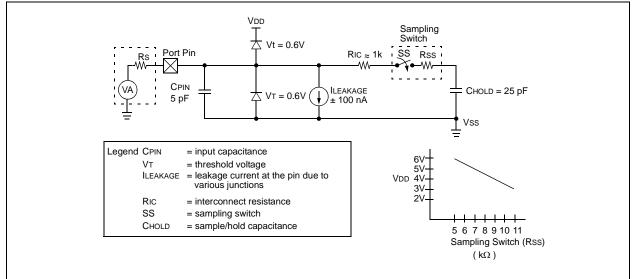

### EXAMPLE 11-3: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

| TACQ =   | Amplifier Settling Time                                  |  |  |  |  |  |  |

|----------|----------------------------------------------------------|--|--|--|--|--|--|

|          | + Holding Capacitor Charging Time                        |  |  |  |  |  |  |

|          | +Temperature offset †                                    |  |  |  |  |  |  |

| TACQ =   | 5 μs                                                     |  |  |  |  |  |  |

|          | + Tc                                                     |  |  |  |  |  |  |

|          | + [(Temp - 25°C)(0.05 μs/°C)] †                          |  |  |  |  |  |  |

| Tc= Ho   | Iding Capacitor Charging Time                            |  |  |  |  |  |  |

| Tc = (C  | HOLD) (RIC + RSS + RS) In (1/16384)                      |  |  |  |  |  |  |

| Tc = -25 | 5 pF (1 kΩ +10 kΩ + 2.5 kΩ) In (1/16384)                 |  |  |  |  |  |  |

| Tc = -25 | 5 pF (13.5 kΩ) In (1/16384)                              |  |  |  |  |  |  |

| Tc = -0. | 338 (-9.704)μs                                           |  |  |  |  |  |  |

| Tc = 3.3 | 3 μs                                                     |  |  |  |  |  |  |

| TACQ =   | 5 µs                                                     |  |  |  |  |  |  |

|          | + 3.3 μs                                                 |  |  |  |  |  |  |

|          | + [(50°C - 25°C)(0.05 μs / °C)]                          |  |  |  |  |  |  |

| TACQ =   | 8.3 μs + 1.25 μs                                         |  |  |  |  |  |  |

| TACQ =   | 9.55 μs                                                  |  |  |  |  |  |  |

|          | perature coefficient is only required for atures > 25°C. |  |  |  |  |  |  |

### FIGURE 11-5: ANALOG INPUT MODEL

# 15.3 AC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

### 15.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

|                                         |                                        | -         | -                                      |

|-----------------------------------------|----------------------------------------|-----------|----------------------------------------|

| 1. TppS2p                               | opS                                    | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

| 2. TppS                                 |                                        | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                                       |                                        |           |                                        |

| F                                       | Frequency                              | Т         | Time                                   |

| Lowerc                                  | ase letters (pp) and their meanings:   |           |                                        |

| рр                                      |                                        |           |                                        |

| сс                                      | CCP1                                   | OSC       | OSC1                                   |

| ck                                      | CLKOUT                                 | rd        | RD                                     |

| CS                                      | CS                                     | rw        | RD or WR                               |

| di                                      | SDI                                    | SC        | SCK                                    |

| do                                      | SDO                                    | SS        | SS                                     |

| dt                                      | Data in                                | tO        | TOCKI                                  |

| io                                      | I/O port                               | t1        | T1CKI                                  |

| mc                                      | MCLR                                   | wr        | WR                                     |

| Upperc                                  | ase letters and their meanings:        |           |                                        |

| S                                       |                                        |           |                                        |

| F                                       | Fall                                   | Р         | Period                                 |

| Н                                       | High                                   | R         | Rise                                   |

| I                                       | Invalid (Hi-impedance)                 | V         | Valid                                  |

| L                                       | Low                                    | Z         | Hi-impedance                           |

| <b>I<sup>2</sup>C</b> (I <sup>2</sup> C | C specifications only)                 |           |                                        |

| AA                                      | output access                          |           |                                        |

| BUF                                     | Bus free                               |           |                                        |

| High                                    | High                                   |           |                                        |

| Low                                     | Low                                    |           |                                        |

| Tcc:st                                  | (I <sup>2</sup> C specifications only) |           |                                        |

| CC                                      | · · ·                                  |           |                                        |

| HD                                      | Hold                                   | SU        | Setup                                  |

| ST                                      |                                        |           |                                        |

| DAT                                     | DATA input hold                        | STO       | STOP condition                         |

| STA                                     | START condition                        |           |                                        |

| TABLE 15-6: | ENHANCED CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP) |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

| Param.<br>No. | Sym Characteristic |                      | Min               | Тур†                        | Max          | Units | Conditions  |    |                                    |    |  |

|---------------|--------------------|----------------------|-------------------|-----------------------------|--------------|-------|-------------|----|------------------------------------|----|--|

| 50*           | TccL               | CCP1 input low       | No Prescaler      |                             | 0.5Tcy + 20  | —     | _           | ns |                                    |    |  |

|               |                    | time                 |                   | PIC16 <b>C</b> 717/770/771  | 10           | _     | _           | ns |                                    |    |  |

|               |                    |                      | With Prescaler    | PIC16 <b>LC</b> 717/770/771 | 20           | —     | _           | ns |                                    |    |  |

| 51* Tccł      | TccH               | CCP1 input high time | CCP1 input high   | CCP1 input high             | No Prescaler | •     | 0.5Tcy + 20 | —  | _                                  | ns |  |

|               |                    |                      | With Prescaler    | PIC16 <b>C</b> 717/770/771  | 10           | _     | _           | ns |                                    |    |  |

|               |                    |                      |                   | PIC16 <b>LC</b> 717/770/771 | 20           | —     | _           | ns |                                    |    |  |

| 52*           | TccP               | CCP1 input period    | CCP1 input period |                             |              | —     | _           | ns | N = prescale value<br>(1, 4 or 16) |    |  |

| 53*           | TccR               | CCP1 output fall ti  | me                | PIC16 <b>C</b> 717/770/771  | —            | 10    | 25          | ns |                                    |    |  |

|               |                    |                      |                   | PIC16 <b>LC</b> 717/770/771 | —            | 25    | 45          | ns |                                    |    |  |

| 54*           | TccF               | CCP1 output fall ti  | me                | PIC16 <b>C</b> 717/770/771  | —            | 10    | 25          | ns |                                    |    |  |

|               |                    |                      |                   | PIC16 <b>LC</b> 717/770/771 | —            | 25    | 45          | ns |                                    |    |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 15.4 Analog Peripherals Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

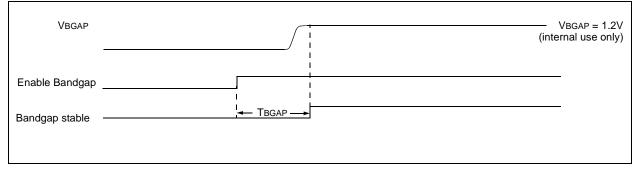

#### 15.4.1 BANDGAP MODULE

#### FIGURE 15-12: BANDGAP START-UP TIME

### TABLE 15-7: BANDGAP START-UP TIME

| Param.<br>No. | Sym   | Characteristic        | Min | Тур† | Мах | Units | Conditions                                                                                                                                   |

|---------------|-------|-----------------------|-----|------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 36*           | Tbgap | Bandgap start-up time |     | 19   | 33  | μS    | Defined as the time between the<br>instant that the bandgap is<br>enabled and the moment that<br>the bandgap reference voltage<br>is stable. |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 15.4.3 PROGRAMMABLE BROWN-OUT RESET MODULE (PBOR)

# TABLE 15-9: DC CHARACTERISTICS: PBOR

| $\label{eq:characteristics} \text{Standard Operating Conditions (unless otherwise stated)} \\ \text{Operating temperature}  0^\circ\text{C} &\leq T\text{A} \leq +70^\circ\text{C} \text{ for commercial} \\ -40^\circ\text{C} &\leq T\text{A} \leq +85^\circ\text{C} \text{ for industrial} \\ -40^\circ\text{C} &\leq T\text{A} \leq +125^\circ\text{C} \text{ for extended} \\ \text{Operating voltage VDD range as described in DC Characteristics Section 15.1.} \end{cases}$ |             |                |        |     |      |      |       |            |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------|-----|------|------|-------|------------|--|

| Param.<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Charac      | teristic       | Symbol | Min | Тур  | Max  | Units | Conditions |  |

| D005                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BOR Voltage | BORV<1:0> = 11 |        | 2.5 | 2.58 | 2.66 |       |            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | BORV<1:0> = 10 | VBOR   | 2.7 | 2.78 | 2.86 | v     |            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | BORV<1:0> = 01 |        | 4.2 | 4.33 | 4.46 |       |            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | BORV<1:0> = 00 |        | 4.5 | 4.64 | 4.78 |       |            |  |

#### 15.4.4 VREF MODULE

#### TABLE 15-10: DC CHARACTERISTICS: VREF

| DC CHARACTERISTICS |                |                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ for commercial $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C$ $\leq TA \leq +125^{\circ}C$ for extendedOperating voltage VDD range as described in DC CharacteristicsSection 15.1. |       |     |       |                                                                                                                 |                                                 |  |  |  |

|--------------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol         | Characteristic          | Min                                                                                                                                                                                                                                                                                                                                | Тур†  | Max | Units | Conditions                                                                                                      |                                                 |  |  |  |

| D400               | VRL            | Output Voltage          | 2.0                                                                                                                                                                                                                                                                                                                                | 2.048 | 2.1 | V     | $VDD \ge 2.7V,$                                                                                                 | $\text{-40°C} \leq \text{TA} \leq \text{+85°C}$ |  |  |  |

|                    | VRH            |                         | 4.0                                                                                                                                                                                                                                                                                                                                | 4.096 | 4.2 | V     | $V\text{DD} \geq 4.5\text{V},$                                                                                  | $\text{-40°C} \leq \text{TA} \leq \text{+85°C}$ |  |  |  |

| D400A              | VRL            | Output Voltage          | 1.9                                                                                                                                                                                                                                                                                                                                | 2.048 | 2.2 | V     | $V \text{DD} \geq 2.7 \text{V}, \ \text{-40}^{\circ} \text{C} \leq \text{Ta} \leq \text{+125}^{\circ} \text{C}$ |                                                 |  |  |  |

|                    | VRH            |                         | 4.0                                                                                                                                                                                                                                                                                                                                | 4.096 | 4.3 | V     | $V\text{DD} \geq 4.5\text{V}, \ \text{-}40^{\circ}\text{C} \leq \text{Ta} \leq \text{+}125^{\circ}\text{C}$     |                                                 |  |  |  |

| D404*              | IVREFSO        | External Load Source    |                                                                                                                                                                                                                                                                                                                                    | _     | 5   | mA    |                                                                                                                 |                                                 |  |  |  |

| D405*              | IVREFSI        | External Load Sink      | _                                                                                                                                                                                                                                                                                                                                  | _     | -5  | mA    |                                                                                                                 |                                                 |  |  |  |

| *                  | CL             | External Capacitor Load | _                                                                                                                                                                                                                                                                                                                                  | _     | 200 | pF    |                                                                                                                 |                                                 |  |  |  |

| D406*              | $\Delta$ Vout/ | VRH Load Regulation     | _                                                                                                                                                                                                                                                                                                                                  | 0.6   | 1   | mV/mA | $V\text{dd} \geq 5V$                                                                                            | ISOURCE = 0 mA to 5 mA                          |  |  |  |

|                    | ∆lout          |                         | _                                                                                                                                                                                                                                                                                                                                  | 1     | 4   | ]     |                                                                                                                 | ISINK = 0 mA to 5 mA                            |  |  |  |

|                    |                | VRL Load Regulation     |                                                                                                                                                                                                                                                                                                                                    | 0.6   | 1   | ]     | $VDD \geq 3V$                                                                                                   | ISOURCE = 0 mA to 5 mA                          |  |  |  |

|                    |                |                         | _                                                                                                                                                                                                                                                                                                                                  | 2     | 4   | ]     |                                                                                                                 | ISINK = 0 mA to 5 mA                            |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param.<br>No. | Symbol  | Characteristic      |                           | Min              | Max  | Units | Conditions                        |

|---------------|---------|---------------------|---------------------------|------------------|------|-------|-----------------------------------|

| 100*          | Thigh   | Clock high time     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 101*          | TLOW    | Clock low time      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         |                     | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 102*          | TR      | SDA and SCL         | 100 kHz mode              | _                | 1000 | ns    | Cb is specified to be from        |

|               |         | rise time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                                   |

| 103*          | TF      | SDA and SCL         | 100 kHz mode              | _                | 300  | ns    | Cb is specified to be from        |

|               |         | fall time           | 400 kHz mode              | 20 + 0.1Cb       | 300  | ns    | 10 to 400 pF                      |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns    |                                   |

| 90*           | TSU:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | Only relevant for Repeated        |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | START                             |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    | condition                         |

| 91*           | THD:STA | START condition     | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period the first clock |

|               |         | hold time           | 400 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    | pulse is generated                |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 106*          | THD:DAT | Data input          | 100 kHz mode              | 0                | —    | ns    |                                   |

|               |         | hold time           | 400 kHz mode              | 0                | 0.9  | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | —    | ns    |                                   |

| 107*          | TSU:DAT | Data input          | 100 kHz mode              | 250              | —    | ns    | Note 2                            |

|               |         | setup time          | 400 kHz mode              | 100              | —    | ns    | 1                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD              | -    | ns    |                                   |

| 92*           | Tsu:sto | STOP condition      | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

|               |         | setup time          | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | ]                                 |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                                   |

| 109*          | TAA     | Output valid from   | 100 kHz mode              | —                | 3500 | ns    |                                   |

|               |         | clock               | 400 kHz mode              |                  | 1000 | ns    |                                   |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | _                | _    | ns    |                                   |

| 110           | TBUF    | Bus free time       | 100 kHz mode              | 4.7 ‡            | —    | ms    | Time the bus must be free         |

|               |         |                     | 400 kHz mode              | 1.3 ‡            | —    | ms    | before a new transmission         |

|               |         |                     | 1 MHz mode <sup>(1)</sup> | TBD‡             | —    | ms    | can start                         |

| D102 ‡        | Cb      | Bus capacitive load |                           | —                | 400  | pF    |                                   |

# TABLE 15-22: MASTER SSP I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested. For the value required by the I<sup>2</sup>C specification, please refer to the PICmicro<sup>TM</sup> Mid-Range MCU Family Reference Manual (DS33023).

‡ These parameters are for design guidance only and are not tested, nor characterized.

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

2: A Fast mode  $l^2C$  bus device can be used in a Standard mode  $l^2C$  bus system, but  $(TSU:DAT) \ge 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line.

[(TR) + (TSU:DAT) = 1000 + 250 = 1250 ns], for 100 kHz mode, before the SCL line is released.

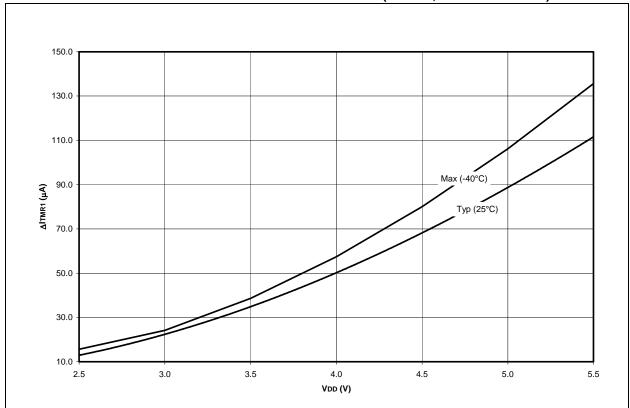

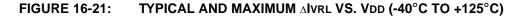

#### FIGURE 16-20: TYPICAL AND MAXIMUM AITMR1 VS. VDD (32 KHZ, -40°C TO +125°C)

17.6 20-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

DRAWING NOT AVAILABLE