Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

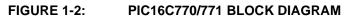

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 15                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc770t-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C717/770/771

#### 2.2.2.2 **OPTION\_REG REGISTER**

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### **OPTION REGISTER (OPTION\_REG: 81h, 181h) REGISTER 2-2:**

|         | R/W-1     | R/W-1                            | R/W-1                      | R/W-1                        | R/W-1         | R/W-1 | R/W-1 | R/W-1 |

|---------|-----------|----------------------------------|----------------------------|------------------------------|---------------|-------|-------|-------|

|         | RBPU      | INTEDG                           | TOCS                       | T0SE                         | PSA           | PS2   | PS1   | PS0   |

|         | bit 7     |                                  |                            |                              |               |       |       | bit 0 |

|         |           |                                  |                            |                              |               |       |       |       |

| bit 7   | RBPU: PC  | RTB Pull-u                       | p Enable bit               | (1)                          |               |       |       |       |

|         |           | B weak pull-<br>B weak pull-     | •                          |                              | WPUB register |       |       |       |

| bit 6   | INTEDG:   | nterrupt Edg                     | ge Select bi               | t                            |               |       |       |       |

|         |           | pt on rising<br>pt on falling    | •                          | •                            |               |       |       |       |

| bit 5   | TOCS: TM  | R0 Clock So                      | ource Selec                | t bit                        |               |       |       |       |

|         |           | ion on RA4/<br>al instruction    |                            | (CLKOUT)                     |               |       |       |       |

| bit 4   | TOSE: TM  | R0 Source E                      | Edge Select                | bit                          |               |       |       |       |

|         |           | •                                |                            | sition on RA<br>sition on RA | •             |       |       |       |

| bit 3   | PSA: Pres | caler Assigr                     | nment bit                  |                              |               |       |       |       |

|         |           | aler is assigr<br>aler is assigr |                            | VDT<br>ïmer0 modu            | le            |       |       |       |

| bit 2-0 | PS<2:0>:  | Prescaler R                      | ate Select b               | oits                         |               |       |       |       |

|         | I         | Bit Value T                      | MR0 Rate                   | WDT Rate                     |               |       |       |       |

|         | _         | 000<br>001<br>010                | 1:2<br>1:4<br>1:8          | 1 : 1<br>1 : 2<br>1 : 4      |               |       |       |       |

|         |           | 011<br>100<br>101                | 1 : 16<br>1 : 32<br>1 : 64 | 1 : 8<br>1 : 16<br>1 : 32    |               |       |       |       |

1:64

1:128

1:128

1:256

110

111

Note 1: Individual weak pull-up on RB pins can be enabled/disabled from the weak pull-up PORTB Register (WPUB).

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

# REGISTER 2-4: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (PIE1: 8Ch)

|         | U-0                                                                                                           | R/W-0                        | U-0                       | U-0          | R/W-0       | R/W-0     | R/W-0          | R/W-0  |  |

|---------|---------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|--------------|-------------|-----------|----------------|--------|--|

|         |                                                                                                               | ADIE                         | —                         | —            | SSPIE       | CCP1IE    | TMR2IE         | TMR1IE |  |

|         | bit 7                                                                                                         |                              |                           |              |             |           |                | bit 0  |  |

|         |                                                                                                               |                              |                           |              |             |           |                |        |  |

| bit 7   | Unimplem                                                                                                      | ented: Read                  | d as '0'                  |              |             |           |                |        |  |

| bit 6   | ADIE: A/D                                                                                                     | Converter In                 | nterrupt Ena              | ble bit      |             |           |                |        |  |

|         |                                                                                                               | s the A/D in<br>s the A/D in | •                         |              |             |           |                |        |  |

| bit 5-4 | Unimplem                                                                                                      | ented: Read                  | d as '0'                  |              |             |           |                |        |  |

| bit 3   | SSPIE: Syr                                                                                                    | nchronous S                  | Serial Port In            | terrupt Enab | ole bit     |           |                |        |  |

|         |                                                                                                               | s the SSP ir<br>s the SSP i  |                           |              |             |           |                |        |  |

| bit 2   | CCP1IE: C                                                                                                     | CP1 Interru                  | pt Enable bit             | t            |             |           |                |        |  |

|         |                                                                                                               | s the CCP1<br>s the CCP1     |                           |              |             |           |                |        |  |

| bit 1   | TMR2IE: T                                                                                                     | MR2 to PR2                   | 2 Match Inter             | rupt Enable  | bit         |           |                |        |  |

|         |                                                                                                               |                              | to PR2 mate<br>to PR2 mat |              |             |           |                |        |  |

| bit 0   | TMR1IE: T                                                                                                     | MR1 Overfle                  | ow Interrupt              | Enable bit   |             |           |                |        |  |

|         | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul> |                              |                           |              |             |           |                |        |  |

|         |                                                                                                               |                              |                           |              |             |           |                |        |  |

|         | Legend:                                                                                                       |                              |                           |              |             |           |                |        |  |

|         | R = Reada                                                                                                     | ble bit                      | W = W                     | ritable bit  | U = Unim    | plemented | bit, read as ' | 0'     |  |

|         | - n = Value                                                                                                   | at POR                       | '1' = Bi                  | t is set     | '0' = Bit i | s cleared | x = Bit is u   | nknown |  |

### 2.2.2.8 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

The PCON register also contains the frequency select bit of the INTRC or ER oscillator.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

# REGISTER 2-8: POWER CONTROL REGISTER (PCON: 8Eh)

- n = Value at POR

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | —   | —   | OSCF  | _   | POR   | BOR   |

| bit 7 |     |     |     |       |     |       | bit 0 |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | OSCF: Oscillator Speed bit                                                                                                       |

|         | INTRC Mode                                                                                                                       |

|         | 1 = 4 MHz nominal                                                                                                                |

|         | 0 = 37 kHz nominal                                                                                                               |

|         | ER Mode                                                                                                                          |

|         | <ul> <li>1 = Oscillator frequency depends on the external resistor value on the OSC1 pin.</li> <li>0 = 37 kHz nominal</li> </ul> |

|         | All other modes                                                                                                                  |

|         | x = Ignored                                                                                                                      |

| bit 2   | Unimplemented: Read as '0'                                                                                                       |

| bit 1   | POR: Power-on Reset Status bit                                                                                                   |

|         | 1 = No Power-on Reset occurred                                                                                                   |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                            |

| bit 0   | BOR: Brown-out Reset Status bit (See Section 2.2.2.8 Note)                                                                       |

|         | 1 = No Brown-out Reset occurred                                                                                                  |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)                                          |

|         |                                                                                                                                  |

|         | Legend: q = Value depends on conditions                                                                                          |

|         | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                             |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

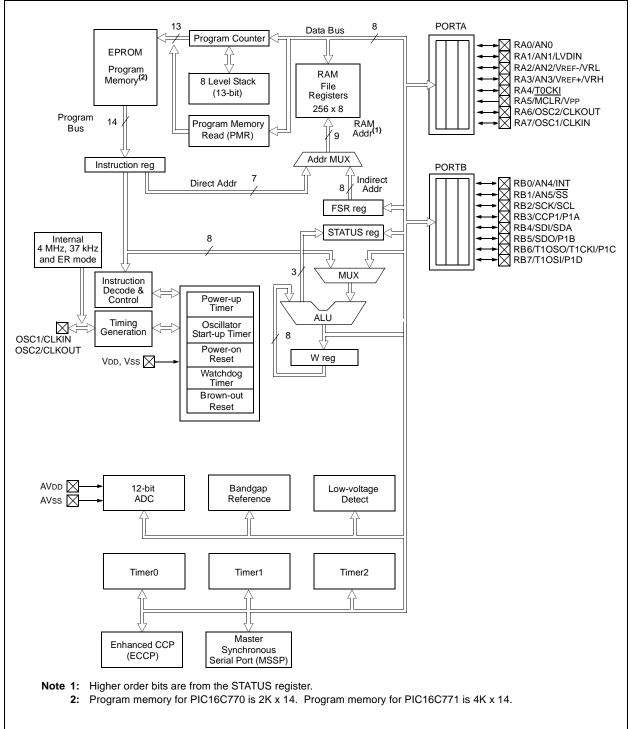

# 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register occur through the PCLATH register.

### 2.3.1 PROGRAM MEMORY PAGING

PIC16C717/770/771 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. A return instruction pops a PC address off the stack onto the PC register. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

# 2.4 Stack

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

#### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

### EXAMPLE 2-1: How to Clear RAM Using Indirect Addressing

|        | movlw | 0x20  | ;initialize pointer  |

|--------|-------|-------|----------------------|

|        | movwf | FSR   | ; to RAM             |

| NEXT   | clrf  | INDF  | ;clear INDF register |

|        | incf  | FSR   | ;inc pointer         |

|        | btfss | FSR,4 | ;all done?           |

|        | goto  | NEXT  | ;NO, clear next      |

| CONTIN | IUE   |       |                      |

|        | :     |       | ;YES, continue       |

|        |       |       |                      |

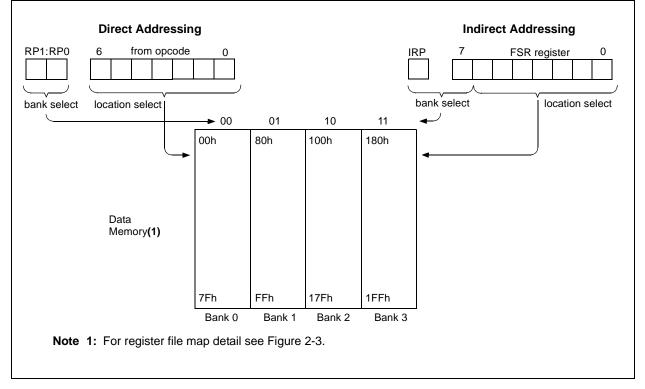

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

# FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

### TABLE 4-1: PROGRAM MEMORY READ REGISTER SUMMARY

| Address | Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|----------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 18Ch    | PMCON1 | Reserved | _     | _     | _     | _     | —     |       | RD    | 1 0                      | 10                              |

| 10Eh    | PMDATH | _        | _     | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  | xx xxxx                  | uu uuuu                         |

| 10Ch    | PMDATL | PMD7     | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _        | _     | —     | _     | PMA11 | PMA10 | PMA9  | PMA8  | xxxx                     | uuuu                            |

| 10Dh    | PMADRL | PMA7     | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  | XXXX XXXX                | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Program Memory Read.

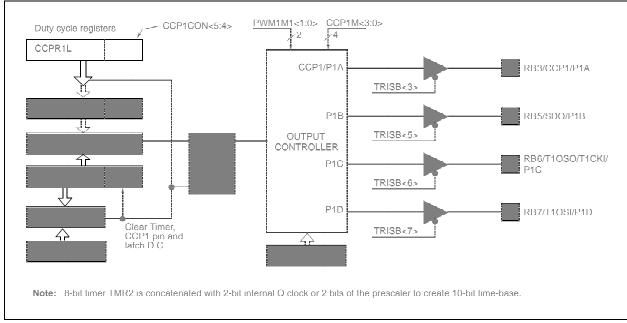

# 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the ECCP module produces up to a 10-bit resolution PWM output. Figure 8-3 shows the simplified PWM block diagram.

### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM PERIOD = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 PRESCALE VALUE)$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 7.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

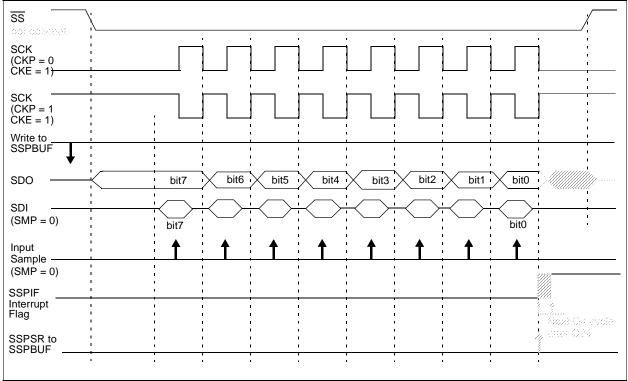

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit, BF (SSPSTAT<0>), indicates when the SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

# EXAMPLE 9-1: Loading the SSPBUF (SSPSR) Register

|      |       |             | , 0               |

|------|-------|-------------|-------------------|

|      | BSF   | STATUS, RPO | ;Specify Bank 1   |

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been    |

|      |       |             | ;received         |

|      |       |             | ;(xmit complete)? |

|      | GOTO  | LOOP        | ;No               |

|      | BCF   | STATUS, RPO | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, W   | ;Save SSPBUF      |

|      | MOVWF | RXDATA      | ;in user RAM      |

|      | MOVF  | TXDATA, W   | ;Get next TXDATA  |

|      | MOVWF | SSPBUF      | ;New data to xmit |

|      |       |             |                   |

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP STATUS register (SSPSTAT) indicates the various status conditions.

# 9.1.2 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISB<5> cleared

- SCK (Master mode) must have TRISB<2> cleared

- SCK (Slave mode) must have TRISB<2> set

- SS must have TRISB<1> set, and ANSEL<5> cleared

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

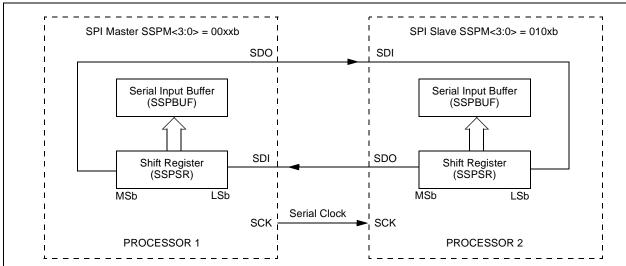

# 9.1.3 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (SSPCON<4>), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

# FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

# PIC16C717/770/771

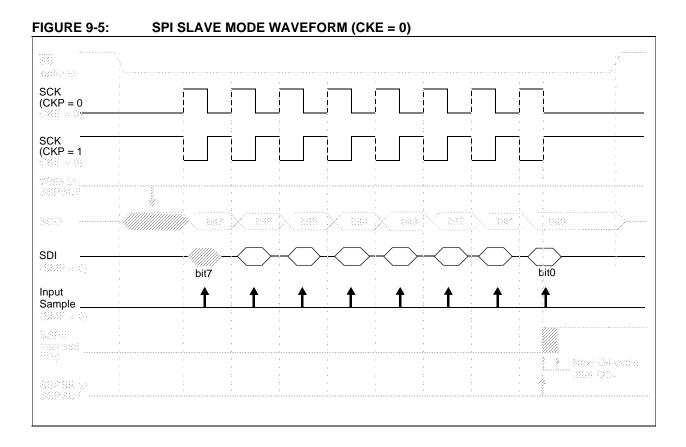

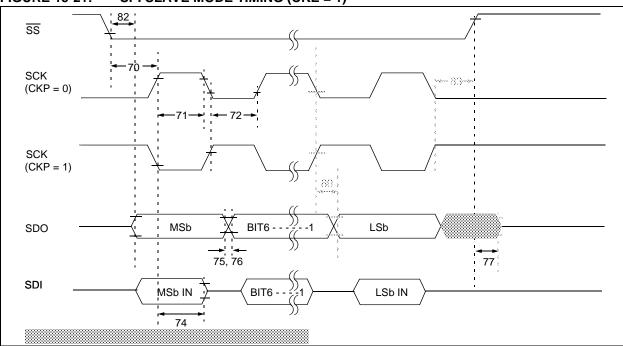

# FIGURE 9-6: SPI SLAVE MODE WAVEFORM (CKE = 1)

### 9.1.7 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from SLEEP. After the device returns to Normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in SLEEP mode and data to be shifted into the SPI transmit/receive shift register. When all eight bits have been received, the SSPIF interrupt flag bit will be set and if enabled will wake the device from SLEEP.

# 9.1.8 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

| Address                | Name    | Bit 7 | Bit 6   | Bit 5       | Bit 4     | Bit 3        | Bit 2         | Bit 1    | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|-------|---------|-------------|-----------|--------------|---------------|----------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE   | PEIE    | TOIE        | INTE      | RBIE         | T0IF          | INTF     | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | _     | ADIF    | -           | -         | SSPIF        | CCP1IF        | TMR2IF   | TMR1IF | -0 0000   | -0 0000   |

| 8Ch                    | PIE1    | _     | ADIE    | -           | -         | SSPIE        | CCP1IE        | TMR2IE   | TMR1IE | -0 0000   | -0 0000   |

| 13h                    | SSPBUF  |       | Synchro | onous Seria | I Port Re | eceive Buffe | er/Transmit I | Register |        | XXXX XXXX | uuuu uuuu |

| 14h                    | SSPCON  | WCOL  | SSPOV   | SSPEN       | CKP       | SSPM3        | SSPM2         | SSPM1    | SSPM0  | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP   | CKE     | D/A         | Р         | S            | R/W           | UA       | BF     | 0000 0000 | 0000 0000 |

| 9Dh                    | ANSEL   |       |         |             |           |              |               |          |        | 11 1111   | 11 1111   |

| 86h                    | TRISB   |       |         |             |           |              |               |          |        | 1111 1111 | 1111 1111 |

# TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the MSSP in SPI mode.

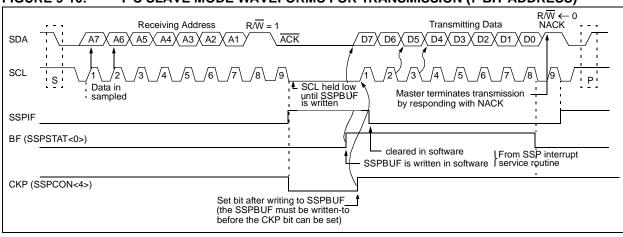

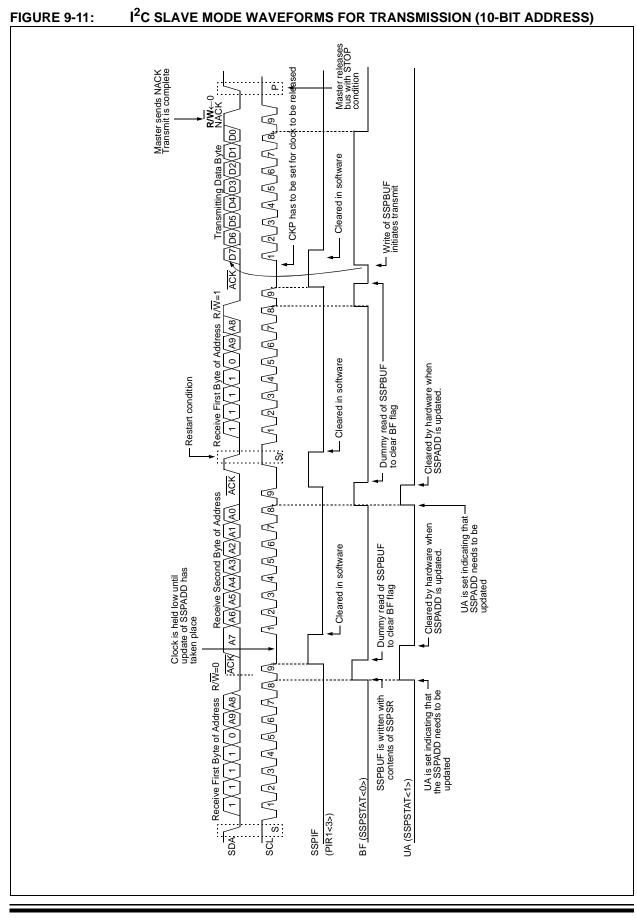

### 9.2.2.4 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSP-STAT register is set. The received address is loaded into the SSPBUF register on the falling edge of the eighth SCL pulse. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The slave module automatically stretches the clock by holding the SCL line low so that the master will be unable to assert another clock pulse until the slave is finished preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. The CKP bit (SSPCON<4>) must then be set to release the SCL pin from the forced low condition. The eight data bits are shifted out on the falling edges of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-10).

The  $\overline{ACK}$  or NACK signal from the master-receiver is latched on the rising edge of the ninth SCL input pulse. The master-receiver terminates slave transmission by

sending a NACK. If the SDA line is high (NACK), then the data transfer is complete. When the NACK is latched by the slave, the slave logic is RESET which also resets the R/W bit to '0'. The slave module then monitors for another occurrence of the START bit. The slave firmware knows not to load another byte into the SSPBUF register by sensing that the buffer is empty (BF = 0) and the R/W bit has gone low. If the SDA line is low (ACK), the R/W bit remains high indicating that the next transmit data must be loaded into the SSPBUF register.

An MSSP interrupt (SSPIF flag) is generated for each data transfer byte on the falling edge of the ninth clock pulse. The SSPIF flag bit must be cleared in software. The SSPSTAT register is used to determine the status of the byte transfer.

For more information about the I<sup>2</sup>C Slave mode, refer to Application Note AN734, "Using the PIC<sup>®</sup> SSP for Slave  $l^2C^{TM}$  Communication".

### FIGURE 9-10: I<sup>2</sup>C SLAVE MODE WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# 10.0 VOLTAGE REFERENCE MODULE AND LOW-VOLTAGE DETECT

The Voltage Reference module provides reference voltages for the Brown-out Reset circuitry, the Low-voltage Detect circuitry and the A/D converter.

b b

b

b

The source for the reference voltages comes from the bandgap reference circuit. The bandgap circuit is energized anytime the reference voltage is required by the other sub-modules, and is powered down when not in use. The control registers for this module are LVDCON and REFCON, as shown in Register 10-1 and Figure 10-2.

### REGISTER 10-1: LOW-VOLTAGE DETECT CONTROL REGISTER (LVDCON: 9Ch)

| U-0                      | U-0           | R-0           | R/W-0                    | R/W-0        | R/W-1          | R/W-0        | R/W-1      |

|--------------------------|---------------|---------------|--------------------------|--------------|----------------|--------------|------------|

| _                        | _             | BGST          | LVDEN                    | LV3          | LV2            | LV1          | LV0        |

| bit 7                    |               | •             | •                        |              |                |              | bit        |

|                          |               |               |                          |              |                |              |            |

| Unimplem                 | nented: Read  | d as '0'      |                          |              |                |              |            |

| BGST: Ba                 | ndgap Stable  | e Status Flag | g bit                    |              |                |              |            |

| 1 = Indicat              | es that the b | andgap volt   | age is stable            | e, and LVD i | nterrupt is re | eliable      |            |

| 0 = Indicat              | es that the b | andgap volt   | age is not st            | able, and L\ | /D interrupt   | should not b | be enabled |

| LVDEN: LO                | ow-voltage D  | etect Powe    | r Enable bit             |              |                |              |            |

| 1 = Enable               | es LVD, powe  | ers up band   | ap circuit a             | nd reference | e generator    |              |            |

|                          | es LVD, pow   | •             | • •                      |              | •              | /RH/VRL      |            |

| LV<3:0>: l               | Low Voltage   | Detection Li  | imit bits <sup>(1)</sup> |              | •              |              |            |

|                          | ternal analog |               |                          |              |                |              |            |

| 1110 = 4.5               |               | 5 1           |                          |              |                |              |            |

| 1101 = 4.2               | 2V            |               |                          |              |                |              |            |

| 1100 = 4.0               |               |               |                          |              |                |              |            |

| 1011 = 3.8               |               |               |                          |              |                |              |            |

| 1010 = 3.6               | -             |               |                          |              |                |              |            |

| 1001 = 3.5               |               |               |                          |              |                |              |            |

| 1000 = 3.3               |               |               |                          |              |                |              |            |

| 0111 = 3.0<br>0110 = 2.8 |               |               |                          |              |                |              |            |

| 0110 = 2.0<br>0101 = 2.7 |               |               |                          |              |                |              |            |

| 0101 = 2.7<br>0100 = 2.5 |               |               |                          |              |                |              |            |

|                          | eserved. Do i | not use       |                          |              |                |              |            |

|                          | eserved. Do i |               |                          |              |                |              |            |

|                          | eserved. Do i |               |                          |              |                |              |            |

| 0000 = Re                |               |               |                          |              |                |              |            |

**Note:** These are the minimum trip points for the LVD. See Table 15-8 for the trip point tolerances. Selection of reserved setting may result in an inadvertent interrupt.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

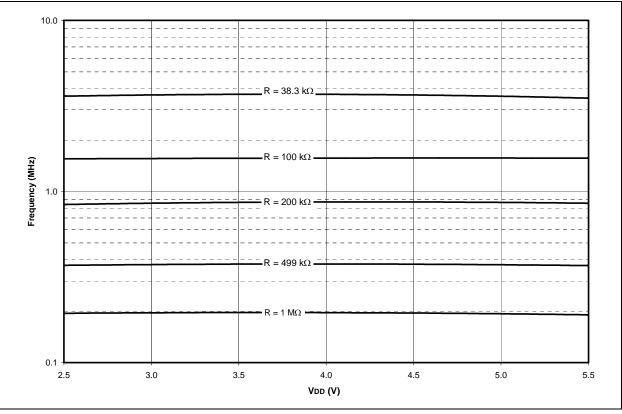

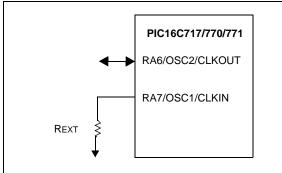

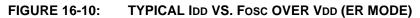

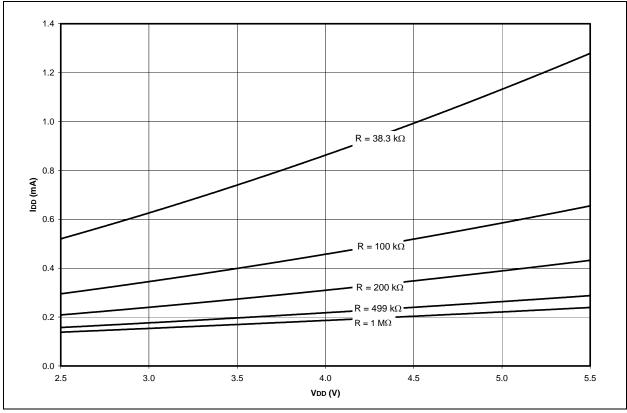

### 12.2.4 ER MODE

For timing insensitive applications, the ER (External Resistor) Clock mode offers additional cost savings. Only one external component, a resistor connected to the OSC1 pin and Vss, is needed to set the operating frequency of the internal oscillator. The resistor draws a DC bias current which controls the oscillation frequency. In addition to the resistance value, the oscillator frequency will vary from unit to unit, and as a function of supply voltage and temperature. Since the controlling parameter is a DC current and not a capacitance, the particular package type and lead frame will not have a significant effect on the resultant frequency.

Figure 12-3 shows how the controlling resistor is connected to the PIC16C717/770/771. For REXT values below 38 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g. 1M), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 38 k $\Omega$  and 1 M $\Omega$ .

### FIGURE 12-3: EXTERNAL RESISTOR

The Electrical Specification section shows the relationship between the REXT resistance value and the operating frequency as well as frequency variations due to operating temperature for given REXT and VDD values.

The ER Oscillator mode has two options that control the OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as CLK-OUT. The ER oscillator does not run during RESET.

### 12.2.5 INTRC MODE

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature. The INTRC oscillator does not run during RESET.

### 12.2.6 CLKOUT

In the INTRC and ER modes, the PIC16C717/770/771 can be configured to provide a clock out signal by programming the configuration word. The oscillator frequency, divided by 4, can be used for test purposes or to synchronize other logic.

In the INTRC and ER modes, if the CLKOUT output is enabled, CLKOUT is held low during RESET.

### 12.2.7 DUAL SPEED OPERATION FOR ER AND INTRC MODES

A software programmable dual speed oscillator is available in either ER or INTRC Oscillator modes. This feature allows the applications to dynamically toggle the oscillator speed between normal and slow frequencies. The nominal slow frequency is 37 kHz. In ER mode, the slow speed operation is fixed and does not vary with resistor size. Applications that require low current power savings, but cannot tolerate putting the part into SLEEP, may use this mode.

The OSCF bit in the PCON register is used to control Dual Speed mode. See the PCON Register, Register 2-8, for details.

When changing the INTRC or ER internal oscillator speed, there is a period of time when the processor is inactive. When the speed changes from fast to slow, the processor inactive period is in the range of 100  $\mu$ S to 300  $\mu$ S. For speed change from slow to fast, the processor is in active for 1.25  $\mu$ S to 3.25  $\mu$ S.

| COMF             | Complement f                                                                                                                                            |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two<br>cycle instruction. |  |  |  |  |  |

| DECF             | Decrement f                                                                                                                                     |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                       |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                     |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             |  |  |  |

| Status Affected: | Z                                                                                                                                               |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |

| INCF             | Increment f                                                                                                                                                              |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                          |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                      |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                        |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'. |  |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                        | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                            | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                               | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                          |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                    | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                          | Status Affected: | None                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>then a NOP is executed instead<br>making it a 2Tcy instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in regis-<br>ter 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead making<br>it a 2TCY instruction. |  |  |  |  |

# TABLE 15-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC16C717/770/771 AND PIC16LC717/770/771

| AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended<br>Operating Voltage VDD range is described in Section and Section |      |                                  |      |                     | tion |       |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|------|---------------------|------|-------|------------|

| Parameter<br>No.                                                                                                                                                                                                                                                                                                                              | Sym  | Characteristic                   | Min  | Тур <sup>(1)*</sup> | Max  | Units | Conditions |

| FIRC                                                                                                                                                                                                                                                                                                                                          |      | Internal Calibrated RC Frequency | 3.65 | 4.00                | 4.28 | MHz   | VDD = 5.0V |

|                                                                                                                                                                                                                                                                                                                                               | TIRC | Internal RC Frequency*           | 3.55 | 4.00                | 4.31 | MHz   | VDD = 2.5V |

These parameters are characterized but not tested.

\*

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

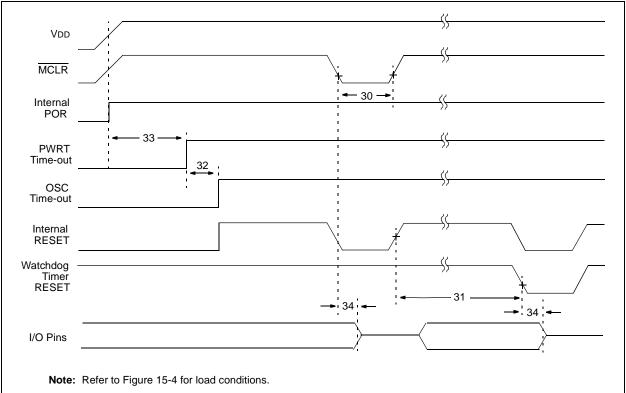

# FIGURE 15-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

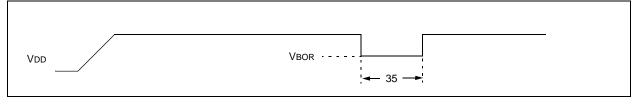

### FIGURE 15-8: BROWN-OUT RESET TIMING

### FIGURE 15-21: SPI SLAVE MODE TIMING (CKE = 1)

# TABLE 15-20: SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                                  | Characteristic                                                                           |                    | Min          | Тур† | Max | Units | Conditions |

|---------------|-----------------------------------------|------------------------------------------------------------------------------------------|--------------------|--------------|------|-----|-------|------------|

| 70*           | TssL2scH,<br>TssL2scL                   | $\overline{\text{SS}}\downarrow$ to $\text{SCK}\downarrow$ or $\text{SCK}\uparrow$ input |                    | Тсү          | —    |     | ns    |            |

| 71*           | TscH                                    | SCK input high time                                                                      | Continuous         | 1.25Tcy + 30 | —    | _   | ns    |            |

| 71A*          |                                         | (Slave mode)                                                                             | Single Byte        | 40           | —    | _   | ns    | Note 1     |

| 72*           | TscL                                    | SCK input low time                                                                       | Continuous         | 1.25Tcy + 30 | —    | _   | ns    |            |

| 72A*          |                                         | (Slave mode)                                                                             | Single Byte        | 40           | —    |     | ns    | Note 1     |

| 73A*          | Тв2в                                    | Last clock edge of Byte1 to the 1st clock<br>edge of Byte2                               |                    | 1.5Tcy + 40  | -    | —   | ns    | Note 1     |

| 74*           | TscH2diL,<br>TscL2diL                   | Hold time of SDI data input to SCK edge                                                  |                    | 100          | -    | —   | ns    |            |

| 75*           | TdoR                                    | SDO data output rise time                                                                | PIC16 <b>C</b> XXX | _            | 10   | 25  | ns    |            |

|               |                                         |                                                                                          | PIC16LCXXX         |              | 20   | 45  | ns    |            |

| 76*           | TdoF                                    | SDO data output fall time                                                                |                    | _            | 10   | 25  | ns    |            |

| 77*           | TssH2doZ                                | SS↑ to SDO output hi-impedance                                                           |                    | 10           | —    | 50  | ns    |            |

| 78* TscR      | SCK output rise time (Mas-<br>ter mode) | PIC16 <b>C</b> XXX                                                                       | _                  | 10           | 25   | ns  |       |            |

|               |                                         | PIC16LCXXX                                                                               | _                  | 20           | 45   | ns  |       |            |

| 79*           | TscF                                    | SCK output fall time (Master mode)                                                       |                    | _            | 10   | 25  | ns    |            |

| 80*           | TscH2doV,                               | ,                                                                                        | PIC16 <b>C</b> XXX | _            | _    | 50  | ns    |            |

| TscL2doV      | TscL2doV                                |                                                                                          | PIC16LCXXX         | _            | —    | 100 | ns    |            |

| 82*           | 82* TssL2doV                            |                                                                                          | PIC16CXXX          | _            | _    | 50  | ns    |            |

|               |                                         | SS↓ edge                                                                                 | PIC16LCXXX         | _            | _    | 100 | ns    |            |

| 83*           | TscH2ssH,<br>TscL2ssH                   | $\overline{\text{SS}}$ $\uparrow$ after SCK edge                                         |                    | 1.5Tcy + 40  | _    |     | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

# PIC16C717/770/771

FIGURE 16-11: TYPICAL Fosc VS. VDD (ER MODE)