Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc770t-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name              | Function | Input<br>Type | Output<br>Type | Description                                 |

|-------------------|----------|---------------|----------------|---------------------------------------------|

| 546/4446          | RA0      | ST            | CMOS           | Bi-directional I/O                          |

| RA0/AN0           | AN0      | AN            |                | A/D input                                   |

|                   | RA1      | ST            | CMOS           | Bi-directional I/O                          |

| RA1/AN1/LVDIN     | AN1      | AN            |                | A/D input                                   |

|                   | LVDIN    | AN            |                | LVD input reference                         |

|                   | RA2      | ST            | CMOS           | Bi-directional I/O                          |

|                   | AN2      | AN            |                | A/D input                                   |

| RA2/AN2/VREF-/VRL | VREF-    | AN            |                | Negative analog reference input             |

|                   | VRL      |               | AN             | Internal voltage reference low output       |

|                   | RA3      | ST            | CMOS           | Bi-directional I/O                          |

|                   | AN3      | AN            |                | A/D input                                   |

| RA3/AN3/VREF+/VRH | VREF+    | AN            |                | Positive analog reference input             |

|                   | VRH      |               | AN             | Internal voltage reference high output      |

|                   | RA4      | ST            | OD             | Bi-directional I/O                          |

| RA4/T0CKI         | T0CKI    | ST            |                | TMR0 clock input                            |

|                   | RA5      | ST            |                | Input port                                  |

| RA5/MCLR/VPP      | MCLR     | ST            |                | Master clear                                |

|                   | Vpp      | Power         |                | Programming voltage                         |

|                   | RA6      | ST            | CMOS           | Bi-directional I/O                          |

| RA6/OSC2/CLKOUT   | OSC2     |               | XTAL           | Crystal/resonator                           |

|                   | CLKOUT   |               | CMOS           | Fosc/4 output                               |

|                   | RA7      | ST            | CMOS           | Bi-directional I/O                          |

| RA7/OSC1/CLKIN    | OSC1     | XTAL          |                | Crystal/resonator                           |

|                   | CLKIN    | ST            |                | External clock input/ER resistor connection |

|                   | RB0      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB0/AN4/INT       | AN4      | AN            |                | A/D input                                   |

|                   | INT      | ST            |                | Interrupt input                             |

|                   | RB1      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB1/AN5/SS        | AN5      | AN            |                | A/D input                                   |

|                   | SS       | ST            |                | SSP slave select input                      |

|                   | RB2      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB2/SCK/SCL       | SCK      | ST            | CMOS           | Serial clock I/O for SPI                    |

|                   | SCL      | ST            | OD             | Serial clock I/O for I <sup>2</sup> C       |

|                   | RB3      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB3/CCP1/P1A      | CCP1     | ST            | CMOS           | Capture 1 input/Compare 1 output            |

|                   | P1A      | -             | CMOS           | PWM P1A output                              |

|                   | RB4      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB4/SDI/SDA       | SDI      | ST            |                | Serial data in for SPI                      |

|                   | SDA      | ST            | OD             | Serial data I/O for I <sup>2</sup> C        |

|                   | RB5      | TTL           | CMOS           | Bi-directional I/O <sup>(1)</sup>           |

| RB5/SDO/P1B       | SDO      |               | CMOS           | Serial data out for SPI                     |

|                   | P1B      |               | CMOS           | PWM P1B output                              |

TABLE 1-1: PIC16C717/770/771 PINOUT DESCRIPTION

Note 1: Bit programmable pull-ups.

2: Only in PIC16C770/771 devices.

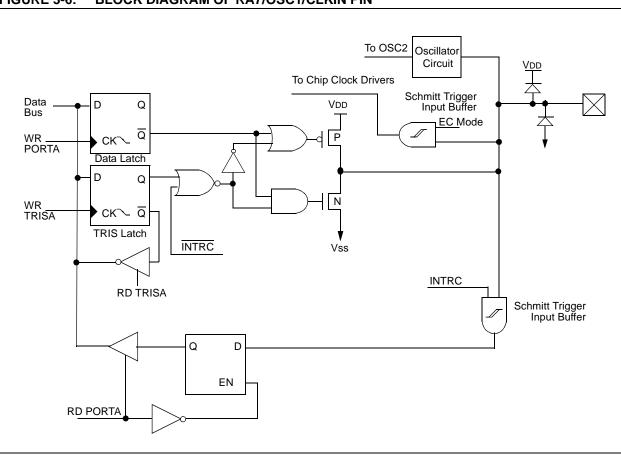

FIGURE 3-6: BLOCK DIAGRAM OF RA7/OSC1/CLKIN PIN

## 6.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- RESET from ECCP module trigger

Timer1 has a control register, shown in Register 6-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 6-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

## 6.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- · As a synchronous counter

- · As an asynchronous counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     |     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                            |

| bit 3   | <b>T1OSCEN:</b> Timer1 Oscillator Enable Control bit<br>1 = Oscillator is enabled<br>0 = Oscillator is shut off <sup>(1)</sup>                                                                                                           |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bitTMR1CS = 1:1 = Do not synchronize external clock input0 = Synchronize external clock inputTMR1CS = 0:This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. |

| bit 1   | <b>TMR1CS:</b> Timer1 Clock Source Select bit<br>1 = External clock from pin RB6/T1OSO/T1CKI /P1C (on the rising edge)<br>0 = Internal clock (Fosc/4)                                                                                    |

| bit 0   | TMR1ON: Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1                                                                                                                                                                          |

Note 1: The oscillator inverter and feedback resistor are turned off to eliminate power drain.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 6-1: TIMER1 CONTROL REGISTER (T1CON: 10h)

## 7.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (Both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register, shown in Register 7-1. Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 7-1 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC Mid-Range MCU Family Reference Manual, (DS33023).

## 7.1 Timer2 Operation

Timer2 can be used as the PWM time-base for PWM mode of the ECCP module.

The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS<1:0> (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### REGISTER 7-1: TIMER2 CONTROL REGISTER (T2CON1: 12h)

|         | U-0               | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0       | R/W-0        | R/W-0   |

|---------|-------------------|---------------|--------------|--------------|-------------|-------------|--------------|---------|

|         | _                 | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON      | T2CKPS1      | T2CKPS0 |

|         | bit 7             |               |              |              |             |             |              | bit 0   |

|         |                   |               |              |              |             |             |              |         |

| bit 7   | Unimplen          | nented: Read  | d as '0'     |              |             |             |              |         |

| bit 6-3 | TOUTPS<           | :3:0>: Timer2 | 2 Output Pos | stscale Sele | ct bits     |             |              |         |

|         |                   | 1 Postscale   |              |              |             |             |              |         |

|         | 0001 = 1:         | 2 Postscale   |              |              |             |             |              |         |

|         | •                 |               |              |              |             |             |              |         |

|         | •                 |               |              |              |             |             |              |         |

|         | 1111 <b>= 1</b> : | 16 Postscale  |              |              |             |             |              |         |

| bit 2   | TMR2ON:           | Timer2 On b   | oit          |              |             |             |              |         |

|         | 1 = Timer2        | 2 is on       |              |              |             |             |              |         |

|         | 0 = Timer2        | 2 is off      |              |              |             |             |              |         |

| bit 1-0 | T2CKPS<           | 1:0>: Timer2  | 2 Clock Pres | cale Select  | bits        |             |              |         |

|         | 00 = Pres         |               |              |              |             |             |              |         |

|         | 01 = Pres         |               |              |              |             |             |              |         |

|         | TY - 1162         |               |              |              |             |             |              |         |

|         | Legend:           |               |              |              |             |             |              |         |

|         | R = Reada         | ahle hit      | M = M        | ritable bit  | II – I Inim | nlemented I | bit, read as | 0'      |

|         |                   |               |              |              |             |             |              |         |

|         | - n = Value       | e at POR      | ΄1΄ = Β      | it is set    | 0' = Bit is | cleared     | x = Bit is u | nknown  |

#### TABLE 8-1: ECCP MODE - TIMER RESOURCE

| ECCP Mode | Timer Resource |

|-----------|----------------|

| Capture   | Timer1         |

| Compare   | Timer1         |

| PWM       | Timer2         |

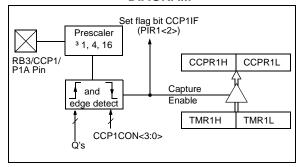

## 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 8.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1/P1A pin is configured as   |

|-------|--------------------------------------------|

|       | an output, a write to the port can cause a |

|       | capture condition.                         |

### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 8.1.4 ECCP PRESCALER

There are three prescaler settings, specified by bits CCP1M<3:0>. Whenever the ECCP module is turned off or the ECCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: Changing Between Capture Prescalers

| CLRF  | CCP1CON     | ; | Turn ECCP module off |

|-------|-------------|---|----------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the   |

|       |             | ; | new prescaler mode   |

|       |             | ; | value and ECCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with    |

|       |             | ; | this value           |

### FIGURE 8-1:

#### CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- driven High

- driven Low

- toggle output (High to Low or Low to High)

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M<3:0>. At the same time, interrupt flag bit CCP1IF is set.

Changing the ECCP mode select bits to the clear output on Match mode (CCP1M<3.0> = "1000") presets the CCP1 output latch to the logic 1 level. Changing the ECCP mode select bits to the clear output on Match mode (CCP1M<3:0> = "1001") presets the CCP1 output latch to the logic 0 level.

#### 8.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRISB bit.

Note: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the port data latch.

### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the ECCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work. In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, RB3/CCP1/P1A pin is continuously active, and RB7/T1OSI/P1D pin is modulated. In the Reverse mode, RB6/T1OSO/T1CKI/P1C pin is continuously active, and RB5/SDO/P1B pin is modulated.

P1A, P1B, P1C and P1D outputs are multiplexed with PORTB<3> and PORTB<5:7> data latches. TRISB<3> and TRISB<5:7> bits must be cleared to make the P1A, P1B, P1C, and P1D pins output.

#### 8.3.5 PROGRAMMABLE DEADBAND DELAY

In half-bridge or full-bridge applications, driven by halfbridge outputs (see Figure 8-7), the power switches normally require longer time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches will be on for a short period of time, until one switch completely turns off. During this time, a very high current, called shootthrough current, will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on the power switch is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable deadband delay is available to avoid shootthrough current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 8-6 for illustration. The P1DEL register sets the amount of delay.

## REGISTER 8-2: PWM DELAY REGISTER (P1DEL: 97H)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| P1DEL7 | P1DEL6 | P1DEL5 | P1DEL4 | P1DEL3 | P1DEL2 | P1DEL1 | P1DEL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

## bit 7-0 **P1DEL<7:0>: PWM Delay Count for Half-Bridge Output Mode:** Number of Fosc/4 (Tosc•4) cycles between the P1A transition and the P1B transition.

| Legend:            |                  |                                           |

|--------------------|------------------|-------------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'        |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared $x = Bit$ is unknown |

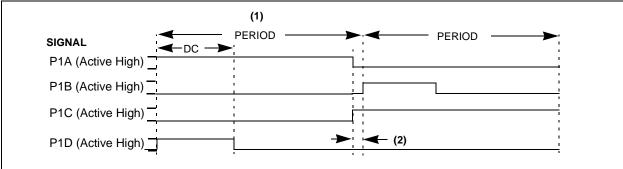

#### 8.3.6 DIRECTION CHANGE IN FULL-BRIDGE OUTPUT MODE

In the Full-Bridge Output mode, the PWM1M1 bit in the CCP1CON register allows user to control the Forward/ Reverse direction. When the application firmware changes this direction control bit, the ECCP module will assume the new direction on the next PWM cycle. The current PWM cycle still continues, however, the nonmodulated outputs, P1A and P1C signals, will transition to the new direction TOSC,  $4 \cdot TOSC$  or  $16 \cdot TOSC$  (for Timer2 prescale T2CKRS<1:0> = 00, 01 and 1x respectively) earlier, before the end of the period. During this transition cycle, the modulated outputs, P1B and P1D, will go to the inactive state. See Figure 8-10 for illustration.

Note 1: The Direction bit in the ECCP Control Register (CCP1CON<PWM1M1>) is written anytime during the PWM cycle.

2: The P1A and P1C signals switch Tosc, 4\*Tosc or 16\*Tosc, depending on the Timer2 prescaler value, earlier when changing direction. The modulated P1B and P1D signals are inactive at this time.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit, BF (SSPSTAT<0>), indicates when the SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the MSSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 9-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

## EXAMPLE 9-1: Loading the SSPBUF (SSPSR) Register

|      |       |             | , 0               |

|------|-------|-------------|-------------------|

|      | BSF   | STATUS, RPO | ;Specify Bank 1   |

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been    |

|      |       |             | ;received         |

|      |       |             | ;(xmit complete)? |

|      | GOTO  | LOOP        | ;No               |

|      | BCF   | STATUS, RPO | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, W   | ;Save SSPBUF      |

|      | MOVWF | RXDATA      | ;in user RAM      |

|      | MOVF  | TXDATA, W   | ;Get next TXDATA  |

|      | MOVWF | SSPBUF      | ;New data to xmit |

|      |       |             |                   |

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP STATUS register (SSPSTAT) indicates the various status conditions.

## 9.1.2 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISB<5> cleared

- SCK (Master mode) must have TRISB<2> cleared

- SCK (Slave mode) must have TRISB<2> set

- SS must have TRISB<1> set, and ANSEL<5> cleared

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

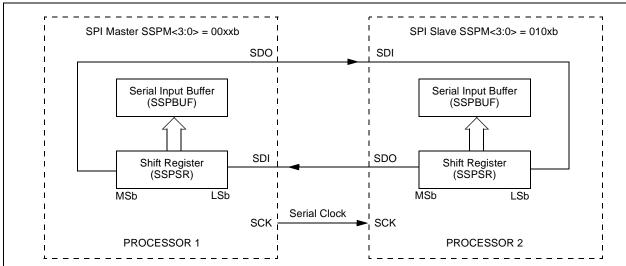

## 9.1.3 TYPICAL CONNECTION

Figure 9-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (SSPCON<4>), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

## FIGURE 9-2: SPI MASTER/SLAVE CONNECTION

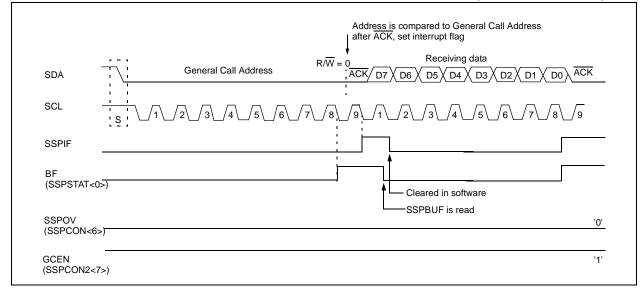

#### 9.2.3 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is set (SSPCON2<7> is set). Following a START bit detect, eight bits are shifted into the SSPSR, and the address is compared against SSPADD. It is also compared to the general call address, fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

If the general call address is sampled with GCEN set and the slave configured in 10-bit Address mode, the second half of the address is not necessary. The UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 9-12).

#### FIGURE 9-12: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7- OR 10-BIT MODE)

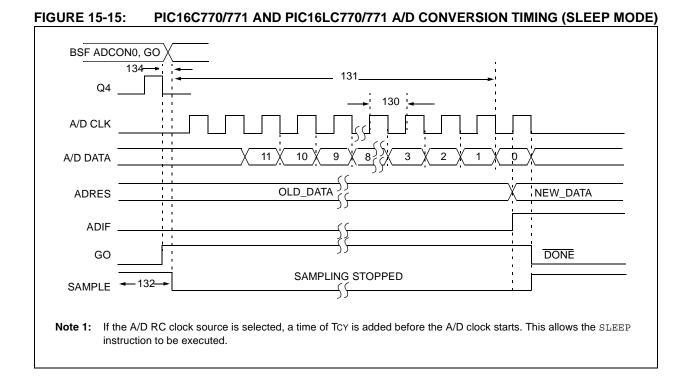

## 11.10 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be configured for RC (ADCS<1:0> = 11b). With the RC clock source selected, when the GO/DONE bit is set the A/D module waits one instruction cycle before starting the conversion cycle. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise during the sample and conversion. When the conversion cycle is completed the GO/DONE bit is cleared, and the result loaded into the ADRESH and ADRESL registers. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction causes the present conversion to be aborted and the A/D module is turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,    |

|-------|--------------------------------------------|

|       | the A/D clock source must be configured to |

|       | RC (ADCS<1:0> = 11).                       |

## **11.11** Connection Considerations

Since the analog inputs employ ESD protection, they have diodes to VDD and VSS. This requires that the analog input must be between VDD and VSS. If the input voltage exceeds this range by greater than 0.3V (either direction), one of the diodes becomes forward biased and it may damage the device if the input current specification is exceeded.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 2.5 k $\Omega$  recommended specification. It is recommended that any external components connected to an analog input pin (capacitor, zener diode, etc.) have very little leakage current.

| Address               | Name    | Bit 7                         | Bit 6                                               | Bit 5        | Bit 4       | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|---------|-------------------------------|-----------------------------------------------------|--------------|-------------|------------|---------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                           | PEIE                                                | TOIE         | INTE        | RBIE       | T0IF    | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | _                             | ADIF                                                | _            | _           | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | -0 0000                  | -0 0000                         |

| 8Ch                   | PIE1    | _                             | ADIE                                                | _            | _           | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | -0 0000                  | -0 0000                         |

| 1Eh                   | ADRESH  | A/D High I                    | Byte Resu                                           | lt Register  |             |            |         |        |        | xxxx xxxx                | uuuu uuuu                       |

| 9Eh                   | ADRESL  | A/D Low E                     | Byte Resul                                          | t Register   |             |            |         |        |        | xxxx xxxx                | uuuu uuuu                       |

| 9Bh                   | REFCON  | VRHEN                         | VRLEN                                               | VRHOEN       | VRLOEN      |            | _       |        |        | 0000                     | 0000                            |

| 1Fh                   | ADCON0  | ADCS1                         | ADCS0                                               | CHS2         | CHS1        | CHS0       | GO/DONE | CHS3   | ADON   | 0000 0000                | 0000 0000                       |

| 9Fh                   | ADCON1  | ADFM                          | VCFG2                                               | VCFG1        | VCFG0       |            | _       |        |        | 0000                     | 0000                            |

| 05h                   | PORTA   | PORTA D                       | ata Latch v                                         | when written | : PORTA pir | ns when re | ad      |        |        | 000x 0000                | 000u 0000                       |

| 06h                   | PORTB   | PORTB D                       | PORTB Data Latch when written: PORTB pins when read |              |             |            |         |        |        | xxxx xx11                | uuuu uu11                       |

| 85h                   | TRISA   | PORTA Data Direction Register |                                                     |              |             |            |         |        |        | 1111 1111                | 1111 1111                       |

| 86h                   | TRISB   | PORTB D                       | PORTB Data Direction Register                       |              |             |            |         |        |        |                          | 1111 1111                       |

| 9Dh                   | ANSEL   | _                             | _                                                   | ANS5         | ANS4        | ANS3       | ANS2    | ANS1   | ANS0   | 1111 1111                | 1111 1111                       |

| 17h                   | CCP1CON | _                             | _                                                   | _            | _           |            |         |        |        | 0000 0000                | 0000 0000                       |

TABLE 11-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

## 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked by the POR pulse. When the PWRT delay expires, the Oscillator Start-up Timer is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 12-6, Figure 12-7, Figure 12-8 and Figure 12-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 12-8). This is useful for testing purposes or to synchronize more than one PIC<sup>®</sup> microcontroller operating in parallel.

Table 12-5 shows the RESET conditions for some special function registers, while Table 12-6 shows the RESET conditions for all the registers.

#### 12.9 Power Control/STATUS Register (PCON)

The Power Control/STATUS Register, PCON, has two status bits that provide indication of which power-up type RESET occurred.

Bit0 is Brown-out Reset Status bit, BOR. The BOR bit is unknown upon a POR. BOR must be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from<br>SLEEP |  |

|--------------------------|------------------|-----------|------------------|-----------------------|--|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                       |  |

| XT, HS, LP               | TPWRT + 1024Tosc | 1024Tosc  | TPWRT + 1024Tosc | 1024Tosc              |  |

| EC, ER, INTRC            | TPWRT            | _         | TPWRT            | —                     |  |

### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |

|---------------------------------------|--------------------|--------------------|------------------|

| Power-on Reset                        | 000h               | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 1-uu             |

| WDT Reset                             | 000h               | 0000 luuu          | 1-uu             |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | u-uu             |

| Brown-out Reset                       | 000h               | 0001 luuu          | 1-u0             |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuul Ouuu          | u-uu             |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                                   |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                         |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                         |  |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| SWAPF            | Swap Nybbles in f                                                                                                                                                            |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                            |  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                      |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                         |  |  |  |  |  |  |

| Description:     | The upper and lower nybbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in W regis-<br>ter. If 'd' is 1, the result is placed in<br>register 'f'. |  |  |  |  |  |  |

#### TABLE 15-13: PIC16C770/771 AND PIC16LC770/771 A/D CONVERSION REQUIREMENT (SLEEP MODE)

| Parameter<br>No.    | Sym  | Characteristic                                            | Min      | Тур†         | Max | Units | Conditions                                                                                                                                                                                                               |

|---------------------|------|-----------------------------------------------------------|----------|--------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D Internal RC oscillator period                         | 3.0      | 6.0          | 9.0 | μs    | ADCS<1:0> = 11 (RC mode)<br>At VDD= 3.0V                                                                                                                                                                                 |

|                     |      |                                                           | 2.0      | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                                            |

| 131*                | TCNV | Conversion time (not including acquisition time) (Note 1) | _        | 13Tad        |     | —     |                                                                                                                                                                                                                          |

| 132*                | TACQ | Acquisition Time                                          | (Note 2) | 11.5         | _   | μs    |                                                                                                                                                                                                                          |

|                     |      |                                                           | 5*       | _            | _   | μS    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1LSb (i.e.,<br>1mV @ 4.096V) from the last sam-<br>pled voltage (as stated on CHOLD). |

| 134*                | TGO  | Q4 to A/D clock start                                     | _        | Tosc/2 + Tcy | _   | _     | If the A/D clock source is selected<br>as RC, a time of TcY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                             |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 11.6 for minimum conditions.

3: These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

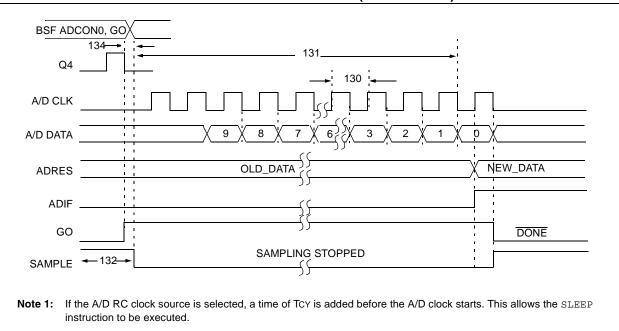

#### FIGURE 15-17: PIC16C717 A/D CONVERSION TIMING (SLEEP MODE)

#### TABLE 15-16: PIC16C717 AND PIC16LC717 A/D CONVERSION REQUIREMENT (SLEEP MODE)

| Parameter<br>No.    | Sym  | Characteristic                                            | Min      | Тур†         | Max | Units | Conditions                                                                                                                                                                                                               |

|---------------------|------|-----------------------------------------------------------|----------|--------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D clock period                                          | 3.0      | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (A/D RC mode)<br>At VDD = 3.0V                                                                                                                                                                            |

|                     |      |                                                           | 2.0      | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                                            |

| 131*                | ΤΟΝΥ | Conversion time (not including acquisition time) (Note 1) | _        | 11Tad        | _   | _     |                                                                                                                                                                                                                          |

| 132*                | TACQ | Acquisition Time                                          | (Note 2) | 11.5         | _   | μs    |                                                                                                                                                                                                                          |

|                     |      |                                                           | 5*       | _            | _   | μS    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1LSb (i.e.,<br>1mV @ 4.096V) from the last sam-<br>pled voltage (as stated on CHOLD). |

| 134*                | TGO  | Q4 to A/D clock start                                     |          | Tosc/2 + Tcy |     | _     | If the A/D RC clock source is<br>selected, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 11.6 for minimum conditions.

3: These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

© 1999-2013 Microchip Technology Inc.

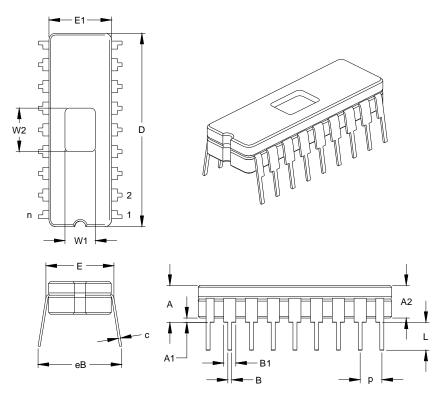

#### 18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP) 17.3

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  |      | INCHES* |      | MILLIMETERS |       |       |

|----------------------------|--------|------|---------|------|-------------|-------|-------|

| Dimension                  | Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n      |      | 18      |      |             | 18    |       |

| Pitch                      | р      |      | .100    |      |             | 2.54  |       |

| Top to Seating Plane       | Α      | .170 | .183    | .195 | 4.32        | 4.64  | 4.95  |

| Ceramic Package Height     | A2     | .155 | .160    | .165 | 3.94        | 4.06  | 4.19  |

| Standoff                   | A1     | .015 | .023    | .030 | 0.38        | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е      | .300 | .313    | .325 | 7.62        | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1     | .285 | .290    | .295 | 7.24        | 7.37  | 7.49  |

| Overall Length             | D      | .880 | .900    | .920 | 22.35       | 22.86 | 23.37 |

| Tip to Seating Plane       | L      | .125 | .138    | .150 | 3.18        | 3.49  | 3.81  |

| Lead Thickness             | С      | .008 | .010    | .012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width           | B1     | .050 | .055    | .060 | 1.27        | 1.40  | 1.52  |

| Lower Lead Width           | В      | .016 | .019    | .021 | 0.41        | 0.47  | 0.53  |

| Overall Row Spacing        | eB     | .345 | .385    | .425 | 8.76        | 9.78  | 10.80 |

| Window Width               | W1     | .130 | .140    | .150 | 3.30        | 3.56  | 3.81  |

| Window Length              | W2     | .190 | .200    | .210 | 4.83        | 5.08  | 5.33  |

\*Controlling Parameter JEDEC Equivalent: MO-036 Drawing No. C04-010

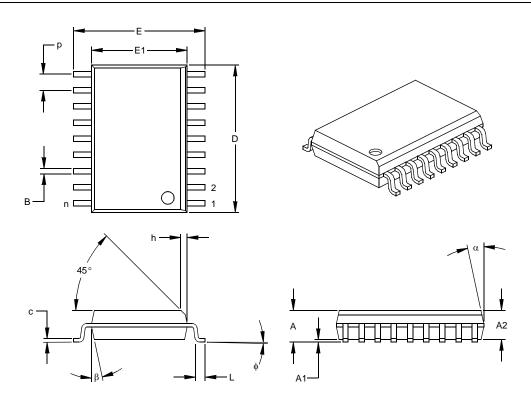

## 17.4 18-Lead Plastic Small Outline (SO) – Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |      | INCHES* |      | MILLIMETERS |       |       |

|--------------------------|-----------|------|---------|------|-------------|-------|-------|

| Dimensio                 | on Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n         |      | 18      |      |             | 18    |       |

| Pitch                    | р         |      | .050    |      |             | 1.27  |       |

| Overall Height           | Α         | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2        | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1        | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | Е         | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1        | .291 | .295    | .299 | 7.39        | 7.49  | 7.59  |

| Overall Length           | D         | .446 | .454    | .462 | 11.33       | 11.53 | 11.73 |

| Chamfer Distance         | h         | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L         | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle               | ф         | 0    | 4       | 8    | 0           | 4     | 8     |

| Lead Thickness           | С         | .009 | .011    | .012 | 0.23        | 0.27  | 0.30  |

| Lead Width               | В         | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α         | 0    | 12      | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β         | 0    | 12      | 15   | 0           | 12    | 15    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

NOTES:

NOTES: