Welcome to E-XFL.COM

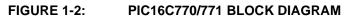

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc771-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the SSP bus collision and low voltage detect interrupts.

# REGISTER 2-6: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (PIE2: 8Dh)

|         | R/W-0       | U-0                           | U-0           | U-0           | R/W-0        | U-0       | U-0          | U-0    |  |  |  |  |  |

|---------|-------------|-------------------------------|---------------|---------------|--------------|-----------|--------------|--------|--|--|--|--|--|

|         | LVDIE       |                               | —             | —             | BCLIE        | _         | —            |        |  |  |  |  |  |

|         | bit 7       |                               |               |               |              |           |              | bit 0  |  |  |  |  |  |

|         |             |                               |               |               |              |           |              |        |  |  |  |  |  |

| bit 7   | LVDIE: Lov  | v Voltage De                  | etect Interru | ot Enable bit |              |           |              |        |  |  |  |  |  |

|         |             | 1 = LVD Interrupt is enabled  |               |               |              |           |              |        |  |  |  |  |  |

|         |             | 0 = LVD Interrupt is disabled |               |               |              |           |              |        |  |  |  |  |  |

| bit 6-4 | Unimpleme   | Unimplemented: Read as '0'    |               |               |              |           |              |        |  |  |  |  |  |

| bit 3   | BCLIE: Bus  | s Collision Ir                | nterrupt Ena  | ble bit       |              |           |              |        |  |  |  |  |  |

|         | 1 = Bus Co  | llision interr                | upt is enable | ed            |              |           |              |        |  |  |  |  |  |

|         | 0 = Bus Co  | llision interr                | upt is disabl | ed            |              |           |              |        |  |  |  |  |  |

| bit 2-0 | Unimpleme   | ented: Read                   | d as '0'      |               |              |           |              |        |  |  |  |  |  |

|         |             |                               |               |               |              |           |              |        |  |  |  |  |  |

|         | Legend:     |                               |               |               |              |           |              |        |  |  |  |  |  |

|         | R = Readal  | ole bit                       | W = W         | ritable bit   | U = Unim     | plemented | bit, read as | 0'     |  |  |  |  |  |

|         | - n = Value | at POR                        | '1' = Bi      | t is set      | '0' = Bit is | s cleared | x = Bit is u | nknown |  |  |  |  |  |

#### TABLE 4-1: PROGRAM MEMORY READ REGISTER SUMMARY

| Address | Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|----------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 18Ch    | PMCON1 | Reserved | _     | _     | _     | _     | —     |       | RD    | 1 0                      | 10                              |

| 10Eh    | PMDATH | _        | _     | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  | xx xxxx                  | uu uuuu                         |

| 10Ch    | PMDATL | PMD7     | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH | _        | _     | —     | _     | PMA11 | PMA10 | PMA9  | PMA8  | xxxx                     | uuuu                            |

| 10Dh    | PMADRL | PMA7     | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  | XXXX XXXX                | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Program Memory Read.

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

#### 9.2.4 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C slave module can receive addresses or data. When an address match or complete byte transfer occurs, it wakes the processor from SLEEP (if the SSP interrupt bit is enabled).

#### 9.2.5 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

### 9.2.6 MASTER MODE

Master mode operation supports interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is idle with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit (SSPIF) to be set (SSP Interrupt, if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

#### SSPM<3:0>, Internal Data Bus SSPADD<6:0> Read Write SSPBUF Baud Rate Generator SDA Shift clock arbitrate/WCOL detect SDA in Clock $\ge$ SSPSR (hold off clock source) MSb LSb Enable START bit, STOP bit cntl Receive Acknowledge Generate clock SCL START bit detect, STOP bit detect SCL in Set/RESET, S, P, WCOL (SSPSTAT) Vrite collision detect **Clock Arbitration** Set SSPIF. BCLIF State counter for **Bus Collision** RESET ACKSTAT, PEN (SSPCON2) end of XMIT/RCV

# FIGURE 9-13: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

### 9.2.7 MULTI-MASTER OPERATION

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

Refer to Application Note AN578, "Use of the SSP Module in the  $l^2C^{TM}$  Multi-Master Environment."

### 9.2.8 I<sup>2</sup>C MASTER OPERATION

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once Master mode is enabled, the user has six options.

- 1. Assert a START condition on SDA and SCL.

- 2. Assert a Repeated START condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Generate a STOP condition on SDA and SCL.

- 5. Configure the I<sup>2</sup>C port to receive data.

- 6. Generate an Acknowledge condition at the end of a received byte of data.

The master device generates all serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $I^2C$  bus will not be released.

| Note: | The MSSP Module, when configured in I <sup>2</sup> C |

|-------|------------------------------------------------------|

|       | Master mode, does not allow queueing of              |

|       | events. For instance, the user is not                |

|       | allowed to initiate a START condition and            |

|       | immediately write the SSPBUF register to             |

|       | initiate transmission before the START               |

|       | condition is complete. In this case, the             |

|       | SSPBUF will not be written to, and the               |

|       | WCOL bit will be set, indicating that a write        |

|       | to the SSPBUF did not occur.                         |

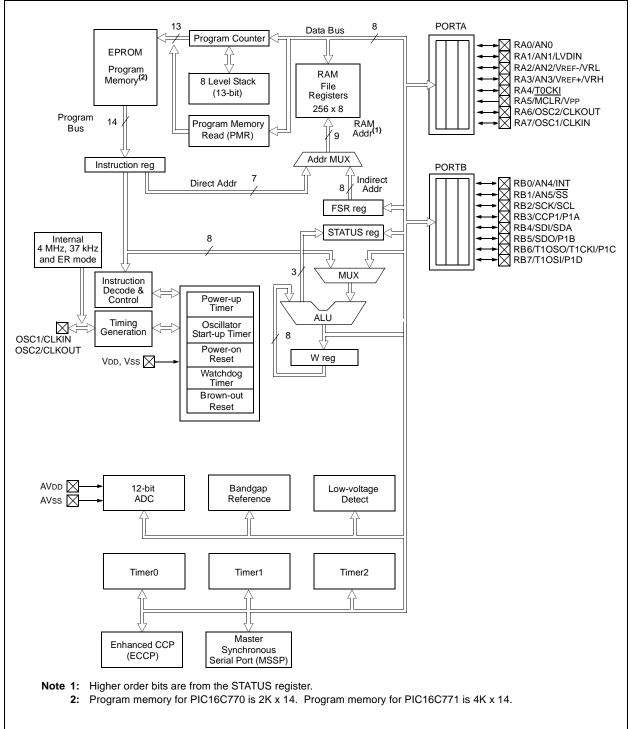

#### 9.2.9 BAUD RATE GENERATOR

The baud rate generator used for SPI mode operation is used in the I<sup>2</sup>C Master mode to set the SCL clock frequency. Standard SCL clock frequencies are 100 kHz, 400 kHz, and 1 MHz. One of these frequencies can be achieved by setting the SSPADD register to the appropriate number for the selected Fosc frequency. One half of the SCL period is equal to [(SSPADD+1)  $\bullet$ 2]/Fosc.

The baud rate generator reload value is contained in the lower seven bits of the SSPADD register (Figure 9-14). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload occurs. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clock.

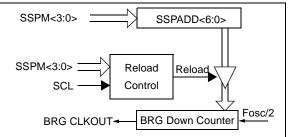

In I<sup>2</sup>C Master mode, the BRG is reloaded automatically provided that the SCL line is sampled high. For example, if Clock Arbitration is taking place, the BRG reload will be suppressed until the SCL line is released by the slave allowing the pin to float high (Figure 9-15).

FIGURE 9-14:

#### BAUD RATE GENERATOR BLOCK DIAGRAM

#### 9.2.16 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the

SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 9-22).

#### FIGURE 9-22: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has six inputs for the PIC16C717/770/771.

The PIC16C717 analog-to-digital converter (A/D) allows conversion of an analog input signal to a corresponding 10-bit digital value, while the A/D converter in the PIC16C770/771 allows conversion to a corresponding 12-bit digital value. The A/D module has up to 6 analog inputs, which are multiplexed into one sample and hold. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltages are software selectable to either the device's analog positive and negative supply voltages (AVDD/AVSS), the voltage level on the VREF+ and VREF- pins, or internal voltage references if enabled (VRH, VRL).

The A/D converter can be triggered by setting the GO/ DONE bit, or by the special event Compare mode of the ECCP module. When conversion is complete, the GO/DONE bit returns to '0', the ADIF bit in the PIR1 register is set, and an A/D interrupt will occur, if enabled.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result Register Low ADRESL

- A/D Result Register High ADRESH

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

# 11.1 Control Registers

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins, the voltage reference configuration and the result format. The ANSEL register, shown in Register 3-1, selects between the Analog or Digital Port Pin modes. The port pins can be configured as analog inputs or as digital I/O.

The combination of the ADRESH and ADRESL registers contain the result of the A/D conversion. The register pair is referred to as the ADRES register. When the A/D conversion is complete, the result is loaded into ADRES, the GO/DONE bit (ADCON0<2>) is cleared, and the A/D interrupt flag ADIF is set. The block diagram of the A/D module is shown in Figure 11-3.

#### REGISTER 11-2: A/D CONTROL REGISTER 1 (ADCON1: 9Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-------|-------|-------|----------|----------|----------|----------|

| ADFM  | VCFG2 | VCFG1 | VCFG0 | Reserved | Reserved | Reserved | Reserved |

| bit 7 |       |       |       |          |          |          | bit 0    |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified

0 = Left justified

```

bit 6-4

```

VCFG<2:0>: Voltage Reference Configuration bits

|     | A/D VREF+           | A/D VREF-           |

|-----|---------------------|---------------------|

| 000 | AVDD <sup>(1)</sup> | AVss <sup>(2)</sup> |

| 001 | External VREF+      | External VREF-      |

| 010 | Internal VRH        | Internal VRL        |

| 011 | External VREF+      | AVss <sup>(2)</sup> |

| 100 | Internal VRH        | AVss <sup>(2)</sup> |

| 101 | AVDD <sup>(1)</sup> | External VREF-      |

| 110 | AVDD <sup>(1)</sup> | Internal VRL        |

| 111 | Internal VRL        | AVss                |

bit 3-0 Reserved: Do not use.

Note 1: This parameter is VDD for the PIC16C717.

2: This parameter is Vss for the PIC16C717.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

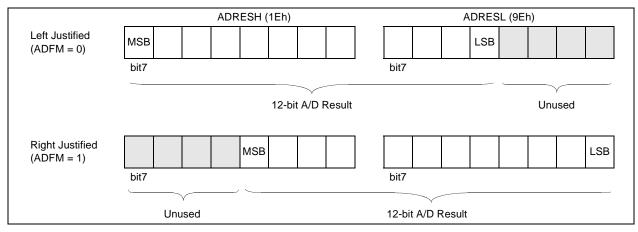

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset. The A/D conversion results can be left justified (ADFM bit cleared), or right justified (ADFM bit set). Figure 11-1 through Figure 11-2 show the A/D result data format of the PIC16C717/770/771.

#### FIGURE 11-1: PIC16C770/771 12-BIT A/D RESULT FORMATS

### REGISTER 12-1: CONFIGURATION WORD FOR 16C717/770/771 DEVICE

| CP                | CP                                            | BORV1                                                                                                                                       | BORV0                                                                                                                                   | CP                                                                                 | CP                                                                                      | _                                                                 | BODEN                                                                   | MCLRE                                                                         | PWRTE                                                                      | WDTE                                                        | FOSC2         | FOSC1                  | FOSC0 |

|-------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|---------------|------------------------|-------|

| bit13             |                                               |                                                                                                                                             |                                                                                                                                         |                                                                                    |                                                                                         |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        | bit0  |

| bit 13-12,<br>9-8 | 1 = 0                                         | <b>CP: Program Memory Code Protection</b><br>1 = Code protection off<br>0 = All program memory is protected <sup>(2)</sup>                  |                                                                                                                                         |                                                                                    |                                                                                         |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 11-10:        | 00 =<br>01 =<br>10 =                          | BORV<1:0>: Brown-out Reset Voltage bits<br>00 = VBOR set to 4.5V<br>01 = VBOR set to 4.2V<br>10 = VBOR set to 2.7V<br>11 = VBOR set to 2.5V |                                                                                                                                         |                                                                                    |                                                                                         |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 7:            | Unin                                          | nplement                                                                                                                                    | ted: Read a                                                                                                                             | as '1'                                                                             |                                                                                         |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 6:            | 1 <b>= E</b>                                  | Brown-out                                                                                                                                   | vn-out Dete<br>t Detect Res<br>t Detect Res                                                                                             | set enab                                                                           | ed                                                                                      | <sub>it</sub> (1)                                                 |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 5:            | 1 = F                                         | RA5/MCLI                                                                                                                                    | MCLR pin t<br>R pin functi<br>R pin functi                                                                                              | on is MC                                                                           | LR                                                                                      | MCLR in                                                           | ternally tie                                                            | d to VDD                                                                      |                                                                            |                                                             |               |                        |       |

| bit 4:            | 1 = F                                         | <b>RTE:</b> Powe<br>PWRT dis<br>PWRT ena                                                                                                    |                                                                                                                                         | r Enable                                                                           | bit <sup>(1)</sup>                                                                      |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 3:            | 1 = \                                         | T <b>E:</b> Watch<br>WDT enat<br>WDT disal                                                                                                  |                                                                                                                                         | Enable b                                                                           | it                                                                                      |                                                                   |                                                                         |                                                                               |                                                                            |                                                             |               |                        |       |

| bit 2-0:          | 000<br>001<br>010<br>011<br>100<br>101<br>110 | = LP osci<br>= XT osci<br>= HS osci<br>= EC: I/O<br>= INTRC<br>= INTRC<br>= ER osci                                                         | Oscillator S<br>Ilator: Cryst<br>Illator: Cryst<br>function or<br>oscillator: I,<br>oscillator: Cyst<br>illator: I/O fu<br>illator: CLK | tal/Resor<br>tal/Resor<br>tal/Resor<br>RA6/OS<br>O function<br>CLKOUT<br>unction c | hator on F<br>nator on F<br>nator on F<br>SC2/CLK<br>on on RA<br>function on<br>n RA6/O | RA6/OSC<br>RA6/OSC<br>DUT pin,<br>6/OSC2/(<br>on RA6/C<br>SC2/CLK | 2/CLKOUT<br>2/CLKOUT<br>CLKIN fun<br>CLKOUT p<br>SC2/CLK0<br>OUT pin, F | F and RA7<br>F and RA7<br>ction on F<br>in, I/O fur<br>OUT pin,<br>Resistor o | 7/OSC1/C<br>7/OSC1/C<br>RA7/OSC1<br>nction on F<br>I/O functio<br>n RA7/OS | LKIN<br>LKIN<br>I/CLKIN<br>RA7/OSC<br>on on RA7<br>SC1/CLKI | 7/OSC1/C<br>N | LKIN                   |       |

|                   | Ensure                                        | the Powe                                                                                                                                    | out Reset a<br>r-up Timer<br>must be giv                                                                                                | is enable                                                                          | d anytim                                                                                | e Brown-o                                                         | out Reset i                                                             | s enabled                                                                     |                                                                            | dless of th                                                 | ne value o    | f bit <mark>PWR</mark> | TE.   |

| Legend            |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown |

# 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked by the POR pulse. When the PWRT delay expires, the Oscillator Start-up Timer is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 12-6, Figure 12-7, Figure 12-8 and Figure 12-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 12-8). This is useful for testing purposes or to synchronize more than one PIC<sup>®</sup> microcontroller operating in parallel.

Table 12-5 shows the RESET conditions for some special function registers, while Table 12-6 shows the RESET conditions for all the registers.

#### 12.9 Power Control/STATUS Register (PCON)

The Power Control/STATUS Register, PCON, has two status bits that provide indication of which power-up type RESET occurred.

Bit0 is Brown-out Reset Status bit, BOR. The BOR bit is unknown upon a POR. BOR must be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator Configuration | Power                     | -up       | Brown-out        | Wake-up from |

|--------------------------|---------------------------|-----------|------------------|--------------|

|                          | PWRTE = 0                 | PWRTE = 1 | Brown-out        | SLEEP        |

| XT, HS, LP               | TPWRT + 1024Tosc 1024Tosc |           | TPWRT + 1024Tosc | 1024Tosc     |

| EC, ER, INTRC            | TPWRT                     | _         | TPWRT            | —            |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | x   | 0  | x  | legal, TO is set on POR                                 |  |  |  |

| 0   | x   | x  | 0  | llegal, PD is set on POR                                |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |

|---------------------------------------|--------------------|--------------------|------------------|

| Power-on Reset                        | 000h               | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 1-uu             |

| WDT Reset                             | 000h               | 0000 luuu          | 1-uu             |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | u-uu             |

| Brown-out Reset                       | 000h               | 0001 luuu          | 1-u0             |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuul Ouuu          | u-uu             |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

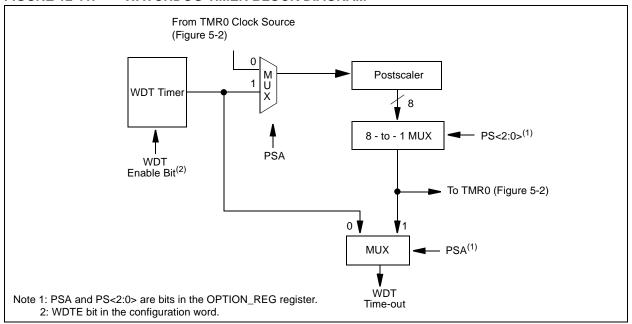

# 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This oscillator is independent from the processor clock. If enabled, the WDT will run even if the main clock of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to

wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{TO}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by programming the configuration bit WDTE to '0' (Section 12.1).

WDT time-out period values may be found in Table 15-4. Values for the WDT prescaler may be assigned using the OPTION\_REG register.

**Note:** The SLEEP instruction clears the WDT and the postscaler, if assigned to the WDT, restarting the WDT period.

#### FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-----------------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h    | Config. bits <sup>(1)</sup> | _     | BODEN  | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG                  | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for the full description of the configuration word bits.

| IORLW            | Inclusive OR Literal with W                                                                                                 |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                         |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                           |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |  |  |  |

| MOVLW            | Move Literal to W                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                              |

| Status Affected: | None                                                                                             |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                   |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                       |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in regis-<br>ter 'f'. |  |  |  |  |  |  |

| MOVWF            | Move W to f                                     |  |  |  |  |  |  |

|------------------|-------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                                 |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                             |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                           |  |  |  |  |  |  |

| Status Affected: | None                                            |  |  |  |  |  |  |

| Description:     | Move data from W register to reg-<br>ister 'f'. |  |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                        |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself. d<br>= 1 is useful to test a file register<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

# 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

# 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

### 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

| TABLE 15-6: | ENHANCED CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP) |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

| Param.<br>No. | Sym  | Characteristic          | Characteristic        |                             |             |    | Max | Units | Conditions                         |

|---------------|------|-------------------------|-----------------------|-----------------------------|-------------|----|-----|-------|------------------------------------|

| 50*           | TccL | CCP1 input low          | No Prescaler          |                             | 0.5Tcy + 20 | —  | _   | ns    |                                    |

|               |      | time                    |                       | PIC16 <b>C</b> 717/770/771  | 10          | _  | _   | ns    |                                    |

|               |      |                         | With Prescaler        | PIC16 <b>LC</b> 717/770/771 | 20          | —  | _   | ns    |                                    |

| 51*           | TccH | CCP1 input high<br>time | No Prescaler          |                             | 0.5Tcy + 20 | —  | _   | ns    |                                    |

|               |      |                         | With Prescaler        | PIC16 <b>C</b> 717/770/771  | 10          | _  | _   | ns    |                                    |

|               |      |                         |                       | PIC16 <b>LC</b> 717/770/771 | 20          | —  | _   | ns    |                                    |

| 52*           | TccP | CCP1 input period       | CCP1 input period     |                             |             | —  | _   | ns    | N = prescale value<br>(1, 4 or 16) |

| 53*           | TccR | CCP1 output fall ti     | me                    | PIC16 <b>C</b> 717/770/771  | —           | 10 | 25  | ns    |                                    |

|               |      |                         |                       | PIC16 <b>LC</b> 717/770/771 | —           | 25 | 45  | ns    |                                    |

| 54* TccF CCF  |      | CCP1 output fall ti     | CCP1 output fall time |                             | —           | 10 | 25  | ns    |                                    |

|               |      |                         |                       | PIC16 <b>LC</b> 717/770/771 | —           | 25 | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 15.4.3 PROGRAMMABLE BROWN-OUT RESET MODULE (PBOR)

# TABLE 15-9: DC CHARACTERISTICS: PBOR

| $\begin{array}{c} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C & \leq TA \leq & +70^{\circ}C \mbox{ for commercial} \\ & -40^{\circ}C & \leq TA \leq & +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C & \leq TA \leq & +125^{\circ}C \mbox{ for extended} \\ & \mbox{Operating voltage VDD range as described in DC Characteristics Section 15.1.} \end{array}$ |             |                |        |     |      |      | ection 15.1. |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------|-----|------|------|--------------|------------|

| Param.<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                         | Charac      | teristic       | Symbol | Min | Тур  | Max  | Units        | Conditions |

| D005                                                                                                                                                                                                                                                                                                                                                                                                                                  | BOR Voltage | BORV<1:0> = 11 |        | 2.5 | 2.58 | 2.66 |              |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | BORV<1:0> = 10 | VBOR   | 2.7 | 2.78 | 2.86 | V            |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | BORV<1:0> = 01 | VBOR   | 4.2 | 4.33 | 4.46 | v            |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | BORV<1:0> = 00 |        | 4.5 | 4.64 | 4.78 |              |            |

#### 15.4.4 VREF MODULE

#### TABLE 15-10: DC CHARACTERISTICS: VREF

| DC CHA        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                         |     |       |     |       |                                                                                                                 |                                                            |  |

|---------------|------------------------------------------------------|-------------------------|-----|-------|-----|-------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Param.<br>No. | Symbol                                               | Characteristic          | Min | Тур†  | Max | Units |                                                                                                                 | Conditions                                                 |  |

| D400          | VRL                                                  | Output Voltage          | 2.0 | 2.048 | 2.1 | V     | $VDD \ge 2.7V,$                                                                                                 | $-40^{\circ}C \le TA \le +85^{\circ}C$                     |  |

|               | VRH                                                  |                         | 4.0 | 4.096 | 4.2 | V     | $V\text{DD} \geq 4.5\text{V},$                                                                                  | $\textbf{-40^{\circ}C} \leq TA \leq \textbf{+85^{\circ}C}$ |  |

| D400A         | VRL                                                  | Output Voltage          | 1.9 | 2.048 | 2.2 | V     | $V \text{DD} \geq 2.7 \text{V}, \ \text{-40}^{\circ} \text{C} \leq \text{Ta} \leq \text{+125}^{\circ} \text{C}$ |                                                            |  |

|               | VRH                                                  |                         | 4.0 | 4.096 | 4.3 | V     | $V\text{DD} \geq 4.5\text{V},$                                                                                  | $\text{-40°C} \leq \text{TA} \leq \text{+125°C}$           |  |

| D404*         | IVREFSO                                              | External Load Source    |     | _     | 5   | mA    |                                                                                                                 |                                                            |  |

| D405*         | IVREFSI                                              | External Load Sink      | _   | _     | -5  | mA    |                                                                                                                 |                                                            |  |

| *             | CL                                                   | External Capacitor Load | _   | _     | 200 | pF    |                                                                                                                 |                                                            |  |

| D406*         | $\Delta$ Vout/                                       | VRH Load Regulation     | _   | 0.6   | 1   | mV/mA | $V \text{DD} \geq 5 V$                                                                                          | ISOURCE = 0 mA to 5 mA                                     |  |

|               | ∆lout                                                |                         | _   | 1     | 4   | ]     |                                                                                                                 | ISINK = 0 mA to 5 mA                                       |  |

|               |                                                      | VRL Load Regulation     |     | 0.6   | 1   | ]     | $V\text{DD} \geq 3V$                                                                                            | ISOURCE = 0 mA to 5 mA                                     |  |

|               |                                                      |                         | _   | 2     | 4   |       |                                                                                                                 | ISINK = 0 mA to 5 mA                                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

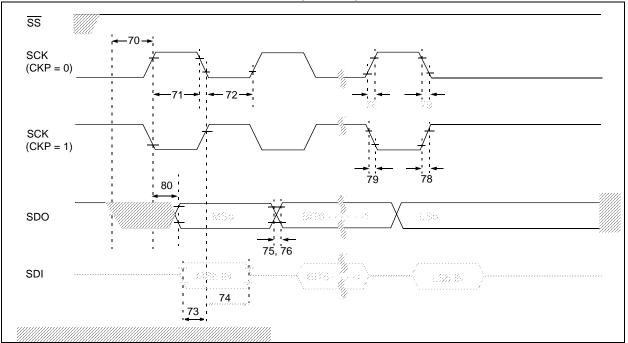

# 15.5 Master SSP SPI Mode Timing Waveforms and Requirements

#### FIGURE 15-18: SPI MASTER MODE TIMING (CKE = 0)

# TABLE 15-17: SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                                                      | Min            | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|---------------------------------------------------------------------|----------------|--------------|-----|-------|------------|--------|

| 70*           | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ inp | ut             | Тсү          | _   | _     | ns         |        |

| 71*           | TscH                  | SCK input high time                                                 | Continuous     | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A*          |                       | (Slave mode)                                                        | Single Byte    | 40           | _   | _     | ns         | Note 1 |

| 72*           | TscL                  | SCK input low time                                                  | Continuous     | 1.25Tcy + 30 |     |       | ns         |        |

| 72A*          |                       | (Slave mode)                                                        | Single Byte    | 40           |     |       | ns         | Note 1 |

| 73*           | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inpu                                         | ut to SCK edge | 100          | _   | _     | ns         |        |

| 73A*          | Тв2в                  | Last clock edge of Byte1 to edge of Byte2                           | the 1st clock  | 1.5Tcy + 40  | —   | —     | ns         | Note 1 |

| 74*           | TscH2diL,<br>TscL2diL | Hold time of SDI data input                                         | to SCK edge    | 100          | _   | _     | ns         |        |

| 75*           | TdoR                  | SDO data output rise time                                           | PIC16CXXX      | _            | 10  | 25    | ns         |        |

|               |                       |                                                                     | PIC16LCXXX     | _            | 20  | 45    | ns         |        |

| 76*           | TdoF                  | SDO data output fall time                                           |                | —            | 10  | 25    | ns         |        |

| 78*           | TscR                  | SCK output rise time PIC16 <b>C</b> XXX                             |                | _            | 10  | 25    | ns         |        |

|               |                       | (Master mode)                                                       | PIC16LCXXX     |              | 20  | 45    | ns         |        |

| 79*           | TscF                  | SCK output fall time (Master mode)                                  |                |              | 10  | 25    | ns         |        |

| 80*           | TscH2doV,             | SDO data output valid                                               | PIC16CXXX      |              | _   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                                                      | PIC16LCXXX     |              | —   | 100   | ns         |        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

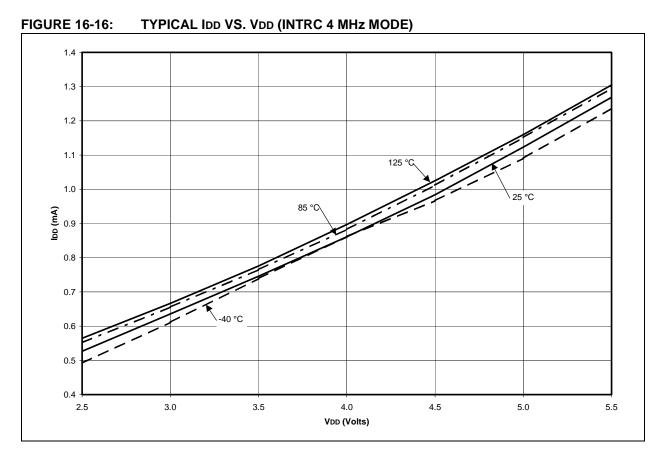

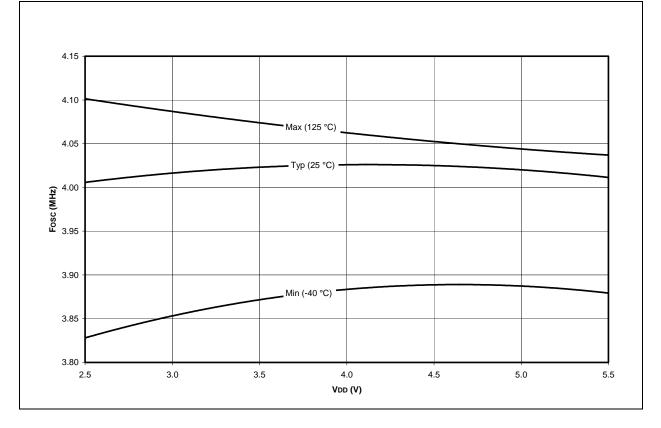

FIGURE 16-17: INTERNAL RC Fosc VS. VDD OVER TEMPERATURE (4 MHz)

© 1999-2013 Microchip Technology Inc.

17.6 20-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

DRAWING NOT AVAILABLE