Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 7KB (4K x 14)                                                          |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                            |

| Data Converters            | A/D 6x12b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc771-p |

TABLE 2-1: PIC16C717/770/771 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address               | Name       | Bit 7         | Bit 6          | Bit 5          | Bit 4           | Bit 3        | Bit 2           | Bit 1        | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>Page: |

|-----------------------|------------|---------------|----------------|----------------|-----------------|--------------|-----------------|--------------|---------|--------------------------|------------------------|

| Bank 2                |            |               |                |                |                 |              |                 |              |         |                          |                        |

| 100h <sup>(3)</sup>   | INDF       | Addressing    | this location  | uses content   | s of FSR to ad  | dress data m | emory (not a    | physical rec | gister) | 0000 0000                | 23                     |

| 101h                  | TMR0       | Timer0 mod    | lule's registe | r              |                 |              |                 |              |         | xxxx xxxx                | 45                     |

| 102h <sup>(3)</sup>   | PCL        | Program Co    | ounter's (PC)  | Least Signific | cant Byte       |              |                 |              |         | 0000 0000                | 22                     |

| 103h <sup>(3)</sup>   | STATUS     | IRP           | RP1            | RP0            | TO              | PD           | Z               | DC           | С       | 0001 1xxx                | 14                     |

| 104h <sup>(3)</sup>   | FSR        | Indirect data | a memory ad    | dress pointer  |                 |              |                 |              |         | xxxx xxxx                | 23                     |

| 105h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 106h                  | PORTB      | PORTB Dat     | ta Latch whe   | n written: PO  | RTB pins whe    | n read       |                 |              |         | xxxx xx11                | 33                     |

| 107h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 108h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 109h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 10Ah <sup>(1,3)</sup> | PCLATH     | _             | _              | _              | Write Buffer f  | or the upper | 5 bits of the I | Program Cou  | ınter   | 0 0000                   | 22                     |

| 10Bh <sup>(3)</sup>   | INTCON     | GIE           | PEIE           | TOIE           | INTE            | RBIE         | TOIF            | INTF         | RBIF    | 0000 000x                | 16                     |

| 10Ch                  | PMDATL     | Program me    | emory read o   | lata low       |                 | •            |                 | l            | ı       | xxxx xxxx                |                        |

| 10Dh                  | PMADRL     | Program me    | emory read a   | ddress low     |                 |              |                 |              |         | xxxx xxxx                |                        |

| 10Eh                  | PMDATH     | _             | _              | Program me     | mory read data  | a high       |                 |              |         | xx xxxx                  |                        |

| 10Fh                  | PMADRH     | _             | _              | _              | _               | Program me   | emory read a    | ddress high  |         | xxxx                     |                        |

| 110h-<br>11Fh         | _          | Unimpleme     | Unimplemented  |                |                 |              |                 |              |         |                          |                        |

| Bank 3                |            |               |                |                |                 |              |                 |              |         |                          |                        |

| 180h <sup>(3)</sup>   | INDF       | Addressing    | this location  | uses content   | s of FSR to ad  | dress data m | emory (not a    | physical rec | gister) | 0000 0000                | 23                     |

| 181h                  | OPTION_REG | RBPU          | INTEDG         | T0CS           | T0SE            | PSA          | PS2             | PS1          | PS0     | 1111 1111                | 15                     |

| 182h <sup>(3)</sup>   | PCL        | Program Co    | ounter's (PC)  | Least Signific | cant Byte       |              |                 |              |         | 0000 0000                | 22                     |

| 183h <sup>(3)</sup>   | STATUS     | IRP           | RP1            | RP0            | TO              | PD           | Z               | DC           | С       | 0001 1xxx                | 14                     |

| 184h <sup>(3)</sup>   | FSR        | Indirect data | a memory ad    | dress pointer  |                 |              |                 |              |         | xxxx xxxx                | 23                     |

| 185h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 186h                  | TRISB      | PORTB Dat     | ta Direction F | Register       |                 |              |                 |              |         | 1111 1111                | 33                     |

| 187h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 188h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 189h                  | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

| 18Ah <sup>(1,3)</sup> | PCLATH     | _             | _              | _              | Write Buffer fo | or the upper | 5 bits of the I | Program Cou  | ınter   | 0 0000                   | 22                     |

| 18Bh <sup>(3)</sup>   | INTCON     | GIE           | PEIE           | TOIE           | INTE            | RBIE         | TOIF            | INTF         | RBIF    | 0000 000x                | 16                     |

| 18Ch                  | PMCON1     | Reserved      | -              | _              | _               | _            | _               | _            | RD      | 10                       |                        |

| 18Dh-<br>18Fh         | _          | Unimpleme     | nted           |                |                 |              |                 |              |         | _                        | _                      |

$\label{eq:local_equation} \textbf{Legend:} \quad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{q} = \textbf{value} \ \textbf{depends} \ \textbf{on condition}, \ \textbf{-} = \textbf{unimplemented} \ \textbf{read} \ \textbf{as} \ \textbf{'0'}.$

Shaded locations are unimplemented, read as '0'.

- 2: Other (non Power-up) Resets include external RESET through MCLR and Watchdog Timer Reset.

- 3: These registers can be addressed from any bank.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

To OSC2 Oscillator Circuit To Chip Clock Drivers Schmitt Trigger Input Buffer Data D Q VDD Bus EC Mode Q Р WR \_\_\_ PORTA CK\ Data Latch D Q Ν WR\_ TRISA CK√ Q TRIS Latch INTRC Vss INTRC **RD TRISA** Schmitt Trigger Input Buffer Q D ΕN RD PORTA

FIGURE 3-6: **BLOCK DIAGRAM OF RA7/OSC1/CLKIN PIN**

### PIC16C717/770/771

TABLE 4-1: PROGRAM MEMORY READ REGISTER SUMMARY

| Address | Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|----------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 18Ch    | PMCON1 | Reserved | _     | _     | _     | _     | _     | _     | RD    | 10                       | 10                              |

| 10Eh    | PMDATH | _        | _     | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  | xx xxxx                  | uu uuuu                         |

| 10Ch    | PMDATL | PMD7     | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  | xxxx xxxx                | uuuu uuuu                       |

| 10Fh    | PMADRH |          |       | _     |       | PMA11 | PMA10 | PMA9  | PMA8  | xxxx                     | uuuu                            |

| 10Dh    | PMADRL | PMA7     | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  | xxxx xxxx                | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Program Memory Read.

#### 7.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

#### 7.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 7-1: **Timer2 Block Diagram** Sets flag TMR2 output (1) bit TMR2IF Prescaler TMR2 reg 1:1, 1:4, 1:16 Postscaler 2 Comparator 1:1 to 1:16 PR2 reg Note: TMR2 register output can be software selected by the SSP Module as a baud clock.

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name                       | Bit 7               | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|----------------------------|---------------------|---------|---------|---------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON                     | GIE                 | PEIE    | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1                       |                     | ADIF    | 1       | 1       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0 0000                  | -0 0000                         |

| 8Ch                   | PIE1                       | -                   | ADIE    | 1       | -       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                  | -0 0000                         |

| 11h                   | TMR2                       | MR2 Timer2 register |         |         |         |         |        |         |         |                          | 0000 0000                       |

| 12h                   | T2CON                      | _                   | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2 Timer2 Period Register |                     |         |         |         |         |        |         |         | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only an ECCP interrupt is generated (if enabled).

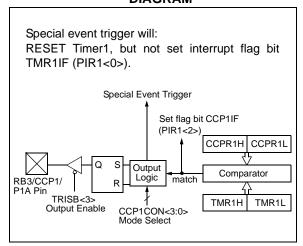

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of ECCP resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of ECCP module will also start an A/D conversion if the A/D module is enabled.

**Note:** The special event trigger will not set the interrupt flag bit TMR1IF (PIR1<0>).

# FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Name    | Bit 7                | Bit 6           | Bit 5         | Bit 4         | Bit 3        | Bit 2   | Bit 1  | Bit 0      | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|----------------------|-----------------|---------------|---------------|--------------|---------|--------|------------|-------------------------|---------------------------------|

| INTCON  | GIE                  | PEIE            | TOIE          | INTE          | RBIE         | TOIF    | INTF   | RBIF       | 0000 000x               | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF            | RCIF          | TXIF          | SSPIF        | CCP1IF  | TMR2IF | TMR1IF     | 0000 0000               | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE            | RCIE          | TXIE          | SSPIE        | CCP1IE  | TMR2IE | TMR1IE     | 0000 0000               | 0000 0000                       |

| TRISB   | PORTB Data           | a Direction Re  | gister        |               |              |         |        |            | 1111 1111               | 1111 1111                       |

| TMR1L   | Holding regis        |                 | xxxx xxxx     | uuuu uuuu     |              |         |        |            |                         |                                 |

| TMR1H   | Holding regis        | ster for the Mo | st Significan | t Byte of the | 16-bit TMR1r | egister |        |            | xxxx xxxx               | uuuu uuuu                       |

| T1CON   | ı                    | ı               | T1CKPS<br>1   | T1CKP<br>S0   | T1OSCEN      | T1SYNC  | TMR1CS | TMR10<br>N | 00 0000                 | uu uuuu                         |

| CCPR1L  | Capture/Cor          | npare/PWM re    |               | xxxx xxxx     | uuuu uuuu    |         |        |            |                         |                                 |

| CCPR1H  | Capture/Cor          | npare/PWM re    |               | xxxx xxxx     | uuuu uuuu    |         |        |            |                         |                                 |

| CCP1CON | PWM1M1               | PWM1M0          | DC1B1         | DC1B0         | CCP1M3       | CCP1M2  | CCP1M1 | CCP1M0     | 0000 0000               | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

#### 8.3.7 SYSTEM IMPLEMENTATION

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller powers up, all of the I/O pins are in the high-impedance state. The external pull-up and pull-down resistors must keep the power switch devices in the off state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

#### 8.3.8 START-UP CONSIDERATIONS

Prior to enabling the PWM outputs, the P1A, P1B, P1C and P1D latches may not be in the proper states. Enabling the TRISB bits for output at the same time with the CCP module may cause damage to the power switch devices. The CCP1 module must be enabled in the proper Output mode with the TRISB bits enabled as inputs. Once the CCP1 completes a full PWM cycle, the P1A, P1B, P1C and P1D output latches are properly initialized. At this time, the TRISB bits can be enabled for outputs to start driving the power switch devices. The completion of a full PWM cycle is indicated by the TMR2IF bit going from a '0' to a '1'.

#### 8.3.9 SET UP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM module:

- a) Disable the CCP1/P1A, P1B, P1C and/or P1D outputs by setting the respective TRISB bits.

- Set the PWM period by loading the PR2 register.

- Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- d) Configure the ECCP module for the desired PWM operation by loading the CCP1CON register. With the CCP1M<3:0> bits select the active high/low levels for each PWM output. With the PWM1M<1:0> bits select one of the available Output modes: Single, Half-Bridge, Full-Bridge, Forward or Full-Bridge Reverse.

- e) For Half-Bridge Output mode, set the deadband delay by loading the P1DEL register.

- 2. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit in the PIR1 register.

- Set the TMR2 prescale value by loading the T2CKPS<1:0> bits in the T2CON register.

- c) Enable Timer2 by setting the TMR2ON bit in the T2CON register.

- Enable PWM outputs after a new cycle has started:

- Wait until TMR2 overflows (TMR2IF bit becomes a '1'). The new PWM cycle begins here.

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRISB bits.

TABLE 8-3: REGISTERS ASSOCIATED WITH PWM

| Address                 | Name    | Bit 7                | Bit 6                               | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|---------|----------------------|-------------------------------------|---------|-----------|-----------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE    | INTE      | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch                     | PIR1    | _                    | ADIF                                | _       | _         | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | -0 0000                 | -0 0000                         |

| 8Ch                     | PIE1    | _                    | ADIE                                | _       | _         | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | -0 0000                         |

| 86h, 186h               | TRISB   | PORTB Dat            | a Direction R                       |         | 1111 1111 | 1111 1111 |        |         |         |                         |                                 |

| 11h                     | TMR2    | Timer2 register      |                                     |         |           |           |        |         |         | 0000 0000               | 0000 0000                       |

| 92h                     | PR2     | Timer2 perio         | od register                         |         |           |           |        |         |         | 1111 1111               | 1111 1111                       |

| 12h                     | T2CON   | _                    | TOUTPS3                             | TOUTPS2 | TOUTPS1   | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h                     | CCPR1L  | Capture/Cor          | Capture/Compare/PWM register1 (LSB) |         |           |           |        |         |         |                         | uuuu uuuu                       |

| 17h                     | CCP1CON | PWM1M1               | PWM1M0                              | DC1B1   | DC1B0     | CCP1M3    | CCP1M2 | CCP1M1  | CCP1M0  | 0000 0000               | 0000 0000                       |

| 97h                     | P1DEL   | DEL PWM1 Delay value |                                     |         |           |           |        |         |         | 0000 0000               | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by ECCP module in PWM mode.

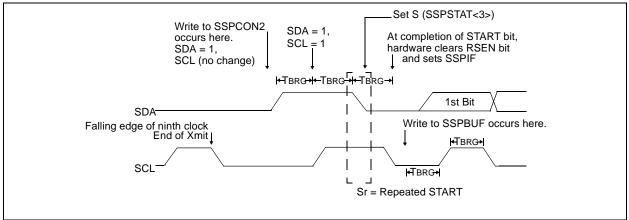

### 9.2.11 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is set high while the I<sup>2</sup>C module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG period. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG period while SCL is high. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. Following this, the baud rate generator is reloaded with the contents of SSPAD<6:0> and begins counting. When the BRG times out a third time, the RSEN bit in the SSPCON2 register is automatically cleared and SCL is pulled low. The SSPIF flag is set, which indicates the Restart sequence is complete.

**Note 1:** If RSEN is set while another event is in progress, it will not take effect. Queuing of events is not allowed.

- 2: A bus collision during the Repeated START condition occurs if either of the following is true:

- a) SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit transition to true, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then perform one of the following:

- Transmit an additional eight bits of address (if the user transmitted the first half of a 10-bit address with R/W = 0),

- Transmit eight bits of data (if the user transmitted a 7-bit address with R/W = 0), or

- Receive eight bits of data (if the user transmitted either the first half of a 10-bit address or a 7-bit address with R/W = 1).

#### 9.2.11.1 WCOL STATUS FLAG

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower five bits of SSPCON2 is disabled until the Repeated START condition is complete.

FIGURE 9-17: REPEAT START CONDITION WAVEFORM

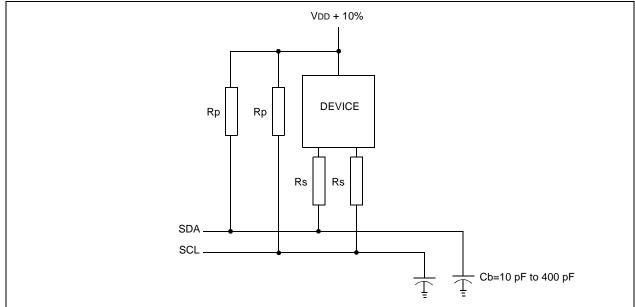

### 9.2.18 CONNECTION CONSIDERATIONS FOR I<sup>2</sup>C BUS

For Standard mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-31 depends on the following parameters

- · Supply voltage

- · Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at Vol max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_{p \ min}$  = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $\textit{R}_{p}$  is shown in Figure 9-31. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $\textit{R}_{s}$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-31).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in I<sup>2</sup>C mode (master or slave).

#### FIGURE 9-31: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

Note: I<sup>2</sup>C devices with input levels related to VDD must have one common supply line to which the pull-up resistor is also connected.

#### TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                | Name    | Bit 7 | Bit 6   | Bit 5      | Bit 4       | Bit 3       | Bit 2        | Bit 1    | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|-------|---------|------------|-------------|-------------|--------------|----------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE   | PEIE    | TOIE       | INTE        | RBIE        | TOIF         | INTF     | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | _     | ADIF    | _          | _           | SSPIF       | CCP1IF       | TMR2IF   | TMR1IF | -0 0000   | -0 0000   |

| 8Ch                    | PIE1    | _     | ADIE    | _          | _           | SSPIE       | CCP1IE       | TMR2IE   | TMR1IE | -0 0000   | -0 0000   |

| 0Dh                    | PIR2    | LVDIF | _       | _          | _           | BCLIF       | _            | _        | CCP2IF | 0 00      | 0 00      |

| 8Dh                    | PIE2    | LVDIE | _       | _          | _           | BCLIE       | _            | _        | CCP2IE | 0 00      | 0 00      |

| 13h                    | SSPBUF  |       | Synch   | ronous Ser | ial Port Re | ceive Buffe | r/Transmit F | Register |        | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL  | SSPOV   | SSPEN      | CKP         | SSPM3       | SSPM2        | SSPM1    | SSPM0  | 0000 0000 | 0000 0000 |

| 91h                    | SSPCON2 | GCEN  | ACKSTAT | ACKDT      | ACKEN       | RCEN        | PEN          | RSEN     | SEN    | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP   | CKE     | D/Ā        | Р           | S           | R/W          | UA       | BF     | 0000 0000 | 0000 0000 |

| 93h                    | SSPADD  |       | Synd    | 2          | 0000 0000   | 0000 0000   |              |          |        |           |           |

Legend: x = unknown, u = unchanged,  $- = unimplemented read as '0'. Shaded cells are not used by the MSSP in <math>I^2C$  mode.

#### 10.3 Low Voltage Detect (LVD)

This module is used to generate an interrupt when the supply voltage falls below a specified "trip" voltage. This module operates completely under software control. This allows a user to power the module on and off to periodically monitor the supply voltage, and thus minimize total current consumption.

The LVD module is enabled by setting the LVDEN bit in the LVDCON register. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to or less than the trip point, the module will generate an interrupt signal setting interrupt flag bit LVDIF. If interrupt enable bit LVDIE was set, then an interrupt is generated. The LVD interrupt can wake the device from SLEEP. The "trip point" voltage is software programmable to any one of 16 values, five of which are reserved (See Figure 10-1). The trip point is selected by programming the LV<3:0> bits (LVDCON<3:0>).

Note:

The LVDIF bit can not be cleared until the supply voltage rises above the LVD trip point. If interrupts are enabled, clear the LVDIE bit once the first LVD interrupt occurs to prevent reentering the interrupt service routine immediately after exiting the ISR.

Once the LV bits have been programmed for the specified trip voltage, the low-voltage detect circuitry is then enabled by setting the LVDEN (LVDCON<4>) bit.

If the bandgap reference voltage is previously unused by either the brown-out circuitry or the voltage reference circuitry, then the bandgap circuit requires a time to start-up and become stable before a low voltage condition can be reliably detected. The low-voltage interrupt flag is prevented from being set until the bandgap has reached a stable reference voltage.

When the bandgap is stable the BGST (LVDCON<5>) bit is set indicating that the low-voltage interrupt flag bit is released to be set if VDD is equal to or less than the LVD trip point.

#### 10.3.1 EXTERNAL ANALOG VOLTAGE INPUT

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when LV<3:0>=1111. When these bits are set the comparator input is multiplexed from an external input pin (RA1/AN1/LVDIN).

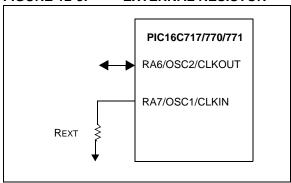

#### 12.2.4 ER MODE

For timing insensitive applications, the ER (External Resistor) Clock mode offers additional cost savings. Only one external component, a resistor connected to the OSC1 pin and Vss, is needed to set the operating frequency of the internal oscillator. The resistor draws a DC bias current which controls the oscillation frequency. In addition to the resistance value, the oscillator frequency will vary from unit to unit, and as a function of supply voltage and temperature. Since the controlling parameter is a DC current and not a capacitance, the particular package type and lead frame will not have a significant effect on the resultant frequency.

Figure 12-3 shows how the controlling resistor is connected to the PIC16C717/770/771. For REXT values below 38 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g. 1M), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 38 k $\Omega$  and 1 M $\Omega$ .

FIGURE 12-3: EXTERNAL RESISTOR

The Electrical Specification section shows the relationship between the REXT resistance value and the operating frequency as well as frequency variations due to operating temperature for given REXT and VDD values.

The ER Oscillator mode has two options that control the OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as CLK-OUT. The ER oscillator does not run during RESET.

#### 12.2.5 INTRC MODE

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature. The INTRC oscillator does not run during RESET.

#### 12.2.6 CLKOUT

In the INTRC and ER modes, the PIC16C717/770/771 can be configured to provide a clock out signal by programming the configuration word. The oscillator frequency, divided by 4, can be used for test purposes or to synchronize other logic.

In the INTRC and ER modes, if the CLKOUT output is enabled, CLKOUT is held low during RESET.

### 12.2.7 DUAL SPEED OPERATION FOR ER AND INTRC MODES

A software programmable dual speed oscillator is available in either ER or INTRC Oscillator modes. This feature allows the applications to dynamically toggle the oscillator speed between normal and slow frequencies. The nominal slow frequency is 37 kHz. In ER mode, the slow speed operation is fixed and does not vary with resistor size. Applications that require low current power savings, but cannot tolerate putting the part into SLEEP, may use this mode.

The OSCF bit in the PCON register is used to control Dual Speed mode. See the PCON Register, Register 2-8, for details.

When changing the INTRC or ER internal oscillator speed, there is a period of time when the processor is inactive. When the speed changes from fast to slow, the processor inactive period is in the range of 100  $\mu$ S to 300  $\mu$ S. For speed change from slow to fast, the processor is in active for 1.25  $\mu$ S to 3.25  $\mu$ S.

#### 12.4 Power-On Reset (POR)

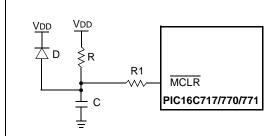

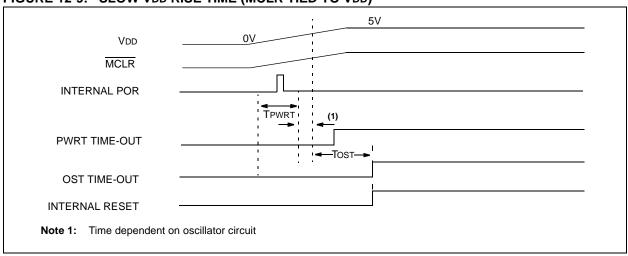

A Power-on Reset pulse is generated on-chip when a VDD rise is detected (in the range of 1.5V - 2.1V). Enable the internal MCLR feature to eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details. For a long rise time, enable external MCLR function and use circuit as shown in Figure 12-5.

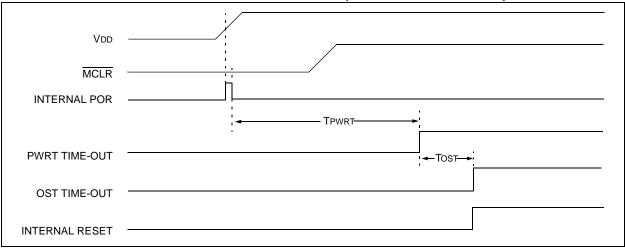

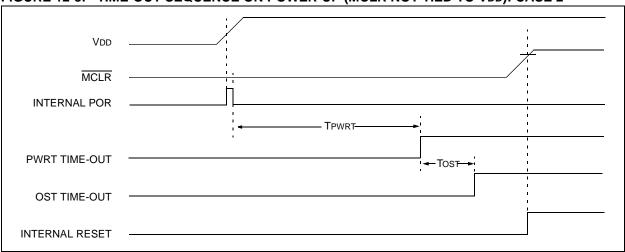

Two delay timers, (PWRT on OST), have been provided which hold the device in RESET after a POR (dependent upon device configuration) so that all operational parameters have been met prior to releasing the device to resume/begin normal operation.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions, or if necessary an external POR circuit may be implemented to delay end of RESET for as long as needed.

FIGURE 12-5: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD RAMP)

- **Note 1:** External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

- 4: External MCLR must be enabled (MCLRE = 1).

#### 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed TPWRT time-out on power-up type RESETS only. For a POR, the PWRT is invoked when the POR pulse is generated. For a BOR, the PWRT is invoked when the device exits the RESET condition (VDD rises above BOR trip point). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay is designed to allow VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT for the POR only. For a BOR the PWRT is always available regardless of the configuration bit setting.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

#### 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on a power-up type RESET or a wake-up from SLEEP.

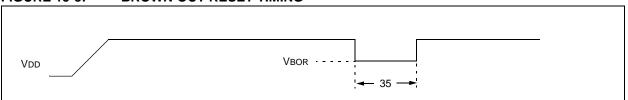

# 12.7 Programmable Brown-Out Reset (PBOR)

The Programmable Brown-out Reset module is used to generate a RESET when the supply voltage falls below a specified trip voltage. The trip voltage is configurable to any one of four voltages provided by the BORV<1:0> configuration word bits.

Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below the specified trip point for longer than TBOR, (parameter #35), the brown-out situation will RESET the chip. A RESET may not occur if VDD falls below the trip point for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer will be invoked at that point and will keep the chip in RESET an additional TPWRT. If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will again begin a TPWRT time delay. Even though the PWRT is always enabled when brown-out is enabled, the PWRT configuration word bit should be cleared (enabled) when brown-out is enabled.

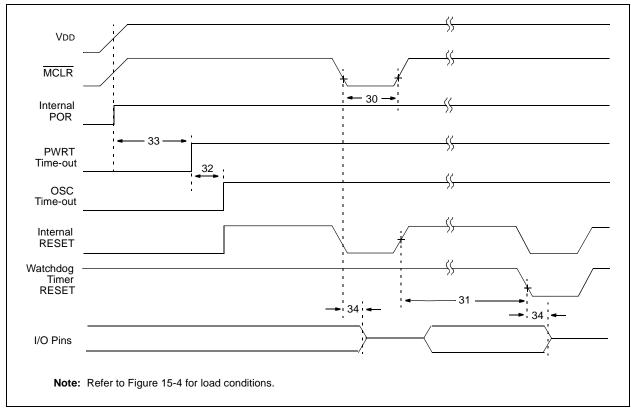

FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 12-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 12-9: SLOW VDD RISE TIME (MCLR TIED TO VDD)

#### 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

TABLE 14-1: DEVELOPMENT TOOLS FROM MICROCHIP

\* \* +

DC CHARACTERISTICS

# 15.2 DC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$  +125°C for extended

Operating voltage VDD range as described in Section 15.1 and

Section 15.2.

|                 | Section 15.2.              |                                                                           |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-----------------|----------------------------|---------------------------------------------------------------------------|---------------------------------------------------|------|------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Param.          | . Sym                      | Characteristic                                                            | Min                                               | Typ† | Max                    | Units                | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| No.             |                            |                                                                           |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 |                            | Input Low Voltage                                                         |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 | VIL                        | I/O ports                                                                 |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| D030            |                            | with TTL buffer                                                           | Vss                                               | _    | 0.15VDD                | V                    | For entire VDD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| D030A           |                            |                                                                           | Vss                                               | _    | V8.0                   | V                    | $4.5V \le VDD \le 5.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| D031            |                            | with Schmitt Trigger buffer                                               | Vss                                               | _    | 0.2Vdd                 | V                    | For entire VDD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| D032            |                            | MCLR                                                                      | Vss                                               | _    | 0.2Vdd                 | V                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| D033            |                            | OSC1 (in XT, HS, LP and EC)                                               | Vss                                               | _    | 0.3VDD                 | V                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 |                            | Input High Voltage                                                        |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 | VIH                        | I/O ports                                                                 |                                                   | _    |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 |                            | with TTL buffer                                                           |                                                   |      |                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| D040            |                            |                                                                           | 2.0                                               | _    | Vdd                    | V                    | $4.5V \le VDD \le 5.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |