Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 15                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc771t-i-so |

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 2-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7 |       |       |     |     |       |       | bit 0 |

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP<1:0>: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4 TO: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD:** Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

**Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

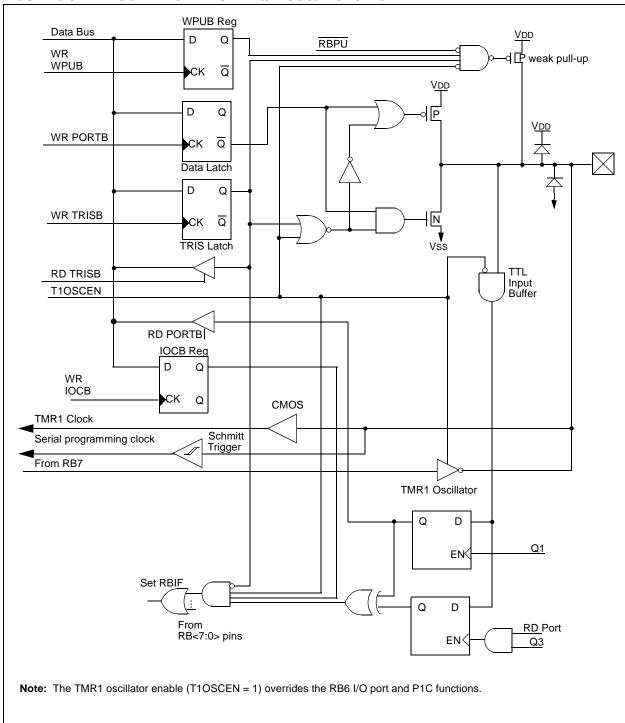

FIGURE 3-9: BLOCK DIAGRAM OF RB6/T10S0/T1CKI/P1C

## REGISTER 4-2: PROGRAM MEMORY DATA HIGH (PMDATH: 10Eh)

| U-0   | U-0     | R-x | R-x   | R-x   | R-x  | R-x  | R-x   |

|-------|---------|-----|-------|-------|------|------|-------|

| _     | — PMD13 |     | PMD12 | PMD11 | PMD9 | PMD8 |       |

| bit 7 |         |     |       |       |      |      | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

Legend:  $R = Readable \ bit \qquad W = Writable \ bit \qquad U = Unimplemented \ bit, \ read \ as \ '0' \\ -n = Value \ at \ POR \qquad '1' = Bit \ is \ set \qquad '0' = Bit \ is \ cleared \qquad x = Bit \ is \ unknown$

### REGISTER 4-3: PROGRAM MEMORY DATA LOW (PMDATL: 10Ch)

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| PMD7  | PMD6 | PMD5 | PMD4 | PMD3 | PMD2 | PMD1 | PMD0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

# REGISTER 4-4: PROGRAM MEMORY ADDRESS HIGH (PMADRH: 10Fh)

| U-0   | U-0 | U-0 | U-0   | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | -   - |       | PMA10 | PMA9  | PMA8  |

| bit 7 |     |     |       |       |       |       | bit 0 |

bit 7-4 Unimplemented: Read as '0' bit 3-0 PMA<11:8>: PMR Address bits

### REGISTER 4-5: PROGRAM MEMORY ADDRESS LOW (PMADRL: 10Dh)

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMA7  | PMA6  | PMA5  | PMA4  | PMA3  | PMA2  | PMA1  | PMA0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

### bit 7-0 **PMA<7:0>:** PMR Address bits

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 6.2 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 6-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type | Freq    | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

### These values are for design guidance only.

- **Note 1:** Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

## 6.3 Timer1 Interrupt

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

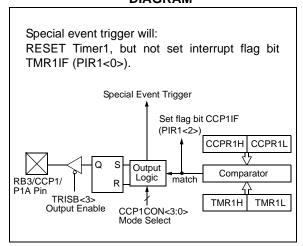

# 6.4 Resetting Timer1 using a CCP Trigger Output

If the ECCP module is configured in Compare mode to generate a "special event trigger" (CCP1M<3:0> = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The spe                                | cial e | vent | trigg | ers from th | ne CC | P1 |  |  |  |

|-------|----------------------------------------|--------|------|-------|-------------|-------|----|--|--|--|

|       | module will not set interrupt flag bit |        |      |       |             |       |    |  |  |  |

|       | TMR1IF                                 | (PIR   | 1<0> | ).    |             |       |    |  |  |  |

Timer1 must be configured for either timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from ECCP, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7         | Bit 6       | Bit 5          | Bit 4           | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|---------------|-------------|----------------|-----------------|---------------|-------------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE           | PEIE        | TOIE           | INTE            | RBIE          | TOIF        | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | _             | ADIF        | ı              | ı               | SSPIF         | CCP1IF      | TMR2IF | TMR1IF | -0 0000                  | -0 0000                         |

| 8Ch                   | PIE1   | _             | ADIE        | I              | I               | SSPIE         | CCP1IE      | TMR2IE | TMR1IE | -0 0000                  | -0 0000                         |

| 0Eh                   | TMR1L  | Holding regis | ster for th | ne Least Signi | ificant Byte of | the 16-bit TM | R1 register |        |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding regis | ster for th |                | xxxx xxxx       | uuuu uuuu     |             |        |        |                          |                                 |

| 10h                   | T1CON  | _             | _           | T1CKPS1        | T1CKPS0         | T10SCEN       | T1SYNC      | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only an ECCP interrupt is generated (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of ECCP resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of ECCP module will also start an A/D conversion if the A/D module is enabled.

**Note:** The special event trigger will not set the interrupt flag bit TMR1IF (PIR1<0>).

# FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Name    | Bit 7                | Bit 6            | Bit 5          | t 5 Bit 4 B                     |               | Bit 2                | Bit 1     | Bit 0      | Value on<br>POR,<br>BOR | Value on all other RESETS |

|---------|----------------------|------------------|----------------|---------------------------------|---------------|----------------------|-----------|------------|-------------------------|---------------------------|

| INTCON  | GIE                  | PEIE             | TOIE           | INTE                            | RBIE          | E TOIF INTF          |           | RBIF       | 0000 000x               | 0000 000u                 |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF             | RCIF           | TXIF                            | SSPIF         | CCP1IF TMR2IF TMR1IF |           | TMR1IF     | 0000 0000               | 0000 0000                 |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE             | RCIE           | TXIE SSPIE CCP1IE TMR2IE TMR1IE |               | TMR1IE               | 0000 0000 | 0000 0000  |                         |                           |

| TRISB   | PORTB Data           | a Direction Re   | gister         |                                 |               |                      |           |            | 1111 1111               | 1111 1111                 |

| TMR1L   | Holding regis        | ster for the Lea | ast Significar | nt Byte of the                  | e 16-bit TMR1 | register             |           |            | xxxx xxxx               | uuuu uuuu                 |

| TMR1H   | Holding regis        | ster for the Mo  | st Significan  | t Byte of the                   | 16-bit TMR1r  | egister              |           |            | xxxx xxxx               | uuuu uuuu                 |

| T1CON   | ı                    | ı                | T1CKPS<br>1    | T1CKP<br>S0                     | T1OSCEN       | T1SYNC               | TMR1CS    | TMR10<br>N | 00 0000                 | uu uuuu                   |

| CCPR1L  | Capture/Cor          | npare/PWM re     | gister1 (LSB   | 3)                              |               |                      |           |            | xxxx xxxx               | uuuu uuuu                 |

| CCPR1H  | Capture/Cor          | npare/PWM re     | gister1 (MSE   | 3)                              |               | •                    | •         |            | xxxx xxxx               | uuuu uuuu                 |

| CCP1CON | PWM1M1               | PWM1M0           | DC1B1          | DC1B0                           | CCP1M3        | CCP1M2               | CCP1M1    | CCP1M0     | 0000 0000               | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

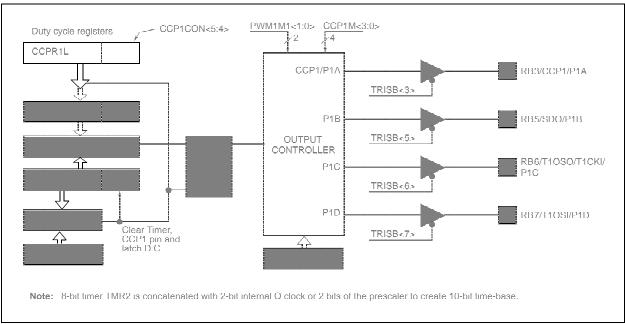

#### 8.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the ECCP module produces up to a 10-bit resolution PWM output. Figure 8-3 shows the simplified PWM block diagram.

FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 7.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## REGISTER 9-2: SYNC SERIAL PORT CONTROL REGISTER (SSPCON: 14h) (CONTINUED)

bit 3-0 SSPM<3:0>: Synchronous Serial Port Mode Select bits 0000 = SPI Master mode, clock = Fosc/4 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64 0011 = SPI Master mode, clock = TMR2 output/2 0100 = SPI Slave mode, clock = SCK pin. SS pin control enabled. 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin.  $0110 = I^2C$  Slave mode, 7-bit address  $0111 = I^2C$  Slave mode, 10-bit address 1000 =  $I^2C$  Master mode, clock = Fosc / (4 • (SSPADD+1)) 1001 = Reserved 1010 = Reserved 1011 = Firmware controlled Master mode (slave idle) 1100 = Reserved 1101 = Reserved 1110 = 7-bit Slave mode with START and STOP condition interrupts

1111 = 10-bit Slave mode with START and STOP condition interrupts

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 9.1.7 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from SLEEP. After the device returns to Normal mode, the module will continue to transmit/receive data.

In Slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in SLEEP mode and data to be shifted into the SPI transmit/receive shift register. When all eight bits have been received, the SSPIF interrupt flag bit will be set and if enabled will wake the device from SLEEP.

#### 9.1.8 EFFECTS OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7 | Bit 6   | Bit 5      | Bit 4     | Bit 3        | Bit 2         | Bit 1    | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|-------|---------|------------|-----------|--------------|---------------|----------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE   | PEIE    | TOIE       | INTE      | RBIE         | TOIF          | INTF     | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | -     | ADIF    | _          | _         | SSPIF        | CCP1IF        | TMR2IF   | TMR1IF | -0 0000   | -0 0000   |

| 8Ch                    | PIE1    | -     | ADIE    | _          | _         | SSPIE        | CCP1IE        | TMR2IE   | TMR1IE | -0 0000   | -0 0000   |

| 13h                    | SSPBUF  |       | Synchro | nous Seria | I Port Re | eceive Buffe | er/Transmit F | Register |        | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL  | SSPOV   | SSPEN      | CKP       | SSPM3        | SSPM2         | SSPM1    | SSPM0  | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP   | CKE     | D/A        | Р         | S            | R/W           | UA       | BF     | 0000 0000 | 0000 0000 |

| 9Dh                    | ANSEL   |       |         |            |           |              |               |          |        | 11 1111   | 11 1111   |

| 86h                    | TRISB   |       |         |            |           |              |               |          |        | 1111 1111 | 1111 1111 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the MSSP in SPI mode.

# PIC16C717/770/771

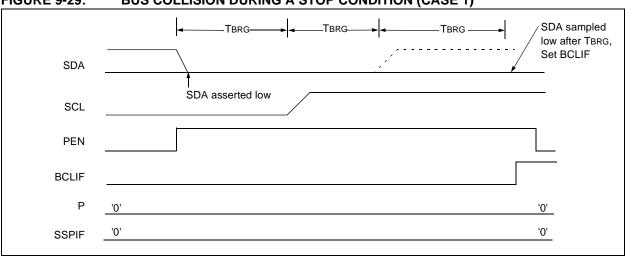

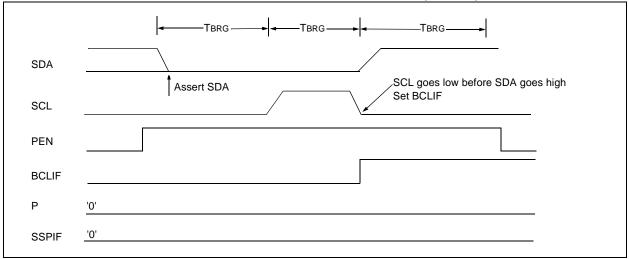

# 9.2.17.3 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to '0'. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 9-29). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 9-30).

FIGURE 9-29: BUS COLLISION DURING A STOP CONDITION (CASE 1)

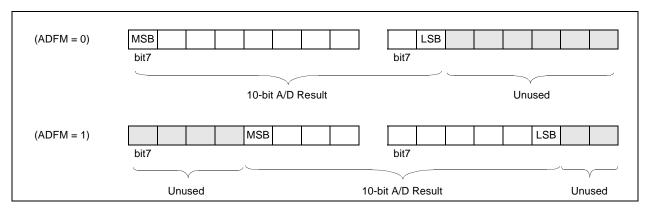

FIGURE 11-2: PIC16C717 10-BIT A/D RESULT FORMAT

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS and ANSEL bits selected as an input. To determine acquisition time, see Section 11.6. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

# 11.2 Configuring the A/D Module

# 11.2.1 CONFIGURING ANALOG PORT PINS

The ANSEL and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted. The proper ANSEL bits must be set (analog input) to disable the digital input buffer.

The A/D operation is independent of the state of the TRIS bits and the ANSEL bits.

- **Note 1:** When reading the PORTA register, all pins configured as analog input channels will read as '0'.

- 2: When reading the PORTB register, all pins configured as analog pins on PORTB will be read as '1'.

- 3: Analog levels on any pin that is defined as a digital input, including the ANx pins, may cause the input buffer to consume current that is out of the devices specification.

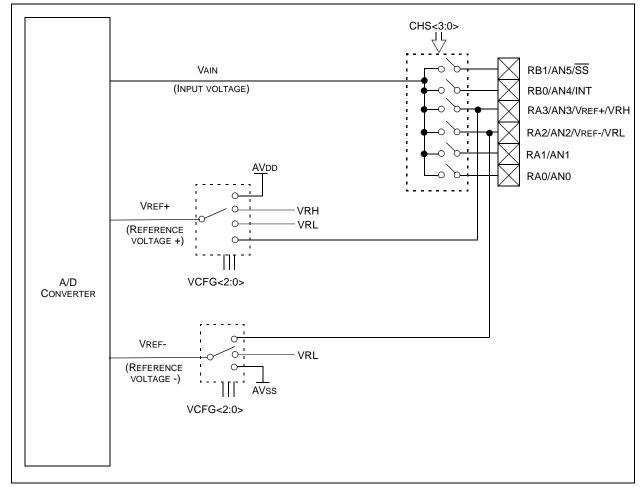

# 11.2.2 CONFIGURING THE REFERENCE VOLTAGES

The VCFG bits in the ADCON1 register configure the A/D module reference inputs. The reference high input can come from an internal reference (VRH) or (VRL), an external reference (VREF+), or AVDD. The low reference input can come from an internal reference (VRL), an external reference (VREF-), or AVSS. If an external reference is chosen for the reference high or reference low inputs, the port pin that multiplexes the incoming external references is configured as an analog input, regardless of the values contained in the A/D port configuration bits (PCFG<3:0>).

After the A/D module has been configured as desired and the analog input channels have their corresponding TRIS bits selected for port inputs, the selected channel must be acquired before conversion is started. The A/D conversion cycle can be initiated by setting the GO/DONE bit. The A/D conversion begins and lasts for 13TAD. The following steps should be followed for performing an A/D conversion:

- 1. Configure port pins:

- Configure Analog Input mode (ANSEL)

- Configure pin as input (TRISA or TRISB)

- 2. Configure the A/D module

- Configure A/D Result Format / voltage reference (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 3. Configure A/D interrupt (if required)

- · Clear ADIF bit

- · Set ADIE bit

- · Set PEIE bit

- · Set GIE bit

- 4. Wait the required acquisition time.

- 5. START conversion

Note:

- Set GO/DONE bit (ADCON0)

- Wait 13TAD until A/D conversion is complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- · Waiting for the A/D interrupt

- 7. Read A/D Result registers (ADRESH and ADRESL), clear ADIF if required.

- 8. For next conversion, go to step 1, step 2 or step 3 as required.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRESH and ADRESL registers will be updated with the partially completed A/D conversion value. That is, the ADRESH and ADRESL registers will contain the value of the current incomplete conversion.

Do not set the ADON bit and the GO/DONE bit in the same instruction. Doing so will cause the GO/DONE bit to be automatically cleared.

FIGURE 11-3: A/D BLOCK DIAGRAM

# 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming™ protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

# 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

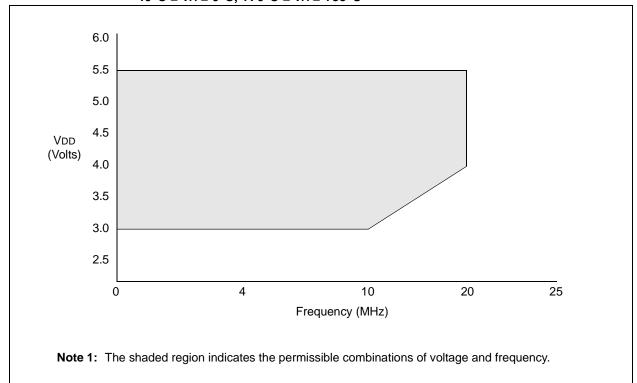

FIGURE 15-3: PIC16LC717/770/771 VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}\text{C} \leq \text{Ta} \leq 0^{\circ}\text{C}, \ +70^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$

# 15.1 DC Characteristics: PIC16C717/770/771 (Commercial, Industrial, Extended) PIC16LC717/770/771 (Commercial, Industrial, Extended)

| PIC16LC717/770/771        |      |                                                            |      | Standard Operating Conditions (unless otherwise stated) Operating temperature $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for extended |     |       |                                                            |  |  |  |

|---------------------------|------|------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------------|--|--|--|

| PIC16C717/770/771         |      |                                                            |      | tandard Operating Conditions (unless otherwise stated) perating temperature $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for extended   |     |       |                                                            |  |  |  |

| Param. Sym Characteristic |      |                                                            |      | Тур†                                                                                                                                                                                                                                                                                                              | Max | Units | Conditions                                                 |  |  |  |

| D001                      | VDD  | Supply Voltage                                             | 2.5  | _                                                                                                                                                                                                                                                                                                                 | 5.5 | V     |                                                            |  |  |  |

| D001                      | VDD  | Supply Voltage                                             | 4.0  | _                                                                                                                                                                                                                                                                                                                 | 5.5 | V     |                                                            |  |  |  |

| D002*                     | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup>               | _    | 1.5                                                                                                                                                                                                                                                                                                               |     | V     |                                                            |  |  |  |

| D002*                     | VDR  | RAM Data Retention Voltage <sup>(1)</sup>                  | _    | 1.5                                                                                                                                                                                                                                                                                                               | 1   | V     |                                                            |  |  |  |

| D003*                     | VPOR | VDD start voltage to ensure internal Power-on Reset signal | _    | Vss                                                                                                                                                                                                                                                                                                               | 1   | V     | See section on Power-on Reset for details                  |  |  |  |

| D003*                     | VPOR | VDD start voltage to ensure internal Power-on Reset signal | _    | Vss                                                                                                                                                                                                                                                                                                               | I   | V     | See section on Power-on Reset for details                  |  |  |  |

| D004*                     | SVDD | VDD rise rate to ensure internal Power-on Reset signal     | 0.05 | _                                                                                                                                                                                                                                                                                                                 | _   | V/ms  | See section on Power-on Reset for details.<br>PWRT enabled |  |  |  |

| D004*                     | SVDD | VDD rise rate to ensure internal Power-on Reset signal     | 0.05 | _                                                                                                                                                                                                                                                                                                                 | ı   | V/ms  | See section on Power-on Reset for details.<br>PWRT enabled |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 15.3 AC Characteristics: PIC16C717/770/771 & PIC16LC717/770/771 (Commercial, Industrial, Extended)

#### 15.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2 | opS       | 3. Tcc:st | (I <sup>2</sup> C specifications only) |  |

|----------|-----------|-----------|----------------------------------------|--|

| 2. TppS  |           | 4. Ts     | (I <sup>2</sup> C specifications only) |  |

| Т        |           |           |                                        |  |

| F        | Frequency | Т         | Time                                   |  |

Lowercase letters (pp) and their meanings:

1. TppS2ppS

| pp |               |     |          |

|----|---------------|-----|----------|

| CC | CCP1          | osc | OSC1     |

| ck | CLKOUT        | rd  | RD       |

| cs | <del>CS</del> | rw  | RD or WR |

| di | SDI           | SC  | SCK      |

| do | SDO           | SS  | SS       |

| dt | Data in       | t0  | TOCKI    |

| io | I/O port      | t1  | T1CKI    |

| mc | MCLR          | wr  | WR       |

|    |               |     |          |

Uppercase letters and their meanings:

| S                                       |                                                         |   |              |  |

|-----------------------------------------|---------------------------------------------------------|---|--------------|--|

| F                                       | Fall                                                    | Р | Period       |  |

| Н                                       | High                                                    | R | Rise         |  |

| 1                                       | Invalid (Hi-impedance)                                  | V | Valid        |  |

| L                                       | Low                                                     | Z | Hi-impedance |  |

| <b>I<sup>2</sup>C</b> (I <sup>2</sup> C | I <sup>2</sup> C (I <sup>2</sup> C specifications only) |   |              |  |

| AA                                      | AA output access                                        |   |              |  |

| BUF                                     | Bus free                                                |   |              |  |

| High                                    | High                                                    |   |              |  |

| Low                                     | Low                                                     |   |              |  |

Tcc:st (I<sup>2</sup>C specifications only)

| CC  |                 |     |                |

|-----|-----------------|-----|----------------|

| HD  | Hold            | SU  | Setup          |

| ST  |                 |     |                |

| DAT | DATA input hold | STO | STOP condition |

| STA | START condition |     |                |

# 15.3.2 TIMING DIAGRAMS AND SPECIFICATIONS

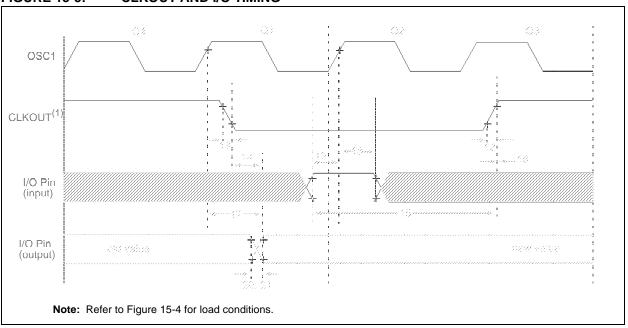

FIGURE 15-5: CLKOUT AND I/O TIMING

TABLE 15-1: CLKOUT AND I/O TIMING REQUIREMENTS

| Param. | Sym      | Characteristic                        |                             | Min          | Typ† | Max         | Unit   | Conditions |

|--------|----------|---------------------------------------|-----------------------------|--------------|------|-------------|--------|------------|

| No.    |          |                                       |                             |              |      |             | S      |            |

| 12*    | TckR     | CLKOUT rise time                      | _                           | 35           | 100  | ns          | Note 1 |            |

| 13*    | TckF     | CLKOUT fall time                      |                             | _            | 35   | 100         | ns     | Note 1     |

| 14*    | TckL2ioV | CLKOUT ↓ to Port out v                | alid                        | _            | _    | 0.5Tcy + 20 | ns     | Note 1     |

| 15*    | TioV2ckH | Port in valid before CLK              | OUT ↑                       | 0.25Tcy + 25 | _    | _           | ns     | Note 1     |

| 16*    | TckH2iol | Port in hold after CLKO               | UT ↑                        | 0            | _    | _           | ns     | Note 1     |

| 17*    | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid |                             | _            | 50   | 150         | ns     |            |

| 18*    | TosH2iol | (                                     | PIC16 <b>C</b> 717/770/771  | 100          | _    | _           | ns     |            |

|        |          | Port input invalid (I/O in hold time) | PIC16 <b>LC</b> 717/770/771 | 200          | _    | _           | ns     |            |

| 19*    | TioV2osH | Port input valid to OSC1              | ↑ (I/O in setup time)       | 0            | _    | _           | ns     |            |

| 20*    | TioR     | Port output rise time                 | PIC16 <b>C</b> 717/770/771  | _            | 10   | 25          | ns     |            |

|        |          |                                       | PIC16 <b>LC</b> 717/770/771 | _            | _    | 60          | ns     |            |

| 21*    | TioF     | Port output fall time                 | PIC16 <b>C</b> 717/770/771  | _            | 10   | 25          | ns     |            |

|        |          |                                       | PIC16 <b>LC</b> 717/770/771 | _            | _    | 60          | ns     |            |

| 22††*  | Tinp     | INT pin high or low time              | TCY                         | _            | _    | ns          |        |            |

| 23††*  | Trbp     | RB<7:0> change INT hi                 | Tcy                         | _            | _    | ns          |        |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken ER or INTRC w/CLKOUT mode where CLKOUT output is 4 x Tosc.

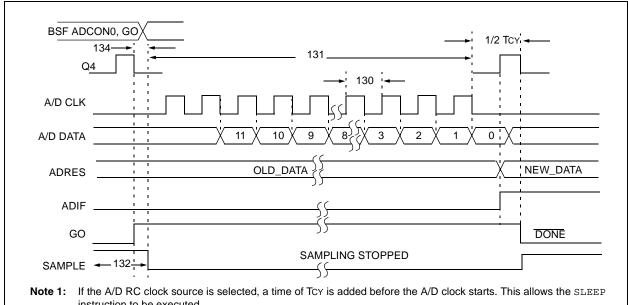

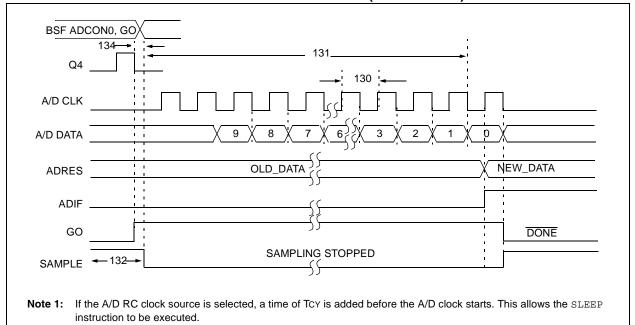

FIGURE 15-14: PIC16C770/771 AND PIC16LC770/771 A/D CONVERSION TIMING (NORMAL MODE)

FIGURE 15-17: PIC16C717 A/D CONVERSION TIMING (SLEEP MODE)

TABLE 15-16: PIC16C717 AND PIC16LC717 A/D CONVERSION REQUIREMENT (SLEEP MODE)

| Parameter No.       | Sym  | Characteristic                                            | Min      | Тур†         | Max | Units | Conditions                                                                                                                                                                                              |

|---------------------|------|-----------------------------------------------------------|----------|--------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130* <sup>(3)</sup> | TAD  | A/D clock period                                          | 3.0      | 6.0          | 9.0 | μS    | ADCS<1:0> = 11 (A/D RC mode)<br>At VDD = 3.0V                                                                                                                                                           |

|                     |      |                                                           | 2.0      | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                           |

| 131*                | TCNV | Conversion time (not including acquisition time) (Note 1) | _        | 11TAD        | 1   | _     |                                                                                                                                                                                                         |

| 132*                | TACQ | Acquisition Time                                          | (Note 2) | 11.5         |     | μS    |                                                                                                                                                                                                         |

|                     |      |                                                           | 5*       | _            | 1   | μѕ    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1LSb (i.e., 1mV @ 4.096V) from the last sampled voltage (as stated on CHOLD). |

| 134*                | Tgo  | Q4 to A/D clock start                                     | _        | Tosc/2 + Tcy | ı   | _     | If the A/D RC clock source is selected, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                           |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TcY cycle.

- 2: See Section 11.6 for minimum conditions.

- ${\bf 3:}\ \ \,$  These numbers multiplied by 8 if VRH or VRL is selected as A/D reference.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

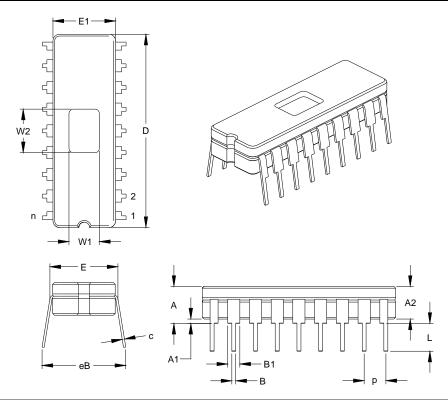

# 17.3 18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |     | INCHES* |      | MILLIMETERS |       |       |       |

|----------------------------|-----|---------|------|-------------|-------|-------|-------|

| Dimension                  | MIN | NOM     | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins             | n   |         | 18   |             |       | 18    |       |

| Pitch                      | р   |         | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | Α   | .170    | .183 | .195        | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2  | .155    | .160 | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1  | .015    | .023 | .030        | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е   | .300    | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1  | .285    | .290 | .295        | 7.24  | 7.37  | 7.49  |

| Overall Length             | D   | .880    | .900 | .920        | 22.35 | 22.86 | 23.37 |

| Tip to Seating Plane       | L   | .125    | .138 | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С   | .008    | .010 | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1  | .050    | .055 | .060        | 1.27  | 1.40  | 1.52  |

| Lower Lead Width           | В   | .016    | .019 | .021        | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing        | eВ  | .345    | .385 | .425        | 8.76  | 9.78  | 10.80 |

| Window Width               | W1  | .130    | .140 | .150        | 3.30  | 3.56  | 3.81  |

| Window Length              | W2  | .190    | .200 | .210        | 4.83  | 5.08  | 5.33  |

\*Controlling Parameter JEDEC Equivalent: MO-036 Drawing No. C04-010