Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 50MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | POR, PWM, WDT                                                     |

| Number of I/O              | 21                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | 512 x 8                                                           |

| RAM Size                   | 1K x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | -                                                                 |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f371-a-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 29.2. Timer Settings for Standard Baud Rates   |     |

|------------------------------------------------------|-----|

| Using an External 22.1184 MHz Oscillator             | 227 |

| Table 30.1. SPI Slave Timing Parameters              | 241 |

| Table 32.1. PCA Timebase Input Options               | 276 |

| Table 32.2. PCA0CPM and PCA0PWM Bit Settings for PCA |     |

| Capture/Compare Modules                              | 278 |

| Table 32.3. Watchdog Timer Timeout Intervals1        | 287 |

| SFR Definition 32.3. PCA0PWM: PCA PWM Configuration              | 292 |

|------------------------------------------------------------------|-----|

| SFR Definition 32.4. PCA0CLR: PCA Comparator Clear Control       |     |

| SFR Definition 32.5. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR Definition 32.6. PCA0L: PCA Counter/Timer Low Byte           | 295 |

| SFR Definition 32.7. PCA0H: PCA Counter/Timer High Byte          | 295 |

| SFR Definition 32.8. PCA0CPLn: PCA Capture Module Low Byte       | 296 |

| SFR Definition 32.9. PCA0CPHn: PCA Capture Module High Byte      | 296 |

| C2 Register Definition 33.1. C2ADD: C2 Address                   | 297 |

| C2 Register Definition 33.2. DEVICEID: C2 Device ID              | 298 |

| C2 Register Definition 33.3. REVID: C2 Revision ID               | 298 |

| C2 Register Definition 33.4. FPCTL: C2 Flash Programming Control | 299 |

| C2 Register Definition 33.5. FPDAT: C2 Flash Programming Data    | 299 |

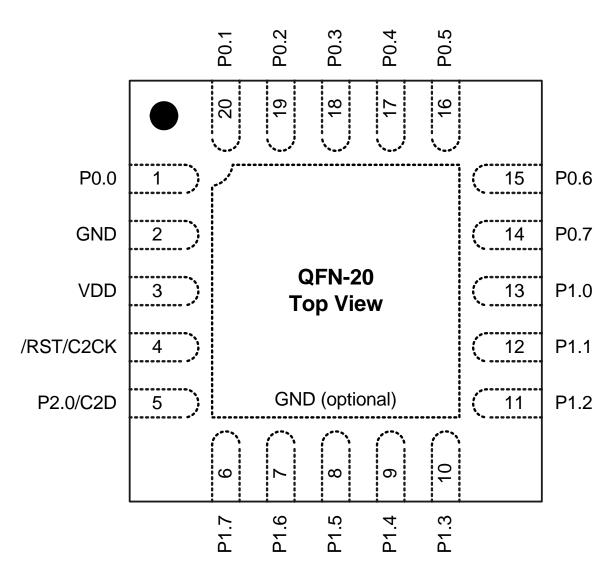

Figure 4.1. C8051F392/3/6/7/8/9 QFN-20 Pinout Diagram (Top View)

**Table 7.16. Comparator Electrical Characteristics (Continued)** V<sub>DD</sub> = 3.0 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), unless otherwise specified.

| Parameter                                         | Test Condition          | Min   | Тур   | Max                    | Unit |

|---------------------------------------------------|-------------------------|-------|-------|------------------------|------|

| Negative Hysteresis                               | CP0HYN1-0 = 00          | _     | 1.6   | 2.3                    | mV   |

| Mode 3 (CPMD = 11)                                | CP0HYN1-0 = 01          | -6    | -4    | -2                     | mV   |

|                                                   | CP0HYN1-0 = 10          | -11   | -8    | -4.8                   | mV   |

|                                                   | CP0HYN1-0 = 11          | -21   | -15.5 | -10                    | mV   |

| Inverting or Non-Inverting Input<br>Voltage Range |                         | -0.25 |       | V <sub>DD</sub> + 0.25 | V    |

| Input Capacitance                                 |                         | _     | 4     | —                      | pF   |

| Input Bias Current                                |                         | —     | 0.001 | —                      | nA   |

| Input Offset Voltage                              |                         | 10    | —     | -10                    | mV   |

| Power Supply                                      |                         |       |       |                        |      |

| Power Supply Rejection                            |                         | —     | 0.1   | —                      | mV/V |

| Power-up Time                                     |                         | —     | 6.5   | —                      | μs   |

| Supply Current at DC                              | Mode 0                  | —     | 32    | 50                     | μA   |

|                                                   | Mode 1                  | —     | 15    | 25                     | μA   |

|                                                   | Mode 2                  | —     | 5     | 12                     | μA   |

|                                                   | Mode 3                  | —     | 2     | 8                      | μA   |

| Note: Vcm is the common-mode vc                   | Itage on CP0+ and CP0–. |       |       |                        |      |

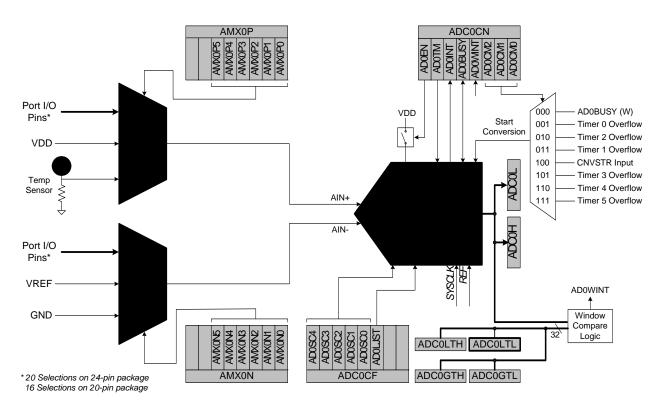

# 9. 10-Bit ADC (ADC0, C8051F390/2/4/6/8 and C8051F370/4 Only)

ADC0 on the C8051F390/2/4/6/8 and C8051F370/4 is a 500 ksps, 10-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and a programmable window detector. The ADC is fully configurable under software control via Special Function Registers. The ADC may be configured to measure various different signals using the analog multiplexer described in Section "9.4. ADC0 Analog Multiplexer (C8051F390/2/4/6/8 and C8051F370/4 Only)" on page 61. The voltage reference for the ADC is selected as described in Section "12. Voltage Reference Options" on page 73. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 9.1. ADC0 Functional Block Diagram

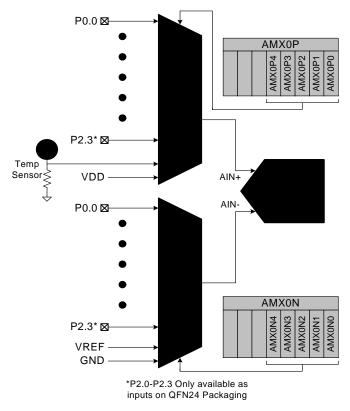

### 9.4. ADC0 Analog Multiplexer (C8051F390/2/4/6/8 and C8051F370/4 Only)

ADC0 on the C8051F390/2/4/6/8 and C8051F370/4 has two analog multiplexers, referred to collectively as AMUX0.

AMUX0 selects the positive and negative inputs to the ADC. Any of the following may be selected as the positive input: Port I/O pins, the on-chip temperature sensor, or the positive power supply ( $V_{DD}$ ). Any of the following may be selected as the negative input: Port I/O pins,  $V_{REF}$ , or GND. When GND is selected as the negative input, ADC0 operates in Single-ended Mode; all other times, ADC0 operates in Differential Mode. The ADC0 input channels are selected in the AMX0P and AMX0N registers as described in SFR Definition 9.9 and SFR Definition 9.10.

Figure 9.6. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to '0' the corresponding bit in register PnMDIN. To force the Crossbar to skip a Port pin, set to '1' the corresponding bit in register PnSKIP. See Section "27. Port Input/Output" on page 173 for more Port I/ O configuration details.

# SFR Definition 12.1. REF0CN: Reference Control

| Bit   | 7      | 6 | 5 | 4      | 3     | 2     | 1     | 0     |

|-------|--------|---|---|--------|-------|-------|-------|-------|

| Name  | REFBGS |   |   | REGOVR | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R/W    | R | R | R/W    | R/W   | R/W   | R/W   | R/W   |

| Reset | 0      | 0 | 0 | 0      | 0     | 0     | 0     | 0     |

SFR Address = 0xD1; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REFBGS | <ul> <li>Reference Buffer Gain Select.</li> <li>This bit selects between 1x and 2x gain for the on-chip voltage reference buffer.</li> <li>0: 2x Gain</li> <li>1: 1x Gain</li> </ul>                                                                                                                           |

| 6:5 | Unused | Read = 00b; Write = Don't care.                                                                                                                                                                                                                                                                                |

| 4   | REGOVR | <ul> <li>Regulator Reference Override.</li> <li>This bit "overrides" the REFSL bit, and allows the internal regulator to be used as a reference source.</li> <li>0: The voltage reference source is selected by the REFSL bit.</li> <li>1: The internal regulator is used as the voltage reference.</li> </ul> |

| 3   | REFSL  | <ul> <li>Voltage Reference Select.</li> <li>This bit selects the ADCs voltage reference.</li> <li>0: V<sub>REF</sub> pin used as voltage reference.</li> <li>1: V<sub>DD</sub> used as voltage reference.</li> </ul>                                                                                           |

| 2   | TEMPE  | Temperature Sensor Enable Bit.0: Internal Temperature Sensor off.1: Internal Temperature Sensor on.                                                                                                                                                                                                            |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on.                                                                                                                                                                                                |

| 0   | REFBE  | <ul> <li>On-chip Reference Buffer Enable Bit.</li> <li>0: On-chip Reference Buffer off.</li> <li>1: On-chip Reference Buffer on. Internal voltage reference driven on the V<sub>REF</sub> pin.</li> </ul>                                                                                                      |

# 13. Voltage Regulator

C8051F39x/37x devices include an internal regulator that regulates the internal core supply from a  $V_{DD}$  supply of 1.8 to 3.6 V. The regulator has two power-saving modes built in to help reduce current consumption in low-power applications. These modes are accessed through the REGOCN register.

#### 13.1. Power Modes

Under default conditions, the internal regulator will remain on when the device enters STOP mode. This allows any enabled reset source to generate a reset for the device and bring the device out of STOP mode. For additional power savings, the STOPCF bit can be used to shut down the regulator and the internal power network of the device when the part enters STOP mode. When STOPCF is set to 1, the RST pin and a full power cycle of the device are the only methods of generating a reset.

## SFR Definition 13.1. REG0CN: Voltage Regulator Control

| Bit   | 7   | 6 | 5 | 4 | 3      | 2 | 1   | 0 |

|-------|-----|---|---|---|--------|---|-----|---|

| Name  |     |   |   |   | STOPCF |   |     |   |

| Туре  | R/W |   |   |   | R/W    |   | R/W |   |

| Reset | 0   | 0 | 0 | 0 | 0      | 0 | 0   | 0 |

SFR Address = 0xC9; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                      |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved | Must Write 0000b.                                                                                                                                                                                                                                                                                             |

| 3   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                                                      |

|     |          | <ul> <li>This bit configures the regulator's behavior when the device enters STOP mode.</li> <li>0: Regulator is still active in STOP mode. Any enabled reset source will reset the device.</li> <li>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset the device.</li> </ul> |

| 2:0 | Reserved | Must Write 000b.                                                                                                                                                                                                                                                                                              |

# SFR Definition 14.3. CPT0MX: Comparator0 MUX Selection

| Bit   | 7          | 6 | 5 | 4 | 3          | 2  | 1 | 0 |  |

|-------|------------|---|---|---|------------|----|---|---|--|

| Name  | CMX0N[3:0] |   |   |   | CMX0P[3:0] |    |   |   |  |

| Туре  | R/W        |   |   |   |            | R/ | W |   |  |

| Reset | 1          | 1 | 1 | 1 | 1          | 1  | 1 | 1 |  |

SFR Address = 0x9F; SFR Page = All Pages

| Bit | Name       | Function         |                                           |  |  |  |  |

|-----|------------|------------------|-------------------------------------------|--|--|--|--|

| 7:4 | CMX0N[3:0] | Comparator0 Nega | ative Input MUX Selection.                |  |  |  |  |

|     |            | 0000:            | P0.1                                      |  |  |  |  |

|     |            | 0001:            | P0.3                                      |  |  |  |  |

|     |            | 0010:            | P0.5                                      |  |  |  |  |

|     |            | 0011:            | P0.7                                      |  |  |  |  |

|     |            | 0100:            | P1.1                                      |  |  |  |  |

|     |            | 0101:            | P1.3                                      |  |  |  |  |

|     |            | 0110:            | P1.5                                      |  |  |  |  |

|     |            | 0111:            | P1.7                                      |  |  |  |  |

|     |            | 1000:            | P2.1 (C8051F390/1/4/5 and C8051F37x Only) |  |  |  |  |

|     |            | 1001:            | P2.3 (C8051F390/1/4/5 and C8051F37x Only) |  |  |  |  |

|     |            | 1010-1111:       | None                                      |  |  |  |  |

| 3:0 | CMX0P[3:0] | Comparator0 Posi | tive Input MUX Selection.                 |  |  |  |  |

|     |            | 0000:            | P0.0                                      |  |  |  |  |

|     |            | 0001:            | P0.2                                      |  |  |  |  |

|     |            | 0010:            | P0.4                                      |  |  |  |  |

|     |            | 0011:            | P0.6                                      |  |  |  |  |

|     |            | 0100:            | P1.0                                      |  |  |  |  |

|     |            | 0101:            | P1.2                                      |  |  |  |  |

|     |            | 0110:            | P1.4                                      |  |  |  |  |

|     |            | 0111:            | P1.6                                      |  |  |  |  |

|     |            | 1000:            | P2.0 (C8051F390/1/4/5 and C8051F37x Only) |  |  |  |  |

|     |            | 1001:            | P2.2 (C8051F390/1/4/5 and C8051F37x Only) |  |  |  |  |

|     |            | 1010-1111:       | None                                      |  |  |  |  |

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 15.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

#### 26.5.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 26.1, "RC Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in  $k\Omega$ .

$$f = 1.23 \times 10^3 / (R \times C)$$

#### Equation 26.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>) / RC = 1.23 (10<sup>3</sup>) / [246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 26.5, the required XFCN setting is 010b.

#### 26.5.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 26.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation , where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

$$f = (KF)/(C \times V_{DD})$$

#### Equation 26.2. C Mode Oscillator Frequency

For example: Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 26.5 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

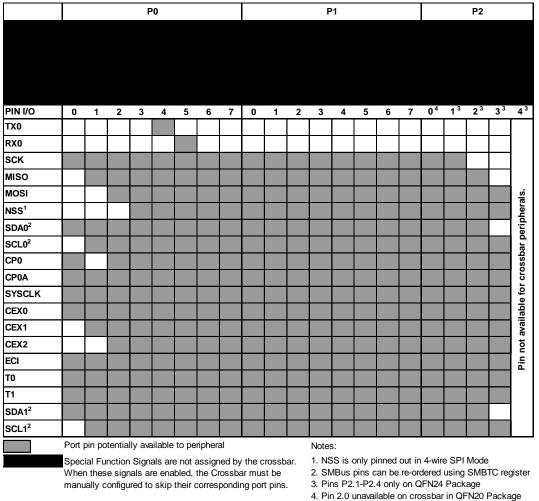

### 27.3. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 27.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC or IDAC is configured to use the external conversion start signal (CNVSTR), and any selected ADC or Comparator inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin.

Figure 27.3 shows all of the potential peripheral-to-pin assignments available to the crossbar. Note that this does not mean any peripheral can always be assigned to the highlighted pins. The actual pin assignments are determined by the priority of the enabled peripherals.

5. C8051F37x only

### Figure 27.3. Crossbar Priority Decoder - Possible Pin Assignments

### 27.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = '1').

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 27.8 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to '1' enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

# SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7     | 6     | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|-------|-------|-------|------|--------|-------|-------|-------|

| Name  | EEPUE | SMB1E | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R/W   | R/W   | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0     | 0     | 0     | 0    | 0      | 0     | 0     | 0     |

SFR Address = 0xE1; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                         |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 7   | EEPUE  | EEPROM Pullup Enable.                                                                                                            |

|     |        | <ul><li>0: On-chip strong pullups not active.</li><li>1: On-chip strong pullups active on pins P2.2 and P2.3.</li></ul>          |

| 6   | SMB1E  | SMBus1 I/O Enable.                                                                                                               |

|     |        | <ul><li>0: SMBus1 I/O unavailable at Port pins.</li><li>1: SMBus1 I/O routed to Port pins.</li></ul>                             |

| 5   | CP0AE  | Comparator0 Asynchronous Output Enable.                                                                                          |

|     |        | <ul><li>0: Asynchronous CP0 unavailable at Port pin.</li><li>1: Asynchronous CP0 routed to Port pin.</li></ul>                   |

| 4   | CP0E   | Comparator0 Output Enable.                                                                                                       |

|     |        | 0: CP0 unavailable at Port pin.                                                                                                  |

|     |        | 1: CP0 routed to Port pin.                                                                                                       |

| 3   | SYSCKE | /SYSCLK Output Enable.                                                                                                           |

|     |        | 0: /SYSCLK unavailable at Port pin.                                                                                              |

|     |        | 1: /SYSCLK output routed to Port pin.                                                                                            |

| 2   | SMB0E  | SMBus0 I/O Enable.                                                                                                               |

|     |        | 0: SMBus0 I/O unavailable at Port pins.                                                                                          |

| 1   |        | 1: SMBus0 I/O routed to Port pins.                                                                                               |

| 1   | SPIOE  | SPI I/O Enable.                                                                                                                  |

|     |        | <ul><li>0: SPI I/O unavailable at Port pins.</li><li>1: SPI I/O routed to Port pins. Note that the SPI can be assigned</li></ul> |

|     |        | either 3 or 4 GPIO pins.                                                                                                         |

| 0   | URT0E  | UART I/O Output Enable.                                                                                                          |

|     |        | 0: UART I/O unavailable at Port pin.                                                                                             |

|     |        | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5.                                                                              |

# SFR Definition 28.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7      | 6    | 5     | 4        | 3       | 2       | 1           | 0 |

|-------|--------|------|-------|----------|---------|---------|-------------|---|

| Name  | ENSMB0 | INH0 | BUSY0 | EXTHOLD0 | SMB0TOE | SMB0FTE | SMB0CS[1:0] |   |

| Туре  | R/W    | R/W  | R     | R/W      | R/W     | R/W     | R/W         |   |

| Reset | 0      | 0    | 0     | 0        | 0       | 0       | 0           | 0 |

SFR Address = 0xC1; SFR Page = 0

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB0      | <b>SMBus0 Enable.</b><br>This bit enables the SMBus0 interface when set to 1. When enabled, the interface constantly monitors the SDA0 and SCL0 pins.                                                                                                                                                                                                                                                                                                                                    |

| 6   | INHO        | <b>SMBus0 Slave Inhibit.</b><br>When this bit is set to logic 1, the SMBus0 does not generate an interrupt when slave events occur. This effectively removes the SMBus0 slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                                     |

| 5   | BUSY0       | <b>SMBus0 Busy Indicator.</b><br>This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                                  |

| 4   | EXTHOLD0    | <ul> <li>SMBus0 Setup and Hold Time Extension Enable.</li> <li>This bit controls the SDA0 setup and hold times according to Table 28.2.</li> <li>0: SDA0 Extended Setup and Hold Times disabled.</li> <li>1: SDA0 Extended Setup and Hold Times enabled.</li> </ul>                                                                                                                                                                                                                      |

| 3   | SMB0TOE     | SMBus0 SCL Timeout Detection Enable.<br>This bit enables SCL low timeout detection. If set to logic 1, the<br>SMBus0 forces Timer 3 to reload while SCL0 is high and allows<br>Timer 3 to count when SCL0 goes low. If Timer 3 is configured to<br>Split Mode, only the High Byte of the timer is held in reload while<br>SCL0 is high. Timer 3 should be programmed to generate interrupts<br>at 25 ms, and the Timer 3 interrupt service routine should reset<br>SMBus0 communication. |

| 2   | SMB0FTE     | SMBus0 Free Timeout Detection Enable.<br>When this bit is set to logic 1, the bus will be considered free if SCL0<br>and SDA0 remain high for more than 10 SMBus clock source peri-<br>ods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMB0CS[1:0] | SMBus0 Clock Source Selection.These two bits select the SMBus0 clock source, which is used to<br>generate the SMBus0 bit rate. The selected device should be config-<br>ured according to Equation 28.1.00: Timer 0 Overflow01: Timer 1 Overflow10: Timer 2 High Byte Overflow11: Timer 2 Low Byte Overflow                                                                                                                                                                              |

Table 28.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Continued)

|                 | Valu               | es F  | Rea                   | d                           |                                  |                                              |   | lues<br>Vrit |     | Status<br>Expected     |

|-----------------|--------------------|-------|-----------------------|-----------------------------|----------------------------------|----------------------------------------------|---|--------------|-----|------------------------|

| Mode            | Status<br>Vector   | ACKRQ | ARBLOST               | ACK                         | Current SMbus State              | Current SMbus State Typical Response Options |   | STO          | ACK | Next Sta<br>Vector Exp |

| uo              | 0010               | 0 1 X | 1 X                   | x                           | Lost arbitration while attempt-  | Abort failed transfer.                       | 0 | 0            | Х   | —                      |

| diti            |                    |       | ing a repeated START. | Reschedule failed transfer. | 1                                | 0                                            | Х | 1110         |     |                        |

| Con             | 0001               | 0     | 1                     | x                           | Lost arbitration due to a        | Abort failed transfer.                       | 0 | 0            | Х   | _                      |

| Error Condition | <b>b</b>           | 0     | 1                     | ^                           | detected STOP.                   | Reschedule failed transfer.                  | 1 | 0            | Х   | 1110                   |

|                 | <b>B</b><br>0000 1 | 1     | 1                     | x                           | Lost arbitration while transmit- | Abort failed transfer.                       | 0 | 0            | 0   | —                      |

| Bu              |                    |       |                       | ^                           | ting a data byte as master.      | Reschedule failed transfer.                  | 1 | 0            | 0   | 1110                   |

## Table 28.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1)

| â                  | v               | Values Read                       |      |     | d  |                                    |                                                                                                                        |                                 | ues<br>Vrit     |                               | Status<br>Expected                                 |   |   |   |   |

|--------------------|-----------------|-----------------------------------|------|-----|----|------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|-------------------------------|----------------------------------------------------|---|---|---|---|

| Mode               | Status          | Vector<br>ACKRQ<br>ACKRQ<br>ACKRQ |      |     |    | Current SMbus State                | Typical Response Options                                                                                               | STA                             | STO             | ACK                           | Next Status<br>Vector Expect                       |   |   |   |   |

|                    | 11 <sup>.</sup> | 10                                | 0    | 0   | х  | A master START was gener-<br>ated. | Load slave address + R/W into SMB0DAT.                                                                                 | 0                               | 0               | Х                             | 1100                                               |   |   |   |   |

|                    | r.              |                                   | _    | _   | _  | A master data or address byte      | Set STA to restart transfer.                                                                                           | 1                               | 0               | Х                             | 1110                                               |   |   |   |   |

| er.                |                 |                                   |      |     | 0  | 0                                  | 0                                                                                                                      | was transmitted; NACK received. | Abort transfer. | 0                             | 1                                                  | Х | — |   |   |

| smitte             |                 |                                   |      |     |    | _                                  | Load next data byte into<br>SMB0DAT.                                                                                   | 0                               | 0               | Х                             | 1100                                               |   |   |   |   |

| ran                |                 |                                   |      |     |    |                                    | End transfer with STOP.                                                                                                | 0                               | 1               | Х                             | —                                                  |   |   |   |   |

| Master Transmitter | 110             | 100                               | 1100 | 100 | 00 |                                    | 0                                                                                                                      | 0                               | 1               | A master data or address byte | End transfer with STOP and start another transfer. | 1 | 1 | Х | — |

| Ë                  |                 |                                   | •    | Ū   |    | received.                          | Send repeated START.                                                                                                   | 1                               | 0               | Х                             | 1110                                               |   |   |   |   |

|                    |                 |                                   |      |     |    |                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0                               | 0               | 1                             | 1000                                               |   |   |   |   |

# SFR Definition 31.2. CKCON1: Clock Control 1

| Bit   | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|-------|---|---|---|---|------|------|------|------|

| Name  |   |   |   |   | T5MH | T5ML | T4MH | T4ML |

| Туре  | R | R | R | R | R/W  | R/W  | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0    | 0    | 0    | 0    |

SFR Address = 0xF4; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused | Read = 0000b; Write = don't care                                                                                                                                                                                                                                                                                                                          |

| 3   | T5MH   | <ul> <li>Timer 5 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 5 high byte (split 8-bit timer mode only).</li> <li>0: Timer 5 high byte uses the clock defined by the T5XCLK bit in TMR5CN.</li> <li>1: Timer 5 high byte uses the system clock.</li> </ul>                                                                    |

| 2   | T5ML   | <ul> <li>Timer 5 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 5. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 5 low byte uses the clock defined by the T5XCLK bit in TMR5CN.</li> <li>1: Timer 5 low byte uses the system clock.</li> </ul>                                    |

| 1   | T4MH   | <ul> <li>Timer 4 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 4 high byte (split 8-bit timer mode only).</li> <li>0: Timer 4 high byte uses the clock defined by the T4XCLK bit in TMR4CN.</li> <li>1: Timer 4 high byte uses the system clock.</li> </ul>                                                                    |

| 0   | T4ML   | <ul> <li>Timer 4 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 4. If Timer 4 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 4 low byte uses the clock defined by the T4XCLK bit in TMR4CN.</li> <li>1: Timer 4 low byte uses the system clock.</li> </ul> |

# SFR Definition 31.14. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1           | 0 |

|-------|------|------|--------|--------|---------|-----|-------------|---|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 | T3XCLK[1:0] |   |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R/W         |   |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0           | 0 |

SFR Address = 0x91; SFR Page = 0

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H        | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                             |

| 6   | TF3L        | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |             | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                                                                                          |

| 5   | TF3LEN      | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |             | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                                                                                                     |

| 4   | TF3CEN      | Timer 3 Low-Frequency Oscillator Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | When set to 1, this bit enables Timer 3 Low-Frequency Oscillator Capture Mode. If TF3CEN is set and Timer 3 interrupts are enabled, an interrupt will be generated on a falling edge of the low-frequency oscillator output, and the current 16-bit timer value in TMR3H:TMR3L will be copied to TMR3RLH:TMR3RLL.                                                                                                                                                                                                                                               |

| 3   | T3SPLIT     | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |             | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.<br>0: Timer 3 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |             | 1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2   | TR3         | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |             | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1:0 | T3XCLK[1:0] | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |             | This bit selects the "external" clock source for Timer 3. If Timer 3 is in 8-bit mode,<br>this bit selects the external oscillator clock source for both timer bytes. However,<br>the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be<br>used to select between the external clock and the system clock for either timer.<br>00: System clock divided by 12.<br>01: External clock divided by 8 (synchronized with SYSCLK when not in suspend).<br>10: Reserved.<br>11: Internal LFO/8 (synchronized with SYSCLK when not in suspend). |

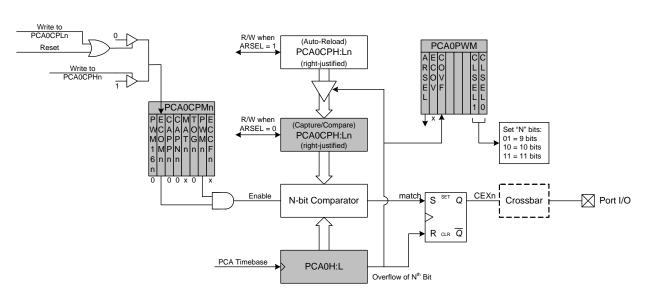

#### 32.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/ compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 32.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 32.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 32.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 32.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

# SFR Definition 32.2. PCA0MD: PCA Mode

| Bit   | 7    | 6    | 5     | 4 | 3    | 2    | 1    | 0   |

|-------|------|------|-------|---|------|------|------|-----|

| Name  | CIDL | WDTE | WDLCK |   | CPS2 | CPS1 | CPS0 | ECF |

| Туре  | R/W  | R/W  | R/W   | R | R/W  | R/W  | R/W  | R/W |

| Reset | 0    | 1    | 0     | 0 | 0    | 0    | 0    | 0   |

SFR Address = 0xD9; SFR Page = All Pages

| Bit | Name      | Function                                                                                                                                |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CIDL      | PCA Counter/Timer Idle Control.                                                                                                         |

|     |           | Specifies PCA behavior when CPU is in Idle Mode.                                                                                        |

|     |           | 0: PCA continues to function normally while the system controller is in Idle Mode.                                                      |

|     |           | 1: PCA operation is suspended while the system controller is in Idle Mode.                                                              |

| 6   | WDTE      | Watchdog Timer Enable.                                                                                                                  |

|     |           | If this bit is set, PCA Module 2 is used as the watchdog timer.                                                                         |

|     |           | 0: Watchdog Timer disabled.                                                                                                             |

|     |           | 1: PCA Module 2 enabled as Watchdog Timer.                                                                                              |

| 5   | WDLCK     | Watchdog Timer Lock.                                                                                                                    |

|     |           | This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set,                                                                    |

|     |           | the Watchdog Timer may not be disabled until the next system reset.                                                                     |

|     |           | 0: Watchdog Timer Enable unlocked.<br>1: Watchdog Timer Enable locked.                                                                  |

| 4   | Unused    | Unused. Read = 0b, Write = Don't care.                                                                                                  |

| 3:1 | CPS[2:0]  | PCA Counter/Timer Pulse Select.                                                                                                         |

| 0.1 | 01 0[2.0] | These bits select the timebase source for the PCA counter                                                                               |

|     |           | 000: System clock divided by 12                                                                                                         |

|     |           | 001: System clock divided by 4                                                                                                          |

|     |           | 010: Timer 0 overflow                                                                                                                   |

|     |           | 011: High-to-low transitions on ECI (max rate = system clock divided by 4)                                                              |

|     |           | 100: System clock                                                                                                                       |

|     |           | 101: External clock divided by 8 (synchronized with the system clock)                                                                   |

|     |           | 110: Low frequency oscillator divided by 8<br>111: Reserved                                                                             |

| 0   | ECF       |                                                                                                                                         |

| 0   | ECF       | PCA Counter/Timer Overflow Interrupt Enable.                                                                                            |

|     |           | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.<br>0: Disable the CF interrupt.                             |

|     |           | 1: Enable a PCA Counter/Timer Overflow interrupt request when CF                                                                        |

|     |           | (PCA0CN.7) is set.                                                                                                                      |

|     |           | et to 1, the other bits in the PCA0MD register cannot be modified. To change the D register, the Watchdog Timer must first be disabled. |