Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                              |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 21                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | 512 x 8                                                          |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f375-a-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 32.3. PCA0PWM: PCA PWM Configuration              | 292 |

|------------------------------------------------------------------|-----|

| SFR Definition 32.4. PCA0CLR: PCA Comparator Clear Control       |     |

| SFR Definition 32.5. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR Definition 32.6. PCA0L: PCA Counter/Timer Low Byte           | 295 |

| SFR Definition 32.7. PCA0H: PCA Counter/Timer High Byte          | 295 |

| SFR Definition 32.8. PCA0CPLn: PCA Capture Module Low Byte       | 296 |

| SFR Definition 32.9. PCA0CPHn: PCA Capture Module High Byte      | 296 |

| C2 Register Definition 33.1. C2ADD: C2 Address                   | 297 |

| C2 Register Definition 33.2. DEVICEID: C2 Device ID              | 298 |

| C2 Register Definition 33.3. REVID: C2 Revision ID               | 298 |

| C2 Register Definition 33.4. FPCTL: C2 Flash Programming Control | 299 |

| C2 Register Definition 33.5. FPDAT: C2 Flash Programming Data    | 299 |

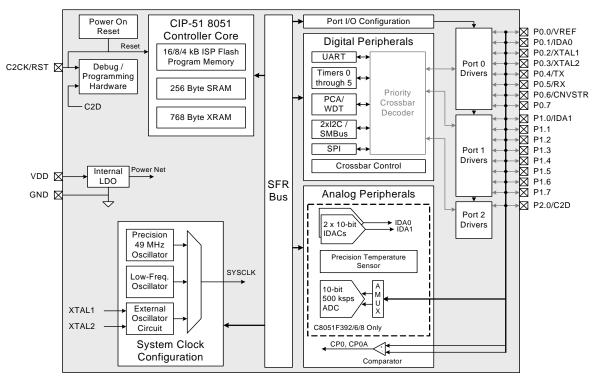

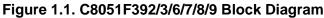

## 1. System Overview

C8051F39x/37x devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Section "2. Ordering Information" on page 20 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- True 10-bit 500 ksps 20 or 16-channel single-ended/differential ADC with analog multiplexer

- Two 10-bit Current Output DACs

- Precision temperature sensor with ±2 °C absolute accuracy

- Precision programmable 49 MHz internal oscillator

- Low-power, low-frequency oscillator

- 16 kB of on-chip Flash memory

- 1024 bytes of on-chip RAM

- Co-packaged with 512 bytes of EEPROM memory, accessible via I<sup>2</sup>C (C8051F37x)

- Two SMBus/I<sup>2</sup>C, UART, and SPI serial interfaces implemented in hardware

- Six general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with three capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Temperature Sensor

- On-chip Voltage Comparator

- 21 or 17 Port I/O

- Low-power suspend mode with fast wake-up time

With on-chip Power-On Reset, V<sub>DD</sub> monitor, Watchdog Timer, and clock oscillator, the C8051F39x/37x devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

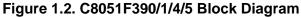

The C8051F37x devices are specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C), while the C8051F39x devices operate over an extended temperature range (-40 to +105 °C). The C8051F392/3/6/7/8/9 are available in a 20-pin QFN package and the C8051F390/1/4/5 and C8051F37x are available in a 24-pin QFN package. Both package options are lead-free and RoHS compliant. See Section "2. Ordering Information" on page 20 for ordering information. Block diagrams are included in Figure 1.1, Figure 1.2 and Figure 1.3.

Figure 4.3. C8051F370/1/4/5 Pinout Diagram (Top View)

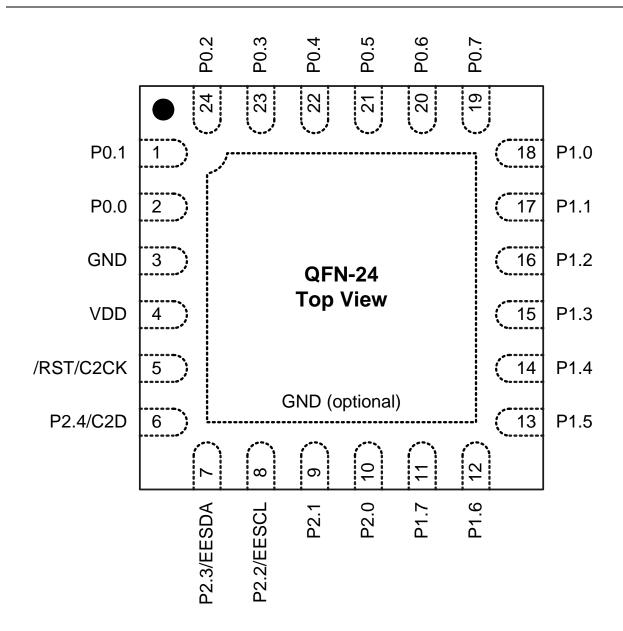

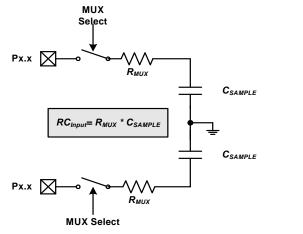

#### 9.2.3. Settling Time Requirements

A minimum tracking time is required before each conversion to ensure that an accurate conversion is performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 9.3 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 9.1. See Table 7.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL}C_{SAMPLE}$$

#### Equation 9.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance. *n* is the ADC resolution in bits (10).

### **Differential Mode**

## Single-Ended Mode

#### Figure 9.3. ADC0 Equivalent Input Circuits

## SFR Definition 11.1. IDA0CN: IDA0 Control

| Bit   | 7      | 6           | 5 | 4 | 3 | 2      | 1      | 0       |

|-------|--------|-------------|---|---|---|--------|--------|---------|

| Name  | IDA0EN | IDA0CM[2:0] |   |   |   | IDA0RP | IDA0OI | MD[1:0] |

| Туре  | R/W    | R/W         |   |   | R | R/W    | R/     | W       |

| Reset | 0      | 1           | 1 | 1 | 0 | Varies | 1      | 0       |

SFR Address = 0xB9; SFR Page = 0

| Bit | Name          | Function                                                                      |

|-----|---------------|-------------------------------------------------------------------------------|

| 7   | <b>IDA0EN</b> | IDA0 Enable.                                                                  |

|     |               | 0: IDA0 Disabled.<br>1: IDA0 Enabled.                                         |

|     |               |                                                                               |

| 6:4 | IDA0CM[2:0]   | IDA0 Update Source Select bits.                                               |

|     |               | 000: DAC output updates on Timer 0 overflow.                                  |

|     |               | 001: DAC output updates on Timer 1 overflow.                                  |

|     |               | 010: DAC output updates on Timer 2 overflow.                                  |

|     |               | 011: DAC output updates on Timer 3 overflow.                                  |

|     |               | 100: DAC output updates on rising edge of CNVSTR.                             |

|     |               | 101: DAC output updates on falling edge of CNVSTR.                            |

|     |               | 110: DAC output updates on any edge of CNVSTR.                                |

|     |               | 111: DAC output updates on write to IDA0H.                                    |

| 3   | Reserved      | Write = 0b.                                                                   |

| 2   | IDA0RP        | IDA0 Reset Persistence.                                                       |

|     |               | 0: IDA0 is disabled by any reset source.                                      |

|     |               | 1: IDA0 will remain enabled through any reset source except a power-on-reset. |

|     |               | This bit is reset to 0 by a power on reset, but is sticky                     |

|     |               | through all other reset sources. When setting IDA0RP to 1,                    |

|     |               | IDA0EN must be set to 1 also in the same mov instruction.                     |

| 1:0 | IDA0OMD[1:0]  | IDA0 Output Mode Select bits.                                                 |

|     |               | 00: 0.5 mA full-scale output current.                                         |

|     |               | 01: 1.0 mA full-scale output current.                                         |

|     |               | 1x: 2.0 mA full-scale output current.                                         |

## SFR Definition 14.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3           | 2 | 1           | 0 |

|-------|-------|--------|--------|--------|-------------|---|-------------|---|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0HYP[1:0] |   | CP0HYN[1:0] |   |

| Туре  | R/W   | R      | R/W    | R/W    | R/W         |   | R/          | W |

| Reset | 0     | 0      | 0      | 0      | 0           | 0 | 0           | 0 |

SFR Address = 0x9B; SFR Page = All Pages

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0–.                                                    |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

### Table 15.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic                    | Description                                | Bytes | Clock<br>Cycles |  |

|-----------------------------|--------------------------------------------|-------|-----------------|--|

| XRL direct, #data           | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A                       | Clear A                                    | 1     | 1               |  |

| CPL A                       | Complement A                               | 1     | 1               |  |

| RL A                        | Rotate A left                              | 1     | 1               |  |

| RLC A                       | Rotate A left through Carry                | 1     | 1               |  |

| RR A                        | Rotate A right                             | 1     | 1               |  |

| RRC A                       | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A                      | Swap nibbles of A                          | 1     | 1               |  |

| Data Transfer               |                                            |       |                 |  |

| MOV A, Rn                   | Move Register to A                         | 1     | 1               |  |

| MOV A, direct               | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri                  | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data                | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A                   | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct              | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data               | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A               | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn              | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct          | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri             | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data           | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A                  | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct             | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data              | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16           | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR             | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC               | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri                 | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A                 | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR               | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A               | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct                 | Push direct byte onto stack                | 2     | 2               |  |

| POP direct                  | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn                   | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct               | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri                  | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri                 | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

| <b>Boolean Manipulation</b> |                                            |       |                 |  |

| CLR C                       | Clear Carry                                | 1     | 1               |  |

| CLR bit                     | Clear direct bit                           | 2     | 2               |  |

| SETB C                      | Set Carry                                  | 1     | 1               |  |

| SETB bit                    | Set direct bit                             | 2     | 2               |  |

| CPL C                       | Complement Carry                           | 1     | 1               |  |

| CPL bit                     | Complement direct bit                      | 2     | 2               |  |

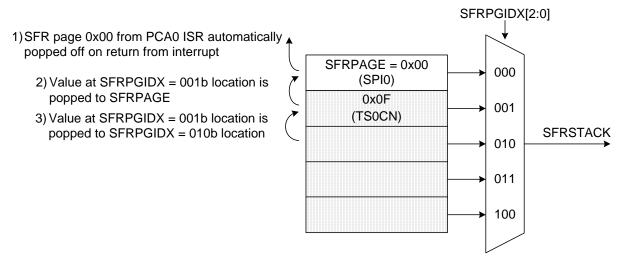

On exit from the PCA0 interrupt service routine, the CIP-51 will return to the SPI0 ISR. On execution of the RETI instruction, SFR page 0x00 used to access the PCA0 registers will be automatically popped off of the SFR page stack, and the contents at the SFRPGIDX = 001b location will be moved to the SFRPAGE register. Software in the SPI0 ISR can continue to access SFRs as it did prior to the PCA interrupt. Likewise, the contents at the SFRPGIDX = 010b location are moved to the SFRPGIDX = 001b location. Recall this was the SFR Page value 0x0F being used to access TS0CN before the SPI0 interrupt occurred. See Figure 19.5.

Figure 19.5. SFR Page Stack Upon Return from PCA0 Interrupt

### SFR Definition 19.3. SFRSTACK: SFR Page Stack

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|----------|---|---|---|---|---|---|--|

| Name  |   | SFRSTACK |   |   |   |   |   |   |  |

| Туре  | R |          |   |   |   |   |   |   |  |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xD3; SFR Page = F

| Bit | Name     | Function                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRSTACK | SFR Page Stack.                                                                                                                                                   |

|     |          | This register is used to access the contents of the SFR page stack. SFRPGIDX in the SFRPGCN register controls which level of the stack this register will access. |

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flags                                                              | Bit addressable? | Cleared by HW? | Enable Flag        |

|-------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|

| Reset                         | 0x0000              | Тор               | None                                                                       | N/A              | N/A            | Always Enabled     |

| External Interrupt 0 (INT0)   | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         |

| External Interrupt 1 (INT1)   | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         |

| UART0                         | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         |

| SPI0                          | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                | N              | ESPI0 (IE.6)       |

| SMB0                          | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y                | Ν              | ESMB0 (EIE1.0)     |

| Port Match                    | 0x0043              | 8                 | None                                                                       | N/A              | N/A            | EMAT (EIE1.1)      |

| ADC0 Window Compare           | 0x004B              | 9                 | AD0WINT (ADC0CN.3)                                                         | Y                | Ν              | EWADC0<br>(EIE1.2) |

| ADC0 Conversion Com-<br>plete | 0x0053              | 10                | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0 (EIE1.3)     |

| Programmable Counter<br>Array | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)<br>COVF (PCA0PWM.6)                       | Y                | N              | EPCA0 (EIE1.4)     |

| Comparator0                   | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0 (EIE1.5)      |

| Reserved                      | 0x006B              | 13                | N/A                                                                        | N/A              | N/A            | N/A                |

| Timer 3 Overflow              | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3 (EIE1.7)       |

| SMB1                          | 0x007B              | 15                | SI (SMB0CN.0)                                                              | Y                | Ν              | ESMB0 (EIE2.0)     |

| Timer 4 Overflow              | 0x0083              | 16                | TF4H (TMR4CN.7)<br>TF4L (TMR4CN.6)                                         | Y                | Ν              | ET4 (EIE2.1)       |

| Timer 5 Overflow              | 0x008B              | 17                | TF5H (TMR5CN.7)<br>TF5L (TMR5CN.6)                                         | N                | N              | ET5 (EIE2.2)       |

| Precision Temp Sensor         | 0x0093              | 18                | TS0DN (TS0CN.6)                                                            | Ν                | Ν              | EPTS (EIE2.3)      |

#### 21.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- 1. Disable interrupts (recommended).

- 2. Erase the 512-byte Flash page containing the target location, as described in Section 21.1.2.

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 8. Clear the PSWE bit.

Steps 5–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

#### 21.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

## SFR Definition 21.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

SFR Address = 0x8F; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | PSEE   | Program Store Erase Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | Setting this bit (in combination with PSWE) allows an entire page<br>of Flash program memory to be erased. If this bit is logic 1 and<br>Flash writes are enabled (PSWE is logic 1), a write to Flash mem-<br>ory using the MOVX instruction will erase the entire page that con-<br>tains the location addressed by the MOVX instruction. The value of<br>the data byte written does not matter.<br>0: Flash program memory erasure disabled.<br>1: Flash program memory erasure enabled. |

| 0   | PSWE   | Program Store Write Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                        |

### SFR Definition 23.6. CRC0FLIP: CRC0 Bit Flip

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|---|---|---|---|---|---|---|

| Name  | CRC0FLIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W           |   |   |   |   |   |   |   |

| Reset | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x9A; SFR Page = All Pages

| Bit | Name          | Function                                                                                                                                                                                                                                                                    |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0FLIP[7:0] | CRC0 Bit Flip.                                                                                                                                                                                                                                                              |

|     |               | Any byte written to CRC0FLIP is read back in a bit-<br>reversed order, i.e., the written LSB becomes the MSB.<br>For example:<br>If 0xC0 is written to CRC0FLIP, the data read back will<br>be 0x03.<br>If 0x05 is written to CRC0FLIP, the data read back will be<br>0xA0. |

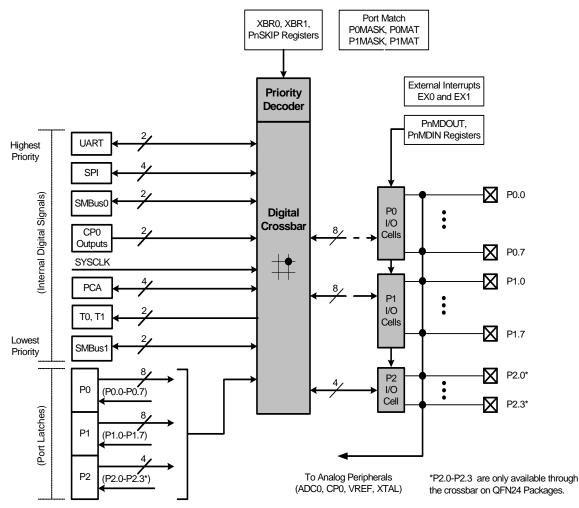

## 27. Port Input/Output

Digital and analog resources are available through 17 (C8051F392/3/6/7/8/9) or 21 (C8051F390/1/4/5 and C8051F37x) I/O pins. Port pins P0.0-P2.3 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 27.3. Port pin P2.4 on the C8051F390/1/4/5 and C8051F37x and P2.0 on the C8051F392/3/6/7/8/9 can be used as GPIO and are shared with the C2 Interface Data signal (C2D). The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 27.3 and Figure 27.4). The registers XBR0 and XBR1, defined in SFR Definition 27.1 and SFR Definition 27.2, are used to select internal digital functions.

The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Section "7. Electrical Characteristics" on page 32.

Figure 27.1. Port I/O Functional Block Diagram

### SFR Definition 27.4. P0MAT: Port 0 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | POMAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0xFD; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                         |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MAT[7:0] | Port 0 Match Value.                                                                                                                                                                              |

|     |            | Match comparison value used on Port 0 for bits in<br>P0MASK which are set to '1'.<br>0: P0.n pin logic value is compared with logic LOW.<br>1: P0.n pin logic value is compared with logic HIGH. |

### SFR Definition 27.5. P1MASK: Port 1 Mask Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P1MASK[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xEE; SFR Page = All Pages

| Bit | Name        | Function                                                                   |

|-----|-------------|----------------------------------------------------------------------------|

| 7:0 | P1MASK[7:0] | Port 1 Mask Value.                                                         |

|     |             | Selects P1 pins to be compared to the corresponding bits in P1MAT.         |

|     |             | 0: P1.n pin logic value is ignored and cannot cause a Port Mismatch event. |

|     |             | 1: P1.n pin logic value is compared to P1MAT.n.                            |

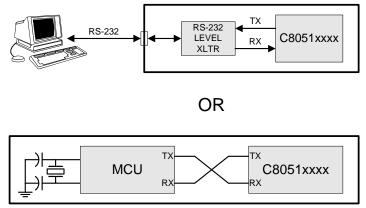

#### 29.2. Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 29.3.

Figure 29.3. UART Interconnect Diagram

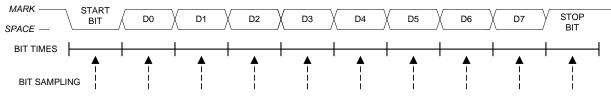

#### 29.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 29.4. 8-Bit UART Timing Diagram

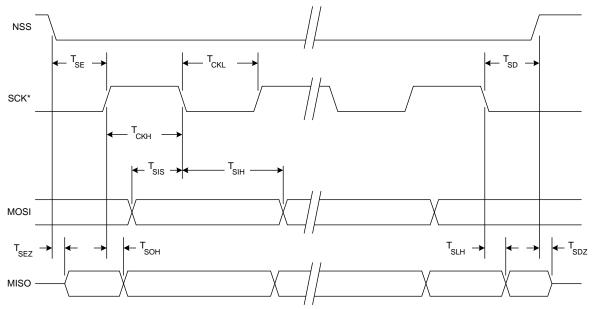

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 30.11. SPI Slave Timing (CKPHA = 1)

## 31. Timers

Each MCU includes six counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and four are 16-bit auto-reload timer for use with the SMBus or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2, 3, 4, and 5 offer 16-bit and split 8-bit timer functionality with auto-reload.

| Timer 0 and Timer 1 Modes:              | Timer 2, 3, 4, and 5 Modes:       |

|-----------------------------------------|-----------------------------------|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     |

| 16-bit counter/timer                    |                                   |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload |

| Two 8-bit counter/timers (Timer 0 only) |                                   |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 31.1 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2, 3, 4, and 5 may be clocked by the system clock, the system clock divided by 12, or the external oscillator clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

### SFR Definition 31.4. TMOD: Timer Mode

| Bit   | 7     | 6    | 5        | 4 | 3     | 2    | 1        | 0 |

|-------|-------|------|----------|---|-------|------|----------|---|

| Name  | GATE1 | C/T1 | T1M[1:0] |   | GATE0 | C/T0 | T0M[1:0] |   |

| Туре  | R/W   | R/W  | R/W      |   | R/W   | R/W  | R/       | W |

| Reset | 0     | 0    | 0        | 0 | 0     | 0    | 0        | 0 |

SFR Address = 0x89; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE1    | Timer 1 Gate Control.                                                                                                                                                                                                         |

|     |          | 0: Timer 1 enabled when TR1 = 1 irrespective of $\overline{INT1}$ logic level.<br>1: Timer 1 enabled only when TR1 = 1 AND $\overline{INT1}$ is active as defined by bit IN1PL in register IT01CF (see SFR Definition 20.10). |

| 6   | C/T1     | Counter/Timer 1 Select.                                                                                                                                                                                                       |

|     |          | <ul><li>0: Timer: Timer 1 incremented by clock defined by T1M bit in register CKCON.</li><li>1: Counter: Timer 1 incremented by high-to-low transitions on external pin (T1).</li></ul>                                       |

| 5:4 | T1M[1:0] | Timer 1 Mode Select.                                                                                                                                                                                                          |

|     |          | These bits select the Timer 1 operation mode.                                                                                                                                                                                 |

|     |          | 00: Mode 0, 13-bit Counter/Timer                                                                                                                                                                                              |

|     |          | 01: Mode 1, 16-bit Counter/Timer                                                                                                                                                                                              |

|     |          | 10: Mode 2, 8-bit Counter/Timer with Auto-Reload                                                                                                                                                                              |

|     |          | 11: Mode 3, Timer 1 Inactive                                                                                                                                                                                                  |

| 3   | GATE0    | Timer 0 Gate Control.                                                                                                                                                                                                         |

|     |          | 0: Timer 0 enabled when TR0 = 1 irrespective of $\overline{INT0}$ logic level.<br>1: Timer 0 enabled only when TR0 = 1 AND $\overline{INT0}$ is active as defined by bit IN0PL in register IT01CF (see SFR Definition 20.10). |

| 2   | C/T0     | Counter/Timer 0 Select.                                                                                                                                                                                                       |

|     |          | <ul><li>0: Timer: Timer 0 incremented by clock defined by T0M bit in register CKCON.</li><li>1: Counter: Timer 0 incremented by high-to-low transitions on external pin (T0).</li></ul>                                       |

| 1:0 | T0M[1:0] | Timer 0 Mode Select.                                                                                                                                                                                                          |

|     |          | These bits select the Timer 0 operation mode.                                                                                                                                                                                 |

|     |          | 00: Mode 0, 13-bit Counter/Timer                                                                                                                                                                                              |

|     |          | 01: Mode 1, 16-bit Counter/Timer                                                                                                                                                                                              |

|     |          | 10: Mode 2, 8-bit Counter/Timer with Auto-Reload                                                                                                                                                                              |

|     |          | 11: Mode 3, Two 8-bit Counter/Timers                                                                                                                                                                                          |