Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 50MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                        |

| Number of I/O              | 17                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 1K x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                       |

| Data Converters            | A/D 16x10b; D/A 2x10b                                             |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 20-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f396-a-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 23.4. Accessing the CRC0 Result                                     | 149 |

|---------------------------------------------------------------------|-----|

| 23.5. CRC0 Bit Reverse Feature                                      |     |

| 24. Reset Sources                                                   | 155 |

| 24.1. Power-On Reset                                                | 156 |

| 24.2. Power-Fail Reset / VDD Monitor                                | 157 |

| 24.3. External Reset                                                | 159 |

| 24.4. Missing Clock Detector Reset                                  | 159 |

| 24.5. Comparator0 Reset                                             | 159 |

| 24.6. PCA Watchdog Timer Reset                                      | 159 |

| 24.7. Flash Error Reset                                             |     |

| 24.8. Software Reset                                                | 159 |

| 25. Power Management Modes                                          | 161 |

| 25.1. Idle Mode                                                     | 161 |

| 25.2. Stop Mode                                                     | 162 |

| 25.3. Suspend Mode                                                  |     |

| 26. Oscillators and Clock Selection                                 |     |

| 26.1. System Clock Selection                                        |     |

| 26.2. Programmable Internal High-Frequency (H-F) Oscillator         |     |

| 26.2.1. Internal Oscillator Suspend Mode                            |     |

| 26.3. Programmable Internal Low-Frequency (L-F) Oscillator          |     |

| 26.3.1. Calibrating the Internal L-F Oscillator                     |     |

| 26.4. Internal Low-Power Oscillator                                 |     |

| 26.5. External Oscillator Drive Circuit                             |     |

| 26.5.1. External Crystal Mode                                       |     |

| 26.5.2. External RC Example                                         |     |

| 26.5.3. External Capacitor Example                                  |     |

| 27. Port Input/Output                                               |     |

| 27.1. Port I/O Modes of Operation                                   |     |

| 27.1.1. Port Pins Configured for Analog I/O                         |     |

| 27.1.2. Port Pins Configured For Digital I/O                        |     |

| 27.2. Assigning Port I/O Pins to Analog and Digital Functions       |     |

| 27.2.1. Assigning Port I/O Pins to Analog Functions                 |     |

| 27.2.2. Assigning Port I/O Pins to Digital Functions                |     |

| 27.2.3. Assigning Port I/O Pins to External Event Trigger Functions |     |

| 27.3. Priority Crossbar Decoder                                     |     |

| 27.4. Port I/O Initialization                                       |     |

| 27.5. Port Match                                                    |     |

| 28. SMBus0 and SMBus1 (I2C Compatible)                              |     |

| 28.1. Supporting Documents                                          |     |

| 28.2. SMBus Configuration                                           |     |

| 28.2. SMBus Operation                                               |     |

| 28.3.1. Transmitter vs. Receiver                                    |     |

| 28.3.2. Arbitration                                                 |     |

| 28.3.3. Clock Low Extension                                         |     |

|                                                                     |     |

| Figure 22.6. Selective Address Read (Single Pute)                              | 115   |

|--------------------------------------------------------------------------------|-------|

| Figure 22.6. Selective Address Read (Single Byte)                              |       |

| Figure 22.7. Selective Address Read (Multiple Bytes)                           |       |

| Figure 23.1. CRC0 Block Diagram                                                |       |

| Figure 23.2. Bit Reverse Register                                              |       |

| Figure 24.1. Reset Sources                                                     |       |

| Figure 24.2. Power-On and VDD Monitor Reset Timing                             |       |

| Figure 26.1. Oscillator Options                                                |       |

| Figure 26.2. External Crystal Example                                          |       |

| Figure 27.1. Port I/O Functional Block Diagram                                 |       |

| Figure 27.2. Port I/O Cell Block Diagram                                       |       |

| Figure 27.3. Crossbar Priority Decoder - Possible Pin Assignments              | . 178 |

| Figure 27.4. Crossbar Priority Decoder Example                                 |       |

| Figure 28.1. SMBus0 Block Diagram                                              | . 192 |

| Figure 28.2. Typical SMBus Configuration                                       | . 193 |

| Figure 28.3. SMBus Transaction                                                 | . 194 |

| Figure 28.4. Typical SMBus SCL Generation                                      | . 196 |

| Figure 28.5. Typical Master Write Sequence                                     | . 211 |

| Figure 28.6. Typical Master Read Sequence                                      |       |

| Figure 28.7. Typical Slave Write Sequence                                      | . 213 |

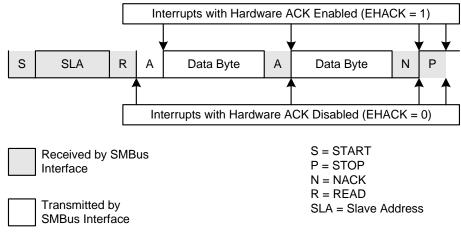

| Figure 28.8. Typical Slave Read Sequence                                       | . 214 |

| Figure 29.1. UART0 Block Diagram                                               | . 220 |

| Figure 29.2. UART0 Baud Rate Logic                                             | . 221 |

| Figure 29.3. UART Interconnect Diagram                                         |       |

| Figure 29.4. 8-Bit UART Timing Diagram                                         | . 222 |

| Figure 29.5. 9-Bit UART Timing Diagram                                         |       |

| Figure 29.6. UART Multi-Processor Mode Interconnect Diagram                    | . 224 |

| Figure 30.1. SPI Block Diagram                                                 |       |

| Figure 30.2. Multiple-Master Mode Connection Diagram                           | . 230 |

| Figure 30.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diag | Iram  |

| 231                                                                            |       |

| Figure 30.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diag   | Iram  |

| 231                                                                            |       |

| Figure 30.5. Master Mode Data/Clock Timing                                     | . 233 |

| Figure 30.6. Slave Mode Data/Clock Timing (CKPHA = 0)                          | . 233 |

| Figure 30.7. Slave Mode Data/Clock Timing (CKPHA = 1)                          |       |

| Figure 30.8. SPI Master Timing (CKPHA = 0)                                     |       |

| Figure 30.9. SPI Master Timing (CKPHA = 1)                                     | . 239 |

| Figure 30.10. SPI Slave Timing (CKPHA = 0)                                     |       |

| Figure 30.11. SPI Slave Timing (CKPHA = 1)                                     |       |

| Figure 31.1. T0 Mode 0 Block Diagram                                           |       |

| Figure 31.2. T0 Mode 2 Block Diagram                                           |       |

| Figure 31.3. T0 Mode 3 Block Diagram                                           |       |

| Figure 31.4. Timer 2 16-Bit Mode Block Diagram                                 |       |

| Figure 31.5. Timer 2 8-Bit Mode Block Diagram                                  |       |

| Figure 31.6. Timer 2 Low-Frequency Oscillation Capture Mode Block Diagram      |       |

|                                                                                |       |

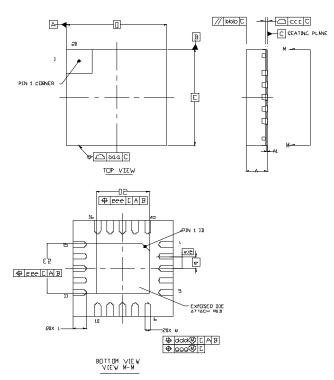

# 5. QFN-20 Package Specifications

| Dimension | Min       | Тур       | Max  | Dimension | Min  | Тур  | Ма  |

|-----------|-----------|-----------|------|-----------|------|------|-----|

| A         | 0.80      | 0.85      | 0.90 | L         | 0.50 | 0.55 | 0.6 |

| A1        | 0.00      | 0.035     | 0.05 | aaa       | —    | —    | 0.1 |

| b         | 0.20      | 0.25      | 0.30 | bbb       | —    | —    | 0.1 |

| D         | 4.00 BSC. |           |      | CCC       | —    | —    | 0.0 |

| D2        | 2.00      | 2.10      | 2.20 | ddd       | _    | —    | 0.1 |

| е         |           | 0.50 BSC. |      | eee       | _    | —    | 0.1 |

| E         | 4.00 BSC. |           |      | ggg       |      |      | 0.0 |

| E2        | 2.00      | 2.10      | 2.20 |           |      |      |     |

Table 5.1. QFN-20 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VGGD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

### Table 7.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), unless otherwise specified.

| Parameters                                                                                                          | Test Condition                                                              | Min                   | Тур                   | Мах                   | Unit     |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------|

| Standard Port I/O                                                                                                   |                                                                             |                       |                       |                       |          |

| Output High Voltage                                                                                                 | I <sub>OH</sub> = –3 mA, Port I/O push-pull                                 | V <sub>DD</sub> – 0.7 | _                     | _                     | V        |

|                                                                                                                     | I <sub>OH</sub> = –10 μA, Port I/O push-pull                                | V <sub>DD</sub> – 0.1 | —                     | _                     | V        |

|                                                                                                                     | I <sub>OH</sub> = −10 mA, Port I/O push-pull                                | —                     | V <sub>DD</sub> – 0.8 | —                     | V        |

| Output Low Voltage                                                                                                  | I <sub>OL</sub> = 8.5 mA                                                    | —                     | —                     | 0.6                   | V        |

|                                                                                                                     | I <sub>OL</sub> = 10 μA                                                     | —                     | —                     | 0.1                   | V        |

|                                                                                                                     | $I_{OL} = 10 \text{ mA}, 1.8 \text{ V} \le \text{V}_{DD} < 2.7 \text{ V}$   | —                     | 0.8                   | —                     | V        |

|                                                                                                                     | $I_{OL} = 25 \text{ mA}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$ | —                     | 1.0                   | —                     | V        |

| Input High Voltage                                                                                                  | 1.8 V ≤ V <sub>DD</sub> < 2.7 V                                             | V <sub>DD</sub> - 0.4 | —                     | _                     | V        |

|                                                                                                                     | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                | V <sub>DD</sub> – 0.5 | —                     | —                     | V        |

| Input Low Voltage                                                                                                   | 1.8 V ≤ V <sub>DD</sub> < 2.7 V                                             | —                     | —                     | 0.5                   | V        |

|                                                                                                                     | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                | —                     | —                     | 0.6                   | V        |

| Input Leakage                                                                                                       | Weak Pullup Off                                                             | —                     | —                     | ±1                    | μA       |

| Current                                                                                                             | Weak Pullup On, V <sub>IN</sub> = 0 V                                       | —                     | 20                    | 100                   | μA       |

| EESDA and EESCL                                                                                                     | (C8051F37x Only)*                                                           |                       |                       |                       |          |

| Output Low Voltage<br>(EESDA)                                                                                       | I <sub>OL</sub> = 0.15 mA, V <sub>DD</sub> = 1.8 V                          | -                     | —                     | 0.2                   | V        |

| Output Low Voltage<br>(EESDA)                                                                                       | I <sub>OL</sub> = 2.1 mA, V <sub>DD</sub> = 3 V                             | -                     | —                     | 0.4                   | V        |

| Output LeakageEEPUE = 0, $V_{DD}$ = 3.6 V,Current $0 V \le V_{OUT} \le V_{DD}$ (EESDA) $0 V \le V_{OUT} \le V_{DD}$ |                                                                             | -                     | _                     | 2                     | μA       |

| Input High Voltage                                                                                                  |                                                                             | V <sub>DD</sub> x 0.7 | —                     | _                     | V        |

| Input Low Voltage                                                                                                   |                                                                             | _                     | _                     | V <sub>DD</sub> x 0.3 | V        |

| Input Leakage EEPUE = 0, Standby, $V_{DD}$ = 3.6 V,<br>Current $0 V \le V_{IN} \le V_{DD}$                          |                                                                             | _                     | _                     | ±3                    | μA       |

| Note: Applicable when                                                                                               | interfacing to the C8051F37x EEPROM. C                                      | Otherwise, stan       | dard port I/O         | characteristics       | s apply. |

### Table 7.4. Reset Electrical Characteristics

-40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), unless otherwise specified.

| Parameter                                       | Test Condition                                                                        | Min | Тур  | Max | Unit |

|-------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

| RST Output Low Voltage                          | I <sub>OL</sub> = 4 mA,<br>V <sub>DD</sub> = 1.8 to 3.6 V                             | —   | —    | 0.6 | V    |

| RST Input Low Voltage                           |                                                                                       | —   |      | 0.6 | V    |

| RST Input Pullup Current                        | $\overline{\text{RST}} = 0.0 \text{ V}$                                               | —   | 20   | 100 | μA   |

| $V_{DD}$ POR Threshold ( $V_{RST}$ )            | V <sub>RST_LOW</sub>                                                                  | 1.7 | 1.75 | 1.8 | V    |

|                                                 | V <sub>RST_HIGH</sub>                                                                 | 2.4 | 2.55 | 2.7 | V    |

| Missing Clock Detector Time-<br>out             | Time from last system clock rising edge to reset initiation                           | 80  | 580  | 800 | μs   |

| Reset Time Delay                                | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _   | _    | 40  | μs   |

| Minimum RST Low Time to Generate a System Reset |                                                                                       | 15  | —    | _   | μs   |

| V <sub>DD</sub> Monitor Turn-on Time            |                                                                                       | 100 | _    | _   | μs   |

| V <sub>DD</sub> Monitor Supply Current          |                                                                                       | —   | 20   | 50  | μA   |

## Table 7.7. Internal High-Frequency Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), using factory-calibrated settings, unless otherwise specified.

| Parameter                                            | Test Condition                  | Min | Тур  | Max | Unit   |

|------------------------------------------------------|---------------------------------|-----|------|-----|--------|

| Oscillator Frequency                                 | C8051F390/1/2/3,<br>C8051F370/1 | 48  | 49   | 50  | MHz    |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | C8051F394/5/6/7,<br>C8051F374/5 | —   | 840  | 880 | μA     |

| Power Supply Sensitivity                             | C8051F398/9                     |     | 0.12 |     | %/V    |

| Temperature Sensitivity                              |                                 | —   | 90   |     | ppm/°C |

### Table 7.8. Internal Low-Frequency Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), using factory-calibrated settings, unless otherwise specified.

| Parameter                                            | Test Condition                  | Min | Тур  | Max | Unit   |

|------------------------------------------------------|---------------------------------|-----|------|-----|--------|

| Oscillator Frequency                                 | C8051F390/1/2/3,<br>C8051F370/1 | 75  | 80   | 85  | kHz    |

| Oscillator Supply Current<br>(from V <sub>DD</sub> ) | C8051F394/5/6/7,<br>C8051F374/5 | _   | 5.5  | 12  | μA     |

| Power Supply Sensitivity                             | C8051F398/9                     |     | 0.05 |     | %/V    |

| Temperature Sensitivity                              |                                 | —   | 160  | —   | ppm/°C |

### Table 7.9. Internal Low-Power Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), using factory-calibrated settings, unless otherwise specified.

| Parameter                | Test Condition                  | Min  | Тур | Max  | Unit   |

|--------------------------|---------------------------------|------|-----|------|--------|

| Oscillator Frequency     | C8051F390/1/2/3,<br>C8051F370/1 | 18.5 | 20  | 21.5 | MHz    |

| Power Supply Sensitivity | C8051F394/5/6/7,<br>C8051F374/5 |      | 0.1 | —    | %/V    |

| Temperature Sensitivity  | C8051F398/9                     |      | 60  |      | ppm/°C |

## SFR Definition 9.9. AMX0P: AMUX0 Positive Channel Select

| Bit   | 7 | 6 | 5 | 4 | 3          | 2 | 1 | 0 |  |  |

|-------|---|---|---|---|------------|---|---|---|--|--|

| Name  |   |   |   |   | AMX0P[4:0] |   |   |   |  |  |

| Туре  | R | R | R |   | R/W        |   |   |   |  |  |

| Reset | 0 | 0 | 0 | 1 | 1          | 1 | 1 | 1 |  |  |

SFR Address = 0xBB; SFR Page = All Pages

| Bit | Name       |                    | Function                                  |

|-----|------------|--------------------|-------------------------------------------|

| 7:5 | Unused     | Read = 000b; Write | = Don't Care.                             |

| 4:0 | AMX0P[4:0] | AMUX0 Positive Ir  | put Selection.                            |

|     |            | 00000:             | P0.0                                      |

|     |            | 00001:             | P0.1                                      |

|     |            | 00010:             | P0.2                                      |

|     |            | 00011:             | P0.3                                      |

|     |            | 00100:             | P0.4                                      |

|     |            | 00101:             | P0.5                                      |

|     |            | 00110:             | P0.6                                      |

|     |            | 00111:             | P0.7                                      |

|     |            | 01000:             | P1.0                                      |

|     |            | 01001:             | P1.1                                      |

|     |            | 01010:             | P1.2                                      |

|     |            | 01011:             | P1.3                                      |

|     |            | 01100:             | P1.4                                      |

|     |            | 01101:             | P1.5                                      |

|     |            | 01110:             | P1.6                                      |

|     |            | 01111:             | P1.7                                      |

|     |            | 10000:             | Temp Sensor                               |

|     |            | 10001:             | V <sub>DD</sub>                           |

|     |            | 10010:             | P2.0 (C8051F390/1/4/5 and C8051F37x Only) |

|     |            | 10011:             | P2.1 (C8051F390/1/4/5 and C8051F37x Only) |

|     |            | 10100:             | P2.2 (C8051F390/1/4/5 and C8051F37x Only) |

|     |            | 10101:             | P2.3 (C8051F390/1/4/5 and C8051F37x Only) |

|     |            | 10110 – 11111:     | no input selected                         |

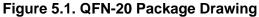

While in the SPI0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the SPI0 interrupt is configured as a low priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the value that was in the SFRPGIDX = 001b location before the PCA interrupt (in this case SFR page 0x0F for TS0CN) is pushed down to the SFRPGIDX = 010b location. Likewise, the value that was in the SFRPAGE register before the PCA interrupt (SFR page 0x00 for SPI0) is pushed down the stack into the SFRPGIDX = 001b location. Lastly, the CIP-51 will automatically places the SFR page needed to access the PCA0's special function registers into the SFRPAGE register, SFR page 0x00. See Figure 19.4.

Figure 19.4. SFR Page Stack Upon PCA Interrupt Occurring During a SPI0 ISR

## 20. Interrupts

The C8051F39x/37x includes an extended interrupt system supporting multiple interrupt sources with four priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE, EIE1, and EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears a bit to disable an interrupt should be immediately followed by an instruction that has two or more opcode bytes. Using EA (global interrupt enable) as an example:

```

// in 'C':

EA = 0; // clear EA bit.

EA = 0; // this is a dummy instruction with two-byte opcode.

; in assembly:

CLR EA ; clear EA bit.

CLR EA ; this is a dummy instruction with two-byte opcode.

```

For example, if an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears a bit to disable an interrupt source), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the enable bit will return a '0' inside the interrupt service routine. When the bit-clearing opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 21.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device. The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

### 21.4.1. $V_{DD}$ Maintenance and the $V_{DD}$ Monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- Make certain that the minimum V<sub>DD</sub> rise time specification of 1 ms is met. If <u>the system</u> cannot meet this rise time specification, then add an external V<sub>DD</sub> brownout circuit to the RST pin of the device that holds the device in reset until V<sub>DD</sub> reaches 2.7 V and re-asserts RST if V<sub>DD</sub> drops below 2.7 V.

- 3. Enable the on-chip V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For 'C'-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor and enabling the V<sub>DD</sub> monitor as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> monitor and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a '1'. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

### 21.4.2. PSWE Maintenance

- 7. Reduce the number of places in code where the PSWE bit (b0 in PSCTL) is set to a '1'. There should be exactly one routine in code that sets PSWE to a '1' to write Flash bytes and one routine in code that sets PSWE and PSEE both to a '1' to erase Flash pages.

- 8. Minimize the number of variable accesses while PSWE is set to a '1'. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 9. Disable interrupts prior to setting PSWE to a '1' and leave them disabled until after PSWE has been reset to 0. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- 10. Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 11. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

# SFR Definition 21.2. FLKEY: Flash Lock and Key

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | FLKEY[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xB7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | FLKEY[7:0] | Flash Lock and Key Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |            | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |            | This register provides a lock and key function for Flash erasures<br>and writes. Flash writes and erases are enabled by writing 0xA5<br>followed by 0xF1 to the FLKEY register. Flash writes and erases<br>are automatically disabled after the next write or erase is com-<br>plete. If any writes to FLKEY are performed incorrectly, or if a<br>Flash write or erase operation is attempted while these opera-<br>tions are disabled, the Flash will be permanently locked from<br>writes or erasures until the next device reset. If an application<br>never writes to Flash, it can intentionally lock the Flash by writing<br>a non-0xA5 value to FLKEY from software.<br>Read:<br>When read, bits 1–0 indicate the current Flash lock state.<br>00: Flash is write/erase locked.<br>01: The first key code has been written (0xA5). |

|     |            | 10: Flash is unlocked (writes/erases allowed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | 11: Flash writes/erases disabled until the next reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# SFR Definition 24.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|--------|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT | VDMLVL |   |   |   |   |   |

| Туре  | R/W    | R       | R/W    | R | R | R | R | R |

| Reset | Varies | Varies  | 0      | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xFF; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 24.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.<br>1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | VDMLVL  | VDD Monitor Level Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |         | 0: VDD Monitor Threshold is set to VRST-LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         | 1: VDD Monitor Threshold is set to VRST-HIGH. This setting<br>is required for any system with firmware that writes and/or<br>erases Flash.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4:0 | Unused  | Read = 000000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### 25.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. Before entering stop mode, the system clock must be sourced by the internal high-frequency oscillator. In stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

By default, when in stop mode the internal regulator is still active. However, the regulator can be configured to shut down while in stop mode to save power. To shut down the regulator in stop mode, the STOPCF bit in register REG01CN should be set to 1 prior to setting the STOP bit (see SFR Definition 25.1). If the regulator is shut down using the STOPCF bit, only the RST pin or a full power cycle are capable of resetting the device.

### 25.3. Suspend Mode

Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source or the internal low-frequency oscillator.

Suspend mode can be terminated by four types of events, a port match (described in Section "27.5. Port Match" on page 183), a Timer 3 overflow (described in Section "31.3. Timer 3" on page 259), a Comparator low output (if enabled), or a device reset event. Note that in order to run Timer 3 in suspend mode, the timer must be configured to clock from either the external clock source or the internal low-frequency oscillator source. When suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event (port match or Timer 3 overflow) was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

imum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                                                                | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| 0                                                                                                                                                                                                                                                                                                                      | T <sub>low</sub> – 4 system clocks<br>or<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                      | 11 system clocks                                                                    | 12 system clocks      |  |  |  |  |

| <b>Note:</b> Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero. |                                                                                     |                       |  |  |  |  |

With the SMBnTOE bit set, Timer 3 (SMBus0) and Timer 5 (SMBus1) should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "28.3.4. SCL Low Timeout" on page 194). The SMBus interface will force the associated timer to reload while SCL is high, and allow the timer to count when SCL is low. The timer interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBnFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 28.4).

### 28.4.2. SMBus Pin Swap

The SMBus peripherals are assigned to pins using the priority crossbar decoder. By default, the SMBus signals are assigned to port pins starting with SDA on the lower-numbered pin, and SCL on the next available pin. The SMBnSWAP bits in the SMBTC register can be set to 1 to reverse the order in which the SMBus signals are assigned.

### 28.4.3. SMBus Timing Control

The SMBnSDD field in the SMBTC register are used to restrict the detection of a START condition under certain circumstances. In some systems where there is significant mis-match between the impedance or the capacitance on the SDA and SCL lines, it may be possible for SCL to fall after SDA during an address or data transfer. Such an event can cause a false START detection on the bus. These kind of events are not expected in a standard SMBus or I2C-compliant system. In most systems this parameter should not be adjusted, and it is recommended that it be left at its default value.

By default, if the SCL falling edge is detected after the falling edge of SDA (i.e. one SYSCLK cycle or more), the device will detect this as a START condition. The SMBnSDD field is used to increase the amount of hold time that is required between SDA and SCL falling before a START is recognized. An additional 2, 4, or 8 SYSCLKs can be added to prevent false START detection in systems where the bus conditions warrant this.

### 28.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters slave transmitter mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (an error condition may be generated if SMB0DAT is written following a received NACK while in slave transmitter mode). The interface exits slave transmitter mode after receiving a STOP. The interface will switch to slave receiver mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 28.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

### 28.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 28.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 28.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

| Parameter         | Description                                      | Min                          | Max                     | Units |

|-------------------|--------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode       | e Timing (See Figure 30.8 and Figure 30.9)       |                              |                         |       |

| Т <sub>МСКН</sub> | SCK High Time                                    | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub> | SCK Low Time                                     | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MIS</sub>  | MISO Valid to SCK Shift Edge                     | 1 x T <sub>SYSCLK</sub> + 20 | —                       | ns    |

| т <sub>мін</sub>  | SCK Shift Edge to MISO Change                    | 0                            |                         | ns    |

| Slave Mode        | Timing (See Figure 30.10 and Figure 30.11        | )                            |                         | •     |

| T <sub>SE</sub>   | NSS Falling to First SCK Edge                    | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SD</sub>   | Last SCK Edge to NSS Rising                      | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SEZ</sub>  | NSS Falling to MISO Valid                        | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>  | NSS Rising to MISO High-Z                        | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| т <sub>скн</sub>  | SCK High Time                                    | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| Т <sub>СКL</sub>  | SCK Low Time                                     | 5 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SIS</sub>  | MOSI Valid to SCK Sample Edge                    | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIH</sub>  | SCK Sample Edge to MOSI Change                   | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| Т <sub>SOH</sub>  | SCK Shift Edge to MISO Change                    | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>  | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY) | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

Table 30.1. SPI Slave Timing Parameters

## SFR Definition 31.15. TMR3RLL: Timer 3 Reload Register Low Byte

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------------|---|---|---|---|---|---|

| Name  |   | TMR3RLL[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W          |   |   |   |   |   |   |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x92; SFR Page = 0

| Bit | Name         | Function                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR3RLL[7:0] | Timer 3 Reload Register Low Byte.                           |

|     |              | TMR3RLL holds the low byte of the reload value for Timer 3. |

### SFR Definition 31.16. TMR3RLH: Timer 3 Reload Register High Byte

| Bit   | 7   | 6 | 5 | 4     | 3       | 2 | 1 | 0 |

|-------|-----|---|---|-------|---------|---|---|---|

| Name  |     |   |   | TMR3R | LH[7:0] |   |   |   |

| Туре  | R/W |   |   |       |         |   |   |   |

| Reset | 0   | 0 | 0 | 0     | 0       | 0 | 0 | 0 |

SFR Address = 0x93; SFR Page = 0

| Bit | Name         | Function                                                     |

|-----|--------------|--------------------------------------------------------------|

| 7:0 | TMR3RLH[7:0] | Timer 3 Reload Register High Byte.                           |

|     |              | TMR3RLH holds the high byte of the reload value for Timer 3. |

## SFR Definition 31.17. TMR3L: Timer 3 Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | TMR3L[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x94; SFR Page = 0

| Bit | Name       | Function                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR3L[7:0] | Timer 3 Low Byte.                                                                                                                             |

|     |            | In 16-bit mode, the TMR3L register contains the low byte of the 16-bit Timer 3. In 8-bit mode, TMR3L contains the 8-bit low byte timer value. |

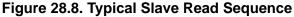

### 32.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 32.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2      | CPS1                                      | CPS0 | Timebase                                                              |  |  |

|-----------|-------------------------------------------|------|-----------------------------------------------------------------------|--|--|

| 0         | 0                                         | 0    | System clock divided by 12                                            |  |  |

| 0         | 0                                         | 1    | System clock divided by 4                                             |  |  |

| 0         | 1                                         | 0    | Timer 0 overflow                                                      |  |  |

| 0         | 1                                         | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |  |  |

| 1         | 0                                         | 0    | System clock                                                          |  |  |

| 1         | 0                                         | 1    | External oscillator source divided by 8                               |  |  |

| 1         | 1                                         | 0    | Low frequency oscillator divided by 8                                 |  |  |

| 1         | 1                                         | 1    | Reserved                                                              |  |  |

| Note: Syr | Note: Synchronized with the system clock. |      |                                                                       |  |  |

### Table 32.1. PCA Timebase Input Options

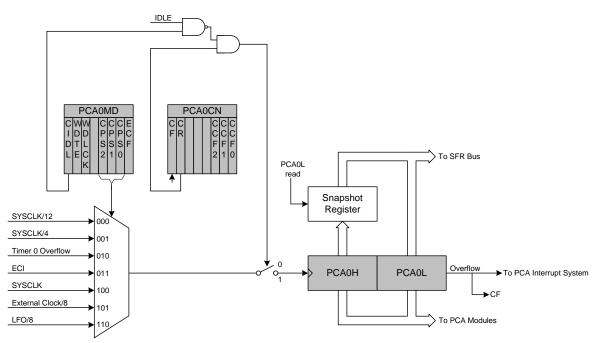

### 32.3.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 32.5. PCA Software Timer Mode Diagram

# SFR Definition 32.3. PCA0PWM: PCA PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3 | 2 | 1    | 0      |

|-------|-------|------|------|---|---|---|------|--------|

| Name  | ARSEL | ECOV | COVF |   |   |   | CLSE | L[1:0] |

| Туре  | R/W   | R/W  | R/W  | R | R | R | R/W  |        |

| Reset | 0     | 0    | 0    | 0 | 0 | 0 | 0    | 0      |

SFR Address = 0xF7; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |            | <ul> <li>This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9, 10, and 11-bit PWM modes. In all other modes, the Auto-Reload registers have no function.</li> <li>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.</li> <li>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn.</li> </ul> |  |  |  |  |

| 6   | ECOV       | <ul> <li>Cycle Overflow Interrupt Enable.</li> <li>This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.</li> <li>0: COVF will not generate PCA interrupts.</li> <li>1: A PCA interrupt will be generated when COVF is set.</li> </ul>                                                                                                                                                                                                                        |  |  |  |  |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     |            | <ul> <li>This bit indicates an overflow of the 8th, 9th, 10th, or 11th bit of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.</li> <li>0: No overflow has occurred since the last time this bit was cleared.</li> <li>1: An overflow has occurred since the last time this bit was cleared.</li> </ul>                   |  |  |  |  |

| 4:2 | Unused     | Unused. Read = 000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 1:0 | CLSEL[1:0] | Cycle Length Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|     |            | <ul> <li>When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, between 8, 9, 10, or 11 bits. This affects all channels configured for PWM which are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode.</li> <li>00: 8 bits.</li> <li>01: 9 bits.</li> <li>10: 10 bits.</li> <li>11: 11 bits.</li> </ul>                                                                                    |  |  |  |  |