Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/l²C), SPI, UART/USART                              |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f397-a-gm |

| 31.3.1. 16-bit Timer with Auto-Reload                               | 259 |

|---------------------------------------------------------------------|-----|

| 31.3.2. 8-bit Timers with Auto-Reload                               |     |

| 31.3.3. Low-Frequency Oscillator (LFO) Capture Mode                 | 261 |

| 31.4. Timer 4                                                       | 265 |

| 31.4.1. 16-bit Timer with Auto-Reload                               | 265 |

| 31.4.2. 8-bit Timers with Auto-Reload                               | 266 |

| 31.5. Timer 5                                                       |     |

| 31.5.1. 16-bit Timer with Auto-Reload                               | 270 |

| 31.5.2. 8-bit Timers with Auto-Reload                               | 271 |

| 32. Programmable Counter Array                                      | 275 |

| 32.1. PCA Counter/Timer                                             |     |

| 32.2. PCA0 Interrupt Sources                                        | 277 |

| 32.3. Capture/Compare Modules                                       | 278 |

| 32.3.1. Edge-triggered Capture Mode                                 | 279 |

| 32.3.2. Software Timer (Compare) Mode                               |     |

| 32.3.3. High-Speed Output Mode                                      | 281 |

| 32.3.4. Frequency Output Mode                                       |     |

| 32.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes |     |

| 32.3.5.1. 8-bit Pulse Width Modulator Mode                          |     |

| 32.3.5.2. 9/10/11-bit Pulse Width Modulator Mode                    |     |

| 32.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 32.4. Watchdog Timer Mode                                           |     |

| 32.4.1. Watchdog Timer Operation                                    |     |

| 32.4.2. Watchdog Timer Usage                                        |     |

| 32.5. Comparator Clear Function                                     |     |

| 32.6. Register Descriptions for PCA0                                |     |

| 33. C2 Interface                                                    |     |

| 33.1. C2 Interface Registers                                        |     |

| 33.2. C2 Pin Sharing                                                |     |

| Document Change List                                                |     |

| Contact Information                                                 | 202 |

## 2. Ordering Information

The following features are common to all device in this family:

- 50 MIPS throughput (peak)

- 1 kB of RAM (256 internal bytes and 768 XRAM bytes)

- Calibrated internal 49 MHz oscillator

- Internal 80 kHz oscillator

- Two SMBus/I<sup>2</sup>C

- Enhanced SPI, Enhanced UART

- Six Timers

- Three Programmable Counter Array channels

- Analog Comparator

- Lead-free / RoHS Compliant

Table 2.1 shows the features that differentiate the devices in this family.

**Table 2.1. Product Selection Guide**

| Ordering Part<br>Number | Flash<br>Memory<br>(Bytes) | EEPROM<br>(Bytes) | Digital<br>Port I/Os | 10-bit<br>ADC<br>Channels | 10-bit<br>DAC<br>Channels | On-Chip<br>Voltage<br>Reference | Precision<br>Temperature<br>Sensor | Package<br>4x4 mm |

|-------------------------|----------------------------|-------------------|----------------------|---------------------------|---------------------------|---------------------------------|------------------------------------|-------------------|

| C8051F370-A-GM          | 16k                        | 512               | 21                   | 20                        | 2                         | Y                               | Y                                  | QFN-24            |

| C8051F371-A-GM          | 16k                        | 512               | 21                   | _                         | _                         | _                               | _                                  | QFN-24            |

| C8051F374-A-GM          | 8k                         | 512               | 21                   | 20                        | 2                         | Y                               | Y                                  | QFN-24            |

| C8051F375-A-GM          | 8k                         | 512               | 21                   | _                         | _                         | _                               | _                                  | QFN-24            |

| C8051F390-A-GM          | 16k                        | _                 | 21                   | 20                        | 2                         | Y                               | Y                                  | QFN-24            |

| C8051F391-A-GM          | 16k                        | _                 | 21                   | _                         | _                         | _                               | _                                  | QFN-24            |

| C8051F392-A-GM          | 16k                        | _                 | 17                   | 16                        | 2                         | Y                               | Y                                  | QFN-20            |

| C8051F393-A-GM          | 16k                        | _                 | 17                   | _                         | _                         | _                               | _                                  | QFN-20            |

| C8051F394-A-GM          | 8k                         | _                 | 21                   | 20                        | 2                         | Y                               | Y                                  | QFN-24            |

| C8051F395-A-GM          | 8k                         | _                 | 21                   | _                         | _                         | _                               | _                                  | QFN-24            |

| C8051F396-A-GM          | 8k                         | _                 | 17                   | 16                        | 2                         | Y                               | Y                                  | QFN-20            |

| C8051F397-A-GM          | 8k                         | _                 | 17                   | _                         | _                         | _                               | _                                  | QFN-20            |

| C8051F398-A-GM          | 4k                         | _                 | 17                   | 16                        | 2                         | Y                               | Y                                  | QFN-20            |

| C8051F399-A-GM          | 4k                         | _                 | 17                   | _                         | _                         | _                               | _                                  | QFN-20            |

Table 4.1. Pin Definitions for the C8051F39x/37x (Continued)

| Name  | Pin<br>'F392/3/6/<br>7/8/9 | Pin<br>'F390/1/<br>4/5 | Pin<br>'F370/1/<br>4/5 | Туре             | Description                              |

|-------|----------------------------|------------------------|------------------------|------------------|------------------------------------------|

| P2.2  | _                          | 8                      | _                      | D I/O or<br>A In | Port 2.2.                                |

| P2.2  | -                          |                        | 8                      | D I/O or<br>A In | Port 2.2.                                |

| EESCL |                            |                        |                        | D I/O            | EEPROM SCL Connection.                   |

| P2.3  | _                          | 7                      | _                      | D I/O or<br>A In | Port 2.3.                                |

| P2.3  | -                          | _                      | 7                      | D I/O or<br>A In | Port 2.3.                                |

| EESDA |                            |                        |                        | D I/O            | EEPROM SDA Connection.                   |

| P2.4  | _                          | 6                      | 6                      | D I/O            | Port 2.4. (Also C2D on 24-pin Packaging) |

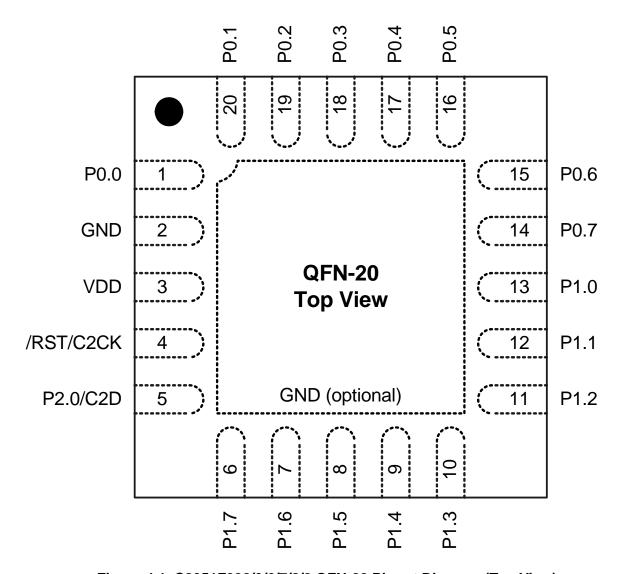

Figure 4.1. C8051F392/3/6/7/8/9 QFN-20 Pinout Diagram (Top View)

SILICON LABS

### **Table 7.10. ADC0 Electrical Characteristics**

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL = 0), -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), unless otherwise specified.

| Parameter                                               | Test Condition                  | Min        | Тур       | Max             | Unit   |

|---------------------------------------------------------|---------------------------------|------------|-----------|-----------------|--------|

| DC Accuracy                                             |                                 |            |           |                 |        |

| Resolution                                              | C8051F394/5/6/7, C8051F374/5    |            | 10        |                 | bits   |

| Integral Nonlinearity                                   | C8051F398/9                     | _          | <±0.5     | ±2.0            | LSB    |

| Differential Nonlinearity                               |                                 | _          | <±0.5     | ±1              | LSB    |

| Offset Error                                            |                                 | -2         | 0         | 2               | LSB    |

| Full Scale Error                                        |                                 | <b>-</b> 5 | -2        | 1               | LSB    |

| Offset Temperature Coefficient                          |                                 | _          | 0.005     | _               | LSB/°C |

| Dynamic performance (10 kHz                             | sine-wave single-ended input, 1 | dB belo    | w Full Sc | ale, 500        | ksps)  |

| Signal-to-Noise Plus Distortion                         |                                 | 55         | 58        | _               | dB     |

| Total Harmonic Distortion                               | Up to the 5th harmonic          | _          | -73       | _               | dB     |

| Spurious-Free Dynamic Range                             |                                 | _          | 68        | _               | dB     |

| Conversion Rate                                         |                                 |            |           |                 |        |

| SAR Conversion Clock                                    |                                 | _          | _         | 8.33            | MHz    |

| Conversion Time in SAR Clocks                           |                                 | 13         | _         | _               | clocks |

| Track/Hold Acquisition Time                             |                                 | 300        | _         | _               | ns     |

| Throughput Rate                                         |                                 | _          | _         | 500             | ksps   |

| Analog Inputs                                           |                                 |            |           |                 |        |

| ADC Input Voltage Range                                 | Single Ended (AIN+ – GND)       | 0          | _         | VREF            | V      |

|                                                         | Differential (AIN+ - AIN-)      | -VREF      | _         | VREF            | V      |

| Absolute Pin Voltage with respect to GND                | Single Ended or Differential    | 0          | _         | V <sub>DD</sub> | V      |

| Sampling Capacitance<br>(C <sub>SAMPLE</sub> )          |                                 | _          | 5         | _               | pF     |

| Input Multiplexer Impedance (R <sub>MUX</sub> )         |                                 |            | 1.6       | _               | kΩ     |

| Power Specifications                                    |                                 |            |           |                 |        |

| Power Supply Current (V <sub>DD</sub> supplied to ADC0) | Operating Mode, 500 ksps        | _          | 860       | 1010            | μΑ     |

| Power Supply Rejection                                  | Single Ended (AIN+ - GND)       | _          | 1.15      | _               | mV/V   |

|                                                         | Differential (AIN+ - AIN-)      | _          | 2.45      | _               | mV/V   |

### **Table 7.13. Voltage Reference Electrical Characteristics**

$V_{DD}$  = 3.0 V, -40 to +105 °C (C8051F39x), -40 to +85 °C (C8051F37x), unless otherwise specified.

| Parameter                       | Test Condition                         | Min  | Тур | Max      | Unit   |  |  |  |

|---------------------------------|----------------------------------------|------|-----|----------|--------|--|--|--|

| nternal Reference (REFBE = 1)   |                                        |      |     |          |        |  |  |  |

| Output Voltage                  | 2.4 V Setting                          | 2.37 | 2.4 | 2.43     | V      |  |  |  |

|                                 | 1.2 V Setting                          | 1.18 | 1.2 | 1.22     | V      |  |  |  |

| VREF Short-Circuit Current      |                                        | _    | _   | 8        | mA     |  |  |  |

| VREF Temperature<br>Coefficient |                                        | _    | 33  | _        | ppm/°C |  |  |  |

| Load Regulation                 | Load = 0 to 200 µA to AGND             | _    | 6   | _        | μV/μΑ  |  |  |  |

| VREF Turn-on Time 1             | 4.7 μF tantalum, 0.1 μF ceramic bypass | _    | 1.5 | _        | ms     |  |  |  |

| VREF Turn-on Time 2             | 0.1 μF ceramic bypass                  | _    | 110 | _        | μs     |  |  |  |

| Power Supply Rejection          | 2.4 V Setting                          | _    | 3.5 | _        | mV/V   |  |  |  |

|                                 | 1.2 V Setting                          | _    | 1.1 | _        | mV/V   |  |  |  |

| External Reference (REFBI       | <b>=</b> = 0)                          |      |     |          |        |  |  |  |

| Input Voltage Range             |                                        | 1.0  | _   | $V_{DD}$ | V      |  |  |  |

| Input Current                   | Sample Rate = 200 ksps; VREF = 3.0 V   | _    | 3   | _        | μA     |  |  |  |

| Power Specifications            |                                        |      |     |          | •      |  |  |  |

| Supply Current                  | REFBE = "1" or TEMPE = "1"             | _    | 70  | 100      | μA     |  |  |  |

### **Table 7.14. Voltage Regulator Electrical Characteristics**

$V_{DD} = 3.0 \text{ V}, -40 \text{ to } +105 \,^{\circ}\text{C} \, (C8051F39x), -40 \text{ to } +85 \,^{\circ}\text{C} \, (C8051F37x), \text{ unless otherwise specified.}$

| Parameter                | Test Condition       | Min  | Тур  | Max  | Unit   |

|--------------------------|----------------------|------|------|------|--------|

| Output Voltage           |                      | 1.73 | 1.78 | 1.83 | V      |

| Power Supply Sensitivity | Constant Temperature | _    | 0.5  | _    | %/V    |

| Temperature Sensitivity  | Constant Supply      | _    | 55   | _    | ppm/°C |

### 9.2. Modes of Operation

ADC0 has a maximum conversion speed of 500 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register.

#### 9.2.1. Starting a Conversion

A conversion can be initiated in one of several ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal

- 6. A Timer 3 overflow

- 7. A Timer 4 overflow

- 8. A Timer 5 overflow

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2, 3, 4, or 5 overflows are used as the conversion source, Low Byte overflows are used if the timer is in 8-bit mode; High byte overflows are used if the timer is in 16-bit mode. See Section "31. Timers" on page 242 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as a Port I/O pin. When the CNVSTR input is used as the ADC0 conversion source, the associated pin should be skipped by the Digital Crossbar. See Section "27. Port Input/Output" on page 173 for details on Port I/O configuration.

### SFR Definition 11.2. IDA0H: IDA0 Data Word MSB

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------|---|---|---|---|---|---|---|--|

| Name  | IDA0[9:2] |   |   |   |   |   |   |   |  |

| Туре  | R/W       |   |   |   |   |   |   |   |  |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0x97; SFR Page = 0

| Bit | Name      | Function                                   |

|-----|-----------|--------------------------------------------|

| 7:0 | IDA0[9:2] | IDA0 Data Word High-Order Bits.            |

|     |           | Upper 8 bits of the 10-bit IDA0 Data Word. |

### SFR Definition 11.3. IDA0L: IDA0 Data Word LSB

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|---|---|---|---|---|---|---|

| Name  | IDA0[1:0] |   |   |   |   |   |   |   |

| Туре  | R/W       |   | R | R | R | R | R | R |

| Reset | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x96; SFR Page = 0

| Bit | Name      | Function                                    |

|-----|-----------|---------------------------------------------|

| 7:6 | IDA0[1:0] | IDA0 Data Word Low-Order Bits.              |

|     |           | Lower 2 bits of the 10-bit IDA0 Data Word.  |

| 5:0 | Unused    | Unused. Read = 000000b. Write = Don't care. |

### SFR Definition 11.5. IDA1H: IDA1 Data Word MSB

| Bit   | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----------|-----|---|---|---|---|---|---|--|--|

| Name  | IDA1[9:2] |     |   |   |   |   |   |   |  |  |

| Туре  |           | R/W |   |   |   |   |   |   |  |  |

| Reset | 0         | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0x97; SFR Page = F

| Bit | Name      | Function                                   |

|-----|-----------|--------------------------------------------|

| 7:0 | IDA1[9:2] | IDA1 Data Word High-Order Bits.            |

|     |           | Upper 8 bits of the 10-bit IDA1 Data Word. |

### SFR Definition 11.6. IDA1L: IDA1 Data Word LSB

| Bit   | 7    | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|-------|---|---|---|---|---|---|

| Name  | IDA1 | [1:0] |   |   |   |   |   |   |

| Туре  | R/W  |       | R | R | R | R | R | R |

| Reset | 0    | 0     | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0x96; SFR Page = F

| Bit | Name      | Function                                    |

|-----|-----------|---------------------------------------------|

| 7:6 | IDA1[1:0] | IDA1 Data Word Low-Order Bits.              |

|     |           | Lower 2 bits of the 10-bit IDA1 Data Word.  |

| 5:0 | Unused    | Unused. Read = 000000b. Write = Don't care. |

## **SFR Definition 12.1. REF0CN: Reference Control**

| Bit   | 7      | 6 | 5 | 4      | 3     | 2     | 1     | 0     |

|-------|--------|---|---|--------|-------|-------|-------|-------|

| Name  | REFBGS |   |   | REGOVR | REFSL | TEMPE | BIASE | REFBE |

| Туре  | R/W    | R | R | R/W    | R/W   | R/W   | R/W   | R/W   |

| Reset | 0      | 0 | 0 | 0      | 0     | 0     | 0     | 0     |

SFR Address = 0xD1; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REFBGS | Reference Buffer Gain Select.  This bit selects between 1x and 2x gain for the on-chip voltage reference buffer.  0: 2x Gain  1: 1x Gain                                                                                                                           |

| 6:5 | Unused | Read = 00b; Write = Don't care.                                                                                                                                                                                                                                    |

| 4   | REGOVR | Regulator Reference Override.  This bit "overrides" the REFSL bit, and allows the internal regulator to be used as a reference source.  0: The voltage reference source is selected by the REFSL bit.  1: The internal regulator is used as the voltage reference. |

| 3   | REFSL  | Voltage Reference Select.  This bit selects the ADCs voltage reference.  0: V <sub>REF</sub> pin used as voltage reference.  1: V <sub>DD</sub> used as voltage reference.                                                                                         |

| 2   | TEMPE  | Temperature Sensor Enable Bit.  0: Internal Temperature Sensor off.  1: Internal Temperature Sensor on.                                                                                                                                                            |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.  0: Internal Bias Generator off.  1: Internal Bias Generator on.                                                                                                                                                        |

| 0   | REFBE  | On-chip Reference Buffer Enable Bit.  0: On-chip Reference Buffer off.  1: On-chip Reference Buffer on. Internal voltage reference driven on the V <sub>REF</sub> pin.                                                                                             |

### 18. Device ID Registers

The C8051F39x/37x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read two SFRs. DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

The C8051F39x/37x devices also include four SFRs, SN0 through SN3, that are pre-programmed during production with a unique, 32-bit serial number. The serial number provides a unique identification number for each device and can be read from the application firmware. If the serial number is not used in the application, these four registers can be used as general purpose SFRs.

#### SFR Definition 18.1. DERIVID: Device Derivative ID

| Bit   | 7       | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| Name  | DERIVID |        |        |        |        |        |        |        |  |  |  |

| Туре  |         | R      |        |        |        |        |        |        |  |  |  |

| Reset | Varies  | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |

SFR Address = 0xAB; SFR Page = 0

|     |        | Function                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ERIVID | Derivative ID.                                                                                                                                                                                                                                                                                                                                                                    |

|     |        | This read-only register returns the 8-bit derivative ID, which can be used by firmware to identify which device in the product family is being used.  0xD0: C8051F390  0xD1: C8051F391  0xD2: C8051F392  0xD3: C8051F393  0xD4: C8051F394  0xD5: C8051F395  0xD6: C8051F396  0xD7: C8051F397  0xD8: C8051F398  0xD9: C8051F399  0xE0: C8051F370  0xE1: C8051F371  0xE4: C8051F374 |

### SFR Definition 18.2. REVISION: Device Revision ID

| Bit   | 7        | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|----------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| Name  | REVISION |        |        |        |        |        |        |        |  |  |  |

| Туре  |          | R      |        |        |        |        |        |        |  |  |  |

| Reset | Varies   | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |

SFR Address = 0xAC; SFR Page = 0

| Bit | Name     | Function                                                                                                       |

|-----|----------|----------------------------------------------------------------------------------------------------------------|

| 7:0 | REVISION | <b>Device Revision.</b> This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |

## SFR Definition 18.3. SN3: Serial Number Byte 3

| Bit   | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| Name  | SN3    |        |        |        |        |        |        |        |  |  |  |

| Туре  |        | R      |        |        |        |        |        |        |  |  |  |

| Reset | Varies |  |  |  |

SFR Address = 0xAE; SFR Page = F

| Bit | Name | Function                                                               |

|-----|------|------------------------------------------------------------------------|

| 7:0 | SN3  | Serial Number Byte 3.                                                  |

|     |      | This read-only register returns the MSB (byte 3) of the serial number. |

## SFR Definition 19.3. SFRSTACK: SFR Page Stack

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|----------|---|---|---|---|---|---|--|--|--|

| Name  |   | SFRSTACK |   |   |   |   |   |   |  |  |  |

| Туре  |   | R        |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xD3; SFR Page = F

| Bit | Name     | Function                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SFRSTACK | SFR Page Stack.                                                                                                                                                   |

|     |          | This register is used to access the contents of the SFR page stack. SFRPGIDX in the SFRPGCN register controls which level of the stack this register will access. |

### 20.2. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### SFR Definition 20.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; SFR Page = All Pages; Bit-Addressable

| Bit | Name  | Function                                                                                                                                                                                                               |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | Enable All Interrupts. Globally enables/disables all interrupts. It overrides individual interrupt mask settings. 0: Disable all interrupt sources. 1: Enable each interrupt according to its individual mask setting. |

| 6   | ESPI0 | Enable Serial Peripheral Interface (SPI0) Interrupt.  This bit sets the masking of the SPI0 interrupts. 0: Disable all SPI0 interrupts. 1: Enable interrupt requests generated by SPI0.                                |

| 5   | ET2   | Enable Timer 2 Interrupt.  This bit sets the masking of the Timer 2 interrupt.  0: Disable Timer 2 interrupt.  1: Enable interrupt requests generated by the TF2L or TF2H flags.                                       |

| 4   | ES0   | Enable UART0 Interrupt. This bit sets the masking of the UART0 interrupt. 0: Disable UART0 interrupt. 1: Enable UART0 interrupt.                                                                                       |

| 3   | ET1   | Enable Timer 1 Interrupt.  This bit sets the masking of the Timer 1 interrupt.  0: Disable all Timer 1 interrupt.  1: Enable interrupt requests generated by the TF1 flag.                                             |

| 2   | EX1   | Enable External Interrupt 1.  This bit sets the masking of External Interrupt 1.  0: Disable external interrupt 1.  1: Enable interrupt requests generated by the /INT1 input.                                         |

| 1   | ET0   | Enable Timer 0 Interrupt.  This bit sets the masking of the Timer 0 interrupt.  0: Disable all Timer 0 interrupt.  1: Enable interrupt requests generated by the TF0 flag.                                             |

| 0   | EX0   | Enable External Interrupt 0. This bit sets the masking of External Interrupt 0. 0: Disable external interrupt 0. 1: Enable interrupt requests generated by the INTO input.                                             |

## SFR Definition 20.5. EIP1: Extended Interrupt Priority 1

| Bit   | 7   | 6   | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|-----|-----|------|-------|-------|--------|------|-------|

| Name  | PT3 |     | PCP0 | PPCA0 | PADC0 | PWADC0 | PMAT | PSMB0 |

| Туре  | R/W | R/W | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0   | 0   | 0    | 0     | 0     | 0      | 0    | 0     |

SFR Address = 0xF6; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                          |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PT3      | Timer 3 Interrupt Priority Control LSB.                                                                                                           |

|     |          | This bit sets the LSB of the priority field for the Timer 3 interrupt.                                                                            |

| 6   | Reserved | Reserved. Must Write 0.                                                                                                                           |

| 5   | PCP0     | Comparator0 (CP0) Interrupt Priority Control LSB.                                                                                                 |

|     |          | This bit sets the LSB of the priority field for the CP0 interrupt.                                                                                |

| 4   | PPCA0    | Programmable Counter Array (PCA0) Interrupt Priority Control LSB.                                                                                 |

|     |          | This bit sets the LSB of the priority field for the PCA0 interrupt.                                                                               |

| 3   | PADC0    | ADC0 Conversion Complete Interrupt Priority Control LSB.  This bit sets the LSB of the priority field for the ADC0 Conversion Complete interrupt. |

| 2   | PWADC0   | ADC0 Window Comparator Interrupt Priority Control LSB.                                                                                            |

|     |          | This bit sets the LSB of the priority field for the ADC0 Window interrupt.                                                                        |

| 1   | PMAT     | Port Match Interrupt Priority Control LSB.  This bit sets the LSB of the priority field for the Port Match Event interrupt.                       |

| 0   | PSMB0    | SMBus (SMB0) Interrupt Priority Control LSB.  This bit sets the LSB of the priority field for the SMB0 interrupt.                                 |

### SFR Definition 23.1. CRC0CN: CRC0 Control

| Bit   | 7 | 6 | 5 | 4 | 3        | 2       | 1 | 0       |

|-------|---|---|---|---|----------|---------|---|---------|

| Name  |   |   |   |   | CRC0INIT | CRC0VAL |   | CRC0PNT |

| Туре  | R | R | R | R | R/W      | R/W     | R | R/W     |

| Reset | 0 | 0 | 0 | 1 | 0        | 0       | 0 | 0       |

SFR Address = 0xDF; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                           |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused   | Read = 0001b; Write = Don't Care.                                                                                                                                                                                                                                                                  |

| 3   | CRC0INIT | CRC0 Result Initialization Bit.                                                                                                                                                                                                                                                                    |

|     |          | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.                                                                                                                                                                                                                        |

| 2   | CRC0VAL  | CRC0 Set Value Initialization Bit.                                                                                                                                                                                                                                                                 |

|     |          | This bit selects the set value of the CRC result.  0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.  1: CRC result is set to 0xFFFFFFFF on write of 1 to CRC0INIT.                                                                                                                    |

| 1   | Unused   | Read = 0b; Write = Don't Care.                                                                                                                                                                                                                                                                     |

| 0   | CRC0PNT  | CRC0 Result Pointer.  Specifies the byte of the CRC result to be read/written on the next access to CRC0DAT. The value of these bits will auto-increment upon each read or write.  0: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.  1: CRC0DAT accesses bits 15–8 of the 16-bit CRC result. |

Note: Upon initiation of an automatic CRC calculation, the three cycles following a write to CRC0CN that initiate a CRC operation must only contain instructions which execute in the same number of cycles as the number of bytes in the instruction. An example of such an instruction is a 3-byte MOV that targets the CRC0FLIP register. When programming in C, the dummy value written to CRC0FLIP should be a non-zero value to prevent the compiler from generating a 2-byte MOV instruction.

### SFR Definition 27.11. P1: Port 1

| Bit   | 7       | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|---------|---|---|----|---|---|---|---|--|--|--|--|

| Name  | P1[7:0] |   |   |    |   |   |   |   |  |  |  |  |

| Туре  |         |   |   | R/ | W |   |   |   |  |  |  |  |

| Reset | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 |  |  |  |  |

SFR Address = 0x90; SFR Page = All Pages; Bit Addressable

| Bi  | Name    | Description                                                                                                               | Write                                                                 | Read                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P1[7:0] | Port 1 Data.  Sets the Port latch logic value or reads the Port pin logic state in Port cells configured for digital I/O. | O: Set output latch to logic LOW.  1: Set output latch to logic HIGH. | 0: P1.n Port pin is logic<br>LOW.<br>1: P1.n Port pin is logic<br>HIGH. |

### SFR Definition 27.12. P1MDIN: Port 1 Input Mode

| Bit   | 7           | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-------------|---|---|----|---|---|---|---|--|--|--|--|

| Name  | P1MDIN[7:0] |   |   |    |   |   |   |   |  |  |  |  |

| Туре  |             |   |   | R/ | W |   |   |   |  |  |  |  |

| Reset | 1           | 1 | 1 | 1  | 1 | 1 | 1 | 1 |  |  |  |  |

SFR Address = 0xF2; SFR Page = All Pages

| Bit | Name        | Function                                                                                                                                                                                                                            |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDIN[7:0] | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                             |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled.  0: Corresponding P1.n pin is configured for analog mode.  1: Corresponding P1.n pin is not configured for analog mode. |

#### 32.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8 to 11-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 32.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8–11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

Table 32.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

| Operational Mode                            | PCA0CPMn |   |   |   |   |   |   |   |   | PCA0PWM |   |     |     |  |  |

|---------------------------------------------|----------|---|---|---|---|---|---|---|---|---------|---|-----|-----|--|--|

| Bit Number                                  | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6       | 5 | 4–2 | 1–0 |  |  |

| Capture triggered by positive edge on CEXn  | Χ        | Χ | 1 | 0 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| Capture triggered by negative edge on CEXn  | Χ        | Χ | 0 | 1 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| Capture triggered by any transition on CEXn | Χ        | Χ | 1 | 1 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| Software Timer                              | Χ        | С | 0 | 0 | 1 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| High Speed Output                           | Χ        | С | 0 | 0 | 1 | 1 | 0 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| Frequency Output                            | Χ        | С | 0 | 0 | 0 | 1 | 1 | Α | 0 | Χ       | В | XXX | XX  |  |  |

| 8-Bit Pulse Width Modulator (Note 7)        | 0        | С | 0 | 0 | Е | 0 | 1 | Α | 0 | Χ       | В | XXX | 00  |  |  |

| 9-Bit Pulse Width Modulator (Note 7)        | 0        | С | 0 | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 01  |  |  |

| 10-Bit Pulse Width Modulator (Note 7)       | 0        | С | 0 | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 10  |  |  |

| 11-Bit Pulse Width Modulator (Note 7)       | 0        | С | 0 | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 11  |  |  |

| 16-Bit Pulse Width Modulator                | 1        | С | 0 | 0 | Е | 0 | 1 | Α | 0 | Χ       | В | XXX | XX  |  |  |

#### Notes:

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

SILICON LABS

### SFR Definition 32.2. PCA0MD: PCA Mode

| Bit   | 7    | 6    | 5     | 4 | 3    | 2    | 1    | 0   |

|-------|------|------|-------|---|------|------|------|-----|

| Name  | CIDL | WDTE | WDLCK |   | CPS2 | CPS1 | CPS0 | ECF |

| Туре  | R/W  | R/W  | R/W   | R | R/W  | R/W  | R/W  | R/W |

| Reset | 0    | 1    | 0     | 0 | 0    | 0    | 0    | 0   |

SFR Address = 0xD9; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | CIDL     | PCA Counter/Timer Idle Control.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|     |          | Specifies PCA behavior when CPU is in Idle Mode.  0: PCA continues to function normally while the system controller is in Idle Mode.  1: PCA operation is suspended while the system controller is in Idle Mode.                                                                                                                                                           |  |  |  |  |

| 6   | WDTE     | Watchdog Timer Enable.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|     |          | If this bit is set, PCA Module 2 is used as the watchdog timer.  0: Watchdog Timer disabled.  1: PCA Module 2 enabled as Watchdog Timer.                                                                                                                                                                                                                                   |  |  |  |  |

| 5   | WDLCK    | Watchdog Timer Lock.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|     |          | This bit locks/unlocks the Watchdog Timer Enable. When WDLCK is set, the Watchdog Timer may not be disabled until the next system reset.  0: Watchdog Timer Enable unlocked.  1: Watchdog Timer Enable locked.                                                                                                                                                             |  |  |  |  |

| 4   | Unused   | Unused. Read = 0b, Write = Don't care.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 3:1 | CPS[2:0] | PCA Counter/Timer Pulse Select.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|     |          | These bits select the timebase source for the PCA counter 000: System clock divided by 12 001: System clock divided by 4 010: Timer 0 overflow 011: High-to-low transitions on ECI (max rate = system clock divided by 4) 100: System clock 101: External clock divided by 8 (synchronized with the system clock) 110: Low frequency oscillator divided by 8 111: Reserved |  |  |  |  |

| 0   | ECF      | PCA Counter/Timer Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|     |          | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.  0: Disable the CF interrupt.  1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.                                                                                                                                                                             |  |  |  |  |

**Note:** When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701