# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 50MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                |                                                                  |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | <u> </u>                                                         |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f399-a-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 28.3.4. SCL Low Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 194                                                                                                                                            |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 28.3.5. SCL High (SMBus Free) Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 195                                                                                                                                            |

|    | 28.4. Using the SMBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                |

|    | 28.4.1. SMBus Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                |

|    | 28.4.2. SMBus Pin Swap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

|    | 28.4.3. SMBus Timing Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                |

|    | 28.4.4. SMBnCN Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

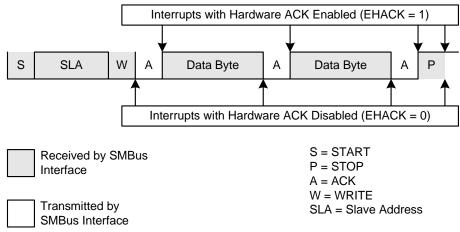

|    | 28.4.4.1. Software ACK Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                |

|    | 28.4.4.2. Hardware ACK Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 201                                                                                                                                            |

|    | 28.4.5. Hardware Slave Address Recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 204                                                                                                                                            |

|    | 28.4.6. Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 209                                                                                                                                            |

|    | 28.5. SMBus Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                |

|    | 28.5.1. Write Sequence (Master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

|    | 28.5.2. Read Sequence (Master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|    | 28.5.3. Write Sequence (Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

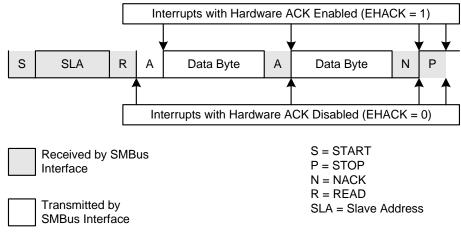

|    | 28.5.4. Read Sequence (Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

| ~~ | 28.6. SMBus Status Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                |

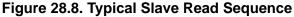

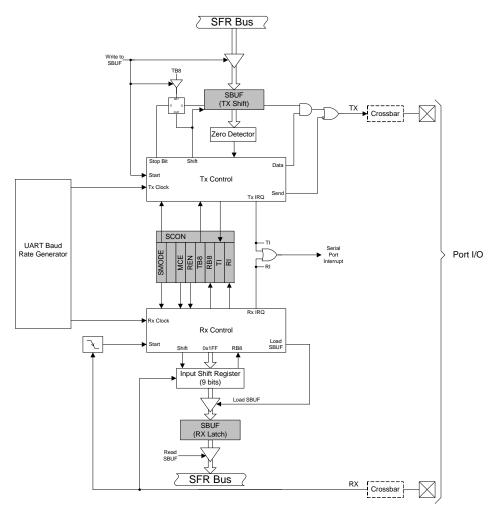

| 29 | . UARTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 220                                                                                                                                            |

|    | 29.1. Enhanced Baud Rate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                |

|    | 29.2. Operational Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                |

|    | 29.2.1. 8-Bit UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 222                                                                                                                                            |

|    | 29.2.2. 9-Bit UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 223                                                                                                                                            |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 004                                                                                                                                            |

|    | 29.3. Multiprocessor Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 224                                                                                                                                            |

| 30 | 29.3. Multiprocessor Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 224<br>228                                                                                                                                     |

| 30 | . Enhanced Serial Peripheral Interface (SPI0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 228                                                                                                                                            |

| 30 | . Enhanced Serial Peripheral Interface (SPI0)<br>30.1. Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>228</b><br>229                                                                                                                              |

| 30 | . Enhanced Serial Peripheral Interface (SPI0)<br>30.1. Signal Descriptions<br>30.1.1. Master Out, Slave In (MOSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>228</b><br>229<br>229                                                                                                                       |

| 30 | . Enhanced Serial Peripheral Interface (SPI0)<br>30.1. Signal Descriptions<br>30.1.1. Master Out, Slave In (MOSI)<br>30.1.2. Master In, Slave Out (MISO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>228</b><br>229<br>229<br>229                                                                                                                |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 229<br>229<br>229<br>229<br>229                                                                                                                |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 229<br>229<br>229<br>229<br>229<br>229<br>229                                                                                                  |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 229<br>229<br>229<br>229<br>229<br>229<br>229<br>230                                                                                           |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 228<br>229<br>229<br>229<br>229<br>229<br>230<br>231                                                                                           |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 228<br>229<br>229<br>229<br>229<br>229<br>230<br>231                                                                                           |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 228<br>229<br>229<br>229<br>229<br>229<br>230<br>231<br>232                                                                                    |

| 30 | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 228<br>229<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232                                                                             |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>232                                                                             |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>234<br>242                                                               |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                  | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>232<br>234<br><b>242</b><br>245                                                 |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1. Mode 0: 13-bit Counter/Timer</li> </ul>                                                                                                                                                                                                                                                                                                     | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>232<br>234<br>245<br>245<br>245                                                 |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer</li> </ul>                                                                                                                                                                                                                                                      | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>246                                   |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer</li> <li>31.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload</li> </ul>                                                                                                                                                                                        | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>242<br>245<br>245<br>245<br>246<br>247                                   |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer with Auto-Reload</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> </ul>                                                                                                                                                                                                      | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>246<br>247<br>248                            |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer</li> <li>31.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload.</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> <li>31.2. Timer 2</li> </ul>                                                                                                                                            | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>24 |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer with Auto-Reload</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> <li>31.2. Timer 2</li> <li>31.2.1. 16-bit Timer with Auto-Reload</li> </ul>                                                                                                                                | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>24        |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer</li> <li>31.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload.</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> <li>31.2. Timer 2</li> </ul>                                                                                                                                            | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>24        |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer with Auto-Reload</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> <li>31.2. Timer 2</li> <li>31.2.1. 16-bit Timer with Auto-Reload</li> </ul>                                                                                                                                | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>24        |

|    | <ul> <li>Enhanced Serial Peripheral Interface (SPI0)</li> <li>30.1. Signal Descriptions.</li> <li>30.1.1. Master Out, Slave In (MOSI)</li> <li>30.1.2. Master In, Slave Out (MISO)</li> <li>30.1.3. Serial Clock (SCK)</li> <li>30.1.4. Slave Select (NSS)</li> <li>30.2. SPI0 Master Mode Operation</li> <li>30.3. SPI0 Slave Mode Operation</li> <li>30.4. SPI0 Interrupt Sources</li> <li>30.5. Serial Clock Phase and Polarity</li> <li>30.6. SPI Special Function Registers</li> <li>Timers</li> <li>31.1. Timer 0 and Timer 1</li> <li>31.1.1. Mode 0: 13-bit Counter/Timer</li> <li>31.1.2. Mode 1: 16-bit Counter/Timer</li> <li>31.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload</li> <li>31.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)</li> <li>31.2. Timer 2</li> <li>31.2.1. 16-bit Timer with Auto-Reload</li> <li>31.2.2. 8-bit Timers with Auto-Reload</li> </ul> | 228<br>229<br>229<br>229<br>229<br>230<br>231<br>232<br>232<br>234<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>24        |

| Name  | Pin<br>'F392/3/6/<br>7/8/9 | Pin<br>'F390/1/<br>4/5 | Pin<br>'F370/1/<br>4/5 | Туре             | Description                              |

|-------|----------------------------|------------------------|------------------------|------------------|------------------------------------------|

| P2.2  | _                          | 8                      | _                      | D I/O or<br>A In | Port 2.2.                                |

| P2.2  | -                          | _                      | 8                      | D I/O or<br>A In | Port 2.2.                                |

| EESCL |                            |                        |                        | D I/O            | EEPROM SCL Connection.                   |

| P2.3  | _                          | 7                      | _                      | D I/O or<br>A In | Port 2.3.                                |

| P2.3  | -                          |                        | 7                      | D I/O or<br>A In | Port 2.3.                                |

| EESDA |                            |                        |                        | D I/O            | EEPROM SDA Connection.                   |

| P2.4  |                            | 6                      | 6                      | D I/O            | Port 2.4. (Also C2D on 24-pin Packaging) |

Table 4.1. Pin Definitions for the C8051F39x/37x (Continued)

## SFR Definition 8.1. TS0CN: Temperature Sensor Control

| Bit   | 7       | 6     | 5 | 4   | 3 | 2   | 1       | 0   |

|-------|---------|-------|---|-----|---|-----|---------|-----|

| Name  | TS0STRT | TS0DN |   |     |   |     | TS0CNVL |     |

| Туре  | R/W     | R     |   | R/W |   | R/W | R/W     | R/W |

| Reset | 0       | 0     | 0 | 0   | 0 | 0   | 0       | 0   |

SFR Address = 0xD2; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TS0STRT  | Temperature Sensor Start.                                                                                                                                                                                                                                                                                                                                                             |

|     |          | Firmware must set this bit to 1, then clear this bit to 0 to start a temperature sensor measurement.                                                                                                                                                                                                                                                                                  |

| 6   | TSODN    | Temperature Sensor Finished Flag.                                                                                                                                                                                                                                                                                                                                                     |

|     |          | Hardware will set TS0DN to 1 when a temperature sensor measurement is com-<br>plete. If enabled, a temperature sensor interrupt will be generated. This bit must<br>be cleared to 0 by firmware.                                                                                                                                                                                      |

| 5:3 | Reserved | Must Write 000b.                                                                                                                                                                                                                                                                                                                                                                      |

| 2:0 | TS0CNVL  | Temperature Sensor Conversion Length.                                                                                                                                                                                                                                                                                                                                                 |

|     |          | This field sets the conversion length of time over which the temperature is calculated. A longer conversion length results in a more accurate measurement. The conversion length in microseconds is derived from the following equation, where TS0CNVL is the 3-bit value held in TS0CNVL[2:0] and $F_{TS0}$ is the precision temperature sensor clock frequency given in Table 7.12. |

|     |          | Conversion Length in $\mu s = \left(\frac{256}{F_{TS0}} \times 10^6\right) \times (2^{TS0CNVL+1} + 1) + 32$                                                                                                                                                                                                                                                                           |

## SFR Definition 11.4. IDA1CN: IDA1 Control

| Bit   | 7      | 6 | 5           | 4 | 3 | 2      | 1     | 0       |

|-------|--------|---|-------------|---|---|--------|-------|---------|

| Name  | IDA1EN |   | IDA1CM[2:0] | ] |   | IDA1RP | IDA10 | MD[1:0] |

| Туре  | R/W    |   | R/W         |   | R | R/W    | R/    | W       |

| Reset | 0      | 1 | 1           | 1 | 0 | Varies | 1     | 0       |

SFR Address = 0xB9; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IDA1EN       | IDA1 Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |              | 0: IDA1 Disabled.<br>1: IDA1 Enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6:4 | IDA1CM[2:0]  | IDA0 Update Source Select bits.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | <ul> <li>000: DAC output updates on Timer 0 overflow.</li> <li>001: DAC output updates on Timer 5 overflow.</li> <li>010: DAC output updates on Timer 2 overflow.</li> <li>011: DAC output updates on Timer 3 overflow.</li> <li>100: DAC output updates on rising edge of CNVSTR.</li> <li>101: DAC output updates on falling edge of CNVSTR.</li> <li>110: DAC output updates on any edge of CNVSTR.</li> <li>111: DAC output updates on write to IDA1H.</li> </ul> |

| 3   | Reserved     | Write = 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | IDA1RP       | <ul> <li>IDA1 Reset Persistence.</li> <li>0: IDA1 is disabled by any reset source.</li> <li>1: IDA1 will remain enabled through any reset source except a power-on-reset.</li> <li>This bit is reset to 0 by a power on reset, but is sticky through all other reset sources. When setting IDA1RP to 1, IDA1EN must be set to 1 also in the same move instruction.</li> </ul>                                                                                         |

| 1:0 | IDA1OMD[1:0] | IDA1 Output Mode Select bits.<br>00: 0.5 mA full-scale output current.<br>01: 1.0 mA full-scale output current.<br>1x: 2.0 mA full-scale output current.                                                                                                                                                                                                                                                                                                              |

With the CIP-51's maximum system clock at 48 MHz, it has a peak throughput of 48 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/4 | 3  | 3/5 | 4 | 5 | 4/6 | 6 | 8 |

|------------------------|----|----|-----|----|-----|---|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 10 | 7   | 5 | 2 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the EPROM program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "33. C2 Interface" on page 297.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 15.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 15.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 15.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## SFR Definition 17.1. EMI0CN: External Memory Interface Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |  |

|-------|---|---|---|---|---|---|-----|-----|--|

| Name  |   |   |   |   |   |   | PG  | SEL |  |

| Туре  | R | R | R | R | R | R | R/W |     |  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0   |  |

SFR Address = 0xAA; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                       |

| 1:0 | PGSEL  | XRAM Page Select.                                                                                                                                                                                                                                                                                                                                                        |

|     |        | The PGSEL field provides the high byte of the 16-bit external data memory address when using an 8-bit MOVX command, effectively selecting a 256-byte page of RAM. Since the upper (unused) bits of the register are always zero, the PGSEL determines which page of XRAM is accessed.<br>For Example: If PGSEL = 0x01, addresses 0x0100 through 0x01FF will be accessed. |

## SFR Definition 20.3. IPH: Interrupt Priority High

| Bit   | 7 | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|---|--------|------|------|------|------|------|------|

| Name  |   | PHSPI0 | PHT2 | PHS0 | PHT1 | PHX1 | PHT0 | PHX0 |

| Туре  | R | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset | 1 | 0      | 0    | 0    | 0    | 0    | 0    | 0    |

SFR Address = 0x84; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                                                                                  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1, Write = Don't Care.                                                                                                             |

| 6   | PHSPI0 | Serial Peripheral Interface (SPI0) Interrupt Priority Control MSB.<br>This bit sets the MSB of the priority field for the SPI0 interrupt. |

| 5   | PHT2   | Timer 2 Interrupt Priority Control MSB.This bit sets the MSB of the priority field for the Timer 2 interrupt.                             |

| 4   | PHS0   | UART0 Interrupt Priority Control MSB.<br>This bit sets the MSB of the priority field for the UART0 interrupt.                             |

| 3   | PHT1   | Timer 1 Interrupt Priority Control MSB.This bit sets the MSB of the priority field for the Timer 1 interrupt.                             |

| 2   | PHX1   | <b>External Interrupt 1 Priority Control MSB.</b><br>This bit sets the MSB of the priority field for the External Interrupt 1 interrupt.  |

| 1   | PHT0   | Timer 0 Interrupt Priority Control MSB.This bit sets the MSB of the priority field for the Timer 0 interrupt.                             |

| 0   | PHX0   | <b>External Interrupt 0 Priority Control MSB.</b><br>This bit sets the MSB of the priority field for the External Interrupt 0 interrupt.  |

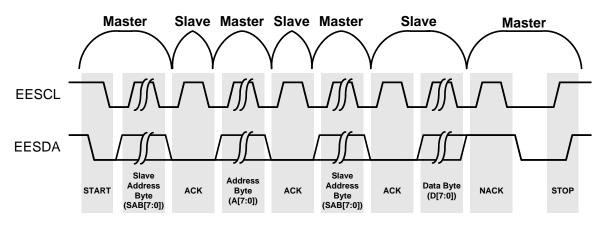

#### 22.3.2. Selective Address Read

In a selective address read operation, the master selects the target memory location for the read operation.

To perform a selective address read:

- 1. The master sends the START condition and the slave address byte with the R/W bit set to 1.

- 2. The EEPROM generates an ACK.

- 3. The master sends the read memory address (A[7:0]) to the EEPROM.

- 4. The EEPROM stores the address in the address counter and generates an ACK.

- 5. The master again sends the slave address byte with the R/W bit set to 1.

- 6. The EEPROM generates an ACK.

- 7. The EEPROM sends the byte of data (D[7:0]) specified by the address counter.

- 8. The EEPROM increments the internal address counter by one.

- 9. (Optional) To read additional bytes:

- a. The master generates an ACK.

- b. The EEPROM sends the byte of data (D[7:0]) specified by the address counter.

- c. The EEPROM increments the internal address counter by one.

- d. Repeat Steps9a through 9c until the master reads all of the desired bytes.

- 10. The master generates a NACK.

- 11. The master generates a STOP condition.

- 12. The EEPROM terminates the transmission.

- **Note:** If the selective read operation overflows the top of memory, the EEPROM address counter will wrap, and the EEPROM transmit the data from address location 0x00.

Figure 22.6. Selective Address Read (Single Byte)

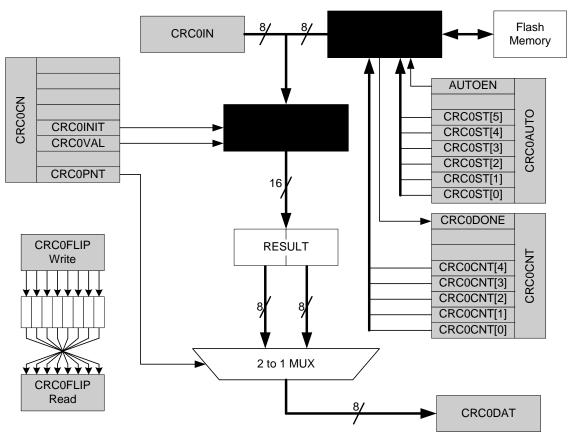

## 23. Cyclic Redundancy Check Unit (CRC0)

C8051F39x/37x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit result to an internal register. The internal result register may be accessed indirectly using the CRC0PNT bits and CRC0DAT register, as shown in Figure 23.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 23.1. CRC0 Block Diagram

## 23.1. CRC Algorithm

The C8051F39x/37x CRC unit generates a CRC result equivalent to the following algorithm:

- XOR the input with the most-significant bits of the current CRC result. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x00000000 or 0xFFFFFFF).

- 2a. If the MSB of the CRC result is set, shift the CRC result and XOR the result with the selected polynomial.

- 2b. If the MSB of the CRC result is not set, shift the CRC result.

Repeat Steps 2a/2b for the number of input bits (8). The algorithm is also described in the following example.

## SFR Definition 23.6. CRC0FLIP: CRC0 Bit Flip

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|---------------|---|---|---|---|---|---|--|

| Name  |   | CRC0FLIP[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W           |   |   |   |   |   |   |  |

| Reset | 0 | 0             | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0x9A; SFR Page = All Pages

| Bit | Name          | Function                                                                                                                                                                                                                                                                    |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0FLIP[7:0] | CRC0 Bit Flip.                                                                                                                                                                                                                                                              |

|     |               | Any byte written to CRC0FLIP is read back in a bit-<br>reversed order, i.e., the written LSB becomes the MSB.<br>For example:<br>If 0xC0 is written to CRC0FLIP, the data read back will<br>be 0x03.<br>If 0x05 is written to CRC0FLIP, the data read back will be<br>0xA0. |

## 25.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. Before entering stop mode, the system clock must be sourced by the internal high-frequency oscillator. In stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering stop mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout.

By default, when in stop mode the internal regulator is still active. However, the regulator can be configured to shut down while in stop mode to save power. To shut down the regulator in stop mode, the STOPCF bit in register REG01CN should be set to 1 prior to setting the STOP bit (see SFR Definition 25.1). If the regulator is shut down using the STOPCF bit, only the RST pin or a full power cycle are capable of resetting the device.

#### 25.3. Suspend Mode

Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source or the internal low-frequency oscillator.