# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB, USB OTG                   |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                               |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 22x16b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 64-WLCSP (3.35x3.32)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk22fn256cah12r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Ordering Information**

| Part Number     | Mer        | Number of GPIOs |    |

|-----------------|------------|-----------------|----|

|                 | Flash (KB) | SRAM (KB)       |    |

| MK22FN256CAH12R | 256        | 48              | 40 |

| MK22FN128CAH12R | 128        | 48              | 40 |

#### **Device Revision Number**

| Device Mask Set Number | SIM_SDID[REVID] | JTAG ID Register[PRN] |

|------------------------|-----------------|-----------------------|

| 0N51M                  | 0001            | 0001                  |

#### **Related Resources**

| Туре                | Description                                                                                                               | Document                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Selector Guide      | The NXP Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector | KINETISKMCUSELGD                                   |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.          | K22P121M120SF8RM                                   |

| Data Sheet          | The Data Sheet is this document. It includes electrical characteristics and signal connections.                           | K22P64M120SF8                                      |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                  | KINETIS_K_xN51M <sup>1</sup>                       |

| Package drawing     | Package dimensions are provided by part number:<br>• MK22FN256CAH12R<br>• MK22FN128CAH12R                                 | Package drawing:<br>• 98ASA00650D<br>• 98ASA00650D |

1. To find the associated resource, go to nxp.com and perform a search using this term with the *x* replaced by the revision of the device you are using.

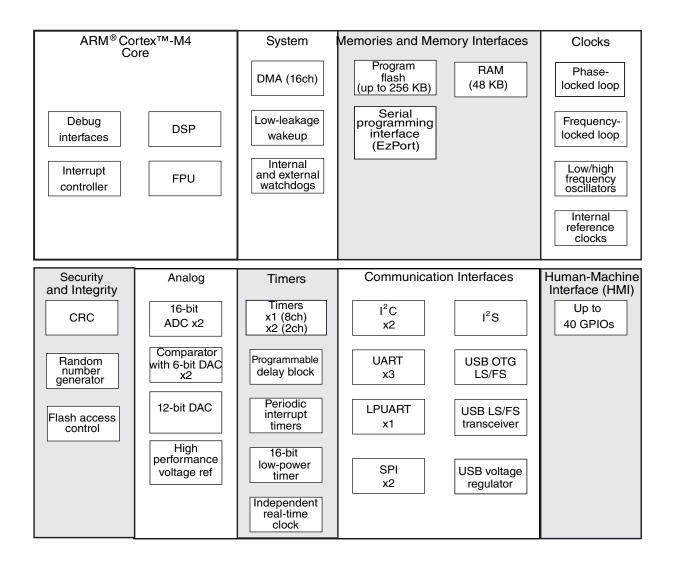

Figure 1 shows the functional modules in the chip.

Figure 1. Functional block diagram

| Symbol                | Description                                                                             | Min. | Тур.  | Max.  | Unit | Notes   |

|-----------------------|-----------------------------------------------------------------------------------------|------|-------|-------|------|---------|

|                       | @ 3.0V                                                                                  |      | 25.75 | 26.44 | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral clocks disabled, code executing from flash |      |       |       |      |         |

|                       | @ 1.8V                                                                                  |      | 23.6  | 24.29 | mA   | 2       |

|                       | @ 3.0V                                                                                  | —    | 23.7  | 24.39 | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current — all peripheral clocks enabled, code executing from flash  |      |       |       |      |         |

|                       | @ 1.8V                                                                                  | —    | 31.9  | 32.59 | mA   | 5       |

|                       | @ 3.0V                                                                                  | —    | 32.0  | 32.69 | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current in Compute operation —<br>CoreMark benchmark code executing from flash |      |       |       |      |         |

|                       | @ 1.8V                                                                                  | —    | 15.8  | 16.49 | mA   | 3, 4, 6 |

|                       | @ 3.0V                                                                                  | —    | 15.8  | 16.49 | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current in Compute operation — code executing from flash                       |      |       |       |      |         |

|                       | @ 1.8V                                                                                  |      | 14.00 | 15.50 | mA   | 6       |

|                       | @ 3.0V                                                                                  |      | 14.00 | 15.69 | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks disabled, code executing from flash            |      |       |       |      |         |

|                       | @ 1.8V                                                                                  | —    | 15.3  | 15.99 | mA   | 7       |

|                       | @ 3.0V                                                                                  | —    | 15.4  | 16.09 | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks enabled, code executing from flash             |      |       |       |      |         |

|                       | @ 1.8V                                                                                  | —    | 20.4  | 21.09 | mA   | 8       |

|                       | @ 3.0V                                                                                  |      |       |       |      |         |

|                       | • @ 25°C                                                                                |      | 20.5  | 21.19 | mA   |         |

|                       | • @ 70°C                                                                                | —    | 20.5  | 21.19 | mA   |         |

|                       | • @ 85°C                                                                                | —    | 20.5  | 21.19 | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current — Compute operation, code executing from flash                         |      |       |       |      |         |

|                       | @ 1.8V                                                                                  |      | 14.0  | 14.69 | mA   | 9       |

|                       | @ 3.0V                                                                                  |      |       |       |      |         |

|                       | • @ 25°C                                                                                | —    | 14.0  | 14.69 | mA   |         |

|                       | • @ 70°C                                                                                | —    | 14.0  | 14.69 | mA   |         |

|                       | • @ 85°C                                                                                |      | 14.0  | 14.69 | mA   |         |

| I <sub>DD_WAIT</sub>  | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled              | —    | 8.1   | 8.79  | mA   | 7       |

| I <sub>DD_WAIT</sub>  | Wait mode reduced frequency current at 3.0 V<br>— all peripheral clocks disabled        |      | 4.4   | 5.09  | mA   | 10      |

### Table 6. Power consumption operating behaviors (continued)

#### General

- 80MHz core and system clock, 40MHz bus clock, and 26.67MHz flash clock. MCG configured for FEI mode. Compute

operation.

- 10. 25MHz core and system clock, 25MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode.

- 11. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. Compute operation. Code executing from flash.

- 12. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 13. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 14. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 15. Includes 32kHz oscillator current and RTC operation.

Table 7. Low power mode peripheral adders—typical value

| Symbol                    | Description                                                                                                                                                                                                                                                  |     | •   | Tempera | ature (°C | C)  |     | Unit |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|------|

|                           |                                                                                                                                                                                                                                                              | -40 | 25  | 50      | 70        | 85  | 105 |      |

| I <sub>IREFSTEN4MHz</sub> | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled.                                                                                                                                             | 56  | 56  | 56      | 56        | 56  | 56  | μA   |

| IIREFSTEN32KHz            | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.                                                                                                                                               | 52  | 52  | 52      | 52        | 52  | 52  | μA   |

| IEREFSTEN4MHz             | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                                                                                                                   | 206 | 228 | 237     | 245       | 251 | 258 | uA   |

| IEREFSTEN32KHz            | External 32 kHz crystal clock adder by means of the OSC0_CR[EREFSTEN and EREFSTEN] bits. Measured by entering all modes with the crystal enabled.                                                                                                            |     |     |         |           |     |     |      |

|                           | VLLS1                                                                                                                                                                                                                                                        | 440 | 490 | 540     | 560       | 570 | 580 | nA   |

|                           | VLLS3                                                                                                                                                                                                                                                        | 440 | 490 | 540     | 560       | 570 | 580 |      |

|                           | LLS                                                                                                                                                                                                                                                          | 490 | 490 | 540     | 560       | 570 | 680 |      |

|                           | VLPS                                                                                                                                                                                                                                                         | 510 | 560 | 560     | 560       | 610 | 680 |      |

|                           | STOP                                                                                                                                                                                                                                                         | 510 | 560 | 560     | 560       | 610 | 680 |      |

| I <sub>48MIRC</sub>       | 48 Mhz internal reference clock                                                                                                                                                                                                                              | 350 | 350 | 350     | 350       | 350 | 350 | μA   |

| I <sub>CMP</sub>          | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare.<br>Includes 6-bit DAC power consumption.                                                            | 22  | 22  | 22      | 22        | 22  | 22  | μA   |

| I <sub>RTC</sub>          | RTC peripheral adder measured by<br>placing the device in VLLS1 mode with<br>external 32 kHz crystal enabled by<br>means of the RTC_CR[OSCE] bit and<br>the RTC ALARM set for 1 minute.<br>Includes ERCLK32K (32 kHz external<br>crystal) power consumption. | 432 | 357 | 388     | 475       | 532 | 810 | nA   |

| I <sub>UART</sub>         | UART peripheral adder measured by placing the device in STOP or VLPS                                                                                                                                                                                         |     |     |         |           |     |     |      |

| Symbol           | Description                                                                                                                                                                                                        |     | •   | Tempera | ature (°C | ;)  |     | Unit |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|------|

|                  |                                                                                                                                                                                                                    | -40 | 25  | 50      | 70        | 85  | 105 |      |

|                  | mode with selected clock source waiting<br>for RX data at 115200 baud rate.<br>Includes selected clock source power<br>consumption.                                                                                |     |     |         |           |     |     |      |

|                  | MCGIRCLK (4 MHz internal reference clock)                                                                                                                                                                          | 66  | 66  | 66      | 66        | 66  | 66  | μA   |

|                  | >OSCERCLK (4 MHz external crystal)                                                                                                                                                                                 | 214 | 237 | 246     | 254       | 260 | 268 |      |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set<br>and device is placed in VLPx, LLS, or<br>VLLSx mode.                                                                                                                         | 45  | 45  | 45      | 45        | 45  | 45  | μA   |

| I <sub>ADC</sub> | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions. | 42  | 42  | 42      | 42        | 42  | 42  | μA   |

Table 7. Low power mode peripheral adders—typical value (continued)

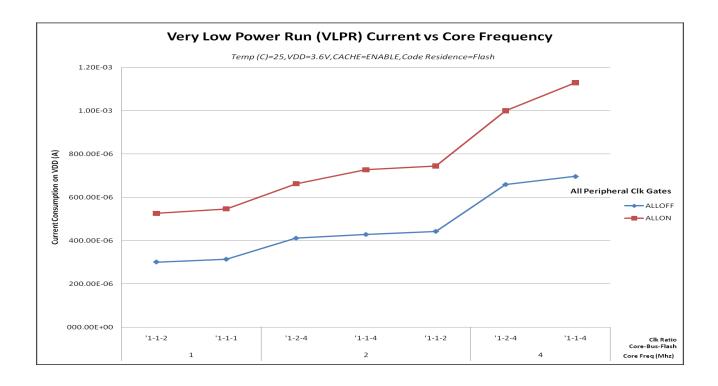

## 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode for 50 MHz and lower frequencies. MCG in FEE mode at frequencies between 50 MHz and 100MHz. MCG in PEE mode at frequencies greater than 100 MHz.

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 4. VLPR mode supply current vs. core frequency

## 2.2.6 EMC radiated emissions operating behaviors Table 8. EMC radiated emissions operating behaviors for 64 LQFP package

| Parame<br>ter    | Conditions                                                    | Clocks                   | Frequency range  | Level<br>(Typ.) | Unit | Notes   |

|------------------|---------------------------------------------------------------|--------------------------|------------------|-----------------|------|---------|

| V <sub>EME</sub> | Device configuration,                                         | FSYS = 120 MHz           | 150 kHz–50 MHz   | 14              | dBuV | 1, 2, 3 |

| test             | test conditions and EM testing per standard IEC 61967-2.      | FBUS = 60 MHz            | 50 MHz–150 MHz   | 23              |      |         |

|                  |                                                               | External crystal = 8 MHz | 150 MHz–500 MHz  | 23              |      |         |

|                  | Supply voltages:                                              |                          | 500 MHz-1000 MHz | 9               |      |         |

|                  | <ul> <li>VREGIN (USB) = 5.0 V</li> <li>VDD = 3.3 V</li> </ul> |                          | IEC level        | L               |      | 4       |

|                  | Temp = 25°C                                                   |                          |                  |                 |      |         |

1. Measurements were made per IEC 61967-2 while the device was running typical application code.

2. Measurements were performed on the 64LQFP device, MK22FN512VLH12 .

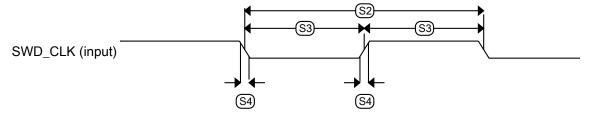

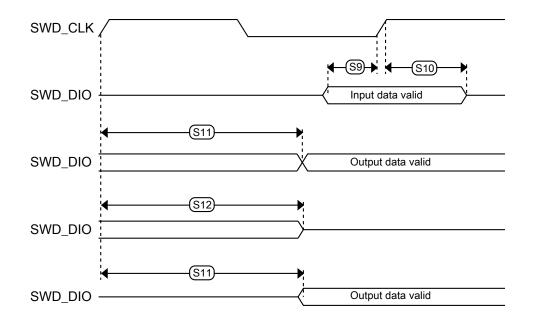

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| S11    | SWD_CLK high to SWD_DIO data valid | —    | 25   | ns   |

| S12    | SWD_CLK high to SWD_DIO high-Z     | 5    |      | ns   |

Table 13. SWD full voltage range electricals (continued)

Figure 5. Serial wire clock input timing

## 3.1.2 JTAG electricals

Table 14. JTAG limited voltage range electricals

| Symbol | Operating voltage                |          | Max. | Unit |

|--------|----------------------------------|----------|------|------|

|        | Operating voltage                | 2.7      | 3.6  | V    |

| J1     | TCLK frequency of operation      |          |      | MHz  |

|        | Table continues on the next page | <b>`</b> |      |      |

# 3.3.1 MCG specifications

| Symbol                  | Description                                                                                                          |                                                                                     | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                                                                                                      | frequency (slow clock) —<br>nominal VDD and 25 °C                                   | _                               | 32.768    | _       | kHz                   |       |

| $\Delta f_{ints_t}$     |                                                                                                                      | internal reference frequency<br>voltage and temperature                             | _                               | +0.5/-0.7 | ± 2     | %                     |       |

| $f_{ints_t}$            | Internal reference frequency (slow clock) —<br>user trimmed                                                          |                                                                                     | 31.25                           | _         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM and SCFTRIM |                                                                                     | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco\_t}$     | Total deviation of trimmed average DCO output frequency over voltage and temperature                                 |                                                                                     | _                               | +0.5/-0.7 | ± 2     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      | Total deviation of trimmed average DCO output frequency over fixed voltage and temperature range of 0–70°C           |                                                                                     | _                               | ± 0.3     | ± 1.5   | %f <sub>dco</sub>     | 1     |

| f <sub>intf_ft</sub>    |                                                                                                                      | frequency (fast clock) —<br>nominal VDD and 25°C                                    | —                               | 4         | —       | MHz                   |       |

| $\Delta f_{intf_{ft}}$  | (fast clock) over te                                                                                                 | on of internal reference clock<br>emperature and voltage —<br>mominal VDD and 25 °C | _                               | +1/-2     | ± 5     | %f <sub>intf_ft</sub> |       |

| f <sub>intf_t</sub>     | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C                                    |                                                                                     | 3                               | _         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external clock minimum frequency —<br>RANGE = 00                                                             |                                                                                     | (3/5) x<br>f <sub>ints_t</sub>  | _         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external cl<br>RANGE = 01, 10,                                                                               | lock minimum frequency —<br>or 11                                                   | (16/5) x<br>f <sub>ints_t</sub> | _         | —       | kHz                   |       |

|                         |                                                                                                                      | FL                                                                                  | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference free                                                                                                   | quency range                                                                        | 31.25                           | _         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                                                        | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                                    | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         |                                                                                                                      | Mid range (DRS=01)<br>1280 × f <sub>flL_ref</sub>                                   | 40                              | 41.94     | 50      | MHz                   |       |

|                         |                                                                                                                      | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>                              | 60                              | 62.91     | 75      | MHz                   |       |

|                         |                                                                                                                      | High range (DRS=11)<br>2560 × f <sub>fll ref</sub>                                  | 80                              | 83.89     | 100     | MHz                   |       |

| dco_t_DMX3<br>2         | DCO output<br>frequency                                                                                              | Low range (DRS=00)<br>732 × f <sub>fll_ref</sub>                                    |                                 | 23.99     |         | MHz                   | 5, 6  |

|                         |                                                                                                                      | Mid range (DRS=01)<br>1464 × f <sub>fll_ref</sub>                                   |                                 | 47.97     |         | MHz                   |       |

|                         |                                                                                                                      | Mid-high range (DRS=10)                                                             |                                 | 71.99     |         | MHz                   |       |

Table 16. MCG specifications

| Symbol                   | Description                |                                                                                   | Min.   | Тур.  | Max.                                | Unit | Notes |

|--------------------------|----------------------------|-----------------------------------------------------------------------------------|--------|-------|-------------------------------------|------|-------|

|                          |                            | $2197 \times f_{fll\_ref}$                                                        |        |       |                                     |      |       |

|                          |                            | High range (DRS=11)                                                               | _      | 95.98 | —                                   | MHz  |       |

|                          |                            | $2929 \times f_{fll_ref}$                                                         |        |       |                                     |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter          |                                                                                   |        | _     | _                                   | ps   |       |

|                          | • f <sub>VCO</sub> = 48 M  |                                                                                   | _      | 180   | _                                   |      |       |

|                          | • f <sub>VCO</sub> = 98 M  | Hz                                                                                |        | 150   |                                     |      |       |

| t <sub>fll_acquire</sub> | FLL target frequer         | ncy acquisition time                                                              |        | _     | 1                                   | ms   | 7     |

|                          | •                          | PI                                                                                | _L     | Į     | · · ·                               |      | 1     |

| f <sub>vco</sub>         | VCO operating fre          | equency                                                                           | 48.0   | _     | 120                                 | MHz  |       |

| I <sub>pll</sub>         | PLL operating cur          |                                                                                   | _      | 1060  | _                                   | μA   | 8     |

|                          |                            | /IHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>V multiplier = 48) |        |       |                                     | ŗ    |       |

| I <sub>pll</sub>         | PLL operating cur          | • •                                                                               |        |       |                                     |      | 8     |

| pii                      | • PLL @ 48 N               | /Hz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =                        | —      | 600   |                                     | μA   |       |

|                          |                            | V multiplier = 24)                                                                |        |       |                                     |      |       |

| f <sub>pll_ref</sub>     | PLL reference free         |                                                                                   | 2.0    | —     | 4.0                                 | MHz  |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (F       | RMS)                                                                              | —      | 120   |                                     | ps   | 9     |

|                          | • f <sub>vco</sub> = 48 MH | łz                                                                                | _      | 75    |                                     | ps   |       |

|                          | • f <sub>vco</sub> = 100 M | IHz                                                                               |        |       |                                     |      |       |

| J <sub>acc_pll</sub>     | PLL accumulated            | jitter over 1µs (RMS)                                                             |        | 1350  |                                     | ne   | 9     |

|                          | • f <sub>vco</sub> = 48 MH | łz                                                                                | —      | 600   |                                     | ps   |       |

|                          | • f <sub>vco</sub> = 100 M |                                                                                   |        | 600   |                                     | ps   |       |

|                          |                            | any talaranaa                                                                     | . 1 40 |       |                                     | 0/   |       |

| D <sub>lock</sub>        | Lock entry freque          |                                                                                   | ± 1.49 |       | ± 2.98                              | %    |       |

| D <sub>unl</sub>         | Lock exit frequence        |                                                                                   | ± 4.47 |       | ± 5.97                              | %    |       |

| t <sub>pll_lock</sub>    | Lock detector dete         | ection time                                                                       |        | _     | 150 × 10 <sup>-6</sup><br>+ 1075(1/ | S    | 10    |

|                          |                            |                                                                                   |        |       | f <sub>pll_ref</sub> )              |      |       |

| Table 16. | MCG s | pecifications | (continued) | ) |

|-----------|-------|---------------|-------------|---|

|-----------|-------|---------------|-------------|---|

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2.0 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 9. This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

## 3.3.2 IRC48M specifications

Table 17. IRC48M specifications

| Symbol                    | Description                                                                                          | Min. | Тур.  | Max.  | Unit                 | Notes |

|---------------------------|------------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| V <sub>DD</sub>           | Supply voltage                                                                                       | 1.71 | —     | 3.6   | V                    |       |

| I <sub>DD48M</sub>        | Supply current                                                                                       | _    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>       | Internal reference frequency                                                                         | _    | 48    |       | MHz                  |       |

| $\Delta f_{irc48m_ol_hv}$ | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over 0°C to 70°C      | _    |       |       |                      |       |

|                           | Regulator enable<br>(USB_CLK_RECOVER_IRC_EN[REG_EN]=1)                                               | —    | ± 0.2 | ± 0.5 | %f <sub>irc48m</sub> | 1     |

| $\Delta f_{irc48m_ol_hv}$ | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over full temperature |      |       |       |                      |       |

|                           | Regulator enable<br>(USB_CLK_RECOVER_IRC_EN[REG_EN]=1)                                               | —    | ± 0.4 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

| $\Delta f_{irc48m_ol_lv}$ | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over full temperature |      |       |       |                      | 1     |

|                           | Regulator disable<br>(USB_CLK_RECOVER_IRC_EN[REG_EN]=0)                                              | —    | ± 0.4 | ± 1.0 | %f <sub>irc48m</sub> |       |

|                           | Regulator enable<br>(USB_CLK_RECOVER_IRC_EN[REG_EN]=1)                                               | —    | ± 0.5 | ± 1.5 |                      |       |

| $\Delta f_{irc48m\_cl}$   | Closed loop total deviation of IRC48M frequency over voltage and temperature                         |      | _     | ± 0.1 | %f <sub>host</sub>   | 2     |

| J <sub>cyc_irc48m</sub>   | Period Jitter (RMS)                                                                                  | —    | 35    | 150   | ps                   |       |

| t <sub>irc48mst</sub>     | Startup time                                                                                         | —    | 2     | 3     | μs                   | 3     |

1. The maximum value represents characterized results equivalent to the mean plus or minus three times the standard deviation (mean ± 3 sigma).

- Closed loop operation of the IRC48M is only feasible for USB device operation; it is not usable for USB host operation. It is enabled by configuring for USB Device, selecting IRC48M as USB clock source, and enabling the clock recover function (USB\_CLK\_RECOVER\_IRC\_CTRL[CLOCK\_RECOVER\_EN]=1, USB\_CLK\_RECOVER\_IRC\_EN]=1).

- 3. IRC48M startup time is defined as the time between clock enablement and clock availability for system use. Enable the clock by one of the following settings:

- USB\_CLK\_RECOVER\_IRC\_EN[IRC\_EN]=1 or

- MCG operating in an external clocking mode and MCG\_C7[OSCSEL]=10 or MCG\_C5[PLLCLKEN0]=1, or

- SIM\_SOPT2[PLLFLLSEL]=11

## **3.3.3 Oscillator electrical specifications**

| Symbol | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|--------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|        | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  |      | V <sub>DD</sub> | _    | V    |       |

|        | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|        | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

Table 18.

Oscillator DC electrical specifications (continued)

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

- 4. When low-power mode is selected,  $R_F$  is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

## 3.3.3.2 Oscillator frequency specifications Table 19. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | —    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high-<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01) | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | _    | _    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency, low-power mode (HGO=0)                                   | —    | 750  |      | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  |      | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL or PLL.

- 2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

## 3.4.1.4 Reliability specifications Table 25. NVM reliability specifications

| Symbol                  | Description                            | Min. | Typ. <sup>1</sup> | Max. | Unit   | Notes |  |  |  |

|-------------------------|----------------------------------------|------|-------------------|------|--------|-------|--|--|--|

|                         | Program Flash                          |      |                   |      |        |       |  |  |  |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5    | 50                | _    | years  |       |  |  |  |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20   | 100               | _    | years  | _     |  |  |  |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K | 50 K              | _    | cycles | 2     |  |  |  |

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40 °C  $\leq$  T<sub>i</sub>  $\leq$  125 °C.

## 3.4.2 EzPort switching specifications Table 26. EzPort switching specifications

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 1.71                    | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | _                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | —                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | _                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 5                       | —                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 5                       | _                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 2                       | —                   | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)                | 5                       | —                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid                         | —                       | 25                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)                | 0                       | —                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state                       | —                       | 12                  | ns   |

| Symbol            | Description                               | Conditions                                                       | Min.             | Typ. <sup>1</sup> | Max.             | Unit | Notes |

|-------------------|-------------------------------------------|------------------------------------------------------------------|------------------|-------------------|------------------|------|-------|

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to $V_{SS}$ ( $V_{SS} - V_{SSA}$ )                         | -100             | 0                 | +100             | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high                |                                                                  | 1.13             | V <sub>DDA</sub>  | V <sub>DDA</sub> | V    |       |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                  | V <sub>SSA</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub> | V    |       |

| V <sub>ADIN</sub> | Input voltage                             | 16-bit differential mode                                         | VREFL            |                   | 31/32 *<br>VREFH | V    |       |

|                   |                                           | All other modes                                                  | VREFL            | _                 | VREFH            |      |       |

| C <sub>ADIN</sub> | Input                                     | 16-bit mode                                                      | _                | 8                 | 10               | pF   |       |

|                   | capacitance                               | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>            | _                | 4                 | 5                |      |       |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                  | —                | 2                 | 5                | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance<br>(external) | 13-bit / 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz               | _                | _                 | 5                | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | ≤ 13-bit mode                                                    | 1.0              |                   | 24.0             | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency         | 16-bit mode                                                      | 2.0              |                   | 12.0             | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion                            | ≤ 13-bit modes                                                   |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 20               | _                 | 1200             | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

| C <sub>rate</sub> | ADC conversion                            | 16-bit mode                                                      |                  |                   |                  |      | 5     |

|                   | rate                                      | No ADC hardware averaging                                        | 37               | —                 | 461              | Ksps |       |

|                   |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                  |                   |                  |      |       |

Table 27. 16-bit ADC operating conditions (continued)

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

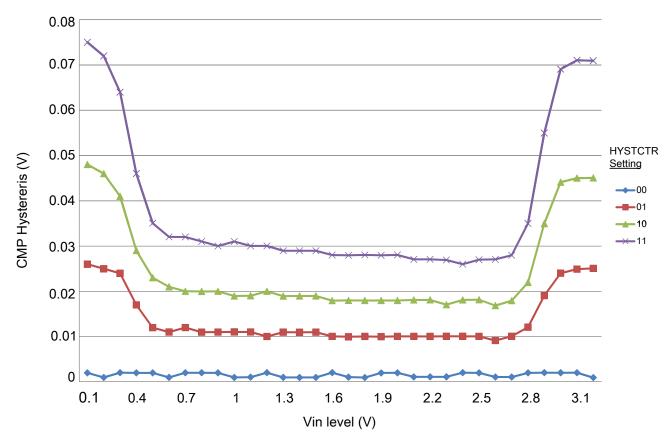

Figure 15. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

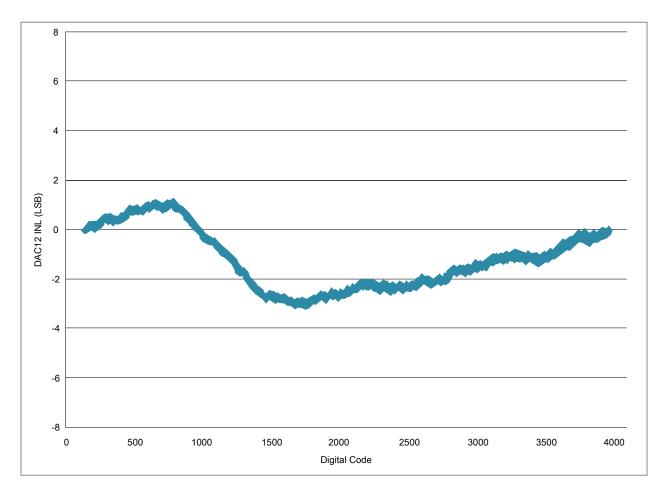

Figure 17. Typical INL error vs. digital code

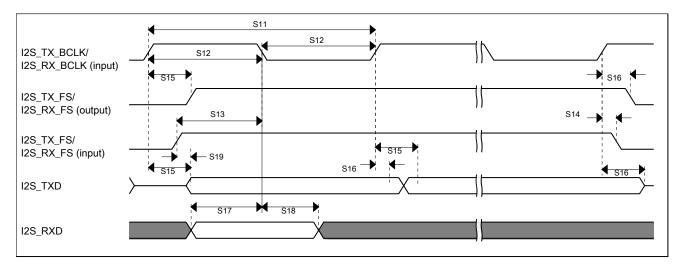

| Table 44. | I2S/SAI slave mode timing in Normal Run, Wait and Stop modes (limited voltage |

|-----------|-------------------------------------------------------------------------------|

|           | range) (continued)                                                            |

| Num. | Characteristic                                                  | Min. | Max. | Unit |

|------|-----------------------------------------------------------------|------|------|------|

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK | 2    | _    | ns   |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                   | —    | 20   | ns   |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                 | 0    | —    | ns   |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                | 4.5  | —    | ns   |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                  | 2    | —    | ns   |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>  |      | 25   | ns   |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 25. I2S/SAI timing — slave modes

# 3.8.7.2 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

# Table 45. I2S/SAI master mode timing in Normal Run, Wait and Stop modes (full voltage range)

| Num. | Characteristic                | Min. | Max. | Unit        |

|------|-------------------------------|------|------|-------------|

|      | Operating voltage             | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time           | 40   | _    | ns          |

| S2   | I2S_MCLK pulse width high/low | 45%  | 55%  | MCLK period |

# 5 Pinout

# 5.1 K22F Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

| 64<br>WLC<br>SP | Pin Name                                         | Default                                          | ALTO                                             | ALT1               | ALT2      | ALT3     | ALT4 | ALT5 | ALT6     | ALT7           | EzPort |

|-----------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------|-----------|----------|------|------|----------|----------------|--------|

| A8              | PTE0/<br>CLKOUT32K                               | ADC1_SE4a                                        | ADC1_SE4a                                        | PTE0/<br>CLKOUT32K | SPI1_PCS1 | UART1_TX |      |      | I2C1_SDA | RTC_<br>CLKOUT |        |

| B8              | PTE1/<br>LLWU_P0                                 | ADC1_SE5a                                        | ADC1_SE5a                                        | PTE1/<br>LLWU_P0   | SPI1_SOUT | UART1_RX |      |      | I2C1_SCL | SPI1_SIN       |        |

| D5              | VDD                                              | VDD                                              | VDD                                              |                    |           |          |      |      |          |                |        |

| D6              | VSS                                              | VSS                                              | VSS                                              |                    |           |          |      |      |          |                |        |

| C8              | USB0_DP                                          | USB0_DP                                          | USB0_DP                                          |                    |           |          |      |      |          |                |        |

| D8              | USB0_DM                                          | USB0_DM                                          | USB0_DM                                          |                    |           |          |      |      |          |                |        |

| C7              | VOUT33                                           | VOUT33                                           | VOUT33                                           |                    |           |          |      |      |          |                |        |

| D7              | VREGIN                                           | VREGIN                                           | VREGIN                                           |                    |           |          |      |      |          |                |        |

| E8              | ADC0_DP1                                         | ADC0_DP1                                         | ADC0_DP1                                         |                    |           |          |      |      |          |                |        |

| F8              | ADC0_DM1                                         | ADC0_DM1                                         | ADC0_DM1                                         |                    |           |          |      |      |          |                |        |

| E7              | ADC0_DP0/<br>ADC1_DP3                            | ADC0_DP0/<br>ADC1_DP3                            | ADC0_DP0/<br>ADC1_DP3                            |                    |           |          |      |      |          |                |        |

| F7              | ADC0_DM0/<br>ADC1_DM3                            | ADC0_DM0/<br>ADC1_DM3                            | ADC0_DM0/<br>ADC1_DM3                            |                    |           |          |      |      |          |                |        |

| G8              | VDDA                                             | VDDA                                             | VDDA                                             |                    |           |          |      |      |          |                |        |

| F6              | VREFH                                            | VREFH                                            | VREFH                                            |                    |           |          |      |      |          |                |        |

| G7              | VREFL                                            | VREFL                                            | VREFL                                            |                    |           |          |      |      |          |                |        |

| H8              | VSSA                                             | VSSA                                             | VSSA                                             |                    |           |          |      |      |          |                |        |

| G6              | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                    |           |          |      |      |          |                |        |

| G5              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                    |           |          |      |      |          |                |        |

| H7              | XTAL32                                           | XTAL32                                           | XTAL32                                           |                    |           |          |      |      |          |                |        |

| H6              | EXTAL32                                          | EXTAL32                                          | EXTAL32                                          |                    |           |          |      |      |          |                |        |

| H5              | VBAT                                             | VBAT                                             | VBAT                                             |                    |           |          |      |      |          |                |        |

## 6.2 Format

Part numbers for this device have the following format:

Q K## A M FFF R T PP CC N

# 6.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                                                                  |

|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow, full reel</li> <li>P = Prequalification</li> <li>K = Fully qualified, general market flow, 100 piece reel</li> </ul> |

| K##   | Kinetis family              | • K22                                                                                                                                                                   |

| A     | Key attribute               | <ul> <li>D = Cortex-M4 w/ DSP</li> <li>F = Cortex-M4 w/ DSP and FPU</li> </ul>                                                                                          |

| М     | Flash memory type           | <ul> <li>N = Program flash only</li> <li>X = Program flash and FlexMemory</li> </ul>                                                                                    |

| FFF   | Program flash memory size   | <ul> <li>128 = 128 KB</li> <li>256 = 256 KB</li> <li>512 = 512 KB</li> </ul>                                                                                            |

| R     | Silicon revision            | <ul> <li>Z = Initial</li> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                |

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul>                                                                                                               |

| PP    | Package identifier          | • AH = 64 WLCSP (3.36 mm x 3.33 mm)                                                                                                                                     |

| СС    | Maximum CPU frequency (MHz) | <ul> <li>5 = 50 MHz</li> <li>7 = 72 MHz</li> <li>10 = 100 MHz</li> <li>12 = 120 MHz</li> <li>15 = 150 MHz</li> </ul>                                                    |

| N     | Packaging type              | R = Tape and reel                                                                                                                                                       |

# 6.4 Example

This is an example part number:

MK22FN256CAH12R

# 7.2 Examples

## Operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |  |

|-----------------|------------------------------|------|------|------|--|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |  |

|                 |                              |      |      |      |  |

## Operating requirement:

| Operating require | ment:                        |      |      |      |

|-------------------|------------------------------|------|------|------|

| Symbol            | Description                  | Min. | Max. | Unit |

| V <sub>DD</sub>   | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

|                   |                              |      |      |      |

## Operating behavior that includes a typical value:

| Symbol          | Description                                    | Mi | n.    |    | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|----|-------|----|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10 | LANNE | 70 |      | 130  | μA   |

#### **Typical-value conditions** 7.3

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description         | Value | Unit |

|-----------------|---------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature | 25    | C°   |

| V <sub>DD</sub> | Supply voltage      | 3.3   | V    |

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address:<u>nxp.com/SalesTermsandConditions</u>.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, the Freescale logo, and Kinetis are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, the ARM Powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2014-2016 NXP B.V.

Document Number K22P64M120SF8 Revision 7, 08/2016