Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

⊡XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128b-i-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |

# REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

# Legend:

|                                   | Logona.           |                  |                           |                    |  |

|-----------------------------------|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                   |                  | U = Unimplemented bit, re | ad as '0'          |  |

|                                   | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/44-pin XLP Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program the Flash memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site (www.microchip.com).

Note: The Flash page size on PIC32MX-1XX/2XX 28/44-pin XLP Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

|                                 | IRQ | Vector |              | Interru       | pt Bit Location |              | Persistent |

|---------------------------------|-----|--------|--------------|---------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | #   | #      | Flag         | Enable        | Priority        | Sub-priority | Interrupt  |

|                                 |     | Highes | st Natural C | rder Priority | ,               |              |            |

| CT – Core Timer Interrupt       | 0   | 0      | IFS0<0>      | IEC0<0>       | IPC0<4:2>       | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0 | 1   | 1      | IFS0<1>      | IEC0<1>       | IPC0<12:10>     | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1 | 2   | 2      | IFS0<2>      | IEC0<2>       | IPC0<20:18>     | IPC0<17:16>  | No         |

| INT0 – External Interrupt       | 3   | 3      | IFS0<3>      | IEC0<3>       | IPC0<28:26>     | IPC0<25:24>  | No         |

| T1 – Timer1                     | 4   | 4      | IFS0<4>      | IEC0<4>       | IPC1<4:2>       | IPC1<1:0>    | No         |

| IC1E – Input Capture 1 Error    | 5   | 5      | IFS0<5>      | IEC0<5>       | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1           | 6   | 5      | IFS0<6>      | IEC0<6>       | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1          | 7   | 6      | IFS0<7>      | IEC0<7>       | IPC1<20:18>     | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1     | 8   | 7      | IFS0<8>      | IEC0<8>       | IPC1<28:26>     | IPC1<25:24>  | No         |

| T2 – Timer2                     | 9   | 8      | IFS0<9>      | IEC0<9>       | IPC2<4:2>       | IPC2<1:0>    | No         |

| IC2E – Input Capture 2          | 10  | 9      | IFS0<10>     | IEC0<10>      | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2           | 11  | 9      | IFS0<11>     | IEC0<11>      | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2          | 12  | 10     | IFS0<12>     | IEC0<12>      | IPC2<20:18>     | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2     | 13  | 11     | IFS0<13>     | IEC0<13>      | IPC2<28:26>     | IPC2<25:24>  | No         |

| T3 – Timer3                     | 14  | 12     | IFS0<14>     | IEC0<14>      | IPC3<4:2>       | IPC3<1:0>    | No         |

| IC3E – Input Capture 3          | 15  | 13     | IFS0<15>     | IEC0<15>      | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3           | 16  | 13     | IFS0<16>     | IEC0<16>      | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3          | 17  | 14     | IFS0<17>     | IEC0<17>      | IPC3<20:18>     | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3     | 18  | 15     | IFS0<18>     | IEC0<18>      | IPC3<28:26>     | IPC3<25:24>  | No         |

| T4 – Timer4                     | 19  | 16     | IFS0<19>     | IEC0<19>      | IPC4<4:2>       | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error    | 20  | 17     | IFS0<20>     | IEC0<20>      | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4           | 21  | 17     | IFS0<21>     | IEC0<21>      | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4          | 22  | 18     | IFS0<22>     | IEC0<22>      | IPC4<20:18>     | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4     | 23  | 19     | IFS0<23>     | IEC0<23>      | IPC4<28:26>     | IPC4<25:24>  | No         |

| T5 – Timer5                     | 24  | 20     | IFS0<24>     | IEC0<24>      | IPC5<4:2>       | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error    | 25  | 21     | IFS0<25>     | IEC0<25>      | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5           | 26  | 21     | IFS0<26>     | IEC0<26>      | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5          | 27  | 22     | IFS0<27>     | IEC0<27>      | IPC5<20:18>     | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done         | 28  | 23     | IFS0<28>     | IEC0<28>      | IPC5<28:26>     | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor  | 29  | 24     | IFS0<29>     | IEC0<29>      | IPC6<4:2>       | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and      | 30  | 25     | IFS0<30>     | IEC0<30>      | IPC6<12:10>     | IPC6<9:8>    | No         |

| Calendar                        | 04  |        |              |               |                 |              | NIa        |

| FCE – Flash Control Event       | 31  | 26     | IFS0<31>     | IEC0<31>      | IPC6<20:18>     | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt     | 32  | 27     | IFS1<0>      | IEC1<0>       | IPC6<28:26>     | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt     | 33  | 28     | IFS1<1>      | IEC1<1>       | IPC7<4:2>       | IPC7<1:0>    | No         |

| CMP3 – Comparator Interrupt     | 34  | 29     | IFS1<2>      | IEC1<2>       | IPC7<12:10>     | IPC7<9:8>    | No         |

| USB – USB Interrupts            | 35  | 30     | IFS1<3>      | IEC1<3>       | IPC7<20:18>     | IPC7<17:16>  | Yes        |

| SPI1E – SPI1 Fault              | 36  | 31     | IFS1<4>      | IEC1<4>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1RX – SPI1 Receive Done      | 37  | 31     | IFS1<5>      | IEC1<5>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1TX – SPI1 Transfer Done     | 38  | 31     | IFS1<6>      | IEC1<6>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|--------------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |

| 31:24        | _                 | —                 | _                 | —                 | _                 | _                    | _                        | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                    | —                        | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0                    | R/W-0            |

| 15:8         | _                 | —                 | _                 | —                 | —                 | S                    | RIPL<2:0> <sup>(1)</sup> |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0                    | R/W-0            |

| 7:0          | _                 | —                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                          |                  |

## REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | IPTMF             | R<31:24>          |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | IPTMR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | _                 | —                 | —                 | _                | -                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | -                 | _                 | —                 | —                 | —                 | _                | —                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | —                 | _                | _                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHPDAT            | ۲<7:0>            |                   |                  |                  |  |

# REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

# Legend:

| 3                                 |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

## bit 31-8 Unimplemented: Read as '0'

## bit 7-0 CHPDAT<7:0>: Channel Data Register bits

<u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        |                   | —                 | _                 | —                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 |                   | —                 | —                 | —                 | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | —                 | —                 | PREFE             | N<1:0>            | —                 | F                 | PFMWS<2:0>       | •                |

## REGISTER 10-1: CHECON: CACHE CONTROL REGISTER

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

## bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 **Unimplemented:** Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

## bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 | _                 | _                 |                   | _                 |                  | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | _                 |                   |                   |                   | -                 |                  | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | _                 |                   |                   |                   | -                 |                  | —                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |  |  |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | _                | VBUSVDIE         |  |  |

## REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

## bit 6 **T1MSECIE:** 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

## bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 **SESVDIE:** Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   | _                 | RXBUFELM<4:0>     |                   |                   |                   |                  |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | _                 | —                 |                   | Tک                | (BUFELM<4:(       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | _                 | _                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |

## REGISTER 19-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR + SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

#### I<sup>2</sup>C Control Registers 20.1

# TABLE 20-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |            |            |           |               |              |              |             | Bi         | ts        |                  |            |              |           |          |           |          |            |

|-----------------------------|---------------------------------|---------------|------------|------------|-----------|---------------|--------------|--------------|-------------|------------|-----------|------------------|------------|--------------|-----------|----------|-----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14      | 29/13     | 28/12         | 27/11        | 26/10        | 25/9        | 24/8       | 23/7      | 22/6             | 21/5       | 20/4         | 19/3      | 18/2     | 17/1      | 16/0     | All Resets |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON    |            | —<br>SIDL | —<br>SCLREL   | —<br>STRICT  | —<br>A10M    | —<br>DISSLW | —<br>SMEN  | —<br>GCEN | —<br>STREN       | —<br>ACKDT | —<br>ACKEN   | —<br>RCEN | —<br>PEN | —<br>RSEN | —<br>SEN | 0000       |

|                             |                                 | 31:16         | _          | _          |           |               |              |              |             |            |           |                  |            |              |           | - FLN    |           |          | 0000       |

| 5010                        | I2C1STAT                        | 15:0          | ACKSTAT    | TRSTAT     | _         |               | _            | BCL          | GCSTAT      | ADD10      | IWCOL     | I2COV            | D A        | <br>P        | S         | R_W      | RBF       | TBF      | 0000       |

|                             |                                 | 31:16         | —          | —          |           |               | _            |              | _           | _          |           | -                |            | -            | -         |          | _         | _        | 0000       |

| 5020                        | I2C1ADD                         | 15:0          | _          | _          | _         | _             | _            | _            |             |            |           |                  | Address    | Register     |           |          |           |          | 0000       |

|                             |                                 | 31:16         | _          | _          | _         | _             | _            | _            | _           | _          | _         | _                | _          | _            | _         | _        | —         | _        | 0000       |

| 5030                        | I2C1MSK                         | 15:0          | _          | _          | _         | _             | —            | _            |             |            |           |                  | Address Ma | ask Register |           |          |           |          | 0000       |

| 5040                        | I2C1BRG                         | 31:16         | _          |            |           | —             | —            | _            | —           | _          | _         | —                | —          | —            | —         | —        | —         | —        | 0000       |

| 5040                        | IZCIBRG                         | 15:0          | —          | _          | _         | —             |              |              |             |            | Βαι       | ud Rate Ger      | erator Reg | ister        |           |          |           |          | 0000       |

| 5050                        | I2C1TRN                         | 31:16         | -          |            |           | _             | _            | -            | —           |            | —         | _                | _          | -            |           |          | —         |          | 0000       |

| 3030                        |                                 | 15:0          |            |            | I         | _             | -            |              | —           | _          |           |                  |            | Transmit     | Register  |          |           |          | 0000       |

| 5060                        | I2C1RCV                         | 31:16         | —          | _          | _         | —             | —            | _            | —           | —          | —         | —                | —          | —            | —         | —        | —         | —        | 0000       |

| 0000                        |                                 | 15:0          | —          | —          | —         |               | —            | _            | —           | —          |           | -                |            | Receive      | Register  |          |           |          | 0000       |

| 5100                        | I2C2CON                         | 31:16         | —          | —          | —         | —             | —            | _            | —           | _          | _         | —                | —          | —            |           | —        | —         |          | 0000       |

|                             |                                 | 15:0          | ON         | _          | SIDL      | SCLREL        | STRICT       | A10M         | DISSLW      | SMEN       | GCEN      | STREN            | ACKDT      | ACKEN        | RCEN      | PEN      | RSEN      | SEN      | 1000       |

| 5110                        | I2C2STAT                        | 31:16         | —          | —          | _         | -             | _            | —            | —           | _          | —         | —                | —          | —            | —         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | ACKSTAT    | TRSTAT     | —         | _             | _            | BCL          | GCSTAT      | ADD10      | IWCOL     | I2COV            | D_A        | Р            | S         | R_W      | RBF       | TBF      | 0000       |

| 5120                        | I2C2ADD                         | 31:16         |            | _          |           |               | _            |              |             |            |           | —                |            | -            | —         | _        | —         | _        | 0000       |

|                             |                                 | 15:0<br>31:16 |            | _          | _         | —             | _            | _            |             |            |           |                  | Address    | Register     |           |          |           |          | 0000       |

| 5130                        | I2C2MSK                         | 15:0          |            |            |           | _             |              | _            |             | _          |           | —                |            | ask Register | —         | _        |           | —        | 0000       |

|                             |                                 | 31:16         |            |            |           |               |              |              |             |            |           |                  |            |              |           |          |           |          | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _          | _          | _         | _             |              |              |             |            | Bai       | I<br>ud Rate Ger | erator Reg | ister        |           |          |           |          | 0000       |

|                             |                                 | 31:16         | _          | _          | _         | _             | _            | _            | _           | _          |           |                  |            | _            | _         | _        | _         | _        | 0000       |

| 5150                        | I2C2TRN                         | 15:0          |            | _          | _         | _             |              |              |             | _          |           |                  |            | Transmit     | Register  |          |           |          | 0000       |

|                             |                                 | 31:16         | _          | _          | _         | _             | _            | _            | _           | _          | _         | _                | _          | _            |           | _        | —         | _        | 0000       |

| 5160                        | I2C2RCV                         | 15:0          | _          | _          | _         | _             | _            | _            | _           | _          |           |                  |            | Receive      | Register  |          |           |          | 0000       |

| Legen                       | d: x = u                        | nknow         | n value on | Reset; — = | unimpleme | ented, read a | as '0'. Rese | t values are | shown in h  | exadecimal |           |                  |            |              | <u> </u>  |          |           |          |            |

© 2016 Microchip Technology Inc.

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

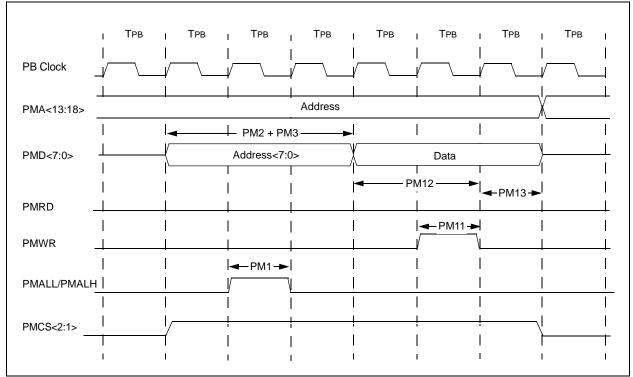

# 22.1 PMP Control Registers

# TABLE 22-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 0             |       |               |       |             |         |        |        | В      | its     |        |                |       |        |      |       |       | 6          |

|-----------------------------|---------------------------------|---------------|-------|---------------|-------|-------------|---------|--------|--------|--------|---------|--------|----------------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14         | 29/13 | 28/12       | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5           | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000                        | PMCON                           | 31:16         |       |               |       | _           |         |        | _      | _      | RDSTART |        | —              |       |        | _    | _     |       | 0000       |

| 1000                        | TWOON                           | 15:0          | ON    | —             | SIDL  | ADRMU       | JX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF<    | <1:0>  | ALP            | _     | CS1P   | _    | WRSP  | RDSP  | 0000       |

| 7010                        | PMMODE                          | 31:16         | —     | —             | —     | —           | —       | —      | —      | —      | —       | —      | —              | —     | —      | —    | —     | —     | 0000       |

| 1010                        | TIMIOBE                         | 15:0          | BUSY  | IRQM          | <1:0> | INCM        | <1:0>   | —      | MODE   | <1:0>  | WAITE   | 3<1:0> |                | WAITN | /<3:0> |      | WAITE | <1:0> | 0000       |

| 7020                        | PMADDR                          | 31:16         | _     | _             | _     | _           | _       |        | —      | —      | _       | —      | —              | —     | —      | —    | —     | _     | 0000       |

| . 020                       |                                 | 15:0          | —     | CS1           | —     | —           | —       |        |        |        |         | /      | ADDR<10:0      | >     |        |      |       |       | 0000       |

| 7030                        | PMDOUT                          | 31:16         |       | DATAOUT<31:0> |       |             |         |        |        |        |         |        |                |       |        |      |       |       |            |

|                             |                                 | 15:0          |       |               |       |             |         |        |        |        |         |        |                |       |        |      |       |       | 0000       |

| 7040                        | PMDIN                           | 31:16         |       |               |       |             |         |        |        | DATAIN | l<31:0> |        |                |       |        |      |       |       | 0000       |

|                             |                                 | 15:0          |       |               |       |             |         |        |        |        |         |        |                |       |        |      |       |       | 0000       |

| 7050                        | PMAEN                           | 31:16         | _     |               |       | —           | _       |        | —      | —      |         | —      |                | —     | _      | —    | —     | _     | 0000       |

|                             |                                 | 15:0          | _     | PTEN14        |       | _           | _       |        |        |        |         |        | PTEN<10:0:     |       |        |      |       |       | 0000       |

| 7060                        | PMSTAT                          | 31:16         | -     | -             |       | —           | -       | -      | -      | -      | -       |        | —              |       | -      | -    | -     | -     | 0000       |

|                             |                                 | 15:0<br>31:16 | IBF   | IBOV          |       |             | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   |                |       | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

| 7070                        | PMWADDR                         | 15:0          |       | WCS1          |       |             |         | _      | _      | _      | _       |        | <br>/ADDR<10:( |       | _      | _    | _     | _     | 0000       |

|                             |                                 | 31:16         |       |               |       |             |         |        |        |        |         |        |                |       |        |      |       |       |            |

| 7080                        | PMRADDR                         |               |       | -             |       |             |         | _      |        |        |         |        |                |       |        |      |       | _     |            |

|                             |                                 | 15:0          | _     | RCS1          |       | _           | _       |        |        |        |         |        | ADDR<10:0      |       |        |      |       |       | 0000       |

| 7090                        | PMRDIN                          | 31:16         | _     |               | _     | _           | _       | _      | _      |        | -       | _      | _              | _     | _      | _    | _     | —     | 0000       |

| Logon                       |                                 | 15:0          |       |               |       | ntod road a | (-1.5   |        |        | RDATAI |         |        |                |       |        |      |       |       | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

# REGISTER 22-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 TPB

- 01 = Wait of 2 Трв

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 Трв

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

# 25.1 Comparator Control Registers

# TABLE 25-1: COMPARATOR REGISTER MAP

| Bits                        |                                 |           |       |       |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| A 000                       | CM1CON                          | 31:16     | _     | _     | _     | _     | -     | _     |      |      | —    | —      | —    | _    |      | —     | —     | _     | 0000       |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     | —     | —     | —    | COUT | EVPO | L<1:0> | —    | CREF | —    | —     | CCH   | <1:0> | 00C3       |

| A010                        | CM2CON                          | 31:16     | -     | _     |       |       |       |       |      |      | -    | _      | _    | _    |      | _     | -     |       | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  |       |       |       |      | COUT | EVPO | L<1:0> | _    | CREF |      | _     | CCH   | <1:0> | 00C3       |

| A020                        | CM3CON                          | 31:16     | -     | _     |       |       |       |       |      |      | -    | _      | _    | _    |      | _     | -     |       | 0000       |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  |       |       |       | -    | COUT | EVPO | L<1:0> | -    | CREF | -    | -     | CCH   | <1:0> | 00C3       |

| A060                        | CMSTAT                          | 31:16     | -     | _     | -     |       |       |       |      |      | _    | _      | _    | _    |      | _     | _     |       | 0000       |

| 7000                        | CIVISTAI                        | 15:0      | _     | _     | SIDL  | _     | _     | _     |      | -    | _    | _      | _    | _    |      | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | -                 | -                 | —                 | _                 | -                | —                |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | -                 |                   | _                 | _                 |                   |                  | -                |  |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 10.0         | —                 | —                 | SIDL              |                   | _                 | —                 |                  | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7.0          |                   | _                 |                   |                   |                   | C3OUT             | C2OUT            | C1OUT            |  |  |  |

# REGISTER 25-2: CMSTAT: COMPARATOR STATUS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-14 Unimplemented: Read as '0'

## bit 13 **SIDL:** Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

### bit 12-3 Unimplemented: Read as '0'

## bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

## bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

## bit 0 **C1OUT:** Comparator Output bit

- 1 =Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|---------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0               | U-0                 | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                   | _                 | -                   | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0               | U-0                 | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                   | -                 | —                   |                  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | U-0                 | R/W-0            |

| 15:8         | ON                | _                 | _                 | _                 | VDIR <sup>(1)</sup> | BGVST             | —                   | HLVDET           |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0               | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                     | HLVDL<            | 3:0> <sup>(1)</sup> |                  |

## REGISTER 27-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleare  | d                  |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** HLVD Module Enable bit 1 = HLVD module is enabled 0 = HLVD module is disabled

- bit 14-12 Unimplemented: Read as '0'

- bit 11 VDIR: Voltage Change Direction Select bit<sup>(1)</sup>

- 1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>)

- 0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>)

- bit 10 **BGVST:** Band Gap Reference Voltages Stable Status bit

- 1 = Indicates internal band gap voltage references is stable

- 0 = Indicates internal band gap voltage reference is not stable

This bit is readable when the HLVD module is disabled (ON = 0).

- bit 9 Unimplemented: Read as '0'

- bit 8 HLVDET: High/Low-Voltage Detection Event Status bit

- 1 = Indicates HLVD Event interrupt is active

- 0 = Indicates HLVD Event interrupt is not active

- bit 7-4 Unimplemented: Read as '0'

- Note 1: To avoid false HLVD events, all HLVD module setting changes should occur only when the module is disabled (ON = 0). See Table 33-6 in the "Electrical Characteristics" chapter for the actual trip points.

# **30.0 SPECIAL FEATURES**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/44-pin XLP Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

# **30.1** Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- CFGCON: Configuration Control Register

In addition, the DEVID register (Register 30-6) provides device and revision information.

| Bit<br>Range           | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|------------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24                  | R/P                   | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 31:24                  | FDSEN                 | DSWDTEN           | DSWDTOSC          |                   | DS                | WDTPS<4:0:        | >                |                  |  |  |  |

| 23:16                  | R/P                   | r-1               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |  |  |

| 23.10                  | DSBOREN               | —                 | VBATBOREN         | BOREN             | —                 | FF                | PLLODIV<2:(      | )>               |  |  |  |

| 45.0                   | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |  |

| 15:8                   | UPLLEN <sup>(1)</sup> | —                 | —                 | —                 | —                 | UP                | LLIDIV<2:0>      | (1)              |  |  |  |

| 7.0                    | R/P                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |  |  |

| 7:0 FPLLICLK FPLLMUL<2 |                       |                   |                   | >                 |                   | F                 | PLLIDIV<2:0      | >                |  |  |  |

# REGISTER 30-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31 **FDSEN:** Deep Sleep Enable bit

1 = Deep Sleep mode is entered on a WAIT command

0 = Sleep mode is entered on a WAIT command

- bit 30 **DSWDTEN:** Deep Sleep Watchdog Timer Enable bit

- 1 = Enable the Deep Sleep Watchdog Timer (DSWDT) during Deep Sleep mode

- 0 = Disable the DSWDT during Deep Sleep mode

- bit 29 **DSWDTOSC:** Deep Sleep Watchdog Timer Reference Clock Select bit 1 = Select the LPRC Oscillator as the DSWDT reference clock 0 = Select the Secondary Oscillator as the DSWDT reference clock

# bit 28-24 **DSWDTPS<4:0>:** Deep Sleep Watchdog Timer Postscale Select bits

| 11111<br>11110<br>11100<br>11001<br>11000<br>11001<br>10010<br>10010<br>10010<br>10010 | $\begin{array}{c} 0 = 1 \\ 1 = 1 \\ 0 = 1 \\ 1 = 1 \\ 0 = 1 \\ 1 = 1 \\ 0 = 1 \\ 1 = 1 \\ 0 = 1 \\ 1 = 1 \\ 0 = 1 \\ 1 = 1 \\ 0 = 1 \end{array}$                                                                                                  | $2^{35}$<br>$2^{34}$<br>$2^{32}$<br>$2^{32}$<br>$2^{31}$<br>$2^{29}$<br>$2^{28}$<br>$2^{27}$<br>$2^{26}$<br>$2^{25}$<br>$2^{24}$<br>$2^{23}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                        | 1 = 1 = 1 $0 = 1 = 1$ $1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1$ $1 = 1 = 1 = 1 = 1 = 1$ | $2^{23}_{222}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{21}_{220}$<br>$2^{2$ |

Note 1: This bit is only available on PIC32MX2XX devices.

| DC CHARACTERISTICS                   |        |                                                           |         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |          |                                                                                         |  |

|--------------------------------------|--------|-----------------------------------------------------------|---------|-------------------------------------------------------|-------|----------|-----------------------------------------------------------------------------------------|--|

| Param.<br>No. Symbol Characteristics |        | Min.                                                      | Typical | Max.                                                  | Units | Comments |                                                                                         |  |

| D300                                 | VIOFF  | Input Offset Voltage                                      | -10     | _                                                     | +10   | mV       | AVDD = VDD,<br>AVSS = VSS                                                               |  |

| D301                                 | VICM   | Input Common Mode Voltage                                 | 0       | —                                                     | Vdd   | V        | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |

| D302                                 | CMRR   | Common Mode Rejection Ratio                               | 70      | —                                                     | _     | dB       | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |

| D303A                                | TRESP  | Large Signal Response Time                                | —       | 100                                                   | 80    | ns       | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |

| D303B                                | TSRESP | Small Signal Response Time                                | —       | 50                                                    | 160   | ns       | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |

| D304                                 | ON20V  | Comparator Enabled to Output<br>Valid                     | —       | —                                                     | 110   | μs       | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |

| D305                                 | IVref  | Internal Voltage Reference                                | 1.16    | 1.2                                                   | 1.24  | V        | —                                                                                       |  |

| D312                                 | TSET   | Internal Comparator Voltage<br>DRC Reference Setting time | _       | —                                                     | 1     | μs       | (Note 3)                                                                                |  |

# TABLE 33-14: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

| DC CHA                               |         | STICS                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                 |  |  |

|--------------------------------------|---------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|

| Param.<br>No. Symbol Characteristics |         |                                                             | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.               | Units | Comments                                                        |  |  |

| D312                                 | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                 | _    | 10                 | μs    | See Note 1                                                      |  |  |

| D313                                 | DACREFH | CVREF Input Voltage<br>Reference Range                      | AVss                                                                                                                                                                                                                                                                              | —    | AVdd               | V     | CVRSRC with CVRSS = 0                                           |  |  |

|                                      |         |                                                             | VREF-                                                                                                                                                                                                                                                                             | —    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |