Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

⊡XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128b-v-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams

### TABLE 3: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITH VBAT

| -P                                                              | IN SOIC (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                         |                                                                                                                                      | 1 28<br><b>SOIC</b>                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                 | PIC32MX155F128B<br>PIC32MX175F256B                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |                                                                                                                                                                                                                                                                               |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      |                                                                                                                                                                                                                                                                               |

|                                                                 | Full Die Norre                                                                                                                                                                                                                                                                                                                                                | <b>Din #</b>                                                                                                                         | Full Dia Nama                                                                                                                                                                                                                                                                 |

|                                                                 | Full Pin Name                                                                                                                                                                                                                                                                                                                                                 | <b>Pin #</b>                                                                                                                         | Full Pin Name PGEC3/RPB6/ASCL2/PMD6/RB6                                                                                                                                                                                                                                       |

|                                                                 | Full Pin Name<br>MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0                                                                                                                                                                                                                                                                                            | Pin #                                                                                                                                | Full Pin Name PGEC3/RPB6/ASCL2/PMD6/RB6 TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                                          |

|                                                                 | MCLR                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                                   | PGEC3/RPB6/ASCL2/PMD6/RB6                                                                                                                                                                                                                                                     |

|                                                                 | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0                                                                                                                                                                                                                                                                                                             | 15<br>16                                                                                                                             | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                                                     |

| E                                                               | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1                                                                                                                                                                                                                                                                      | 15<br>16<br>17                                                                                                                       | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                    |

| <b>#</b>                                                        | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0                                                                                                                                                                                                                              | 15<br>16<br>17<br>18                                                                                                                 | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                    |

|                                                                 | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1                                                                                                                                                                              | 15<br>16<br>17<br>18<br>19                                                                                                           | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>Vss                                                                                                                                             |

|                                                                 | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2                                                                                                                                      | 15<br>16<br>17<br>18<br>19<br>20                                                                                                     | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>Vss<br>VCAP                                                                                                                                     |

| #                                                               | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2<br>AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3                                                                                          | 15<br>16<br>17<br>18<br>19<br>20<br>21                                                                                               | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>Vss<br>VCAP<br>PGED1/RPB10/CTED11/PMD2/RB10                                                                                                     |

|                                                                 | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2<br>AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3<br>Vss                                                                                   | 15           16           17           18           19           20           21           22                                        | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>Vss<br>VCAP<br>PGED1/RPB10/CTED11/PMD2/RB10<br>PGEC1/TMS/RPB11/PMD1/RB11                                                                        |

| )                                                               | MCLR<br>WREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2<br>AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3<br>Vss<br>OSC1/CLKI/RPA2/RA2                                                             | 15           16           17           18           19           20           21           22           23                           | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>Vss<br>VCAP<br>PGED1/RPB10/CTED11/PMD2/RB10<br>PGEC1/TMS/RPB11/PMD1/RB11<br>AN12/PMD0/RB12<br>VBAT                                              |

| )                                                               | MCLR<br>WREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2<br>AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3<br>Vss<br>OSC1/CLKI/RPA2/RA2<br>OSC2/CLKO/RPA3/PMA0/RA3                                  | 15           16           17           18           19           20           21           22           23           24              | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED1/RPB10/CTED11/PMD2/RB10<br>PGEC1/TMS/RPB11/PMD1/RB11<br>AN12/PMD0/RB12                                                      |

| 1 #<br>2<br>3<br>4<br>5<br>5<br>7<br>3<br>3<br>0<br>1<br>2<br>3 | MCLR<br>VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0<br>VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1<br>PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0<br>PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1<br>AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2<br>AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3<br>Vss<br>OSC1/CLKI/RPA2/RA2<br>OSC2/CLKO/RPA3/PMA0/RA3<br>SOSCI/RPB4/RB4 <sup>(4)</sup> | 15           16           17           18           19           20           21           22           23           24           25 | PGEC3/RPB6/ASCL2/PMD6/RB6<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED1/RPB10/CTED11/PMD2/RB10<br>PGEC1/TMS/RPB11/PMD1/RB11<br>AN12/PMD0/RB12<br>VBAT<br>CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: This is an input-only pin.

NOTES:

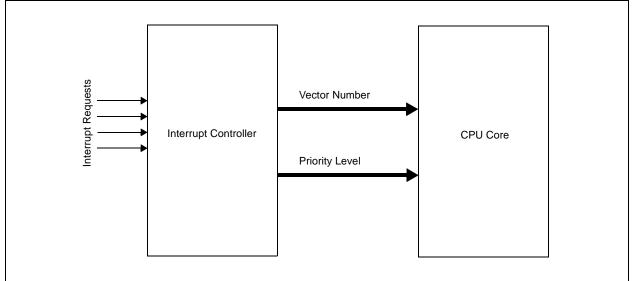

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/44-pin XLP Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU. The PIC32MX1XX/2XX 28/44-pin XLP Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- · User-configurable interrupt vector spacing

- Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/44-pin XLP Family devices.

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

## FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

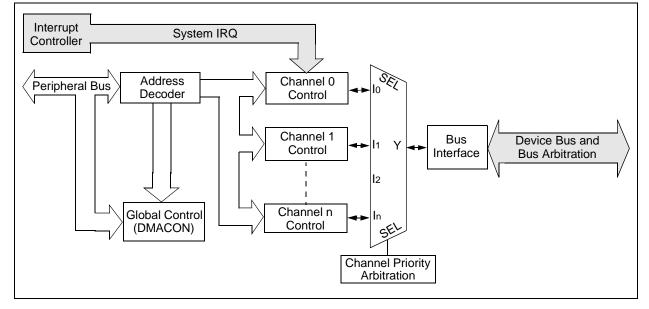

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

#### **TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP**

| SSS                         |                                 |               |            |           |            |             |             |            |            | Bi          | its     |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|------------|-----------|------------|-------------|-------------|------------|------------|-------------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14     | 29/13      | 28/12       | 27/11       | 26/10      | 25/9       | 24/8        | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16         | —          | _         |            | _           |             |            |            | —           | —       | —      | —      | —      | —      | —      |        |        | 0000       |

| 3000                        | DCHUCON                         | 15:0          | CHBUSY     | -         | -          | _           |             |            | —          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16         |            | —         | —          | —           | —           | _          | —          | —           |         |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3070                        | Denieleon                       | 15:0          |            |           |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | —      | _      |        | FF00       |

| 3080                        | DCH0INT                         | 31:16         |            | _         | _          | _           | _           | _          | —          | _           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 3000                        | Denoint                         | 15:0          |            | —         | —          | —           | —           | _          | —          | —           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |            |           |            |             |             |            |            | CHSSA       | <31:0>  |        |        |        |        |        |        |        | 0000       |

| 30A0                        | DCH0DSA                         | 31:16<br>15:0 |            |           |            |             |             |            |            | CHDSA       | A<31:0> |        |        |        |        |        |        |        | 0000       |

| 0000                        | 00100017                        | 31:16         | _          | _         | —          | _           | _           | _          | _          |             | —       | —      | _      | —      | —      | —      | _      | —      | 0000       |

| 30B0                        | DCH0SSIZ                        | 15:0          |            |           |            |             |             |            |            | CHSSIZ      | Z<15:0> |        |        |        |        |        |        |        | 0000       |

|                             | DOLIODOIZ                       | 31:16         | _          | _         | _          | _           | _           | _          | _          |             | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3000                        | DCH0DSIZ                        | 15:0          |            |           |            |             |             |            |            | CHDSIZ      | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 20000                       |                                 | 31:16         | _          | _         | _          | _           | _           | _          |            |             | _       | _      | _      | _      | _      |        | _      | _      | 0000       |

| 30D0                        | DCH0SPTR                        | 15:0          |            |           |            |             |             |            |            | CHSPTI      | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 2050                        |                                 | 31:16         | _          | _         | _          | _           | _           | _          |            |             | _       | _      | _      | _      | _      |        | _      | _      | 0000       |

| 30E0                        | DCH0DPTR                        | 15:0          |            |           |            |             |             |            |            | CHDPT       | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 2050                        | DOUDOOIZ                        | 31:16         | —          |           | _          | _           | _           | _          | _          | _           | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3050                        | DCH0CSIZ                        | 15:0          |            |           |            |             |             |            |            | CHCSIZ      | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 2100                        | DCH0CPTR                        | 31:16         | —          |           | _          | _           | _           | —          | _          | —           | —       | _      | _      | _      | _      | —      | _      | _      | 0000       |

| 3100                        | DCHUCPIK                        | 15:0          |            |           |            |             |             |            |            | CHCPT       | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16         | —          |           | _          | _           | _           | —          | _          | —           | _       | _      | _      | _      | _      | —      | _      | _      | 0000       |

| 3110                        | DCHUDAI                         | 15:0          |            | _         | _          | _           |             |            |            | —           |         |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 24.20                       | DCH1CON                         | 31:16         | —          |           | _          | _           | _           | _          | _          | _           | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3120                        | DUTICON                         | 15:0          | CHBUSY     | _         | —          | —           | _           | _          | _          | CHCHNS      | CHEN    | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | l<1:0> | 0000       |

| 2420                        |                                 | 31:16         | —          |           | _          | _           | _           | _          | _          | _           |         |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3130                        | DCH1ECON                        | 15:0          |            |           |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN |        |        |        | FF00       |

| 3140                        | DCH1INT                         | 31:16         | —          | _         | —          | _           | —           | _          |            | —           | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 3140                        |                                 | 15:0          | _          | _         | —          | _           | —           | _          |            | _           | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         |            |           |            |             |             |            |            | CHSSA       | x<31.0> |        |        |        |        |        |        |        | 0000       |

| 5150                        | DOITIOOA                        | 15:0          |            |           |            |             |             |            |            | 01008       |         |        |        |        |        |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |            |           |            |             |             |            |            | CHDSA       | -31.0>  |        |        |        |        |        |        |        | 0000       |

| 3100                        | DOILIDSA                        | 15:0          |            |           |            |             |             |            |            | CIIDSP      | 1.02    |        |        |        |        |        |        |        | 0000       |

| Leger                       | d. x = 11                       | nknowr        | value on R | eset: = I | unimplemen | nted read a | s '0' Reset | values are | shown in h | nexadecimal |         |        |        | -      |        |        |        |        |            |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more Note 1: information.

|              |                   | •••••             |                   |                   |                   | ••••              |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 |                   | _                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   |                   | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 |                   |                   |                   | -                 |                  | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | _                | VBUSVDIE         |

### REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

### bit 6 **T1MSECIE:** 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 **SESVDIE:** Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

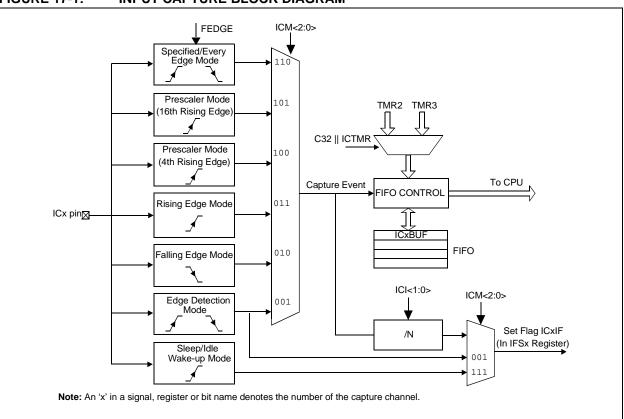

# 17.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- Input capture can also be used to provide additional sources of external interrupts

Figure 17-1 illustrates a general block diagram of the Input Capture module.

### FIGURE 17-1: INPUT CAPTURE BLOCK DIAGRAM

### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 10 UTXEN: Transmit Enable bit 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1) 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset The event of disabling an enabled transmitter will release the TX pin to the PORT function and Note: reset the transmit buffers to empty. Any pending transmission is aborted and data characters in the transmit buffers are lost. All transmit status flags are cleared and the TRMT bit is set bit 9 UTXBF: Transmit Buffer Full Status bit (read-only) 1 = Transmit buffer is full 0 = Transmit buffer is not full, at least one more character can be written bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer URXISEL<1:0>: Receive Interrupt Mode Selection bit bit 7-6 11 = Reserved10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 = Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only) 1 = Receive buffer has data, at least one more character can be read 0 =Receive buffer is empty

|              |                   |                   |                   |                   |                   |                   |                  | /                |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | —                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   |                   | OB3E              | OB2E              | OB1E             | OB0E             |

### REGISTER 22-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                           |                    |  |  |  |  |  |

|-------------------|--------------------------------------------|---------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                           | U = Unimplemented bit, re | ead as '0'         |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

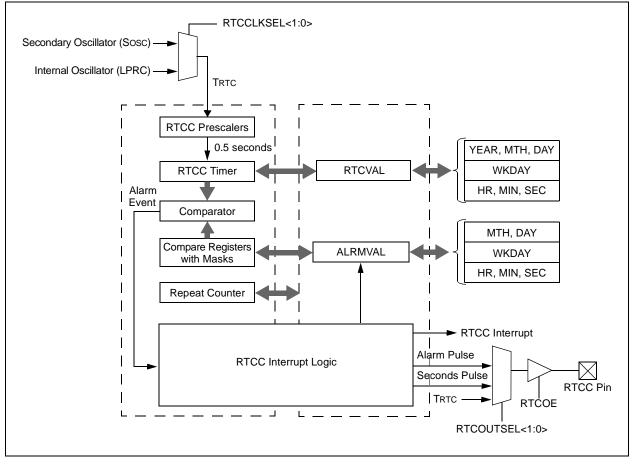

### FIGURE 23-1: RTCC BLOCK DIAGRAM

# 23.1 RTCC Control Registers

# TABLE 23-1: RTCC REGISTER MAP

| ess                         |                                 |           |        |       |          |          |       |                   |          |        | Bits     |          |           |          |         |         |            |       |            |

|-----------------------------|---------------------------------|-----------|--------|-------|----------|----------|-------|-------------------|----------|--------|----------|----------|-----------|----------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11 | 26/10             | 25/9     | 24/8   | 23/7     | 22/6     | 21/5      | 20/4     | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | —      | _     | —        | —        | _     | _                 |          |        |          |          | CAL       | <9:0>    |         |         |            |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON     | -     | SIDL     | —        | _     | RTCCLK            | SEL<1:0> | RTCOUT | SEL<1:0> | RTCCLKON | —         | —        | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | —      | -     | _        | —        | _     | —                 | —        | —      | —        | —        | —         | —        | —       | _       | —          | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC |       | AMAS              | <<3:0>   |        |          |          |           | ARPT     | <7:0>   |         |            |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     | _      | -     | HR1      | 0<1:0>   |       | HR01              | <3:0>    |        | _        | М        | IN10<2:0> | <b>`</b> |         | MIN01   | <3:0>      |       | xxxx       |

| 0220                        | RICHINE                         | 15:0      | _      |       | SEC10<2: | 0>       |       | SEC0              | 1<3:0>   |        | _        | —        | _         | _        | _       | -       | _          | —     | xx00       |

| 0000                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0>  |          |       | YEARC             | 1<3:0>   |        | —        | _        | —         | MONTH10  | )       | MONTH   | 01<3:0>    |       | xxxx       |

| 0230                        | RICDAIE                         | 15:0      | _      | _     | DAY      | 10<1:0>  |       | DAY0 <sup>-</sup> | <3:0>    |        | —        | —        | —         | —        | —       | W       | /DAY01<2:0 | >     | xx00       |

| 0040                        | ALRMTIME                        | 31:16     | —      | _     | HR1      | 0<1:0>   |       | HR01              | <3:0>    |        | —        | M        | IN10<2:0> | •        |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                 | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC0              | 1<3:0>   |        | —        | _        | —         | —        | —       | —       | _          | _     | xx00       |

| 0050                        | ALRMDATE                        | 31:16     | —      | -     | _        | —        | _     | _                 | —        | _      | _        | _        | _         | MONTH10  | )       | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        |                                 | 15:0      |        | DAY1  | 0<3:0>   | •        |       | DAY0 <sup>-</sup> | <3:0>    |        | —        | —        | _         | —        | —       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

# FRC<sup>(1)</sup> $\overrightarrow{Div 2}$ ADCS<7:0> ADCS<7:0> $\overrightarrow{ADCS}$ TPB<sup>(2)</sup> Note 1: See 33.0 "Electrical Characteristics" for the exact FRC clock value. 2: Refer to Figure 8-1 in 8.0 "Oscillator Configuration" for more information.

### FIGURE 24-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# 29.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features     |

|-------|---------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/44-pin XLP         |

|       | Family of devices. It is not intended to be |

|       | a comprehensive reference source. To        |

|       | complement the information in this data     |

|       | sheet, refer to Section 10. "Power-         |

|       | Saving Features" (DS60001130), which        |

|       | is available from the Documentation >       |

|       | Reference Manual section of the             |

|       | Microchip PIC32 web site                    |

|       | (www.microchip.com/pic32).                  |

This section describes power-saving features for the PIC32MX1XX/2XX 28/44-pin XLP Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 29.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

## 29.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 29.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 29.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See **29.3.3** "**Peripheral Bus Scaling Method**" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

### 29.3.4 DEEP SLEEP MODE

Deep Sleep mode brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device.

### • Deep Sleep

In this mode, the CPU, RAM and most peripherals are powered down. Power is maintained to the DSGPR0 register and one or more of the RTCC, DSWDT and DSGPR1 through DSGPR32 registers.

Which of these peripherals is active depends on the state of the following register bits when Deep Sleep mode is entered:

### • RTCDIS (DSCON<12>)

This bit must be set to disable the RTCC in Deep Sleep mode (see Register 29-1).

### DSWDTEN (DEVCFG2<30>)

This Configuration bit must be set to enable the DSWDT register in Deep Sleep mode (see Register 30-3)

### • DSGPREN (DSCON<13>)

This bit must be set to enable the DSGPR1 through DSGPR32 registers in Deep Sleep mode (see Register 29-1).

Note: The Deep Sleep Control registers can only be accessed after the system unlock sequence has been performed. In addition, the Deep Sleep Control registers must be written twice.

In addition to the conditionally enabled peripherals described above, the MCLR filter and INT0 pin are enabled in Deep Sleep mode.

### 29.3.5 VBAT MODE

VBAT mode is similar to Deep Sleep mode, except that the device is powered from the VBAT pin. VBAT mode is controlled strictly by hardware, without any software intervention. VBAT mode is initiated when VDD falls VPOR (refer the 33.0 "Electrical below to Characteristics" for definitions of VDD and VPOR). An external power source must be connected to the VBAT pin before power is removed from VDD to enter VBAT mode. VBAT is the lowest battery-powered mode that can maintain an RTCC. Wake-up from VBAT mode can only occur when VDD is reapplied. The wake-up will appear to be a POR to the rest of the device.

In VBAT mode, the Deep Sleep Watchdog Timer is disabled. The RTCC and DSGPR1 through DSGPR32 registers may be enabled or disabled depending on the state of the RTCDIS bit (DSCON<12>) and the DSGPREN bit (DSCON<13>), respectively. Deep Sleep Persistent General Purpose Register 0 (DSGPR0) is always enabled in VBAT mode.

### 29.3.6 XLP POWER-SAVING MODES

Figure 29-1 shows a block diagram of the system domain for XLP devices and the related power-saving features. The various blocks are controlled by the following Configuration bit settings and SFRs:

- DSBOREN (DEVCFG2<20>)

- DSEN (DSCON<15>)

- DSGPREN (DSCON<13>)

- DSWDTEN (DEVCFG2<30>)

- DSWDTOSC (DEVCFG2<29>)

- RELEASE (DSCON<0>)

- RTCCLKSEL (RTCCON <9:8>)

- RTCDIS (DSCON<12>)

- SLPEN (OSCCON<4>)

- VREGS (PWRCON<0>)

# 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

## 32.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 32.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC<br>CHARAC  | TERISTICS              |               |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                         |  |  |  |  |  |  |  |  |

|---------------|------------------------|---------------|-------|------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Maximum       | Units | Conditions                                           |                                                         |  |  |  |  |  |  |  |  |

| Power-Do      | own Curren             | t (IPD) (Note | 1)    |                                                      |                                                         |  |  |  |  |  |  |  |  |

| DC40k         |                        |               | μA    | -40°C                                                |                                                         |  |  |  |  |  |  |  |  |

| DC40I         | 25                     | 42            | μA    | +25°C                                                | Sloop (Note 1)                                          |  |  |  |  |  |  |  |  |

| DC40m         | 240                    | 390           | μA    | +85°C                                                | Sleep (Note 1)                                          |  |  |  |  |  |  |  |  |

| DC40n         | —                      |               | μA    | +105°C                                               |                                                         |  |  |  |  |  |  |  |  |

| DC41k         | _                      |               | nA    | -40°C                                                |                                                         |  |  |  |  |  |  |  |  |

| DC41I         | 673                    | 800           | nA    | +25°C                                                | Deep Sleep (Note 5)                                     |  |  |  |  |  |  |  |  |

| DC41m         | _                      |               | nA    | +85°C                                                | Deep Sleep (Note 5)                                     |  |  |  |  |  |  |  |  |

| DC41n         | _                      |               | nA    | +105°C                                               |                                                         |  |  |  |  |  |  |  |  |

| DC42k         | _                      |               | nA    | -40°C                                                |                                                         |  |  |  |  |  |  |  |  |

| DC42I         | _                      |               | nA    | +25°C                                                | VBAT <b>(Note 6)</b>                                    |  |  |  |  |  |  |  |  |

| DC42m         | _                      |               | nA    | +85°C                                                | VDAT (NOLE O)                                           |  |  |  |  |  |  |  |  |

| DC42n         | _                      | _             | nA    | +105°C                                               |                                                         |  |  |  |  |  |  |  |  |

| Module D      | oifferential (         | Current       |       |                                                      |                                                         |  |  |  |  |  |  |  |  |

| DC44a         | 5                      | _             | μA    | 3.6V                                                 | Watchdog Timer Current: AIWDT (Note 3)                  |  |  |  |  |  |  |  |  |

| DC44b         | 23                     | _             | μA    | 3.6V                                                 | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC + ΔITMR (Note 3) |  |  |  |  |  |  |  |  |

| DC44c         | 1000                   | _             | mA    | 3.6V                                                 | ADC Current: AIADC (Notes 3, 4)                         |  |  |  |  |  |  |  |  |

| DC44d         | 15                     | _             | μA    | 3.6V                                                 | Deadman Timer Current: ∆IDMT                            |  |  |  |  |  |  |  |  |

| DC44e         | 0.71                   | _             | μA    | 3.6V                                                 | Deep Sleep Watchdog Timer Current: ΔIDSWDT (Note 3)     |  |  |  |  |  |  |  |  |

| DC44f         | 0.8                    | _             | μA    | 3.6V                                                 | RTCC Current: AIRTCC (Note 3)                           |  |  |  |  |  |  |  |  |

### TABLE 33-9: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBMD = 1), VUSB3V3 is connected to VSS

- CPU is in Sleep mode

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), and the associated PMD bit is set. All clocks are disabled ON bit (PBxDIV<15>) = 0 (x ≠ 1,7)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD

- RTCC and JTAG are disabled

- Voltage regulator is in Stand-by mode (VREGS = 0; IOANCPEN = 0)

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Voltage regulator is operational (VREGS = 1).

- 5: The test conditions for Deep Sleep mode current measurements are as follows:

- All I/O pins are configured as inputs and pulled to Vss

- DSBOREN, DSWDTEN, and DGPREN are set to '0' and RTCDIS is set to '1'

- 6: The test conditions for VBAT mode current measurements is as follows:

- VBATBOREN is set to '0'

| DC CHA        |         | STICS                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                 |  |  |  |  |

|---------------|---------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.               | Units | Comments                                                        |  |  |  |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                 | _    | 10                 | μs    | See Note 1                                                      |  |  |  |  |

| D313          | DACREFH |                                                             | AVss                                                                                                                                                                                                                                                                              | —    | AVdd               | V     | CVRSRC with CVRSS = 0                                           |  |  |  |  |

|               |         | Reference Range                                             | VREF-                                                                                                                                                                                                                                                                             | —    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |  |  |

| D314          | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                                                                                                                                                 | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |  |  |

|               |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                 | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |  |  |

| D315          | DACRES  | Resolution                                                  | —                                                                                                                                                                                                                                                                                 |      | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |  |

|               |         |                                                             | —                                                                                                                                                                                                                                                                                 | _    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |  |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                            | —                                                                                                                                                                                                                                                                                 | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |  |

|               |         |                                                             | —                                                                                                                                                                                                                                                                                 | —    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |  |

### TABLE 33-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

### TABLE 33-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                                    |  |  |

|---------------|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol   | Characteristics                 | Min.                                                                                                                                                                                                                                                                              | Typical | Max. | Units | Comments                                                                                           |  |  |

| D321          | Cefc     | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                 | 10      |      | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |  |

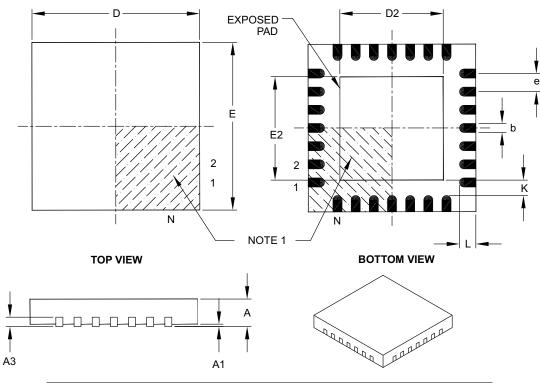

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          | MILLIMETERS |      |  |

|------------------------|-------|----------|-------------|------|--|

| Dimension Limits       |       | MIN      | NOM         | MAX  |  |

| Number of Pins         | Ν     | 28       |             |      |  |

| Pitch                  | е     | 0.65 BSC |             |      |  |

| Overall Height         | Α     | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1    | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3    | 0.20 REF |             |      |  |

| Overall Width          | E     | 6.00 BSC |             |      |  |

| Exposed Pad Width      | E2    | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D     | 6.00 BSC |             |      |  |

| Exposed Pad Length     | D2    | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b     | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L     | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | К     | 0.20     | _           | _    |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES: