Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| oduct Status             | Active                                                                         |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 72MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals               | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                          |

| umber of I/O             | 21                                                                             |

| ogram Memory Size        | 128KB (128K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| M Size                   | 32K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| ca Converters            | A/D 10x10b                                                                     |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 105°C (TA)                                                             |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| pplier Device Package    | 28-SOIC                                                                        |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128b-v-so |

#### TABLE 5: PIN NAMES FOR 28-PIN USB DEVICES WITH VBAT

28-PIN SOIC (TOP VIEW)(1,2,3)

1 28

SOIC

PIC32MX255F128B PIC32MX275F256B

| Pin# | Full Pin Name                                       |

|------|-----------------------------------------------------|

| 1    | MCLR                                                |

| 2    | PGED3/VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMD7/RA0     |

| 3    | PGEC3/VREF-/AN1/RPA1/ASCL1/CTED2/PMD6/RA1           |

| 4    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0           |

| 5    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/PMD1//RB1   |

| 6    | PGED1/AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2     |

| 7    | PGEC1/AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/PMWR/RB3 |

| 8    | Vss                                                 |

| 9    | OSC1/CLKI/RPA2/RA2                                  |

| 10   | OSC2/CLKO/RPA3/PMA0/RA3                             |

| 11   | SOSCI/RPB4/CTED11/RB4 <sup>(4)</sup>                |

| 12   | SOSCO/RPA4/T1CK/CTED9/RA4                           |

| 13   | VDD                                                 |

| 14   | TMS/RPB5/USBID/PMRD/RB5                             |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | VBUS                                           |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19   | Vss                                            |

| 20   | VCAP                                           |

| 21   | D+                                             |

| 22   | D-                                             |

| 23   | Vusb3v3                                        |

| 24   | VBAT                                           |

| 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMA1/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27   | AVss                                           |

| 28   | AVDD                                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

- **4:** This is an input-only pin.

#### **Table of Contents**

| 1.0   | Device Overview                                    | 19  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    | 33  |

| 3.0   | CPU                                                | 39  |

| 4.0   | Memory Organization                                | 43  |

| 5.0   | Flash Program Memory                               | 55  |

| 6.0   | Resets                                             |     |

| 7.0   | Interrupt Controller                               | 69  |

| 8.0   | Oscillator Configuration                           | 79  |

| 9.0   | Direct Memory Access (DMA) Controller              | 93  |

| 10.0  | Prefetch Cache                                     | 113 |

| 11.0  | USB On-The-Go (OTG)                                | 123 |

| 12.0  | I/O Ports                                          | 147 |

| 13.0  | Timer1                                             | 163 |

| 14.0  | Timer2/3, Timer4/5                                 | 167 |

| 15.0  | Watchdog Timer (WDT)                               | 173 |

| 16.0  | Deep Sleep Watchdog Timer (DSWDT)                  | 177 |

| 17.0  | Input Capture                                      | 179 |

|       | Output Compare                                     |     |

| 19.0  | Serial Peripheral Interface (SPI)                  | 187 |

|       | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART) | 203 |

| 22.0  | Parallel Master Port (PMP)                         | 211 |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 24.0  | 10-bit Analog-to-Digital Converter (ADC)           | 233 |

| 25.0  | Comparator                                         | 245 |

| 26.0  | Comparator Voltage Reference (CVREF)               | 249 |

| 27.0  | High/Low-Voltage Detect (HLVD)                     | 253 |

| 28.0  | Charge Time Measurement Unit (CTMU)                | 257 |

| 29.0  | Power-Saving Features                              | 263 |

| 30.0  | Special Features                                   | 277 |

| 31.0  | Instruction Set                                    | 291 |

| 32.0  | Development Support                                | 293 |

| 33.0  | Electrical Characteristics                         | 297 |

|       | DC and AC Device Characteristics Graphs            |     |

| 35.0  | Packaging Information                              | 345 |

| The I | Microchip Web Site                                 | 361 |

| Custo | omer Change Notification Service                   | 361 |

| Custo | omer Support                                       | 361 |

| Prod  | uct Identification System                          | 362 |

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 $^{\circledR}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

Note 1: Registers used in exception processing.

2: Registers used during debug.

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | -                 | _                 |                   |                   | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDKPBA<15:10>: DRM Kernel Program Base Address bits

When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|----------------------|---------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | RW-0, HC          | R/W-0, HC            | U-0                  | U-0                 |

| 31:24        | _                 | _                 | -                 | _                 | BCFGERR           | BCFGFAIL             | _                    | _                   |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | R/W-1, HS            | R/W-1, HS           |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                    | VBPOR <sup>(2)</sup> | VBAT <sup>(2)</sup> |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS            | R/W-0, HS            | U-0                 |

| 15:8         | _                 | _                 | _                 | _                 | _                 | DPSLP <sup>(1)</sup> | CMR                  | _                   |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS            | R/W-1, HS            | R/W-1, HS           |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE                 | BOR <sup>(1)</sup>   | POR <sup>(1)</sup>  |

**Legend:** HS = Hardware Set HC = Hardware Cleared

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 **Unimplemented:** Read as '0' bit **Unimplemented:** Read as '0'

bit 27 BCFGERR: Primary Configuration Registers Error Flag bit

1 = An error occurred during a read of the primary configuration registers0 = No error occurred during a read of the primary configuration registers

bit 26 BCFGFAIL: Primary/Secondary Configuration Registers Error Flag bit

1 = An error occurred during a read of the primary and alternate configuration registers 0 = No error occurred during a read of the primary and alternate configuration registers

bit 25-18 Unimplemented: Read as '0'

bit 17 **VBPOR:** VBPOR Mode Flag bit<sup>(2)</sup>

1 = A VBAT domain POR has occurred

0 = A VBAT domain POR has not occurred

bit 16 VBAT: VBAT Mode Flag bit<sup>(2)</sup>

1 = A POR exit from VBAT has occurred (a true POR must be established with the valid VBAT voltage on the VBAT pin)

0 = A POR exit from VBAT has not occurred

bit 15-11 Unimplemented: Read as '0'

bit 10 **DPSLP:** Deep Sleep Mode Flag bit<sup>(1)</sup>

1 = Deep Sleep mode has occurred

0 = Deep Sleep mode has not occurred

bit 9 CMR: Configuration Mismatch Reset Flag bit

1 = A Configuration Mismatch Reset has occurred

0 = A Configuration Mismatch Reset has not occurred

bit 8 Unimplemented: Read as '0'

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 **SWR:** Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset was not executed

bit 5 Unimplemented: Read as '0'

Note 1: User software must clear this bit to view the next detection.

2: This bit is only available on devices with VBAT.

**TABLE 12-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPA0                 | RPA0R    | RPA0R<3:0>  | 0000 = No Connect<br>0001 = U1TX           |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 0010 = <del>U2RTS</del>                    |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = SS1<br>0100 = VBUSON <sup>(4)</sup> |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 0101 = OC1<br>0110 = Reserved              |

| RPC7 <sup>(1)</sup>  | RPC7R    | RPC7R<3:0>  | 0111 = C2OUT                               |

| RPC0 <sup>(1)</sup>  | RPC0R    | RPC0R<3:0>  | 1000 = Reserved                            |

| RPC5 <sup>(1)</sup>  | RPC5R    | RPC5R<3:0>  | 1111 = Reserved                            |

| RPA1                 | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                          |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                |

| RPB11 <sup>(2)</sup> | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                  |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                            |

| RPA8 <sup>(1)</sup>  | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                               |

| RPC8 <sup>(1)</sup>  | RPC8R    | RPC8R<3:0>  | •                                          |

| RPA9 <sup>(1)</sup>  | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                            |

| RPA2                 | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                          |

| RPB6 <sup>(2)</sup>  | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved         |

| RPB13 <sup>(3)</sup> | RPB13R   | RPB13R<3:0> | 0011 = SDO1<br>0100 = SDO2                 |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 0101 = OC4<br>0110 = OC5                   |

| RPC6 <sup>(1)</sup>  | RPC6R    | RPC6R<3:0>  | 0111 = REFCLKO<br>1000 = Reserved          |

| RPC1 <sup>(1)</sup>  | RPC1R    | RPC1R<3:0>  | • • • • • • • • • • • • • • • • • • •      |

| RPC3 <sup>(1)</sup>  | RPC3R    | RPC3R<3:0>  | •<br>1111 = Reserved                       |

| RPA3                 | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                          |

| RPB14                | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0011 = Reserved<br>0100 = SS2              |

| RPB10 <sup>(2)</sup> | RPB10R   | RPB10R<3:0> | 0101 = OC3                                 |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT            |

| RPC9 <sup>(1)</sup>  | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                            |

| RPC2 <sup>(1)</sup>  | RPC2R    | RPC2R<3:0>  | <b>-</b>  -                                |

| RPC4 <sup>(1)</sup>  | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                            |

Note 1: This pin is only available on 44-pin devices.

<sup>2:</sup> This pin is not available on USB devices.

<sup>3:</sup> This pin is not available on VBAT devices.

<sup>4:</sup> This pin is only available on USB devices.

#### REGISTER 12-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A, B, C)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 |                   | _                 |                   |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | -                 | SIDL              | _                 | -                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = Idle mode halts CN operation0 = Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 31:24        | WDTCLRKEY<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22,16        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 23:16        | WDTCLRKEY<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R-y               | R-y               | R-y               | R-y              | R-y              |  |  |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | RUNDIV<4:0>       |                   |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | WDTWINEN         |  |  |

Legend:y = Values set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits

To clear the Watchdog Timer to prevent a time-out, software must write the value 0x5743 to these bits using a single 16-bit write.

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

1 = The Watchdog Timer module is enabled 0 = The Watchdog Timer module is disabled

bit 14-13 Unimplemented: Read as '0'

bit 12-8 RUNDIV<4:0>: Watchdog Timer Postscaler Value in Run Mode bits

In Run mode, these bits are set to the values of the WDTPS<4:0> Configuration bits in DEVCFG1.

bit 7-1 Unimplemented: Read as '0'

bit 0 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer0 = Disable windowed Watchdog Timer

**Note 1:** This bit only has control when FWDTEN (DEVCFG1<23>) = 0.

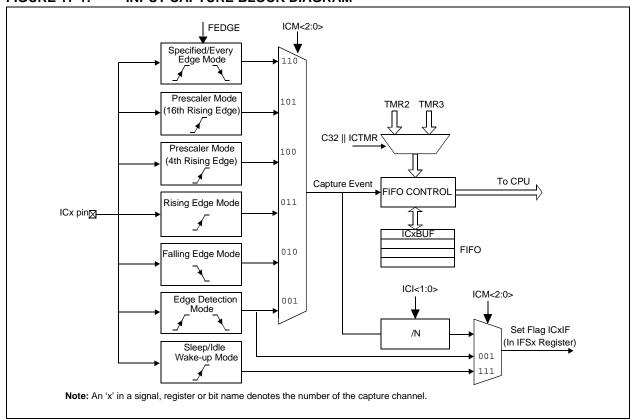

#### 17.0 INPUT CAPTURE

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- · Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- Input capture can also be used to provide additional sources of external interrupts

Figure 17-1 illustrates a general block diagram of the Input Capture module.

#### FIGURE 17-1: INPUT CAPTURE BLOCK DIAGRAM

**NOTES:**

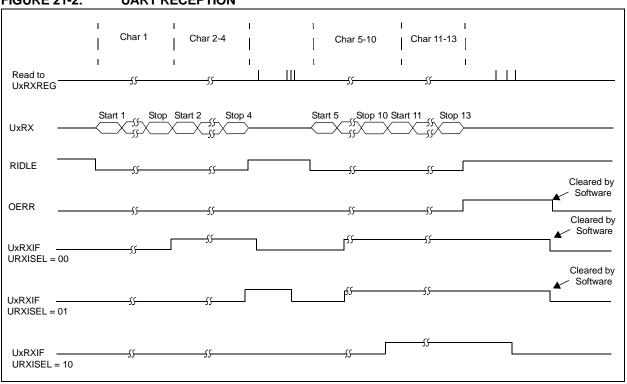

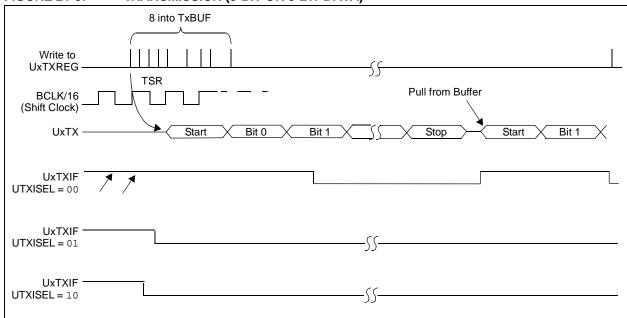

Figure 21-2 and Figure 21-3 illustrate typical receive and transmit timing for the UART module.

FIGURE 21-2: UART RECEPTION

FIGURE 21-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

#### REGISTER 22-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 7-6 **CSF<1:0>:** Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 functions as Chip Select

- 01 = PMCS1 functions as PMA<14>

- 00 = PMCS1 functions as PMA<14>

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$

- bit 4 Unimplemented: Read as '0'

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = Active-low (\overline{PMCS1})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

#### For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

#### For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = Read Strobe active-low (\overline{PMRD})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- $0 = \text{Read/write strobe active-low } (\overline{PMRD/PMWR})$

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

**NOTES:**

**TABLE 33-18: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA        | RACTERI       | STICS                                                                                                            | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |      |       |                                         |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------------------|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                           | Typ. <sup>(1)</sup> | Max. | Units | Conditions                              |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC                                                                                                                                                                                                                                             |                     | 50   | MHz   | EC (Note 3)                             |  |

| OS13          |               | Oscillator Crystal Frequency                                                                                     | 10                                                                                                                                                                                                                                             | _                   | 25   | MHz   | HS (Note 3)                             |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                             | 32.768              | 100  | kHz   | Sosc (Note 3)                           |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                              |                     | _    | _     | See parameter<br>OS10 for Fosc<br>value |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.375 x Tosc                                                                                                                                                                                                                                   | _                   | _    | ns    | EC (Note 3)                             |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                                                                              | _                   | 7.5  | ns    | EC (Note 3)                             |  |

| OS40          | Тоѕт          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                              | 1024                | _    | Tosc  | (Note 3)                                |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                                                                              | 2                   | _    | ms    | (Note 3)                                |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | 14                                                                                                                                                                                                                                             | 16                  | 18   | mA/V  | VDD = 3.3V,<br>TA = +25°C<br>(Note 3)   |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- 3: This parameter is characterized, but not tested in manufacturing.

#### TABLE 33-19: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                               | Standard<br>(unless of<br>Operating | herwise | ture -40°C | ≤ <b>T</b> A ≤ <b>+</b> | ·85°C for  | · Industrial<br>or V-temp      |

|--------------------|--------|---------------------------------------------------------------|-------------------------------------|---------|------------|-------------------------|------------|--------------------------------|

| Param.<br>No.      | Symbol | Characteristi                                                 | Min.                                | Typical | Max.       | Units                   | Conditions |                                |

| OS50               | FIN    | PLL Voltage Controlled Oscillator (VCO) Input Frequency Range |                                     | 4       | ı          | 5                       |            | ECPLL, HSPLL, and FRCPLL modes |

| OS51               | Fsys   | On-Chip VCO System Frequency                                  |                                     | 60      | _          | 120                     | MHz        | _                              |

-0.25

Note 1: These parameters are characterized, but not tested in manufacturing.

PLL Start-up Time (Lock Time)

(Period Jitter or Cumulative)

CLKO Stability<sup>(2)</sup>

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

2

+0.25

ms

%

period

Measured over 100 ms

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### **TABLE 33-20: INTERNAL FRC ACCURACY**

**OS52**

OS53

TLOCK

DCLK

| AC CHARACTERISTICS |                                                 | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |  |  |  |  |

|--------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|--|

| Param.<br>No.      | Characteristics                                 | Min.                                                                                                                                                                                                                                           | Typical | Max. | Units | Conditions |  |  |  |  |

| Internal           | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                |         |      |       |            |  |  |  |  |

| F20b               | FRC                                             | -0.9                                                                                                                                                                                                                                           | _       | +0.9 | %     | _          |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### **TABLE 33-21: INTERNAL LPRC ACCURACY**

| AC CHARACTERISTICS |                                 | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |  |  |  |  |

|--------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|--|

| Param.<br>No.      | Characteristics                 | Min.                                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |  |  |  |  |

| LPRC @             | LPRC @ 31.25 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                 |         |      |       |            |  |  |  |  |

| F21                | LPRC                            | -15                                                                                                                                                                                                                                             | _       | +15  | %     | _          |  |  |  |  |

Note 1: Change of LPRC frequency as VDD changes.

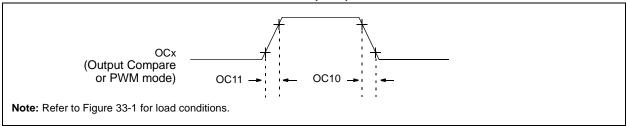

#### FIGURE 33-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 33-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                    |  |  |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| OC10               | TCCF   | OCx Output Fall Time           | _                                                                                                                                                                                                                                              | _                      | _    | ns    | See parameter DO32 |  |  |

| OC11               | TCCR   | OCx Output Rise Time           | _                                                                                                                                                                                                                                              | _                      |      | ns    | See parameter DO31 |  |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

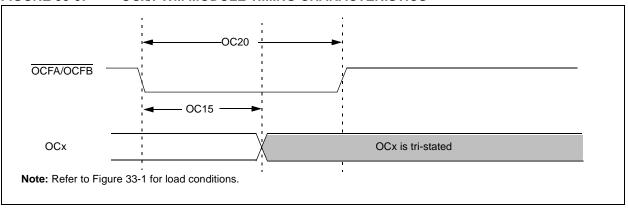

#### FIGURE 33-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 33-28: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                                       | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |     |       |            |  |

|--------------------|--------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol                               | Symbol Characteristics <sup>(1)</sup> |                                                                                                                                                                                                                                                 | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | 15 TFD Fault Input to PWM I/O Change |                                       | _                                                                                                                                                                                                                                               | _                      | 50  | ns    | _          |  |

| OC20               | TFLT                                 | Fault Input Pulse Width               | 50                                                                                                                                                                                                                                              | _                      | _   | ns    | _          |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE 33-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA        | RACTERIS               | STICS                      |                        | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |       |                                            |  |  |

|---------------|------------------------|----------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|--|

| Param.<br>No. | Symbol Characteristics |                            | eristics               | Min.                                                                                                                                                                                                                                           | Max. | Units | Conditions                                 |  |  |

| IS10          | TLO:SCL                | Clock Low Time             | 100 kHz mode           | 4.7                                                                                                                                                                                                                                            | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |

|               |                        |                            | 400 kHz mode           | 1.3                                                                                                                                                                                                                                            | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | 0.5                                                                                                                                                                                                                                            | _    | μS    | _                                          |  |  |

| IS11          | THI:SCL                | Clock High Time            | 100 kHz mode           | 4.0                                                                                                                                                                                                                                            | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |

|               |                        |                            | 400 kHz mode           | 0.6                                                                                                                                                                                                                                            | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | 0.5                                                                                                                                                                                                                                            | _    | μS    | _                                          |  |  |

| IS20          | TF:SCL                 | SDAx and SCLx<br>Fall Time | 100 kHz mode           |                                                                                                                                                                                                                                                | 300  | ns    | CB is specified to be from                 |  |  |

|               |                        |                            | 400 kHz mode           | 20 + 0.1 CB                                                                                                                                                                                                                                    | 300  | ns    | 10 to 400 pF                               |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | _                                                                                                                                                                                                                                              | 100  | ns    |                                            |  |  |

| IS21          | TR:SCL                 | SDAx and SCLx<br>Rise Time | 100 kHz mode           | _                                                                                                                                                                                                                                              | 1000 | ns    | CB is specified to be from                 |  |  |

|               |                        |                            | 400 kHz mode           | 20 + 0.1 CB                                                                                                                                                                                                                                    | 300  | ns    | 10 to 400 pF                               |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | _                                                                                                                                                                                                                                              | 300  | ns    |                                            |  |  |

| IS25          | Tsu:dat                | Data Input<br>Setup Time   | 100 kHz mode           | 250                                                                                                                                                                                                                                            | _    | ns    | _                                          |  |  |

|               |                        |                            | 400 kHz mode           | 100                                                                                                                                                                                                                                            |      | ns    |                                            |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | 100                                                                                                                                                                                                                                            | _    | ns    |                                            |  |  |

| IS26          | THD:DAT                | Data Input<br>Hold Time    | 100 kHz mode           | 0                                                                                                                                                                                                                                              |      | ns    | _                                          |  |  |

|               |                        |                            | 400 kHz mode           | 0                                                                                                                                                                                                                                              | 0.9  | μS    |                                            |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | 0                                                                                                                                                                                                                                              | 0.3  | μS    |                                            |  |  |

| IS30          | Tsu:sta                | Start Condition            | 100 kHz mode           | 4700                                                                                                                                                                                                                                           |      | ns    | Only relevant for Repeated                 |  |  |

|               |                        | Setup Time                 | 400 kHz mode           | 600                                                                                                                                                                                                                                            |      | ns    | Start condition                            |  |  |

|               |                        |                            | 1 MHz mode (Note 1)    | 250                                                                                                                                                                                                                                            | _    | ns    |                                            |  |  |

| IS31          | THD:STA                | Start Condition            | 100 kHz mode           | 4000                                                                                                                                                                                                                                           | _    | ns    | After this period, the first               |  |  |

|               |                        | Hold Time                  | 400 kHz mode           | 600                                                                                                                                                                                                                                            |      | ns    | clock pulse is generated                   |  |  |

|               |                        |                            | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                            | _    | ns    |                                            |  |  |

| IS33          | Tsu:sto                | Stop Condition             | 100 kHz mode           | 4000                                                                                                                                                                                                                                           | _    | ns    |                                            |  |  |

|               |                        | Setup Time                 | 400 kHz mode           | 600                                                                                                                                                                                                                                            | _    | ns    |                                            |  |  |

|               |                        |                            | 1 MHz mode<br>(Note 1) | 600                                                                                                                                                                                                                                            | _    | ns    |                                            |  |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

TABLE 33-35: ADC MODULE SPECIFICATIONS (CONTINUED)

|               | AC CHAR             | RACTERISTICS                   | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |              |      |       |                                                         |  |  |  |

|---------------|---------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol              | Characteristics                | Min.                                                                                                                                                                                                                                           | Typical      | Max. | Units | Conditions                                              |  |  |  |

| ADC Ac        | curacy – N          | leasurements with Inter        | nal VREF+/V                                                                                                                                                                                                                                    | REF-         |      |       | •                                                       |  |  |  |

| AD20d         | Nr                  | Resolution                     |                                                                                                                                                                                                                                                | 10 data bits | 3    | bits  | (Note 3)                                                |  |  |  |

| AD21d         | INL                 | Integral Non-linearity         | > -1                                                                                                                                                                                                                                           | — <1         |      | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.0V to 3.6V<br>(Note 3)    |  |  |  |

| AD22d         | DNL                 | Differential Non-linearity     | > -1                                                                                                                                                                                                                                           | _            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.0V to 3.6V<br>(Notes 2,3) |  |  |  |

| AD23d         | GERR                | Gain Error                     | > -4                                                                                                                                                                                                                                           | _            | < 4  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.0V to 3.6V<br>(Note 3)    |  |  |  |

| AD24d         | EOFF                | Offset Error                   | > -2                                                                                                                                                                                                                                           | _            | < 2  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.0V to 3.6V<br>(Note 3)    |  |  |  |

| AD25d         |                     | Monotonicity                   |                                                                                                                                                                                                                                                |              |      |       | Guaranteed                                              |  |  |  |

| Dynami        | Dynamic Performance |                                |                                                                                                                                                                                                                                                |              |      |       |                                                         |  |  |  |

| AD32b         | SINAD               | Signal to Noise and Distortion | 55                                                                                                                                                                                                                                             | 58.5         |      | dB    | (Notes 3,4)                                             |  |  |  |

| AD34b         | ENOB                | Effective Number of bits       | 9.0                                                                                                                                                                                                                                            | 9.5          |      | bits  | (Notes 3,4)                                             |  |  |  |

**Note 1:** These parameters are not characterized or tested in manufacturing.

- 2: With no missing codes.

- 3: These parameters are characterized, but not tested in manufacturing.

- 4: Characterized with a 1 kHz sine wave.

- **5:** The ADC module is functional at VBORMIN < VDD < 2.0V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

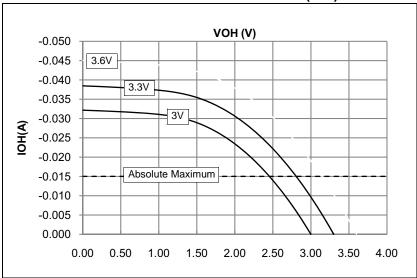

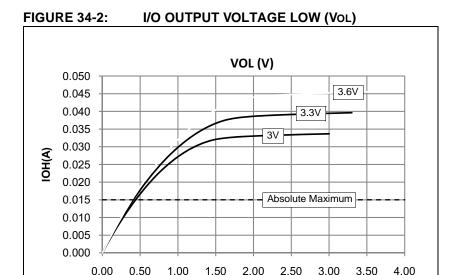

#### DC AND AC DEVICE CHARACTERISTICS GRAPHS 34.0

The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes Note: only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

**FIGURE 34-1:** I/O OUTPUT VOLTAGE HIGH (Voh)

0.50

PIC32MX1XX/2XX 28/44-PIN XLP FAMIL

4.00

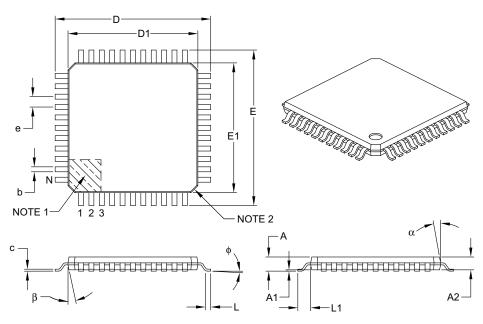

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |  |

|--------------------------|------------------|-------------|----------|------|--|--|

|                          | Dimension Limits | MIN         | MIN NOM  |      |  |  |

| Number of Leads          | N                |             | 44       |      |  |  |

| Lead Pitch               | е                |             | 0.80 BSC |      |  |  |

| Overall Height           | A                | _           | _        | 1.20 |  |  |

| Molded Package Thickness | A2               | 0.95        | 1.00     | 1.05 |  |  |

| Standoff                 | A1               | 0.05        | _        | 0.15 |  |  |

| Foot Length              | L                | 0.45        | 0.60     | 0.75 |  |  |

| Footprint                | L1               | 1.00 REF    |          |      |  |  |

| Foot Angle               | ф                | 0°          | 3.5°     | 7°   |  |  |

| Overall Width            | E                | 12.00 BSC   |          |      |  |  |

| Overall Length           | D                | 12.00 BSC   |          |      |  |  |

| Molded Package Width     | E1               | 10.00 BSC   |          |      |  |  |

| Molded Package Length    | D1               | 10.00 BSC   |          |      |  |  |

| Lead Thickness           | С                | 0.09        | _        | 0.20 |  |  |

| Lead Width               | b                | 0.30        | 0.37     | 0.45 |  |  |

| Mold Draft Angle Top     | α                | 11°         | 12°      | 13°  |  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°      | 13°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B