#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                          |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128d-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Pi                                                                                           | in Number <sup>(</sup> | 1)                     |             |                |                                                                    |                                 |

|----------|----------------------------------------------------------------------------------------------|------------------------|------------------------|-------------|----------------|--------------------------------------------------------------------|---------------------------------|

| Pin Name | 28-pin<br>QFN                                                                                | 28-pin<br>SOIC         | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                        |                                 |

|          |                                                                                              |                        |                        |             | PORTC          |                                                                    |                                 |

| RC0      | —                                                                                            |                        | 25                     | I/O         | ST             | PORTC is a bidirectional I/O port                                  |                                 |

| RC1      | —                                                                                            | —                      | 26                     | I/O         | ST             |                                                                    |                                 |

| RC2      | —                                                                                            | —                      | 27                     | I/O         | ST             |                                                                    |                                 |

| RC3      | —                                                                                            | —                      | 36                     | I/O         | ST             |                                                                    |                                 |

| RC4      | —                                                                                            | —                      | 37                     | I/O         | ST             |                                                                    |                                 |

| RC5      | —                                                                                            | —                      | 38                     | I/O         | ST             |                                                                    |                                 |

| RC6      | —                                                                                            | —                      | 2                      | I/O         | ST             |                                                                    |                                 |

| RC7      | —                                                                                            | —                      | 3                      | I/O         | ST             |                                                                    |                                 |

| RC8      | —                                                                                            | —                      | 4                      | I/O         | ST             |                                                                    |                                 |

| RC9      | —                                                                                            | —                      | 5                      | I/O         | ST             |                                                                    |                                 |

| •        | egend: CMOS = CMOS compatible input or output<br>ST = Schmitt Trigger input with CMOS levels |                        |                        |             |                | Analog = Analog input<br>O = Output<br>PPS = Peripheral Pin Select | P = Power<br>I=Input<br>— = N/A |

#### **TABLE 1-6:** PORTA THROUGH PORTC PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for General Purpose devices only.

3: This pin is not available for devices with VBAT.

4: This pin is not available for devices with USB.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | _                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | —                 | _                 | —                 | _                 | _                 | _                | —                |  |

| 45-0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |

# REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

## bit 9-0 **BMXDUDBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     | NVMOP<3:0>             |                   |                  |                  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                                                                                                                                                                                                           |

|          | <ul> <li>1 = Initiate a Flash operation. Hardware clears this bit when the operation completes</li> <li>0 = Flash operation is complete or inactive</li> </ul>                                                                                                                                    |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                                                                            |

|          | This is the only bit in this register reset by a device Reset.                                                                                                                                                                                                                                    |

|          | 1 = Enable writes to WR bit and enables HLVD circuit                                                                                                                                                                                                                                              |

|          | 0 = Disable writes to WR bit and disables HLVD circuit                                                                                                                                                                                                                                            |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                                                                                                                                                                                                             |

|          | This bit is read-only and is automatically set by hardware.                                                                                                                                                                                                                                       |

|          | 1 = Program or erase sequence did not complete successfully                                                                                                                                                                                                                                       |

|          | 0 = Program or erase sequence completed normally                                                                                                                                                                                                                                                  |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                                                                                                                                                                                                 |

|          | This bit is read-only and is automatically set by hardware.                                                                                                                                                                                                                                       |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                                                                                                                                                                                              |

|          | 0 = Voltage level is acceptable for programming                                                                                                                                                                                                                                                   |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                                                                                                                                                                                               |

|          | This bit is read-only and is automatically set and cleared by the hardware.                                                                                                                                                                                                                       |

|          | 1 = Low-voltage event is active                                                                                                                                                                                                                                                                   |

|          | 0 = Low-voltage event is not active                                                                                                                                                                                                                                                               |

| bit 10-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                        |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                                                                                                                                                                                                    |

|          | These bits are writable when $WREN = 0$ .                                                                                                                                                                                                                                                         |

|          | 1111 = Reserved                                                                                                                                                                                                                                                                                   |

|          | •                                                                                                                                                                                                                                                                                                 |

|          | •                                                                                                                                                                                                                                                                                                 |

|          | 0111 = Reserved                                                                                                                                                                                                                                                                                   |

|          | 0110 = No operation                                                                                                                                                                                                                                                                               |

|          | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected<br>0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected<br>0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected |

|          | 0010 = No operation                                                                                                                                                                                                                                                                               |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation                                                                                                                                                                             |

|          |                                                                                                                                                                                                                                                                                                   |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|----------------------|---------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | RW-0, HC          | R/W-0, HC            | U-0                  | U-0                 |

| 31:24        |                   | _                 | —                 | —                 | BCFGERR           | BCFGFAIL             | _                    | —                   |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | R/W-1, HS            | R/W-1, HS           |

| 23:16        |                   | _                 | _                 | —                 | _                 | _                    | VBPOR <sup>(2)</sup> | VBAT <sup>(2)</sup> |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS            | R/W-0, HS            | U-0                 |

| 15:8         |                   | _                 | —                 | —                 | _                 | DPSLP <sup>(1)</sup> | CMR                  | —                   |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS            | R/W-1, HS            | R/W-1, HS           |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE                 | BOR <sup>(1)</sup>   | POR <sup>(1)</sup>  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Hardware Set HC = Hardware Cleared |                           |                    |

|-------------------|-----------------------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit                        | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set                        | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31-29 | <b>Unimplemented:</b> | Read as '0' |

|-----------|-----------------------|-------------|

|-----------|-----------------------|-------------|

bit **Unimplemented:** Read as '0'

| bit 27    | BCFGERR: Primary Configuration Registers Error Flag bit                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------|

|           | 1 = An error occurred during a read of the primary configuration registers                                         |

|           | 0 = No error occurred during a read of the primary configuration registers                                         |

| bit 26    | BCFGFAIL: Primary/Secondary Configuration Registers Error Flag bit                                                 |

|           | 1 = An error occurred during a read of the primary and alternate configuration registers                           |

|           | 0 = No error occurred during a read of the primary and alternate configuration registers                           |

| bit 25-18 | Unimplemented: Read as '0'                                                                                         |

| bit 17    | VBPOR: VBPOR Mode Flag bit <sup>(2)</sup>                                                                          |

|           | 1 = A VBAT domain POR has occurred                                                                                 |

|           | 0 = A VBAT domain POR has not occurred                                                                             |

| bit 16    | VBAT: VBAT Mode Flag bit <sup>(2)</sup>                                                                            |

|           | 1 = A POR exit from VBAT has occurred (a true POR must be established with the valid VBAT voltage on the VBAT pin) |

|           | 0 = A POR exit from VBAT has not occurred                                                                          |

| bit 15-11 | Unimplemented: Read as '0'                                                                                         |

| bit 10    | DPSLP: Deep Sleep Mode Flag bit <sup>(1)</sup>                                                                     |

|           | 1 = Deep Sleep mode has occurred                                                                                   |

|           | 0 = Deep Sleep mode has not occurred                                                                               |

| bit 9     | CMR: Configuration Mismatch Reset Flag bit                                                                         |

|           | 1 = A Configuration Mismatch Reset has occurred                                                                    |

|           | 0 = A Configuration Mismatch Reset has not occurred                                                                |

| bit 8     | Unimplemented: Read as '0'                                                                                         |

| bit 7     | EXTR: External Reset (MCLR) Pin Flag bit                                                                           |

|           | 1 = Master Clear (pin) Reset has occurred                                                                          |

|           | 0 = Master Clear (pin) Reset has not occurred                                                                      |

| bit 6     | SWR: Software Reset Flag bit                                                                                       |

|           | 1 = Software Reset was executed                                                                                    |

|           | 0 = Software Reset was not executed                                                                                |

| bit 5     | Unimplemented: Read as '0'                                                                                         |

Note 1: User software must clear this bit to view the next detection.

2: This bit is only available on devices with VBAT.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-1               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | PBDIVRDY          | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x            | R/W-x            |

| 7:0          |                   |                   | _                 | _                 | _                 | _                 | PBDIV<1:0>       |                  |

# REGISTER 8-7: PB0DIV: PERIPHERAL BUS CLOCK 0 DIVISOR CONTROL REGISTER

### Legend:

| 5                 |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-12 Unimplemented: Read as '0'

bit 11 **PBDIVRDY:** Peripheral Bus 'x' Clock Divisor Ready bit

1 = Clock divisor logic is not switching divisors and the PBxDIV<6:0> bits may be written

0 = Clock divisor logic is currently switching values and the PBxDIV<6:0> bits cannot be written

- bit 10-2 Unimplemented: Read as '0'

- bit 1-0 **PBDIV<1:0>:** Peripheral Bus 'x' Clock Divisor Control bits

- 11 = PBCLKx is SYSCLK divided by 8

- 10 = PBCLKx is SYSCLK divided by 4

- 01 = PBCLKx is SYSCLK divided by 2

- 00 = PBCLKx is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 42. "Oscillators with Enhanced PLL"** (DS60001250) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                                 |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 **SUSPEND:** DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

#### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | —                 | _                 | —                 | —                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | _                 |                   |                   | RDWR              | Γ                 | DMACH<2:0>       | •                |

#### REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

#### Legend:

| 0                 |                                                         |                      |                    |

|-------------------|---------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | bit W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

#### REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | —                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

# REGISTER 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | W = Writable bit $U =$ Unimplemented bit, read as ' |                    |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |

# bit 31-24 Unimplemented: Read as '0'

|          | · · · · · · · · · · · · · · · · · · ·                                            |

|----------|----------------------------------------------------------------------------------|

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                                 |

|          | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                           |

|          | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                            |

|          | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                       |

|          | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                     |

|          | 1 = Interrupt is enabled                                                         |

| L:1 40   | 0 = Interrupt is disabled                                                        |

| bit 18   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                      |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>  |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                              |

| bit II   | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                               |

|          | 1 = Interrupt is enabled                                                         |

|          | 0 = Interrupt is disabled                                                        |

| bit 15-8 | Unimplemented: Read as '0'                                                       |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                   |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)           |

|          | 0 = No interrupt is pending                                                      |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                             |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)    |

|          | 0 = No interrupt is pending                                                      |

| bit 5    | CHDDIF: Channel Destination Done Interrupt Flag bit                              |

|          | 1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ) |

|          | 0 = No interrupt is pending                                                      |

#### Bit Rit Bit Rit Bit Rit Bit Bit Bit 31/23/15/7 30/22/14/6 29/21/13/5 28/20/12/4 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 R-0 R-0 U-0 U-0 R-0 R-0 U-0 R-0 7:0 ID LSTATE \_\_\_ SESVD SESEND VBUSVD \_\_\_\_ \_\_\_\_

#### **REGISTER 11-3: U1OTGSTAT: USB OTG STATUS REGISTER**

### Legend:

| Legena.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

#### bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|

| 21.24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |

| 31:24        | —                    | —                 |                     |                   | —                  |                   |                    | —                |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |

| 23:16        | —                    | —                 |                     |                   | —                  |                   | -                  | —                |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |

| 15:8         | ON <sup>(1,3)</sup>  | —                 | SIDL <sup>(4)</sup> | _                 | —                  | _                 | _                  | —                |  |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> |                   | TCS <sup>(3)</sup> | —                |  |

#### REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 00.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     |                   | —                 |                   | —                 | _                 |                   |                  | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | —                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

# REGISTER 17-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

# Legend:

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit                 |  |

|-------------------------------------|------------------|---------------------------------------|--|

| -n = Bit Value at POR: ('0', '1', x | = unknown)       | P = Programmable bit r = Reserved bit |  |

| bit 31-16 | Unimplemented: Read as '0'                                                                                            |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                             |

|           | 1 = Module is enabled                                                                                                 |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                |

| bit 14    | Unimplemented: Read as '0'                                                                                            |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                        |

|           | 1 = Halt in Idle mode                                                                                                 |

|           | 0 = Continue to operate in Idle mode                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                            |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                            |

|           | 1 = Capture rising edge first                                                                                         |

|           | 0 = Capture falling edge first                                                                                        |

| bit 8     | C32: 32-bit Capture Select bit                                                                                        |

|           | 1 = 32-bit timer resource capture                                                                                     |

|           | 0 = 16-bit timer resource capture                                                                                     |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                 |

|           | 0 = Timer3 is the counter source for capture                                                                          |

|           | 1 = Timer2 is the counter source for capture                                                                          |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                      |

|           | 11 = Interrupt on every fourth capture event                                                                          |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul> |

|           | 00 = Interrupt on every capture event                                                                                 |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                              |

|           | 1 = Input capture overflow has occurred                                                                               |

|           | 0 = No input capture overflow has occurred                                                                            |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                          |

|           | 1 = Input capture buffer is not empty; at least one more capture value can be read                                    |

|           | 0 = Input capture buffer is empty                                                                                     |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the                  |

| NOLE 1.   | SYSCLK cycle immediately following the instruction that clears the module's ON bit.                                   |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        | —                 | —                 | HR10              | <1:0>             |                   | HR01              | <3:0>            |                  |

| U-0          |                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                   |                  |                  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | —                 |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 | —                 | —                 | —                 | _                 | _                 | —                | _                |

|              |                   | •                 | •                 | •                 | •                 |                   | •                | •                |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Read     | ahle hit          |                   | W = Writable      | hit               | II – I Inimple    | emented bit re    | ad as 'O'        |                  |

# REGISTER 23-3: RTCTIME: RTC TIME VALUE REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

#### REGISTER 24-4: AD1CHS: ADC INPUT SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | CH0NB             | —                 | _                 | CH0SB<4:0>        |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            |                  |  |

| 23:16        | CHONA             |                   | _                 | CH0SA<4:0>        |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | -                 | _                 | —                 | _                 |                   | _                | _                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 |                   |                   | _                 | _                 | _                |                  |  |

# Legend:

bit 23

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31 CH0NB: Negative Input Select bit for Sample B 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VREFL bit 30-29 Unimplemented: Read as '0' bit 28-24 CH0SB<4:0>: Positive Input Select bits for Sample B 11111 = Reserved •

- 10010 = Reserved

10001 = Channel 0 positive input is VDD/2

10000 = Channel 0 positive input is VBAT

01111 = Reserved

01101 = Channel 0 positive input is IVREF<sup>(1)</sup>

01101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

01100 = Channel 0 positive input is AN12<sup>(3)</sup>

.

.

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

CHONA: Negative Input Select bit for Sample A Multiplexer Setting<sup>(1)</sup>

1 = Channel 0 negative input is AN1

0 = Channel 0 negative input is VREFL

- bit 22-21 Unimplemented: Read as '0'

Note 1: See 26.0 "Comparator Voltage Reference (CVREF)" for more information.

- 2: See 28.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 |                   | —                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 23:16        | —                 | —                 | _                 | _                 | —                 | —                 | CSSL17           | CSSL16           |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

#### REGISTER 24-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-18 Unimplemented: Read as '0'

- bit 17-0 CSSL<17:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

- 1 = Select ANx for input scan

- 0 =Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMUT input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan; CSSL16 selects VBAT; CSSL17 selects VDD/2.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

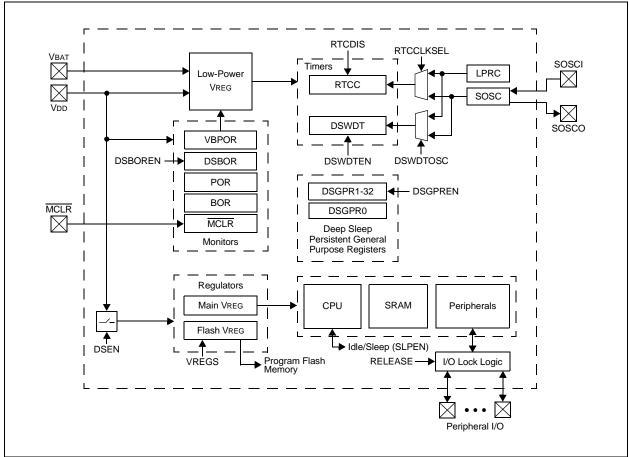

# FIGURE 29-1: XLP DEVICE BLOCK DIAGRAM

# **33.1 DC Characteristics**

# TABLE 33-1: OPERATING MIPS VS. VOLTAGE

|                | Vod Bongo                              | Tomp Bongo             | Max. Frequency                         |

|----------------|----------------------------------------|------------------------|----------------------------------------|

| Characteristic | VDD Range<br>(in Volts) <sup>(1)</sup> | Temp. Range<br>(in °C) | PIC32MX1XX/2XX 28/44-pin XLP<br>Family |

| DC5            | 2.5-3.6V                               | -40°C to +85°C         | 72 MHz                                 |

| DC5a           | 2.5-3.6V                               | -40°C to +105°C        | 72 MHz                                 |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 33-5 for BOR values.

# TABLE 33-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Minimum     | Typical     | Maximum | Unit |

|--------------------------------------------------------------------------------------|--------|-------------|-------------|---------|------|

| Industrial Temperature Devices                                                       |        |             |             |         |      |

| Operating Junction Temperature Range                                                 | TJ     | -40         | —           | +125    | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40         | —           | +85     | °C   |

| V-temp Temperature Devices                                                           |        |             |             |         |      |

| Operating Junction Temperature Range                                                 | TJ     | -40         | —           | +140    | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40         | —           | +105    | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD - S IOH) | PD     | PINT + PI/O |             | ×       |      |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |             |             |         |      |

| Maximum Allowed Power Dissipation                                                    | PDMAX  | (           | TJ — ΤΑ)/θ. | JA      | W    |

# TABLE 33-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                         | Symbol | Typical | Maximum | Unit | Notes |

|-----------------------------------------|--------|---------|---------|------|-------|

| Package Thermal Resistance, 28-pin SOIC | θJA    | 50      | —       | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN  | θJA    | 35      | —       | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN  | θJA    | 32      | —       | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP | θJA    | 45      | _       | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHARACTERISTICS |         |                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |                    |     |                                                                 |  |  |

|--------------------|---------|-------------------------------------------------------------|-------------------------------------------------------|---|--------------------|-----|-----------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics                                             | Min. Typ. Max. Units Comments                         |   |                    |     |                                                                 |  |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                     | _ | 10                 | μs  | See Note 1                                                      |  |  |

| D313               | DACREFH |                                                             | AVss                                                  | — | AVdd               | V   | CVRSRC with CVRSS = 0                                           |  |  |

|                    |         | Reference Range                                             | VREF-                                                 | — | VREF+              | V   | CVRSRC with CVRSS = 1                                           |  |  |

| D314               | DVref   | CVREF Programmable<br>Output Range                          | 0                                                     | _ | 0.625 x<br>DACREFH | V   | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |

|                    |         |                                                             | 0.25 x<br>DACREFH                                     | _ | 0.719 x<br>DACREFH | V   | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |

| D315               | DACRES  | Resolution                                                  | —                                                     | _ | DACREFH/24         |     | CVRCON <cvrr> = 1</cvrr>                                        |  |  |

|                    |         |                                                             | —                                                     | _ | DACREFH/32         | -   | CVRCON <cvrr> = 0</cvrr>                                        |  |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                            | —                                                     | _ | 1/4                | LSB | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |

|                    |         |                                                             | —                                                     | _ | 1/2                | LSB | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |

### TABLE 33-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 33-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                                    |  |

|--------------------|--------|---------------------------------|-------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                  | Typical | Max. | Units | Comments                                                                                           |  |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                     | 10      |      | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |

### TABLE 33-19: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |         |       |       |                                   |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|-----------------------------------|--|

| Param.<br>No.      | Symbol | Characteristi                                                       | cs <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Min.  | Typical | Max.  | Units | Conditions                        |  |