Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                          |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| rogram Memory Type         | FLASH                                                                          |

| EPROM Size                 | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| /oltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Oata Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128d-v-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES WITHOUT VBAT

28-PIN SOIC (TOP VIEW)(1,2,3)

28

SOIC

PIC32MX254F128B PIC32MX274F256B

| Pin# | Full Pin Name                                     |

|------|---------------------------------------------------|

| 1    | MCLR                                              |

| 2    | PGED3/VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMD7/RA0   |

| 3    | PGEC3/VREF-/AN1/RPA1/ASCL1/CTED2/PMD6/RA1         |

| 4    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         |

| 5    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/PMD1//RB1 |

| 6    | PGED1/AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2   |

| 7    | PGEC1/AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3     |

| 8    | Vss                                               |

| 9    | OSC1/CLKI/RPA2/RA2                                |

| 10   | OSC2/CLKO/RPA3/PMA0/RA3                           |

| 11   | SOSCI/RPB4/CTED11/RB4 <sup>(4)</sup>              |

| 12   | SOSCO/RPA4/T1CK/CTED9/RA4                         |

| 13   | VDD                                               |

| 14   | TMS/RPB5/USBID/RB5                                |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | VBUS                                           |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19   | Vss                                            |

| 20   | VCAP                                           |

| 21   | D+                                             |

| 22   | D-                                             |

| 23   | Vusb3v3                                        |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMA1/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27   | AVss                                           |

| 28   | AVDD                                           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

- 4: This is an input-only pin.

### TABLE 7: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITH VBAT

28-PIN QFN (TOP VIEW)(1,2,3.4)

PIC32MX155F128D PIC32MX175F256D

28

1

| Pin# | Full Pin Name                               |

|------|---------------------------------------------|

| 1    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0        |

| 2    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/RB1 |

| 3    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2        |

| 4    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3    |

| 5    | Vss                                         |

| 6    | OSC1/CLKI/RPA2/RA2                          |

| 7    | OSC2/CLKO/RPA3/PMA0/RA3                     |

| 8    | SOSCI/RPB4/RB4 <sup>(5)</sup>               |

| 9    | SOSCO/RPA4/T1CK/CTED9/RA4                   |

| 10   | VDD                                         |

| 11   | PGED3/RPB5/ASDA2/PMD7/RB5                   |

| 12   | PGEC3/RPB6/ASCL2/PMD6/RB6                   |

| 13   | TDI/RPB7/CTED3/PMD5/INT0/RB7                |

| 14   | TCK/RPB8/SCL1/CTED10/PMD4/RB8               |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 16   | Vss                                            |

| 17   | VCAP                                           |

| 18   | PGED1/RPB10/CTED11/PMD2/RB10                   |

| 19   | PGEC1/TMS/RPB11/PMD1/RB11                      |

| 20   | AN12/PMD0/RB12                                 |

| 21   | VBAT                                           |

| 22   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 24   | AVss                                           |

| 25   | AVDD                                           |

| 26   | MCLR                                           |

| 27   | VREF+/AN0/C3INC/RPA0ASDA1//CTED1/PMA1/RA0      |

| 28   | VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1            |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

- 5: This is an input-only pin.

**TABLE 1-11: COMPARATOR 1, COMPARATOR 2, AND COMPARATOR VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS**

|          | Pi            | in Number                | (1) |                         |            |                                        |

|----------|---------------|--------------------------|-----|-------------------------|------------|----------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin QFN/<br>SOIC TQFP |     | Pin Buffer<br>Type Type |            | Description                            |

|          |               |                          | Co  | mparate                 | or Voltage | Reference                              |

| VREF-    | 28            | 3                        | 20  | I                       | Analog     | Comparator Voltage Reference (Low)     |

| VREF+    | 27            | 2                        | 19  | I                       | Analog     | Comparator Voltage Reference (High)    |

| CVREFOUT | 22            | 25                       | 14  | 0                       | Analog     | Comparator Voltage Reference Output    |

|          |               |                          |     | С                       | omparator  | 1                                      |

| C1INA    | 4             | 7                        | 24  | I                       | Analog     | Comparator 1 Positive Input            |

| C1INB    | 3             | 6                        | 23  | I                       | Analog     | Comparator 1 Selectable Negative Input |

| C1INC    | 2             | 5                        | 22  | I                       | Analog     |                                        |

| C1IND    | 1             | 4                        | 21  | I                       | Analog     |                                        |

| C1OUT    | PPS           | PPS                      | PPS | 0                       | _          | Comparator 1 Output                    |

|          |               |                          |     | С                       | omparator  | 2                                      |

| C2INA    | 2             | 5                        | 22  | I                       | Analog     | Comparator 2 Positive Input            |

| C2INB    | 1             | 4                        | 21  | I                       | Analog     | Comparator 2 Selectable Negative Input |

| C2INC    | 4             | 7                        | 24  | I                       | Analog     |                                        |

| C2IND    | 3             | 6                        | 23  | I                       | Analog     |                                        |

| C2OUT    | PPS           | PPS                      | PPS | 0                       | _          | Comparator 2 Output                    |

|          |               |                          |     | С                       | omparator  | 3                                      |

| C3INA    | 23            | 26                       | 15  | I                       | Analog     | Comparator 3 Positive Input            |

| C3INB    | 22            | 25                       | 14  | I                       | Analog     | Comparator 3 Selectable Negative Input |

| C3INC    | 27            | 2                        | 19  | ı                       | Analog     |                                        |

| C3IND    | 1             | 4                        | 21  | I                       | Analog     |                                        |

| C3OUT    | PPS           | PPS                      | PPS | 0                       |            | Comparator 3 Output                    |

**Legend:** CMOS = CMOS compatible input or output

TTL = TTL input buffer

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = OutputPPS = Peripheral Pin Select P = Power I=Input --=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interrupt Source <sup>(1)</sup>     | IRQ | Vector |              | Persistent    |             |              |           |

|-------------------------------------|-----|--------|--------------|---------------|-------------|--------------|-----------|

| interrupt Source(*)                 | #   | #      | Flag         | Enable        | Priority    | Sub-priority | Interrupt |

|                                     |     | Highes | st Natural C | rder Priority | ,           |              | •         |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>       | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>       | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>       | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>       | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>       | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E - Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>       | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>       | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>       | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>       | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>       | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E - Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>      | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>      | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>      | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>      | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>      | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E - Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>      | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>      | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>      | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>      | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>      | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>      | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>      | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>      | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>      | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>      | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E - Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>      | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>      | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>      | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>      | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>      | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>      | IPC6<12:10> | IPC6<9:8>    | No        |

| FCE - Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>      | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>       | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>       | IPC7<4:2>   | IPC7<1:0>    | No        |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>       | IPC7<12:10> | IPC7<9:8>    | No        |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>       | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1E - SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1TX - SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

#### REGISTER 11-1: U10TGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | _                 | -                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | -                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | _                | VBUSVDIF         |

**Legend:** WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIF: ID State Change Indicator bit

1 = A change in the ID state was detected0 = No change in the ID state was detected

bit 6 T1MSECIF: 1 Millisecond Timer bit

1 = 1 millisecond timer has expired0 = 1 millisecond timer has not expired

bit 5 LSTATEIF: Line State Stable Indicator bit

1 = USB line state has been stable for 1 ms, but different from last time

0 = USB line state has not been stable for 1 ms

bit 4 ACTVIF: Bus Activity Indicator bit

1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

0 = Activity has not been detected

bit 3 **SESVDIF:** Session Valid Change Indicator bit

1 = VBUS voltage has dropped below the session end level

0 = VBUS voltage has not dropped below the session end level

bit 2 SESENDIF: B-Device VBUS Change Indicator bit

1 = A change on the session end input was detected

0 = No change on the session end input was detected

bit 1 Unimplemented: Read as '0'

bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

1 = A change on the session valid input was detected

0 = No change on the session valid input was detected

**TABLE 12-4: PORTB REGISTER MAP**

| ess                         |                  |           |               |               |                              |                              |                              |                              |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|------------------------------|------------------------------|------------------------------|------------------------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13                        | 28/12                        | 27/11                        | 26/10                        | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

| 6100                        | ANSELB           | 31:16     | _             | _             | _                            | _                            | _                            | _                            | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 0100                        | ANOLLD           | 15:0      | ANSB15        | ANSB14        | ANSB13 <sup>(3)</sup>        | ANSB12 <sup>(2)</sup>        | _                            | _                            | _            | _            | _            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | _             | -             | _                            | _                            | _                            | _                            | _            | _            | -            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 00                          |                  | 15:0      | TRISB15       | TRISB14       | TRISB13 <sup>(3)</sup>       | TRISB12 <sup>(2)</sup>       | TRISB11 <sup>(2)</sup>       | TRISB10 <sup>(2)</sup>       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | <u> </u>                     |                              | <u> </u>                     | <u> </u>                     | _            | _            | _            |                             | _            |              |              |              |              |              | 0000       |

|                             |                  | 15:0      | RB15          | RB14          | RB13 <sup>(3)</sup>          | RB12 <sup>(2)</sup>          | RB11 <sup>(2)</sup>          | RB10 <sup>(2)</sup>          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | XXXX       |

| 6130                        | LATB             | 31:16     | _             | _             | — (a)                        |                              |                              |                              | _            | _            | _            |                             | _            |              | _            | _            | _            | _            | 0000       |

|                             |                  | 15:0      | LATB15        | LATB14        | LATB13 <sup>(3)</sup>        | LATB12 <sup>(2)</sup>        | LATB11 <sup>(2)</sup>        | LATB10 <sup>(2)</sup>        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | XXXX       |

| 6140                        | ODCB             | 31:16     | _             | _             | — (a)                        |                              |                              |                              | _            | _            | _            | _                           | _            |              | _            | _            | _            | _            | 0000       |

| 0.10                        |                  | 15:0      | ODCB15        | ODCB14        | ODCB13 <sup>(3)</sup>        | ODCB12 <sup>(2)</sup>        | ODCB11 <sup>(2)</sup>        | ODCB10 <sup>(2)</sup>        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        | CNPUB            | 31:16     | _             | _             | — (a)                        |                              |                              |                              | _            | _            | _            |                             | _            |              | _            | _            | _            | _            | 0000       |

| 0.00                        |                  |           | CNPUB15       | CNPUB14       | CNPUB13(3)                   | CNPUB12 <sup>(2)</sup>       | CNPUB11(2)                   | CNPUB10(2)                   | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       |            |

| 6160                        | CNPDB            | 31:16     | _             | _             | _                            |                              |                              |                              | _            | _            | _            |                             | _            |              | _            | _            | _            | _            | 0000       |

| 0.00                        |                  |           | CNPDB15       | CNPDB14       | CNPDB13                      | CNPDB12 <sup>(2)</sup>       | CNPDB11(2)                   | CNPDB10(2)                   | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       |            |

| 6170                        | CNCONB           | 31:16     | _             | _             | _                            |                              | _                            | _                            | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

|                             |                  | 15:0      | ON            | _             | SIDL                         |                              | _                            | _                            | _            | _            | _            | _                           | _            | _            | _            | _            | _            | _            | 0000       |

| 6180                        | CNENB            | 31:16     |               | _             | — (2)                        | — (2)                        | — (2)                        | — (2)                        |              | _            |              | — (2)                       |              |              |              | _            |              |              | 0000       |

|                             |                  | 15:0      | CNIEB15       | CNIEB14       | CNIEB13 <sup>(3)</sup>       | CNIEB11 <sup>(2)</sup>       | CNIEB11 <sup>(2)</sup>       | CNIEB10 <sup>(2)</sup>       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6 <sup>(2)</sup>       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       |              | 0000       |

|                             |                  | 31:16     | _             |               | _                            | _                            | _                            | _                            |              | _            | _            | _                           |              |              |              | _            | _            |              | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 <sup>(3)</sup> | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 <sup>(2)</sup> | CN<br>STATB10 <sup>(2)</sup> | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

- 2: This bit is not available on USB devices.

- 3: This bit is not available on VBAT devices.

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | -                 | _                | -                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 |                   |                   | -                 | -                 | _                | -                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | TECS             | S<1:0>           |

| 7:0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7.0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 TWDIS: Asynchronous Timer Write Disable bit

1 = Writes to Timer1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to the Timer1 register in progress

0 = Asynchronous write to Timer1 register is complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10 Unimplemented: Read as '0'

bit 9-8 TECS<1:0>: Timer1 External Clock Selection bits

11 = Reserved

10 = External clock comes from the LPRC

01 = External clock comes from the T1CK pin

00 = External clock comes from the Sosc

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit

When TCS = 1:

This bit is ignored.

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**NOTES:**

**NOTES:**

### 21.1 UART Control Registers

### TABLE 21-1: UART1 AND UART2 REGISTER MAP

| ess                         |                       |           |        |        |        |       |        |       |       | Ві         | its         |         |       |          |          |       |        |        | "          |

|-----------------------------|-----------------------|-----------|--------|--------|--------|-------|--------|-------|-------|------------|-------------|---------|-------|----------|----------|-------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8       | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0   | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16 — — |        |        |        | 1     | _      | _     |       | _          | SLPEN       | ACTIVE  |       | 1        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

| 0000                        | OTWODE                | 15:0      | ON     | -      | SIDL   | IREN  | RTSMD  | _     | UEN-  | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     |        |        |        | MASK  | <7:0>  |       |       |            |             |         |       | ADDR     | ?<7:0>   |       |        |        | 0000       |

| 0010                        | UISIA                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

| 6020                        | U1TXREG               | 31:16     | _      | _      | _      | -     | _      | _     | 1     | _          | _           | _       | _     | 1        | _        | _     | _      | _      | 0000       |

| 0020                        | OTTAINEO              | 15:0      | _      | 1      | 1      | 1     | _      | _     | 1     | TX8        |             |         |       | Transmit | Register |       |        |        | 0000       |

| 6030                        | U1RXREG               | 31:16     |        | _      | _      | -     | _      | _     | 1     | _          | _           | _       | _     | 1        | _        | _     | _      | _      | 0000       |

| 0030                        | OTIVALLO              | 15:0      | _      | -      | -      | 1     | _      | _     | I     | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | _      | 1      | 1      | 1     | _      | _     | 1     | 1          | _           | _       | 1     | 1        | _        | _     | _      | _      | 0000       |

| 0040                        | OTDINO                | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gen | erator Pres | caler   |       |          |          |       |        |        | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | _     | -      | _     | _     | _          | SLPEN       | ACTIVE  | _     | _        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

| 0200                        | UZIVIODE. 1           | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | -     | UEN-  | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     |        |        |        | MASK  | <7:0>  |       |       |            |             |         |       | ADDR     | ?<7:0>   |       |        |        | 0000       |

| 0210                        | 0231A                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

| 6220                        | U2TXREG               | 31:16     | _      | _      | _      | 1     | _      | -     | _     | _          | _           | _       | _     | _        | _        | _     | _      | _      | 0000       |

| 0220                        | UZIAREG               | 15:0      | _      | _      |        | -     | _      | -     | _     | TX8        |             |         |       | Transmit | Register |       |        |        | 0000       |

| 6230                        | U2RXREG               | 31:16     | _      | 1      |        | 1     | _      |       | I     | -          | _           | _       |       | 1        | _        | _     | _      | _      | 0000       |

| 0230                        | UZKAKLG               | 15:0      | _      | -      | 1      | 1     | _      |       | 1     | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | _      | _      | _      |       | _      | _     | _     | _          | _           | _       | _     |          | _        | _     | _      | _      | 0000       |

| 0240                        | OZDRG"                | 15:0      | •      |        |        | •     |        |       | Bau   | d Rate Gen | erator Pres | caler   |       |          |          |       | •      |        | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

**NOTES:**

### REGISTER 22-7: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   |                   | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | _                 | RCS1              | _                 | _                 | _                 | RADDR<10:8>       |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | RADDR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 14 RCS1: Chip Select 1 bit

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive (RADDR14 function is selected)

bit 13-11 **Unimplemented:** Read as '0' bit 10-0 **RADDR<13:0>:** Address bits

**Note:** This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

### REGISTER 24-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |

|              | _                        | _                 | _                 | _                        | _                 | _                 | _                | _                |  |

| 23:16        | U-0                      | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |

|              | _                        | _                 | _                 | _                        | _                 | _                 | _                | _                |  |

| 15:8         | R/W-0                    | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | ADRC                     | _                 | _                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |

| 7:0          | R/W-0                    | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |

|              | ADCS<7:0> <sup>(2)</sup> |                   |                   |                          |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ADRC: ADC Conversion Clock Source bit

1 = Clock derived from FRC

0 = Clock derived from Peripheral Bus Clock (PBCLK)

bit 14-13 Unimplemented: Read as '0'

bit 12-8 **SAMC<4:0>:** Auto-Sample Time bits<sup>(1)</sup>

11111 = **31** TAD

•

•

00001 = 1 TAD

00000 = 0 TAD (Not allowed)

bit 7-0 ADCS<7:0>: ADC Conversion Clock Select bits<sup>(2)</sup>

11111111 = TPB • 2 • (ADCS<7:0> + 1) = 512 • TPB = TAD

•

•

•

00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

**Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

2: This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

### 29.0 POWER-SAVING FEATURES

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130), which is available from the Documentation > Reference Manual section of the PIC32 Microchip web site (www.microchip.com/pic32).

This section describes power-saving features for the PIC32MX1XX/2XX 28/44-pin XLP Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 29.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

### 29.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

### 29.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

### 29.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- · The CPU is halted

- The system clock source is typically shutdown.

See 29.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

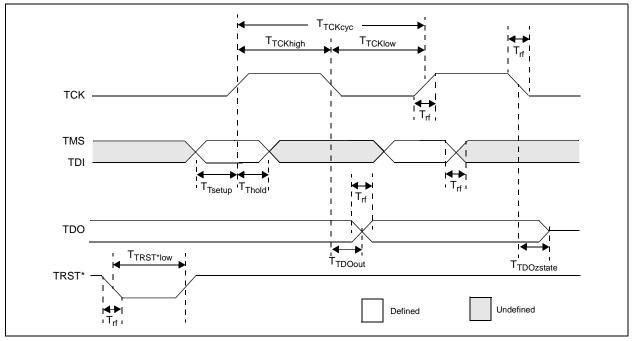

FIGURE 33-23: EJTAG TIMING CHARACTERISTICS

**TABLE 33-43: EJTAG TIMING REQUIREMENTS**

| AC CHARACTERISTICS |            |                                                  | (unless         | s otherw | ating Co<br>rise state<br>erature | ,          |  |

|--------------------|------------|--------------------------------------------------|-----------------|----------|-----------------------------------|------------|--|

| Param.<br>No.      | Symbol     | Description <sup>(1)</sup>                       | Min. Max. Units |          | Units                             | Conditions |  |

| EJ1                | Ттсксүс    | TCK Cycle Time                                   | 25              | _        | ns                                | _          |  |

| EJ2                | Ттскнідн   | TCK High Time                                    | 10              | _        | ns                                | _          |  |

| EJ3                | TTCKLOW    | TCK Low Time                                     | 10              | _        | ns                                | _          |  |

| EJ4                | TTSETUP    | TAP Signals Setup Time Before Rising TCK         | 5               | _        | ns                                | _          |  |

| EJ5                | TTHOLD     | TAP Signals Hold Time After Rising TCK           | 3               | _        | ns                                | _          |  |

| EJ6                | TTDOOUT    | TDO Output Delay Time from Falling TCK           | _               | 5        | ns                                | _          |  |

| EJ7                | TTDOZSTATE | TDO 3-State Delay Time from Falling TCK          | _               | 5        | ns                                | _          |  |

| EJ8                | TTRSTLOW   | TRST Low Time                                    | 25              | _        | ns                                | _          |  |

| EJ9                | TRF        | TAP Signals Rise/Fall Time, All Input and Output | _               | _        | ns                                | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

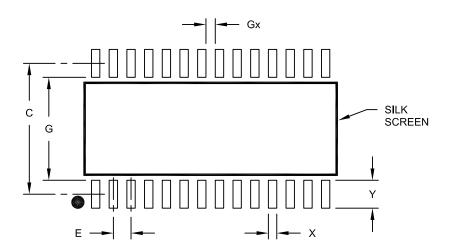

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch E          |             | 1.27 BSC |      |      |

| Contact Pad Spacing      | C           |          | 9.40 |      |

| Contact Pad Width (X28)  | Х           |          |      | 0.60 |

| Contact Pad Length (X28) | Υ           |          |      | 2.00 |

| Distance Between Pads    | Gx          | 0.67     |      |      |

| Distance Between Pads    | G           | 7.40     |      | ·    |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

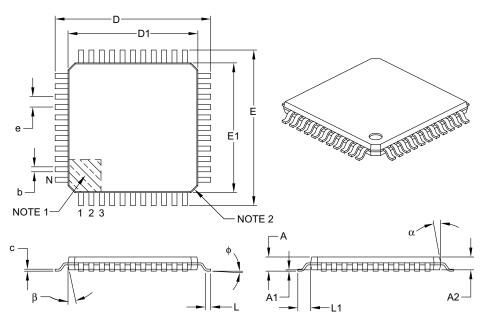

### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |

|--------------------------|-------------|-----------|------|------|--|

| Dimension Limits         |             | MIN       | NOM  | MAX  |  |

| Number of Leads          | N           |           | 44   |      |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |

| Overall Height           | А           | _         | _    | 1.20 |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |

| Standoff                 | A1          | 0.05      | _    | 0.15 |  |

| Foot Length              | L           | 0.45      | 0.60 | 0.75 |  |

| Footprint L1 1.00        |             | 1.00 REF  |      |      |  |

| Foot Angle               | ф           | 0°        | 3.5° | 7°   |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |

| Lead Thickness           | С           | 0.09      | _    | 0.20 |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |

| Mold Draft Angle Top     | α           | 11°       | 12°  | 13°  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°  | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

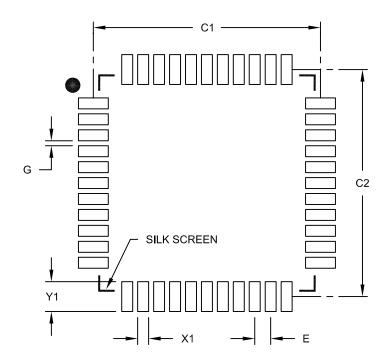

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |  |

|--------------------------|-------------|----------|-------|------|--|

| Dimension Limits         |             | MIN      | NOM   | MAX  |  |

| Contact Pitch            | Е           | 0.80 BSC |       |      |  |

| Contact Pad Spacing      | C1          |          | 11.40 |      |  |

| Contact Pad Spacing      | C2          |          | 11.40 |      |  |

| Contact Pad Width (X44)  | X1          |          |       | 0.55 |  |

| Contact Pad Length (X44) | Y1          |          |       | 1.50 |  |

| Distance Between Pads    | G           | 0.25     |       |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

**NOTES:**

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support