Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 72MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx154f128dt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This document contains device-specific information for PIC32MX1XX/2XX 28/44-pin XLP Family devices.

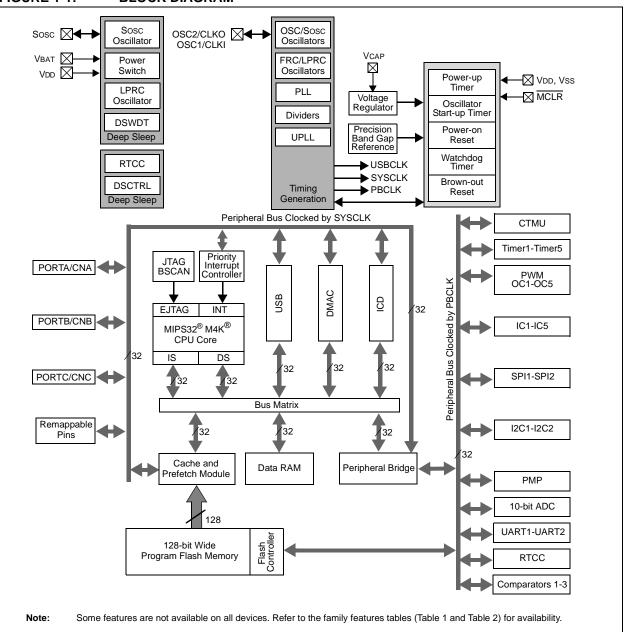

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/44-pin XLP Family of devices.

Table 1-1 through Table 1-16 list the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1: BLOCK DIAGRAM

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 External Oscillator Pins

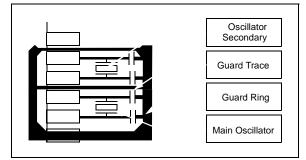

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: S

### : SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

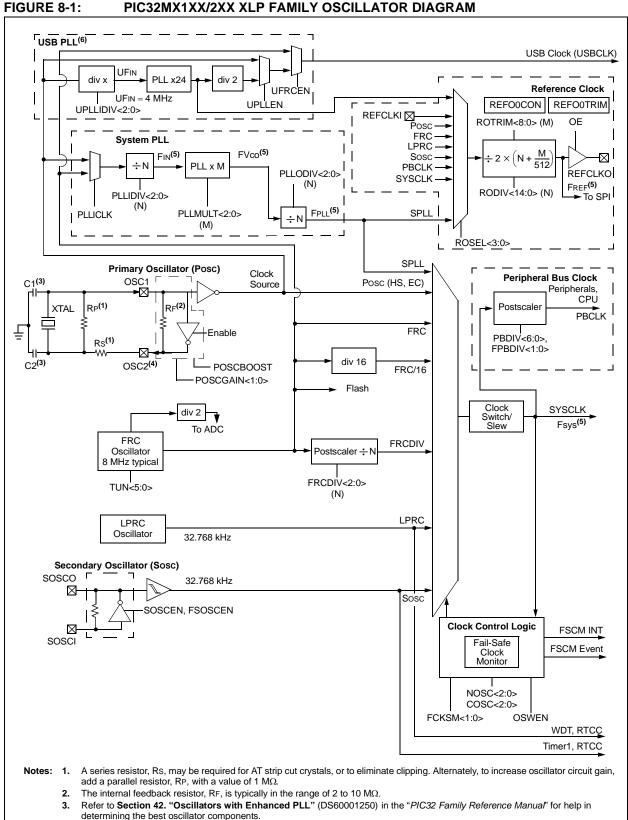

### PIC32MX1XX/2XX XLP FAMILY OSCILLATOR DIAGRAM

PB0CLK divided by 2 is available on the OSC2 pin in certain clock modes. 4.

- 5. Refer to Table 33-19 in 33.0 "Electrical Characteristics" for frequency limitations.

- 6. The USB PLL is only available on PIC32MX2XX XLP devices.

**Advance Information**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | —                 | -                 | _                 | _                 | -                | —                |  |  |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | _                | VBUSVDIF         |  |  |

## REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable             | e bit              |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •        |          |                               |       |                   |                       |                                                  |

|--------------|-------------------|----------|----------|-------------------------------|-------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 |          |          | Bit Bit 28/20/12/4 27/19/11/3 |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0               | U-0      | U-0      | U-0                           | U-0   | U-0               | U-0                   | U-0                                              |

| 31.24        |                   | —        | —        |                               | —     | _                 | _                     | —                                                |

| 23:16        | U-0               | U-0      | U-0      | U-0                           | U-0   | U-0               | U-0                   | U-0                                              |

| 23.10        |                   | —        | —        | _                             | —     | _                 | _                     | —                                                |

| 15:8         | U-0               | U-0      | U-0      | U-0                           | U-0   | U-0               | U-0                   | U-0                                              |

| 15.6         |                   | —        | —        | _                             | —     | _                 | _                     | —                                                |

|              | R/W-0             | R/W-0    | R/W-0    | R/W-0                         | R/W-0 | R/W-0             | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE | RESUMEIE | IDLEIE                        | TRNIE | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

| hake Interrupt Enable bit |

|---------------------------|

| nabled                    |

|                           |

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 =ATTACH interrupt is enabled

- 0 = ATTACH interrupt is disabled

- bit 5 RESUMEIE: RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

### REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| REGIST    | ER 19-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                                                                     |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                                                                                                                                                                 |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                                                                                                                                                                       |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                                                                                                                                                                  |

|           | 1 = Enhanced Buffer mode is enabled                                                                                                                                                                                                                |

|           | 0 = Enhanced Buffer mode is disabled                                                                                                                                                                                                               |

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                                                                    |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                                                                      |

|           | 0 = SPI Peripheral is disabled                                                                                                                                                                                                                     |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                         |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                                                                                        |

|           | 1 = Discontinue module operation when the device enters Idle mode                                                                                                                                                                                  |

|           | 0 = Continue module operation when the device enters Idle mode                                                                                                                                                                                     |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                                                                                |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                                                                                                                                                              |

| hit 11 10 | 0 = SDOx pin is controlled by the module                                                                                                                                                                                                           |

| bit 11-10 | <b>MODE&lt;32,16&gt;:</b> 32/16-Bit Communication Select bits<br>When AUDEN = 1:                                                                                                                                                                   |

|           | $\frac{\text{MODENCE}}{\text{MODE32}}  \text{MODE16} \qquad \text{Communication}$                                                                                                                                                                  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                                                                          |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                                                                          |

|           | 0 1 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                                                                          |

|           | 0 0 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                                                                                                                          |

|           | When AUDEN = 0:                                                                                                                                                                                                                                    |

|           | MODE32 MODE16 Communication                                                                                                                                                                                                                        |

|           | $1 \times 32$ -bit                                                                                                                                                                                                                                 |

|           | 0 1 <b>16-bit</b>                                                                                                                                                                                                                                  |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                                                                   |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                                                                               |

|           | Master mode (MSTEN = 1):                                                                                                                                                                                                                           |

|           | 1 = Input data sampled at end of data output time                                                                                                                                                                                                  |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                                                                               |

|           | <u>Slave mode (MSTEN = 0):</u><br>SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = $0$ .                                                                                                                          |

|           |                                                                                                                                                                                                                                                    |

| 1 1 6     | To write a '1' to this bit, the MSTEN value = 1 must first be written.                                                                                                                                                                             |

| bit 8     | <b>CKE:</b> SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                                                               |

|           | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)</li> </ul> |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                         |

|           | 1 = SSx pin used for Slave mode                                                                                                                                                                                                                    |

|           | 0 = SSx pin not used for Slave mode, pin controlled by port function.                                                                                                                                                                              |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit <sup>(4)</sup>                                                                                                                                                                                               |

| bit 0     | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                                                                              |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                                                                              |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in                                                                                                                                            |

|           | the SYSCLK cycle immediately following the instruction that clears the module's ON bit.                                                                                                                                                            |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                                                                               |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                                                                            |

|           | mode (FRMEN = 1).                                                                                                                                                                                                                                  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                                                                                         |

|           | of CKP.                                                                                                                                                                                                                                            |

|           |                                                                                                                                                                                                                                                    |

#### REGISTER 21-1: **UxMODE: UARTx MODE REGISTER (CONTINUED) IREN:** IrDA<sup>®</sup> Encoder and Decoder Enable bit bit 12 1 = IrDA is enabled 0 = IrDA is disabled bit 11 RTSMD: Mode Selection for UxRTS Pin bit $1 = \overline{\text{UxRTS}}$ pin is in Simplex mode $0 = \overline{\text{UxRTS}}$ pin is in Flow Control mode bit 10 Unimplemented: Read as '0' UEN<1:0>: UARTx Module Enable bits<sup>(1)</sup> bit 9-8 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register 10 = UxTX, UxRX, $\overline{\text{UxCTS}}$ and $\overline{\text{UxRTS}}$ pins are enabled and used 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit 1 = Wake-up enabled 0 = Wake-up disabled LPBACK: UARTx Loopback Mode Select bit bit 6 1 = Loopback mode is enabled 0 = Loopback mode is disabled bit 5 ABAUD: Auto-Baud Enable bit 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion 0 = Baud rate measurement disabled or completed **RXINV:** Receive Polarity Inversion bit bit 4 1 = UxRX Idle state is '0' 0 = UxRX Idle state is '1' bit 3 BRGH: High Baud Rate Enable bit 1 = High-Speed mode – 4x baud clock enabled 0 = Standard Speed mode - 16x baud clock enabled PDSEL<1:0>: Parity and Data Selection bits bit 2-1 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity bit 0 STSEL: Stop Selection bit 1 = 2 Stop bits 0 = 1 Stop bit

Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see 12.3 "Peripheral Pin Select" for more information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 |                   | —                 | _                 | _                 | -                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | _                |  |  |  |

| 45-0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | —                 | WCS1              | —                 | _                 | _                 | V                 | VADDR<10:8       | >                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | WADDR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### PMWADDR: PARALLEL PORT WRITE ADDRESS REGISTER **REGISTER 22-6:**

| R = Readable bit |  |

|------------------|--|

|------------------|--|

Legend:

W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-15 Unimplemented: Read as '0'

bit 14 WCS1: Chip Select 1 bit

1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14-11 Unimplemented: Read as '0'

- bit 10-0 WADDR<10:0>: Address bits

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

# 23.1 RTCC Control Registers

# TABLE 23-1: RTCC REGISTER MAP

| ess                         |                                                             |           | Bits   |       |          |          |       |                   |          |        |           |          |           |          |         |         |            |       |            |

|-----------------------------|-------------------------------------------------------------|-----------|--------|-------|----------|----------|-------|-------------------|----------|--------|-----------|----------|-----------|----------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Virtual Addr<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11 | 26/10             | 25/9     | 24/8   | 23/7      | 22/6     | 21/5      | 20/4     | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                                                      | 31:16     | —      | _     | —        | —        | _     | _                 |          |        |           |          | CAL       | <9:0>    |         |         |            |       | 0000       |

| 0200                        | RICCON                                                      | 15:0      | ON     | -     | SIDL     | —        | _     | RTCCLK            | SEL<1:0> | RTCOUT | SEL<1:0>  | RTCCLKON | —         | -        | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | RTCALRM                                                     | 31:16     | —      | -     | _        | —        | _     | —                 | —        | —      | —         | —        | —         | -        | —       | _       | —          | —     | 0000       |

| 0210                        | RICALKI                                                     | 15:0      | ALRMEN | CHIME | PIV      | ALRMSYNC |       | AMAS              | <<3:0>   |        | ARPT<7:0> |          |           |          | 0000    |         |            |       |            |

| 0220                        | RTCTIME                                                     | 31:16     | _      | -     | HR1      | 0<1:0>   |       | HR01              | <3:0>    |        | _         | М        | IN10<2:0> | <b>`</b> |         | MIN01   | <3:0>      |       | xxxx       |

| 0220                        | RICHINE                                                     | 15:0      | _      |       | SEC10<2: | 0>       |       | SEC0              | 1<3:0>   |        | _         | —        | _         | _        | _       | -       | _          | —     | xx00       |

| 0000                        | RTCDATE                                                     | 31:16     |        | YEAR  | 10<3:0>  |          |       | YEARC             | 1<3:0>   |        | —         | _        | —         | MONTH10  | )       | MONTH   | 01<3:0>    |       | xxxx       |

| 0230                        | RICDAIE                                                     | 15:0      | _      | _     | DAY      | 10<1:0>  |       | DAY0 <sup>-</sup> | <3:0>    |        | —         | —        | _         | —        | —       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                                                    | 31:16     | —      | _     | HR1      | 0<1:0>   |       | HR01<3:0>         |          |        |           | M        | IN10<2:0> | •        |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                                             | 15:0      | —      |       | SEC10<2: | 0>       |       | SEC0              | 1<3:0>   |        | —         | _        | —         | —        | —       | —       |            | _     | xx00       |

| 0050                        | ALRMDATE                                                    | 31:16     | —      |       | _        | —        | _     | _                 | —        | _      | _         | _        | _         | MONTH10  | )       | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        |                                                             | 15:0      |        | DAY1  | 0<3:0>   | •        |       | DAY0              | <3:0>    |        | —         | —        | _         | —        | —       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | -                 | -                 | —                 | _                 | -                | —                |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | -                 | -                 |                   | _                 | _                 |                   |                  | -                |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 10.0         | —                 | —                 | SIDL              |                   | _                 | —                 |                  | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7.0          |                   | _                 |                   |                   |                   | C3OUT             | C2OUT            | C1OUT            |  |

### REGISTER 25-2: CMSTAT: COMPARATOR STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-14 Unimplemented: Read as '0'

### bit 13 **SIDL:** Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

### bit 12-3 Unimplemented: Read as '0'

### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

### bit 0 **C1OUT:** Comparator Output bit

- 1 =Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

### 29.5 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 29-2 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |  |

|------------------------------|------------------------------|--------------------------------|--|

| ADC1                         | AD1MD                        | PMD1<0>                        |  |

| CTMU                         | CTMUMD                       | PMD1<8>                        |  |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |  |

| Low-Voltage Detect           | HLVDMD                       | PMD1<20>                       |  |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |  |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |  |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |  |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |  |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |  |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |  |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |  |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |  |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |  |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |  |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |  |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |  |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |  |

| Timer1                       | T1MD                         | PMD4<0>                        |  |

| Timer2                       | T2MD                         | PMD4<1>                        |  |

| Timer3                       | T3MD                         | PMD4<2>                        |  |

| Timer4                       | T4MD                         | PMD4<3>                        |  |

| Timer5                       | T5MD                         | PMD4<4>                        |  |

| UART1                        | U1MD                         | PMD5<0>                        |  |

| UART2                        | U2MD                         | PMD5<1>                        |  |

| SPI1                         | SPI1MD                       | PMD5<8>                        |  |

| SPI2                         | SPI2MD                       | PMD5<9>                        |  |

| I2C1                         | I2C1MD                       | PMD5<16>                       |  |

| 12C2                         | I2C2MD                       | PMD5<17>                       |  |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |  |

| RTCC                         | RTCCMD                       | PMD6<0>                        |  |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |  |

| PMP                          | PMPMD                        | PMD6<16>                       |  |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

2: The module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

NOTES:

### **30.0 SPECIAL FEATURES**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. Section (DS60001124) and 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/44-pin XLP Family devices include the following features intended to maximize application flexibility, reliability and minimize cost through elimination of external components.

- Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

### **30.1** Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- CFGCON: Configuration Control Register

In addition, the DEVID register (Register 30-6) provides device and revision information.

#### REGISTER 30-1: **DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)**

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits<sup>(3)</sup>

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. 11111111 = Disabled 11111110 = 0xBD00\_0FFF 11111101 = 0xBD00\_1FFF 11111100 = 0xBD00\_2FFF 11111011 = 0xBD00\_3FFF 11111010 = 0xBD00\_4FFF 11111001 = 0xBD00\_5FFF 11111000 = 0xBD00\_6FFF 11110111 = 0xBD00\_7FFF 11110110 = 0xBD00\_8FFF 11110101 = 0xBD00\_9FFF 11110100 = 0xBD00\_AFFF 11110011 = 0xBD00\_BFFF 11110010 = 0xBD00\_CFFF 11110001 = 0xBD00\_DFFF 11110000 = 0xBD00\_EFFF 11101111 = 0xBD00\_FFFF 10111111 = 0xBD03 FFFF 10111110 = Reserved 00000000 = Reserved bit 11-5 Reserved: Write '1' ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits<sup>(2)</sup> bit 4-3 11 = PGEC1/PGED1 pair is used 10 = PGEC2/PGED2 pair is used 01 = PGEC3/PGED3 pair is used 00 = PGEC4/PGED4 pair is used<sup>(2)</sup> JTAGEN: JTAG Enable bit<sup>(1)</sup> 1 = JTAG is enabled 0 = JTAG is disabled bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled) 1x =Debugger is disabled 0x = Debugger is enabled Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

bit 2

| bit 23           | DSBOREN: Deep Sleep BOR Enable bit                                                                                                           |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 1 = Enable BOR during Deep Sleep mode                                                                                                        |

|                  | 0 = Disable BOR during Deep Sleep mode                                                                                                       |

| bit 22           | Reserved: Write '1'                                                                                                                          |

| bit 21           | VBATBOREN: VBAT BOR Enable bit                                                                                                               |

|                  | 1 = Enable BOR during VBAT mode                                                                                                              |

|                  | 0 = Disable BOR during VBAT mode                                                                                                             |

| bit 20           | BOREN: Brown-Out Reset (BOR) Enable bit                                                                                                      |

|                  | 1 = Enable BOR                                                                                                                               |

|                  | 0 = Disable BOR                                                                                                                              |

| bit 19           | Reserved: Write '1'                                                                                                                          |

| bit 18-16        | FPLLODIV<2:0>: Default PLL Output Divisor bits                                                                                               |

|                  | 111 = PLL output divided by 256                                                                                                              |

|                  | 110 = PLL output divided by 64                                                                                                               |

|                  | 101 = PLL output divided by 32                                                                                                               |

|                  | 100 = PLL output divided by 16                                                                                                               |

|                  | 011 = PLL output divided by 8                                                                                                                |

|                  | 010 = PLL output divided by 4<br>001 = PLL output divided by 2                                                                               |

|                  | 000 = PLL output divided by 1                                                                                                                |

| bit 15           | UPLLEN: USB PLL Enable bit <sup>(1)</sup>                                                                                                    |

| DIC 15           | 1 = Disable and bypass USB PLL                                                                                                               |

|                  | 0 = Enable USB PLL                                                                                                                           |

| bit 14-11        | Reserved: Write '1'                                                                                                                          |

|                  | UPLLIDIV<2:0>: USB PLL Input Divider bits <sup>(1)</sup>                                                                                     |

| DIL 10-0         | 111 = 12x divider                                                                                                                            |

|                  | 110 = 10x  divider                                                                                                                           |

|                  | 101 = 6x  divider                                                                                                                            |

|                  | 100 = 5x  divider                                                                                                                            |

|                  | 011 = 4x divider                                                                                                                             |

|                  | 010 = 3x  divider                                                                                                                            |

|                  | 010 = 3x divider                                                                                                                             |

|                  | 001 = 2x  divider                                                                                                                            |

|                  | 000 = 1x divider                                                                                                                             |

| bit 7            | FPLLICLK: System PLL Input Clock Select bit                                                                                                  |

|                  | 1 = FRC is selected as input to the System PLL                                                                                               |

|                  | 0 = POSC is selected as input to the System PLL                                                                                              |

|                  | FPLLMUL<2:0>: PLL Multiplier bits                                                                                                            |

| bit 6-4          |                                                                                                                                              |

| bit 6-4          | 111 = 24x multiplier                                                                                                                         |

| bit 6-4          | 110 = 21x multiplier                                                                                                                         |

| bit 6-4          | 110 = 21x multiplier<br>101 = 20x multiplier                                                                                                 |

| bit 6-4          | 110 = 21x multiplier<br>101 = 20x multiplier<br>100 = 19x multiplier                                                                         |

| bit 6-4          | 110 = 21x multiplier<br>101 = 20x multiplier<br>100 = 19x multiplier<br>011 = 18x multiplier                                                 |

| bit 6-4          | 110 = 21x multiplier<br>101 = 20x multiplier<br>100 = 19x multiplier<br>011 = 18x multiplier<br>010 = 17x multiplier                         |

| bit 6-4          | 110 = 21x multiplier<br>101 = 20x multiplier<br>100 = 19x multiplier<br>011 = 18x multiplier<br>010 = 17x multiplier<br>001 = 16x multiplier |

| bit 6-4<br>bit 3 | 110 = 21x multiplier<br>101 = 20x multiplier<br>100 = 19x multiplier<br>011 = 18x multiplier<br>010 = 17x multiplier                         |

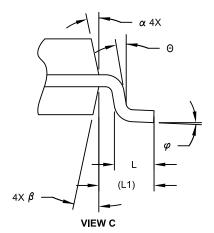

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |

|--------------------------|-------------|-----------|-----|------|

| Dimension Limits         |             | MIN       | NOM | MAX  |

| Number of Pins           | N           | 28        |     |      |

| Pitch                    | е           | 1.27 BSC  |     |      |

| Overall Height           | A           | -         | -   | 2.65 |

| Molded Package Thickness | A2          | 2.05      | -   | -    |

| Standoff §               | A1          | 0.10      | -   | 0.30 |

| Overall Width            | E           | 10.30 BSC |     |      |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |

| Overall Length           | D           | 17.90 BSC |     |      |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |

| Foot Length              | L           | 0.40      | -   | 1.27 |

| Footprint                | L1          | 1.40 REF  |     |      |

| Lead Angle               | Θ           | 0°        | -   | -    |

| Foot Angle               | φ           | 0°        | -   | 8°   |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |

| Lead Width               | b           | 0.31      | -   | 0.51 |

| Mold Draft Angle Top     | α           | 5°        | _   | 15°  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

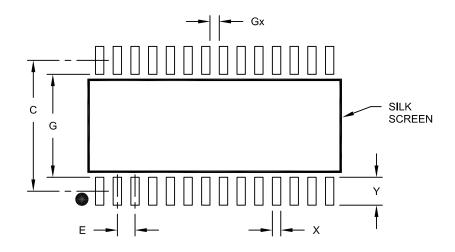

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units    | Units MILLIMETERS |      | S    |

|--------------------------|----------|-------------------|------|------|

| Dimensio                 | n Limits | MIN               | NOM  | MAX  |

| Contact Pitch            | E        | 1.27 BSC          |      |      |

| Contact Pad Spacing      | С        |                   | 9.40 |      |

| Contact Pad Width (X28)  | X        |                   |      | 0.60 |

| Contact Pad Length (X28) | Y        |                   |      | 2.00 |

| Distance Between Pads    | Gx       | 0.67              |      |      |

| Distance Between Pads    | G        | 7.40              |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

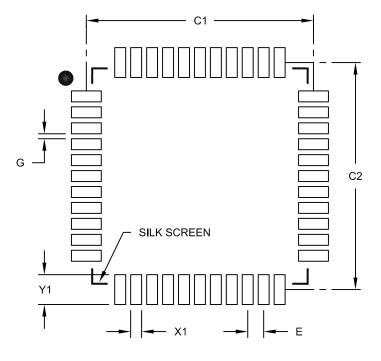

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units  | nits MILLIMETERS |          | S    |

|--------------------------|--------|------------------|----------|------|

| Dimension                | Limits | MIN              | NOM      | MAX  |

| Contact Pitch            | E      |                  | 0.80 BSC |      |

| Contact Pad Spacing      | C1     |                  | 11.40    |      |

| Contact Pad Spacing      | C2     |                  | 11.40    |      |

| Contact Pad Width (X44)  | X1     |                  |          | 0.55 |

| Contact Pad Length (X44) | Y1     |                  |          | 1.50 |

| Distance Between Pads    | G      | 0.25             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B