Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

⊡XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256b-i-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-4: | OC1 THROUGH OC5 PINOUT I/O DESCRIPTIONS |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

|          | Pi            | Pin Number <sup>(1)</sup> |                        |             |                |                                            |  |  |  |

|----------|---------------|---------------------------|------------------------|-------------|----------------|--------------------------------------------|--|--|--|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SOIC            | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                |  |  |  |

|          |               | are                       |                        |             |                |                                            |  |  |  |

| OC1      | PPS           | PPS                       | PPS                    | 0           |                | Output Compare Output 1-5                  |  |  |  |

| OC2      | PPS           | PPS                       | PPS                    | 0           | _              |                                            |  |  |  |

| OC3      | PPS           | PPS                       | PPS                    | 0           | _              |                                            |  |  |  |

| OC4      | PPS           | PPS                       | PPS                    | 0           | —              |                                            |  |  |  |

| OC5      | PPS           | PPS                       | PPS                    | 0           | —              |                                            |  |  |  |

| OCFA     | PPS           | PPS                       | PPS                    | I           | ST             | Output Compare Fault A Input               |  |  |  |

| OCFB     | PPS           | PPS                       | PPS                    | I           | ST             | Output Compare Fault B Input               |  |  |  |

| Legend:  | CMOS = CM     | IOS compa                 | atible input           | or outpu    | t              | Analog = Analog input P = Power            |  |  |  |

|          | ST = Schmi    | 00                        | put with CN            | NOS lev     | els            | O = Output I = Input                       |  |  |  |

|          | TTL = TTL i   | •                         |                        |             |                | $PPS = Peripheral Pin Select \qquad = N/A$ |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

## TABLE 1-5: EXTERNAL INTERRUPTS PINOUT I/O DESCRIPTIONS

|          | P                                                                                                        | in Number      | (1)                    |             |                |                                           |           |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------|----------------|------------------------|-------------|----------------|-------------------------------------------|-----------|--|--|--|

| Pin Name | 28-pin<br>QFN                                                                                            | 28-pin<br>SOIC | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                               |           |  |  |  |

|          | External Interrupts                                                                                      |                |                        |             |                |                                           |           |  |  |  |

| INT0     | 13                                                                                                       | 16             | 43                     | I           | ST             | External Interrupt 0-4                    |           |  |  |  |

| INT1     | PPS                                                                                                      | PPS            | PPS                    | I           | ST             |                                           |           |  |  |  |

| INT2     | PPS                                                                                                      | PPS            | PPS                    | I           | ST             |                                           |           |  |  |  |

| INT3     | PPS                                                                                                      | PPS            | PPS                    | I           | ST             |                                           |           |  |  |  |

| INT4     | PPS                                                                                                      | PPS            | PPS                    | I           | ST             | 1                                         |           |  |  |  |

| Legend:  | CMOS = C                                                                                                 | MOS compa      | atible input           | or outpu    | t              | Analog = Analog input                     | P = Power |  |  |  |

| -        | ST = Schmi                                                                                               | tt Trigger in  | put with CI            | MOS lev     | els            | O = Output I = Input                      |           |  |  |  |

|          | TTL = TTL i                                                                                              | nput buffer    |                        |             |                | $PPS = Peripheral Pin Select \qquad= N/A$ |           |  |  |  |

| Note 1:  | Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. |                |                        |             |                |                                           |           |  |  |  |

NOTES:

| Interrupt Source <sup>(1)</sup>       | IRQ | Vector |             | Interru       | pt Bit Location |              | Persistent |

|---------------------------------------|-----|--------|-------------|---------------|-----------------|--------------|------------|

| Interrupt Source                      | #   | #      | Flag        | Enable        | Priority        | Sub-priority | Interrupt  |

| U1E – UART1 Fault                     | 39  | 32     | IFS1<7>     | IEC1<7>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1RX – UART1 Receive Done             | 40  | 32     | IFS1<8>     | IEC1<8>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1TX – UART1 Transfer Done            | 41  | 32     | IFS1<9>     | IEC1<9>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| I2C1B – I2C1 Bus Collision Event      | 42  | 33     | IFS1<10>    | IEC1<10>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1S – I2C1 Slave Event              | 43  | 33     | IFS1<11>    | IEC1<11>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1M – I2C1 Master Event             | 44  | 33     | IFS1<12>    | IEC1<12>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNA – PORTA Input Change<br>Interrupt | 45  | 34     | IFS1<13>    | IEC1<13>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNB – PORTB Input Change<br>Interrupt | 46  | 34     | IFS1<14>    | IEC1<14>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNC – PORTC Input Change<br>Interrupt | 47  | 34     | IFS1<15>    | IEC1<15>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMP – Parallel Master Port            | 48  | 35     | IFS1<16>    | IEC1<16>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| PMPE – Parallel Master Port Error     | 49  | 35     | IFS1<17>    | IEC1<17>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2E – SPI2 Fault                    | 50  | 36     | IFS1<18>    | IEC1<18>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2RX – SPI2 Receive Done            | 51  | 36     | IFS1<19>    | IEC1<19>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2TX – SPI2 Transfer Done           | 52  | 36     | IFS1<20>    | IEC1<20>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2E – UART2 Error                     | 53  | 37     | IFS1<21>    | IEC1<21>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2RX – UART2 Receiver                 | 54  | 37     | IFS1<22>    | IEC1<22>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2TX – UART2 Transmitter              | 55  | 37     | IFS1<23>    | IEC1<23>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2B – I2C2 Bus Collision Event      | 56  | 38     | IFS1<24>    | IEC1<24>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2S – I2C2 Slave Event              | 57  | 38     | IFS1<25>    | IEC1<25>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2M – I2C2 Master Event             | 58  | 38     | IFS1<26>    | IEC1<26>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| CTMU – CTMU Event                     | 59  | 39     | IFS1<27>    | IEC1<27>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| DMA0 – DMA Channel 0                  | 60  | 40     | IFS1<28>    | IEC1<28>      | IPC10<4:2>      | IPC10<1:0>   | No         |

| DMA1 – DMA Channel 1                  | 61  | 41     | IFS1<29>    | IEC1<29>      | IPC10<12:10>    | IPC10<9:8>   | No         |

| DMA2 – DMA Channel 2                  | 62  | 42     | IFS1<30>    | IEC1<30>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA3 – DMA Channel 3                  | 63  | 43     | IFS1<31>    | IEC1<31>      | IPC10<28:26>    | IPC10<25:24> | No         |

|                                       |     | Lowes  | t Natural O | rder Priority |                 |              |            |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

## REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | CHDSA.            | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                                                       |                      |                    |  |

|-------------------|-------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit $U = Unimplemented bit, read as '0'$ |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                      | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address. **Note:** This must be the physical address of the destination.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| INE OIO I    | LK 11-5.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | -                 | —                 | —                      | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | —                      | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 | —                 | _                      |                   | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | —                 |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

## REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| Logona.           |                         |                      |                    |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | le bit W = Writable bit |                      | nd as '0'          |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

- (Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

- **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | _                       |                         |                   | _                    | _                 |                       |                         |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | _                       |                         |                   | _                    | _                 |                       |                         |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.0         | —                 | _                       |                         |                   | _                    | _                 |                       |                         |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | JIALLIF           |                         | INE SOMEIFY /           | IDLEIF            |                      | JULI              |                       | DETACHIF <sup>(6)</sup> |

|              |                   |                         |                         |                   |                      |                   |                       |                         |

## REGISTER 11-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit               |

|-------------------|-------------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set        | 0' = Bit is cleared $x = Bit is unknown$ |

## bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIF:</b> STALL Handshake Interrupt bit<br>1 = In Host mode a STALL handshake was received during the handshake phase of the transaction<br>In Device mode a STALL handshake was transmitted during the handshake phase of the transaction<br>0 = STALL handshake has not been sent                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup><br>1 = Peripheral attachment was detected by the USB module<br>0 = Peripheral attachment was not detected                                                                                                                                                                                                                                                                               |

| bit 5 | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup><br>1 = K-State is observed on the D+ or D- pin for 2.5 µs<br>0 = K-State is not observed                                                                                                                                                                                                                                                                                                    |

| bit 4 | IDLEIF: Idle Detect Interrupt bit<br>1 = Idle condition detected (constant Idle state of 3 ms or more)<br>0 = No Idle condition detected                                                                                                                                                                                                                                                                                                         |

| bit 3 | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup><br>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information<br>0 = Processing of current token not complete                                                                                                                                                                                                             |

| bit 2 | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host<br>0 = SOF token was not received nor threshold reached                                                                                                                                                                                                                                                               |

| bit 1 | UERRIF: USB Error Condition Interrupt bit <sup>(4)</sup><br>1 = Unmasked error condition has occurred<br>0 = Unmasked error condition has not occurred                                                                                                                                                                                                                                                                                           |

| bit 0 | <pre>URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup> 1 = Valid USB Reset has occurred 0 = No USB Reset has occurred DETACHIF: USB Detach Interrupt bit (Host mode)<sup>(6)</sup> 1 = Peripheral detachment was detected by the USB module 0 = Peripheral detachment was not detected</pre>                                                                                                                                           |

| 3     | <ol> <li>This bit is valid only if the HOSTEN bit is set (see Register 11-11), there is no activity on the USB for 2.5 µs, and the current bus state is not SE0.</li> <li>When not in Suspend mode, this interrupt should be disabled.</li> <li>Clearing this bit will cause the STAT FIFO to advance.</li> <li>Only error conditions enabled through the U1EIE register will set this bit.</li> <li>Device mode.</li> <li>Host mode.</li> </ol> |

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| REGIOI       |                   |                   |                      |                      |                   |                   |                        |                  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 31.24        |                   |                   |                      | _                    |                   | —                 | —                      | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 23.10        |                   |                   |                      |                      |                   | —                 | —                      |                  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |

| 15.6         |                   |                   |                      |                      |                   | —                 | —                      |                  |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |  |

|              | DIGLI             | DIVIALI           |                      | DIOLI                |                   | GIGTUEI           | EOFEF <sup>(3,5)</sup> |                  |  |  |  |

## REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit  |                  |  |  |  |

|-------------------|-------------------------|-----------------------------|------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read | as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared x =    | = Bit is unknown |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## TABLE 12-5: PORTC REGISTER MAP

| ess                         |                                   |           |       |       |       |       |       |       |          |          | Bits     |          |          |          |          |          |          |          |            |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8     | 23/7     | 22/6     | 21/5     | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     | _     |       | _     |       |       | -     | —        | _        | -        |          | -        | -        | —        | -        | —        | _        | 0000       |

| 0200                        | ANGLLO                            | 15:0      | —     | —     | —     | —     | _     |       |          | _        |          | —        | _        |          | ANSC3    | ANSC2    | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | —     | _     | —     | —     | _     | _     | —        | _        | —        |          | —        | —        | —        | —        | —        |          | 0000       |

| 0210                        | 11000                             | 15:0      | —     | —     | —     | —     | _     | _     | TRISC9   | TRISC8   | TRISC7   | TRISC6   | TRISC5   | TRISC4   | TRISC3   | TRISC2   | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | _     | —     | —        |          | _        | —        | -        |          |          |          |          |          | 0000       |

| 0220                        | 1 on 10                           | 15:0      | —     | —     | —     | —     | _     | _     | RC9      | RC8      | RC7      | RC6      | RC5      | RC4      | RC3      | RC2      | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 0200                        | 27.110                            | 15:0      | —     | _     | —     | —     | _     | —     | LATC9    | LATC8    | LATC7    | LATC6    | LATC5    | LATC4    | LATC3    | LATC2    | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 0240                        |                                   | 15:0      | —     | _     | —     | —     | _     | —     | ODCC9    | ODCC8    | ODCC7    | ODCC6    | ODCC5    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | ODCC0    | 0000       |

| 6250                        | CNPUC                             | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 0200                        |                                   | 15:0      | —     | _     | —     | —     | _     | —     | CNPUC9   | CNPUC8   | CNPUC7   | CNPUC6   | CNPUC5   | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | CNPUC0   | 0000       |

| 6260                        | CNPDC                             | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 0200                        |                                   | 15:0      | —     | _     | —     | —     | _     | —     | CNPDC9   | CNPDC8   | CNPDC7   | CNPDC6   | CNPDC5   | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | CNPDC0   | 0000       |

| 6270                        | CNCONC                            | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | _        | _        | —        | _        | —        | -        | 0000       |

| 0270                        |                                   | 15:0      | ON    | _     | SIDL  | —     | _     | —     | —        | -        | _        | —        | _        | _        | —        | _        | —        | -        | 0000       |

| 6280                        | CNENC                             | 31:16     | —     | _     | —     | —     | _     | —     | —        | -        | _        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 0200                        |                                   | 15:0      | —     | _     | —     | —     | —     | —     | CNIEC9   | CNIEC8   | CNIEC7   | CNIEC6   | CNIEC5   | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | CNIEC0   | 0000       |

| 6290                        | CNSTATC                           | 31:16     | —     | —     | —     | —     | _     | —     | —        |          | —        | —        | -        | _        | —        | -        | —        |          | 0000       |

| 5230                        | UNUIAIC                           | 15:0      | —     | —     | —     | —     | —     | —     | CNSTATC9 | CNSTATC8 | CNSTATC7 | CNSTATC6 | CNSTATC5 | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

## TABLE 12-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                       |               |       |       | ULLU   |       |       |       |      | Bi   |      |        |      |      |      |            |             |      |            |

|-----------------------------|-----------------------|---------------|-------|-------|--------|-------|-------|-------|------|------|------|--------|------|------|------|------------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13  | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2       | 17/1        | 16/0 | All Resets |

| FB48                        | RPB7R                 | 31:16<br>15:0 | _     | —     | —      |       |       | -     | -    | -    |      | —      | -    | -    | —    | —<br>RPB7  | —<br><3:0>  | —    | 0000       |

| FB4C                        | RPB8R                 | 31:16<br>15:0 | _     |       |        |       |       |       | _    |      | _    |        | _    | _    | _    | —<br>RPB8  | —<br><3:0>  | _    | 0000       |

| FB50                        | RPB9R                 | 31:16<br>15:0 | _     | _     |        | _     | _     |       | _    |      | _    |        | _    |      | —    | —<br>RPB9  | —<br><3:0>  | —    | 0000       |

| FB54                        | RPB10R                | 31:16<br>15:0 | _     | _     |        | _     | _     | _     | -    | -    | _    | _      | -    | -    | _    | —<br>RPB1  | —<br>0<3:0> | —    | 0000       |

| FB58                        | RPB11R                | 31:16<br>15:0 | _     | _     |        | _     | -     |       | -    |      | -    |        | -    |      | -    | —<br>RPB1  | _           | -    | 0000       |

| FB60                        | RPB13R <sup>(3)</sup> | 31:16<br>15:0 | -     |       | —      | -     |       | _     | _    | _    |      | _      | _    | _    | —    | —<br>RPB1  | —<br>3<3:0> | —    | 0000       |

| FB64                        | RPB14R                | 31:16<br>15:0 | _     |       |        |       |       |       |      |      |      |        |      |      | _    | —<br>RPB1- | —<br>4<3:0> | —    | 0000       |

| FB68                        | RPB15R                | 31:16<br>15:0 | _     |       |        | _     |       |       | _    | _    |      |        | _    | _    | _    | —<br>RPB1  | —           | _    | 0000       |

| FB6C                        | RPC0R <sup>(1)</sup>  | 31:16<br>15:0 | _     |       |        | _     |       |       | _    | _    |      |        | _    | _    | —    | —<br>RPC0  | —<br> <3:0> | _    | 0000       |

| FB70                        | RPC1R <sup>(1)</sup>  | 31:16<br>15:0 | _     |       |        | _     |       | _     | _    | _    | _    |        | _    | _    | _    | —<br>RPC1  | _           | _    | 0000       |

| FB74                        | RPC2R <sup>(1)</sup>  | 31:16<br>15:0 | _     | _     |        | _     | _     | _     | -    | -    | _    | _      | -    | -    | _    | —<br>RPC2  | _           | —    | 0000       |

| FB78                        | RPC3R <sup>(1)</sup>  | 31:16<br>15:0 | _     | —     | —      |       |       | _     | -    | _    |      | —      | -    | _    | —    | –<br>RPC3  | —<br><3:0>  | —    | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup>  | 31:16<br>15:0 | -     |       | _<br>_ | _     | _     | -     | -    | -    | _    | _<br>_ | -    | -    | -    | —<br>RPC4  | —<br>·<3:0> | —    | 0000       |

| FB80                        | RPC5R <sup>(1)</sup>  | 31:16<br>15:0 | _     | _     | _      | _     |       | -     | _    | _    | _    | _      | _    | _    | —    | —<br>RPC5  | —<br><3:0>  | —    | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This register is only available on 44-pin devices.

2: This register is only available on USB devices.

3: This register is only available on VBAT devices.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| REGIST       | REGISTER 19-2: SPIXCON2: SPI CONTROL REGISTER 2 |                   |                   |                   |                          |                   |                  |                         |  |  |  |

|--------------|-------------------------------------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                               | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |  |  |  |

| 31:24        | U-0                                             | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |  |  |  |

| 31.24        | —                                               | —                 | —                 | —                 | —                        | _                 |                  | _                       |  |  |  |

| 23:16        | U-0 U-0                                         |                   | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |  |  |  |

| 23.10        | —                                               | —                 | —                 | —                 | —                        | _                 |                  | —                       |  |  |  |

| 15:8         | R/W-0                                           | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |  |  |  |

| 15.0         | SPISGNEXT                                       | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |  |  |  |

| 7:0          | R/W-0                                           | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |  |  |  |

| 7.0          | AUDEN <sup>(1)</sup>                            | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |  |  |  |

|              |                                                 |                   |                   |                   |                          |                   |                  |                         |  |  |  |

#### ICTED 10 2

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data 0 = A ROV is a critical error that stops SPI operation

- bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

#### AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

#### AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2 S \mod e$

- **Note 1:** This bit can only be written when the ON bit = 0.

- This bit is only valid for AUDEN = 1. 2:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | MASK<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

## REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

## Legend:

| 5                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 MASK<7:0>: UARTx Address Match Mask bits

These bits are used to mask the ADDR<7:0> bits.

11111111 = Corresponding ADDRx bits are used to detect the address match

**Note:** This setting allows the user to assign individual address as well as a group broadcast address to a UART.

00000000 = Corresponding ADDRx bits are not used to detect the address match.

## bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADDEN bit is '1', this value defines the address character to use for automatic address detection.

## bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

## bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

## bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module

- **Note:** The event of disabling an enabled receiver will release the RX pin to the PORT function; however, the receive buffers *will not* be reset. Disabling the receiver has no effect on the receive status flags.

## bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                  | _                 | —                   | —                 | —                | _                |

| 00.40        | R/W-0, HC         | U-0               | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | RDSTART           | —                 | —                  | —                 | —                   | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <b>(2)</b>   | ALP <sup>(2)</sup> |                   | CS1P <sup>(2)</sup> | —                 | WRSP             | RDSP             |

## REGISTER 22-1: PMCON: PARALLEL PORT CONTROL REGISTER

## Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-14 Unimplemented: Read as '0'

bit 23 **RDSTART:** Start Read on PMP Bus bit

This bit is cleared by hardware at the end of the read cycle.

- 1 = Start a read cycle on the PMP bus

- 0 = No effect

- bit 22-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP enabled

- 0 = PMP disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

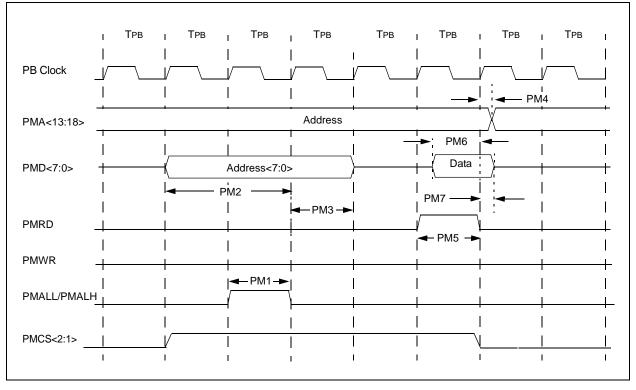

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<10:8> and PMA<14>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port enabled

- 0 = PMWR/PMENB port disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port enabled

- 0 = PMRD/PMWR port disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

## PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

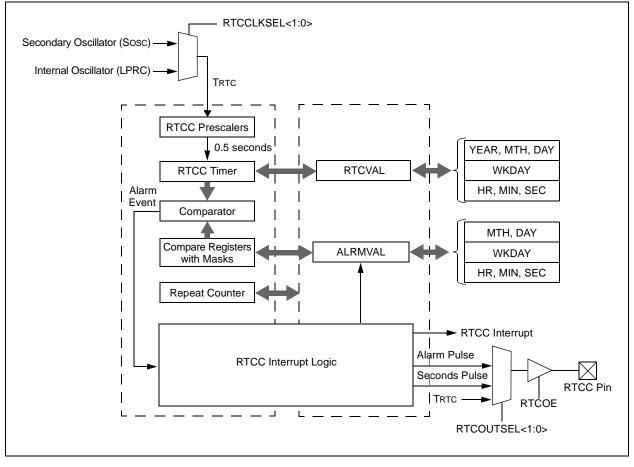

## FIGURE 23-1: RTCC BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | —                 | —                 | HR10              | <1:0>             |                   | HR01              | <3:0>            |                  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | —                 |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | —                 | —                 | —                 | —                 | _                 | _                 | —                | _                |  |

|              |                   | •                 | •                 | •                 | •                 |                   | •                | •                |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |

| R = Read     | ahle hit          |                   | W = Writable      | hit               | II – I Inimple    | emented bit re    | ad as 'O'        |                  |  |

## REGISTER 23-3: RTCTIME: RTC TIME VALUE REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | —                 | —                 | _                 | MONTH10           |                   | 01<3:0>           |                  |                  |

| 45.0         | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | _                 | _                 | DAY1              | 0<1:0>            |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | _                 | _                 | _                 | _                 | V                 | VDAY01<2:0:      | >                |

## REGISTER 23-6: ALRMDATE: ALARM DATE VALUE REGISTER

## Legend:

| 3                 |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-21 Unimplemented: Read as '0'

bit 20 MONTH10: Binary Coded Decimal value of months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary Coded Decimal value of days bits, 10s place digit; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY01<2:0>: Binary Coded Decimal value of weekdays bits; contains a value from 0 to 6

## 27.1 Control Registers

# DS60001404A-page 254

## TABLE 27-1: HIGH/LOW-VOLTAGE DETECT REGISTER MAP

| ess                       |                                 | 0         |       |       |       |       |       |       |      | Bits   |      |      |      |      |      |       |       |      | Ś         |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|--------|------|------|------|------|------|-------|-------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0 | All Reset |

| 1000                      | HLVDCON                         | 31:16     | -     | —     | —     | —     | —     | _     | —    | —      | _    | —    | —    | —    | —    | -     | —     | -    | 0000      |

| 1800                      | HLVDCON                         | 15:0      | ON    | —     | _     | —     | VDIR  | BGVST | -    | HLVDET |      | _    | —    | —    |      | HLVDL | <3:0> |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 13.2 "CLR, SET, and INV Registers" for more information.

## 29.3.4 DEEP SLEEP MODE

Deep Sleep mode brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device.

## • Deep Sleep

In this mode, the CPU, RAM and most peripherals are powered down. Power is maintained to the DSGPR0 register and one or more of the RTCC, DSWDT and DSGPR1 through DSGPR32 registers.

Which of these peripherals is active depends on the state of the following register bits when Deep Sleep mode is entered:

## • RTCDIS (DSCON<12>)

This bit must be set to disable the RTCC in Deep Sleep mode (see Register 29-1).

## • DSWDTEN (DEVCFG2<30>)

This Configuration bit must be set to enable the DSWDT register in Deep Sleep mode (see Register 30-3)

## • DSGPREN (DSCON<13>)

This bit must be set to enable the DSGPR1 through DSGPR32 registers in Deep Sleep mode (see Register 29-1).

Note: The Deep Sleep Control registers can only be accessed after the system unlock sequence has been performed. In addition, the Deep Sleep Control registers must be written twice.

In addition to the conditionally enabled peripherals described above, the MCLR filter and INT0 pin are enabled in Deep Sleep mode.

## 29.3.5 VBAT MODE

VBAT mode is similar to Deep Sleep mode, except that the device is powered from the VBAT pin. VBAT mode is controlled strictly by hardware, without any software intervention. VBAT mode is initiated when VDD falls VPOR (refer the 33.0 "Electrical below to Characteristics" for definitions of VDD and VPOR). An external power source must be connected to the VBAT pin before power is removed from VDD to enter VBAT mode. VBAT is the lowest battery-powered mode that can maintain an RTCC. Wake-up from VBAT mode can only occur when VDD is reapplied. The wake-up will appear to be a POR to the rest of the device.

In VBAT mode, the Deep Sleep Watchdog Timer is disabled. The RTCC and DSGPR1 through DSGPR32 registers may be enabled or disabled depending on the state of the RTCDIS bit (DSCON<12>) and the DSGPREN bit (DSCON<13>), respectively. Deep Sleep Persistent General Purpose Register 0 (DSGPR0) is always enabled in VBAT mode.

## 29.3.6 XLP POWER-SAVING MODES

Figure 29-1 shows a block diagram of the system domain for XLP devices and the related power-saving features. The various blocks are controlled by the following Configuration bit settings and SFRs:

- DSBOREN (DEVCFG2<20>)

- DSEN (DSCON<15>)

- DSGPREN (DSCON<13>)

- DSWDTEN (DEVCFG2<30>)

- DSWDTOSC (DEVCFG2<29>)

- RELEASE (DSCON<0>)

- RTCCLKSEL (RTCCON <9:8>)

- RTCDIS (DSCON<12>)

- SLPEN (OSCCON<4>)

- VREGS (PWRCON<0>)

| DC CHA        |         | STICS                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq T_A \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq T_A \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                 |  |  |

|---------------|---------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.               | Units | Comments                                                        |  |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                   | _    | 10                 | μs    | See Note 1                                                      |  |  |

| D313          | DACREFH |                                                             | AVss                                                                                                                                                                                                                                                                                | —    | AVdd               | V     | CVRSRC with CVRSS = 0                                           |  |  |

|               |         | Reference Range                                             | VREF-                                                                                                                                                                                                                                                                               | —    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |

| D314          | DVref   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                                                                                                                                                   | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |

|               |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                   | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |

| D315          | DACRES  | Resolution                                                  | —                                                                                                                                                                                                                                                                                   | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |

|               |         |                                                             | —                                                                                                                                                                                                                                                                                   | _    | DACREFH/32         | -     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |

| D316          | DACACC  | ACACC Absolute Accuracy <sup>(2)</sup>                      | —                                                                                                                                                                                                                                                                                   | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |

|               |         |                                                             | —                                                                                                                                                                                                                                                                                   | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |

## TABLE 33-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

## TABLE 33-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |       |                                                                                                    |  |  |

|--------------------|--------|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min. | Typical                                                                                                                                                                                                                                                                           | Max. | Units | Comments                                                                                           |  |  |

| D321               | Cefc   | External Filter Capacitor Value | 8    | 10                                                                                                                                                                                                                                                                                |      | μF    | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |  |

## TABLE 33-38: PARALLEL SLAVE PORT REQUIREMENTS

| АС СН         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |

|---------------|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                            | Тур. | Max. | Units | Conditions |  |