#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256b-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 8: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITHOUT VBAT

28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

### PIC32MX154F128B PIC32MX174F256B

28

1

| Pin # | Full Pin Name                               | Pin # | Full Pin Name                                 |

|-------|---------------------------------------------|-------|-----------------------------------------------|

| 1     | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0        | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                  |

| 2     | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/RB1 | 16    | Vss                                           |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2        | 17    | VCAP                                          |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3          | 18    | PGED1/RPB10/CTED11/PMD2/RB10                  |

| 5     | Vss                                         | 19    | PGEC1/TMS/RPB11/PMD1/RB11                     |

| 6     | OSC1/CLKI/RPA2/RA2                          | 20    | AN12/PMD0/RB12                                |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                     | 21    | AN11/RPB13/CTPLS/PMRD/RB13                    |

| 8     | SOSCI/RPB4/RB4 <sup>(5)</sup>               | 22    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB1 |

| 9     | SOSCO/RPA4/T1CK/CTED9/RA4                   | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15         |

| 10    | Vdd                                         | 24    | AVss                                          |

| 11    | PGED3/RPB5/ASDA2/PMD7/RB5                   | 25    | AVDD                                          |

| 12    | PGEC3/RPB6/ASCL2/PMD6/RB6                   | 26    | MCLR                                          |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7                | 27    | VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0     |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8               | 28    | VREF-/AN1/RPA1/ASCL1/CTED2/RA1                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

5: This is an input-only pin.

## 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This document contains device-specific information for PIC32MX1XX/2XX 28/44-pin XLP Family devices.

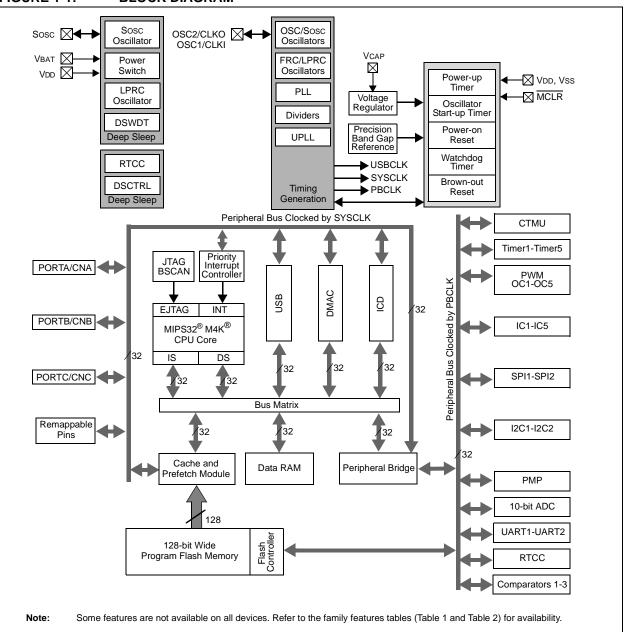

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/44-pin XLP Family of devices.

Table 1-1 through Table 1-16 list the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1: BLOCK DIAGRAM

NOTES:

| Bit<br>Range        | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24               | —                 | —                 | —                 |                   | IP03<2:0>         | IS03<1:0>         |                  |                  |  |  |

| 23:16               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10               | _                 | —                 | _                 |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |  |  |

| 15:8                | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0                | _                 | —                 | _                 |                   | IP01<2:0>         |                   | IS01-            | <1:0>            |  |  |

| 7.0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0 — — — IP00<2:0> |                   |                   |                   |                   |                   |                   |                  | IS00<1:0>        |  |  |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| Logonal           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-29 Unimplemented: Read as '0'

- bit 28-26 **IP03<2:0>:** Interrupt Priority bits 111 = Interrupt priority is 7

- bit 17-16 IS02<1:0>: Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- bit 12-10 IP01<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7

- •

- •

- 010 =Interrupt priority is 2

- 001 =Interrupt priority is 1

- 000 =Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

| REGIS   | STER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10- | 8 NOSC<2:0>: New Oscillator Selection bits                                                                                                      |

|         | 111 = Reserved                                                                                                                                  |

|         | 110 = Reserved                                                                                                                                  |

|         | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                                                   |

|         | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                                             |

|         | 011 = Reserved<br>010 = Primary Oscillator (Posc) (HS or EC)                                                                                    |

|         | 001 = System PLL (SPLL)                                                                                                                         |

|         | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                    |

|         | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>                                                    |

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                                                                        |

|         | 1 = Clock and PLL selections are locked                                                                                                         |

|         | 0 = Clock and PLL selections are not locked and may be modified                                                                                 |

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                      |

| bit 4   | SLPEN: Sleep Mode Enable bit                                                                                                                    |

|         | 1 = Device will enter Sleep mode when a WAIT instruction is executed                                                                            |

|         | 0 = Device will enter Idle mode when a WAIT instruction is executed                                                                             |

| bit 3   | CF: Clock Fail Detect bit                                                                                                                       |

|         | 1 = FSCM has detected a clock failure                                                                                                           |

|         | 0 = No clock failure has been detected                                                                                                          |

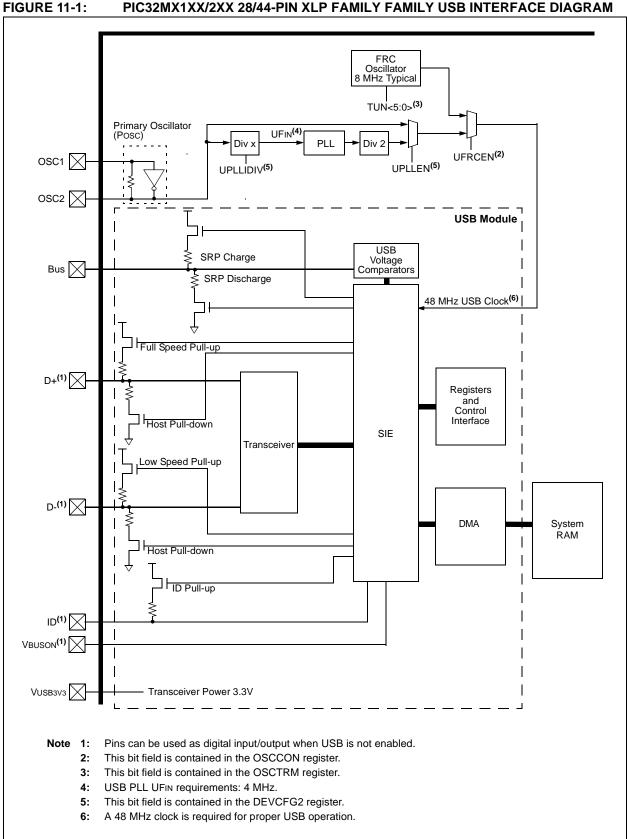

| bit 2   | UFRCEN: USB FRC Clock Enable bit                                                                                                                |

|         | 1 = Enable FRC as the USB clock source                                                                                                          |

|         | 0 = Use the Primary Oscillator or UPLL as the USB clock source                                                                                  |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                  |

|         | <ul> <li>1 = Enable Secondary Oscillator</li> <li>0 = Disable Secondary Oscillator</li> </ul>                                                   |

| hit O   | OSWEN: Oscillator Switch Enable bit <sup>(1)</sup>                                                                                              |

| bit 0   |                                                                                                                                                 |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul> |

|         |                                                                                                                                                 |

|         |                                                                                                                                                 |

**Note 1:** The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the reset value is '1'. When IESO = 0, the reset value is '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

| ILCIOIC L    |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                 |                   |                   | —                 |                  | —                |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | _                 | —                 | _                 | _                 | _                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | CHCSIZ<15:8>      |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | CHCSIZ<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

111111111111111 = 65,535 bytes transferred on an event

### **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24             | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |  |  |

| 00.40             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16             | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0              | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8 CHCPTR<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0 CHCPTR<7:0>   |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

## REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## TABLE 12-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| s                           | L 12-0.          |           |       | Bits  |        |       |       |       |      |      |      |      |      |      |            |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|--------|-------|-------|-------|------|------|------|------|------|------|------------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13  | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3       | 18/2  | 17/1   | 16/0 | All Resets |

| 5404                        |                  | 31:16     |       | _     | —      | —     | —     | _     | —    | _    | _    | _    | —    | _    |            | —     | —      | —    | 0000       |

| FA04                        | INT1R            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | INT1F | R<3:0> |      | 0000       |

| 5400                        |                  | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA08                        | INT2R            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | INT2F | <3:0>  |      | 0000       |

| 5400                        |                  | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA0C                        | INT3R            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA10                        | INT4R            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | INT4F | <3:0>  |      | 0000       |

| 5440                        | TOOKD            | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | T2CK  | R<3:0> |      | 0000       |

| 5440                        | TOOLD            | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | T3CKR<3:0> |       | 0000   |      |            |

| <b>5</b> 400 <b>7</b>       | 3                | 31:16     | _     | _     | _      | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA20                        | 20 T4CKR 15:0    |           |       | T4CKI | R<3:0> |       | 0000  |       |      |      |      |      |      |      |            |       |        |      |            |

| 5404                        | TEOKD            | 31:16     |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | _     | —      | —    | 0000       |

| FA24                        | T5CKR            | 15:0      |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | T5CKI | R<3:0> |      | 0000       |

| FA 00                       | 1040             | 31:16     |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | _     | —      | —    | 0000       |

| FA28                        | IC1R             | 15:0      |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | IC1R  | <3:0>  |      | 0000       |

| FA00                        | 1000             | 31:16     |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | _     | —      | —    | 0000       |

| FA2C                        | IC2R             | 15:0      |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | IC2R  | <3:0>  |      | 0000       |

| FA 00                       | 1000             | 31:16     |       | —     | _      | —     | —     | —     | —    | —    | —    |      | _    | _    |            | _     | —      | —    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | —     | —      | _     | —     | —     | _    | —    | —    | _    | —    | —    |            | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R             | 31:16     |       | _     | _      | _     | -     | _     | -    | —    | _    |      | _    | _    |            | _     | _      | _    | 0000       |

| FA34                        | 104R             | 15:0      | _     | —     | —      | _     | —     | —     | _    | —    | —    | _    | —    | —    |            | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R             | 31:16     | _     | —     | —      | _     | —     | —     | _    | —    | —    | _    | —    | —    | _          | —     | —      | _    | 0000       |

| FA36                        | ICOR             | 15:0      | _     | —     | —      | _     | —     | —     | _    | —    | —    | _    | —    | —    |            | IC5R  | <3:0>  |      | 0000       |

| FA 40                       |                  | 31:16     |       | _     | _      | -     | -     | _     |      | —    | _    |      | _    | —    |            | —     | —      | _    | 0000       |

| FA48                        | OCFAR            | 15:0      |       | _     | _      | -     | -     | _     |      | —    | _    |      | _    | —    |            | OCFA  | R<3:0> |      | 0000       |

| EA 40                       | 00500            | 31:16     |       | —     | —      | _     | _     | —     | _    | —    | _    | _    | —    | —    | _          | _     | _      |      | 0000       |

| FA4C                        | OCFBR            | 15:0      |       | —     | —      | —     | —     | —     | —    | —    |      | -    | —    | —    |            | OCFB  | R<3:0> |      | 0000       |

| FAFO                        |                  | 31:16     |       | —     | —      | —     | —     | —     | —    | —    |      | -    | —    | —    |            | —     | —      | —    | 0000       |

| FA50                        | U1RXR            | 15:0      |       | —     | _      | —     | -     | —     | —    | —    | _    | —    | _    | —    |            | U1RX  | R<3:0> |      | 0000       |

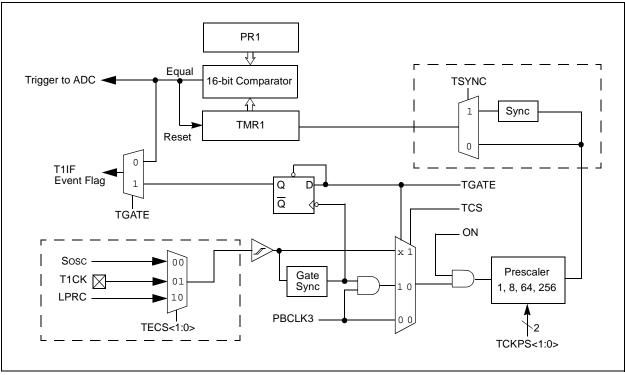

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

FIGURE 13-1: TIMER1 BLOCK DIAGRAM

The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

Figure 13-1 illustrates a general block diagram of Timer1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 31:24        | WDTCLRKEY<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 23:16        | WDTCLRKEY<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R-y               | R-y               | R-y               | R-y              | R-y              |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | _                 |                   |                   | RUNDIV<4:0        | )>               |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |

| 7:0          | _                 | _                 |                   |                   |                   |                   | —                | WDTWINEN         |  |  |  |

### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                          |                                    |  |  |  |  |  |

|-------------------|-----------------------------------------------|------------------------------------------|------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bi                     | U = Unimplemented bit, read as '0' |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | 0' = Bit is cleared $x = Bit is unknown$ |                                    |  |  |  |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits To clear the Watchdog Timer to prevent a time-out, software must write the value 0x5743 to these bits using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = The Watchdog Timer module is enabled

- 0 = The Watchdog Timer module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12-8 **RUNDIV<4:0>:** Watchdog Timer Postscaler Value in Run Mode bits

- In Run mode, these bits are set to the values of the WDTPS<4:0> Configuration bits in DEVCFG1.

- bit 7-1 Unimplemented: Read as '0'

- bit 0 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- **Note 1:** This bit only has control when FWDTEN (DEVCFG1<23>) = 0.

NOTES:

## **REGISTER 20-2:** I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                 |

| bit 3 | <b>S</b> : Start bit                                                                                                                                                                                                             |

| DIL D | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                                                                                                                                        |

|       | 0 = Start bit was not detected last<br>Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                        |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                |

|       | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                              |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>      |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                             |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                                                                                                        |

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

0 = Transmit complete, I2CxTRN is empty

© 2016 Microchip Technology Inc.

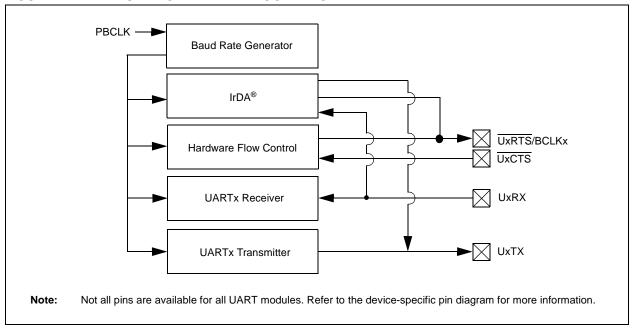

## 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the web Microchip PIC32 site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/44-pin XLP Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The following are key features of the UART module:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 33.4 bps to 17.5 Mbps at 72 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

- · Auto-baud support

- · Ability to receive data during Sleep mode

Figure 21-1 illustrates a simplified block diagram of the UART module.

FIGURE 21-1: UART SIMPLIFIED BLOCK DIAGRAM

|              | -                 | -                 |                   |                   |                   |                   |                  | /                |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   |                   | -                 |                  | —                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

## REGISTER 22-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | Cleared by Software |                                    |                    |  |

|-------------------|---------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

# FRC<sup>(1)</sup> $\overrightarrow{Div 2}$ ADCS<7:0> ADCS<7:0> $\overrightarrow{ADCS}$ TPB<sup>(2)</sup> Note 1: See 33.0 "Electrical Characteristics" for the exact FRC clock value. 2: Refer to Figure 8-1 in 8.0 "Oscillator Configuration" for more information.

### FIGURE 24-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

## 28.1 CTMU Control Registers

## TABLE 28-1: CTMU REGISTER MAP

| ess                        |                                 |           |         | Bits    |          |       |         |          |          |          |         | ú       |                |       |      |      |      |       |            |

|----------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|----------------|-------|------|------|------|-------|------------|

| Virtual Addre:<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5           | 20/4  | 19/3 | 18/2 | 17/1 | 16/0  | All Resets |

| 4000                       |                                 | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL<3:0> — |       | —    | 0000 |      |       |            |

| A200                       | CTMUCON                         | 15:0      | ON      | —       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM<         | <5:0> |      |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

DS60001404A-page 258

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-----------------------|------------------------------|------------------|------------------|--|--|

| 04.04        | R/P                   | R/P               | R/P               | R/P               | R/P                   | R/P                          | R/P              | R/P              |  |  |

| 31:24        | FDSEN                 | DSWDTEN           | DSWDTOSC          | DSWDTPS<4:0>      |                       |                              |                  |                  |  |  |

| 23:16        | R/P                   | r-1               | R/P               | R/P               | r-1                   | R/P                          | R/P              | R/P              |  |  |

| 23.10        | DSBOREN               | —                 | VBATBOREN         | BOREN             | BOREN — FPLLODIV<2:0> |                              |                  |                  |  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1                   | R/P                          | R/P              | R/P              |  |  |

| 15:8         | UPLLEN <sup>(1)</sup> | —                 | —                 | —                 | —                     | UPLLIDIV<2:0> <sup>(1)</sup> |                  |                  |  |  |

| 7.0          | R/P                   | R/P-1             | R/P               | R/P-1             | r-1                   | R/P                          | R/P              | R/P              |  |  |

| 7:0          | FPLLICLK              |                   | FPLLMUL<2:0       | >                 |                       | FPLLIDIV<2:0>                |                  |                  |  |  |

## REGISTER 30-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Legend:           | r = Reserved bit | P = Programmable bit                    |  |  |  |  |

|-------------------|------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 31 **FDSEN:** Deep Sleep Enable bit

1 = Deep Sleep mode is entered on a WAIT command

0 = Sleep mode is entered on a WAIT command

- bit 30 **DSWDTEN:** Deep Sleep Watchdog Timer Enable bit

- 1 = Enable the Deep Sleep Watchdog Timer (DSWDT) during Deep Sleep mode

- 0 = Disable the DSWDT during Deep Sleep mode

- bit 29 **DSWDTOSC:** Deep Sleep Watchdog Timer Reference Clock Select bit 1 = Select the LPRC Oscillator as the DSWDT reference clock 0 = Select the Secondary Oscillator as the DSWDT reference clock

## bit 28-24 **DSWDTPS<4:0>:** Deep Sleep Watchdog Timer Postscale Select bits

| 11<br>11<br>11<br>11<br>11<br>11<br>10<br>10<br>10                              | 1110000111100     | 1001100110011     | 0101010101010       | 11111111111111      | 33332222222      | 5<br>4<br>3<br>2<br>1<br>0<br>9<br>8<br>7<br>6<br>5<br>4<br>3 |  |

|---------------------------------------------------------------------------------|-------------------|-------------------|---------------------|---------------------|------------------|---------------------------------------------------------------|--|

| 10<br>10<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>0 | 00111100001111000 | 00110011001100110 | 1010101010101010101 | 1111111111111111111 | 2221111111119876 | 2109876543210                                                 |  |

Note 1: This bit is only available on PIC32MX2XX devices.

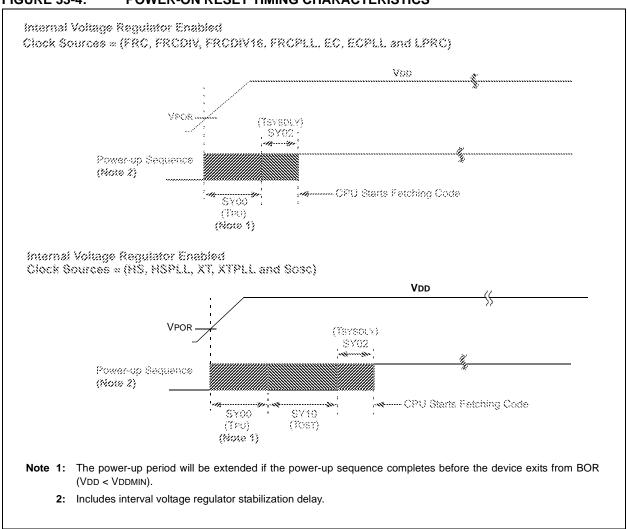

## FIGURE 33-4: POWER-ON RESET TIMING CHARACTERISTICS

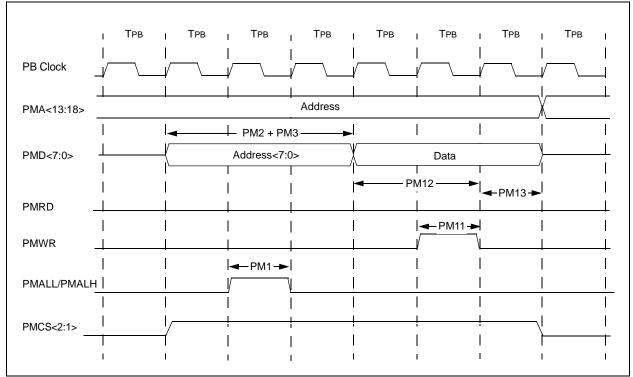

| TABLE 33-39: PARALLEL MASTER PORT READ TIMING REQUIREMENTS |

|------------------------------------------------------------|

|------------------------------------------------------------|

| АС СНА        | ARACTER | ISTICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |  |

|---------------|---------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                | Тур.  | Max. | Units | Conditions |  |  |

| PM1           | TLAT    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                     | 1 Трв |      |       |            |  |  |

| PM2           | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                                                                   | 2 Трв | _    | _     | _          |  |  |

| PM3           | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                                                                   | 1 Трв | _    |       | —          |  |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                   | —     | _    | ns    | _          |  |  |

| PM5           | Trd     | PMRD Pulse Width                                                     | —                                                                                                                                                                                                                                                                                   | 1 Трв | _    | —     | —          |  |  |

| PM6           | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                                  | —     | —    | ns    | —          |  |  |

| PM7           | TDHOLD  | PMRD or PMENB Inactive to<br>Data In Invalid (data hold time)        | —                                                                                                                                                                                                                                                                                   | 80    | _    | ns    | —          |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.