Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

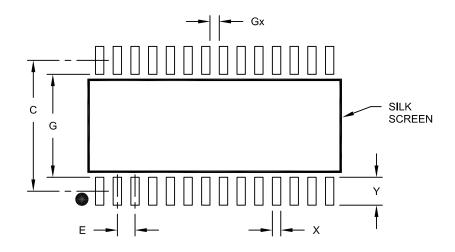

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256b-v-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX XLP Family core.                          |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

#### TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|---------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0                 | U-0              |

| 31:24        | —                 | —                 | —                    | —                     | —                      | —                 | —                   | —                |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0                 | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                   | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0                 | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                   | —                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0               | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | <b>?&lt;3:0&gt;</b> |                  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                                                                                                                                                                                                           |

|          | <ul> <li>1 = Initiate a Flash operation. Hardware clears this bit when the operation completes</li> <li>0 = Flash operation is complete or inactive</li> </ul>                                                                                                                                    |

| bit 14   | WREN: Write Enable bit                                                                                                                                                                                                                                                                            |

|          | This is the only bit in this register reset by a device Reset.                                                                                                                                                                                                                                    |

|          | 1 = Enable writes to WR bit and enables HLVD circuit                                                                                                                                                                                                                                              |

|          | 0 = Disable writes to WR bit and disables HLVD circuit                                                                                                                                                                                                                                            |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                                                                                                                                                                                                             |

|          | This bit is read-only and is automatically set by hardware.                                                                                                                                                                                                                                       |

|          | 1 = Program or erase sequence did not complete successfully                                                                                                                                                                                                                                       |

|          | 0 = Program or erase sequence completed normally                                                                                                                                                                                                                                                  |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                                                                                                                                                                                                 |

|          | This bit is read-only and is automatically set by hardware.                                                                                                                                                                                                                                       |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                                                                                                                                                                                              |

|          | 0 = Voltage level is acceptable for programming                                                                                                                                                                                                                                                   |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                                                                                                                                                                                               |

|          | This bit is read-only and is automatically set and cleared by the hardware.                                                                                                                                                                                                                       |

|          | 1 = Low-voltage event is active                                                                                                                                                                                                                                                                   |

|          | 0 = Low-voltage event is not active                                                                                                                                                                                                                                                               |

| bit 10-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                        |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                                                                                                                                                                                                    |

|          | These bits are writable when $WREN = 0$ .                                                                                                                                                                                                                                                         |

|          | 1111 = Reserved                                                                                                                                                                                                                                                                                   |

|          | •                                                                                                                                                                                                                                                                                                 |

|          | •                                                                                                                                                                                                                                                                                                 |

|          | 0111 = Reserved                                                                                                                                                                                                                                                                                   |

|          | 0110 = No operation                                                                                                                                                                                                                                                                               |

|          | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected<br>0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected<br>0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected |

|          | 0010 = No operation                                                                                                                                                                                                                                                                               |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation                                                                                                                                                                             |

|          |                                                                                                                                                                                                                                                                                                   |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

# TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

|                                 | Interrupt Source(1) IRQ Vector Interrupt Bit Location Pe |        |              |               |             |              |           |  |

|---------------------------------|----------------------------------------------------------|--------|--------------|---------------|-------------|--------------|-----------|--|

| Interrupt Source <sup>(1)</sup> | #                                                        | #      | Flag         | Enable        | Priority    | Sub-priority | Interrupt |  |

|                                 |                                                          | Highes | st Natural C | rder Priority | ,           |              |           |  |

| CT – Core Timer Interrupt       | 0                                                        | 0      | IFS0<0>      | IEC0<0>       | IPC0<4:2>   | IPC0<1:0>    | No        |  |

| CS0 – Core Software Interrupt 0 | 1                                                        | 1      | IFS0<1>      | IEC0<1>       | IPC0<12:10> | IPC0<9:8>    | No        |  |

| CS1 – Core Software Interrupt 1 | 2                                                        | 2      | IFS0<2>      | IEC0<2>       | IPC0<20:18> | IPC0<17:16>  | No        |  |

| INT0 – External Interrupt       | 3                                                        | 3      | IFS0<3>      | IEC0<3>       | IPC0<28:26> | IPC0<25:24>  | No        |  |

| T1 – Timer1                     | 4                                                        | 4      | IFS0<4>      | IEC0<4>       | IPC1<4:2>   | IPC1<1:0>    | No        |  |

| IC1E – Input Capture 1 Error    | 5                                                        | 5      | IFS0<5>      | IEC0<5>       | IPC1<12:10> | IPC1<9:8>    | Yes       |  |

| IC1 – Input Capture 1           | 6                                                        | 5      | IFS0<6>      | IEC0<6>       | IPC1<12:10> | IPC1<9:8>    | Yes       |  |

| OC1 – Output Compare 1          | 7                                                        | 6      | IFS0<7>      | IEC0<7>       | IPC1<20:18> | IPC1<17:16>  | No        |  |

| INT1 – External Interrupt 1     | 8                                                        | 7      | IFS0<8>      | IEC0<8>       | IPC1<28:26> | IPC1<25:24>  | No        |  |

| T2 – Timer2                     | 9                                                        | 8      | IFS0<9>      | IEC0<9>       | IPC2<4:2>   | IPC2<1:0>    | No        |  |

| IC2E – Input Capture 2          | 10                                                       | 9      | IFS0<10>     | IEC0<10>      | IPC2<12:10> | IPC2<9:8>    | Yes       |  |

| IC2 – Input Capture 2           | 11                                                       | 9      | IFS0<11>     | IEC0<11>      | IPC2<12:10> | IPC2<9:8>    | Yes       |  |

| OC2 – Output Compare 2          | 12                                                       | 10     | IFS0<12>     | IEC0<12>      | IPC2<20:18> | IPC2<17:16>  | No        |  |

| INT2 – External Interrupt 2     | 13                                                       | 11     | IFS0<13>     | IEC0<13>      | IPC2<28:26> | IPC2<25:24>  | No        |  |

| T3 – Timer3                     | 14                                                       | 12     | IFS0<14>     | IEC0<14>      | IPC3<4:2>   | IPC3<1:0>    | No        |  |

| IC3E – Input Capture 3          | 15                                                       | 13     | IFS0<15>     | IEC0<15>      | IPC3<12:10> | IPC3<9:8>    | Yes       |  |

| IC3 – Input Capture 3           | 16                                                       | 13     | IFS0<16>     | IEC0<16>      | IPC3<12:10> | IPC3<9:8>    | Yes       |  |

| OC3 – Output Compare 3          | 17                                                       | 14     | IFS0<17>     | IEC0<17>      | IPC3<20:18> | IPC3<17:16>  | No        |  |

| INT3 – External Interrupt 3     | 18                                                       | 15     | IFS0<18>     | IEC0<18>      | IPC3<28:26> | IPC3<25:24>  | No        |  |

| T4 – Timer4                     | 19                                                       | 16     | IFS0<19>     | IEC0<19>      | IPC4<4:2>   | IPC4<1:0>    | No        |  |

| IC4E – Input Capture 4 Error    | 20                                                       | 17     | IFS0<20>     | IEC0<20>      | IPC4<12:10> | IPC4<9:8>    | Yes       |  |

| IC4 – Input Capture 4           | 21                                                       | 17     | IFS0<21>     | IEC0<21>      | IPC4<12:10> | IPC4<9:8>    | Yes       |  |

| OC4 – Output Compare 4          | 22                                                       | 18     | IFS0<22>     | IEC0<22>      | IPC4<20:18> | IPC4<17:16>  | No        |  |

| INT4 – External Interrupt 4     | 23                                                       | 19     | IFS0<23>     | IEC0<23>      | IPC4<28:26> | IPC4<25:24>  | No        |  |

| T5 – Timer5                     | 24                                                       | 20     | IFS0<24>     | IEC0<24>      | IPC5<4:2>   | IPC5<1:0>    | No        |  |

| IC5E – Input Capture 5 Error    | 25                                                       | 21     | IFS0<25>     | IEC0<25>      | IPC5<12:10> | IPC5<9:8>    | Yes       |  |

| IC5 – Input Capture 5           | 26                                                       | 21     | IFS0<26>     | IEC0<26>      | IPC5<12:10> | IPC5<9:8>    | Yes       |  |

| OC5 – Output Compare 5          | 27                                                       | 22     | IFS0<27>     | IEC0<27>      | IPC5<20:18> | IPC5<17:16>  | No        |  |

| AD1 – ADC1 Convert done         | 28                                                       | 23     | IFS0<28>     | IEC0<28>      | IPC5<28:26> | IPC5<25:24>  | Yes       |  |

| FSCM – Fail-Safe Clock Monitor  | 29                                                       | 24     | IFS0<29>     | IEC0<29>      | IPC6<4:2>   | IPC6<1:0>    | No        |  |

| RTCC – Real-Time Clock and      | 30                                                       | 25     | IFS0<30>     | IEC0<30>      | IPC6<12:10> | IPC6<9:8>    | No        |  |

| Calendar                        | 04                                                       |        |              |               |             |              | NIa       |  |

| FCE – Flash Control Event       | 31                                                       | 26     | IFS0<31>     | IEC0<31>      | IPC6<20:18> | IPC6<17:16>  | No        |  |

| CMP1 – Comparator Interrupt     | 32                                                       | 27     | IFS1<0>      | IEC1<0>       | IPC6<28:26> | IPC6<25:24>  | No        |  |

| CMP2 – Comparator Interrupt     | 33                                                       | 28     | IFS1<1>      | IEC1<1>       | IPC7<4:2>   | IPC7<1:0>    | No        |  |

| CMP3 – Comparator Interrupt     | 34                                                       | 29     | IFS1<2>      | IEC1<2>       | IPC7<12:10> | IPC7<9:8>    | No        |  |

| USB – USB Interrupts            | 35                                                       | 30     | IFS1<3>      | IEC1<3>       | IPC7<20:18> | IPC7<17:16>  | Yes       |  |

| SPI1E – SPI1 Fault              | 36                                                       | 31     | IFS1<4>      | IEC1<4>       | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

| SPI1RX – SPI1 Receive Done      | 37                                                       | 31     | IFS1<5>      | IEC1<5>       | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

| SPI1TX – SPI1 Transfer Done     | 38                                                       | 31     | IFS1<6>      | IEC1<6>       | IPC7<28:26> | IPC7<25:24>  | Yes       |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

# 8.2 Oscillator Control Registers

| sse                         |                  |           |       |       |           |       |            |              |                  |                     | Bits       |      |         |         |           |               |         |        | -                         |

|-----------------------------|------------------|-----------|-------|-------|-----------|-------|------------|--------------|------------------|---------------------|------------|------|---------|---------|-----------|---------------|---------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13     | 28/12 | 27/11      | 26/10        | 25/9             | 24/8                | 23/7       | 22/6 | 21/5    | 20/4    | 19/3      | 18/2          | 17/1    | 16/0   | All Resets <sup>(1)</sup> |

| F000                        | OSCCON           | 31:16     | _     | _     | —         | —     | —          |              | FRCDIV<2:0       | >                   | DRMEN      | _    | SLP2SPD | _       | —         | —             | —       | —      | 0020                      |

| F000                        | USCCON           | 15:0      | Ι     | (     | COSC<2:0> |       | —          |              | NOSC<2:0>        |                     | CLKLOCK    | _    | —       | SLPEN   | CF        | UFRCEN        | SOSCEN  | OSWEN  | xx0x                      |

| F010                        | 010 OSCTUN       | 31:16     | —     | _     | —         | —     | —          | —            | —                | —                   | —          |      | —       | —       | _         | —             | —       | —      | 0000                      |

| F010                        |                  | 15:0      | _     | _     | _         |       | —          | _            | —                |                     | —          |      |         |         | ΤL        | JN<5:0>       | •       |        | 00xx                      |

| F000                        |                  | 31:16     | _     | _     | _         |       | —          | PLLODIV<2:0> |                  |                     | —          |      | —       | _       | —         | PLLMULT<2:0>  |         | 01xx   |                           |

| F020                        | SPLLCON          | 15:0      | —     |       | —         | —     | —          | I            | PLLIDIV<2:0      | >                   | PLLICLK    | —    | —       | —       | _         | —             | —       | —      | 0x0x                      |

| F030                        | UPLLCON          | 31:16     | —     |       | —         | —     | —          | UP           | UPLLODIV<2:0>(1) |                     |            | —    | —       | —       | _         | UPLLMULT<2:0> |         | >      | 01xx                      |

| FU30                        | UPLLCON          | 15:0      | —     |       | —         | —     | —          | UF           | PLLIDIV<2:0      | <sub>&gt;</sub> (1) | —          | —    | —       | —       | —         | —             | —       | —      | 0x0x                      |

| E090                        | REF00CON         | 31:16     | —     |       |           |       |            |              |                  |                     | RODIV<14:0 | )>   |         |         |           |               |         |        | 0000                      |

| FU0U                        | REFUCCON         | 15:0      | ON    |       | SIDL      | OE    | RSLP       | —            | DIVSWEN          | ACTIVE              | —          | —    | —       | —       |           | ROS           | EL<3:0> |        | 0000                      |

| E000                        | <b>REFOOTRIM</b> | 31:16     |       |       |           |       | ROTRIM<8:0 | )>           |                  |                     |            | _    | —       |         | _         | _             | —       | _      | 0000                      |

| F090                        | REFOULKIN        | 15:0      | -     | _     | _         | _     | —          | _            | —                | —                   | _          | _    | —       |         | _         | _             | —       | _      | 0000                      |

| F0A0                        | PB0DIV           | 31:16     | -     | _     | _         | _     | —          | _            | —                | —                   | _          | _    | —       |         | _         | _             | —       | _      | 0000                      |

| FUAU                        | FOUDIV           | 15:0      | —     |       | —         | —     | PBDIVRDY   | —            | —                | —                   | —          |      |         |         | PBDIV<6:0 | )>            |         |        | 8801                      |

| F0C0                        | CLKSTAT          | 31:16     | —     |       | —         | —     | —          | —            | —                | —                   | —          | —    | —       | —       | —         | —             | —       | —      | 0000                      |

| FUCU                        | GENSTAT          | 15:0      | _     | _     | _         | _     | —          | _            | _                | UPLLRDY             | SPLLRDY    | _    | LPRCRDY | SOSCRDY | _         | POSCRDY       | SPLLRDY | FRCRDY | 0000                      |

# TABLE 8-1: OSCILLATOR CONFIGURATION REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

#### REGISTER 8-3: SPLLCON: SYSTEM PLL CONTROL REGISTER

bit 10-8 PLLIDIV<2:0>: System PLL Input Clock Divider bits

- 111 = Divide by 12

- 110 = Divide by 10

- 101 =Divide by 6

- 100 =Divide by 5

- 011 = Divide by 4

- 010 = Divide by 3

- 001 = Divide by 2

- 000 = Divide by 1

The default setting is specified by the FPLLIDIV<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 30-3 in **30.0** "**Special Features**" for information. If the PLLICLK is set for FRC, this setting is ignored by the PLL and the divider is set to Divide-by-1.

bit 7 PLLICLK: System PLL Input Clock Source bit

1 = FRC is selected as the input to the System PLL0 = POSC is selected as the input to the System PLL

The POR default is specified by the FPLLICLK Configuration bit in the DEVCFG2 register. Refer to Register 30-3 in **30.0** "**Special Features**" for information.

- bit 6-0 Unimplemented: Read as '0'

- Note 1: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

- 2: Writes to this register are not allowed if the SPLL is selected as a clock source (COSC<2:0> = 001).

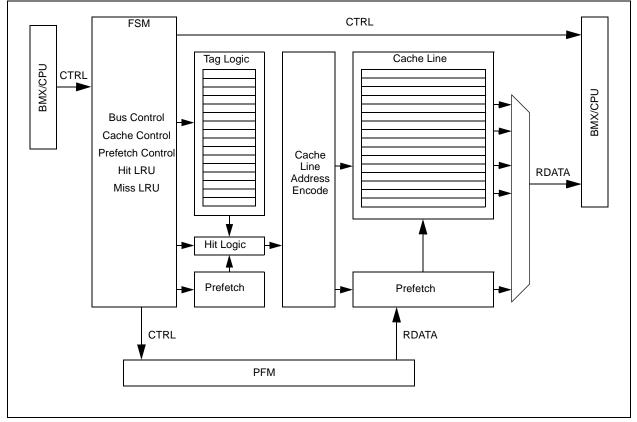

# **10.0 PREFETCH CACHE**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 4.** "**Prefetch Cache**" (DS60001119), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching. The following are key features of the Prefetch Cache module:

- 16 fully associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- Pseudo LRU replacement policy

- All cache lines are software writable

- 16-byte parallel memory fetch

- Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 10-1.

# FIGURE 10-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       | —                     | —                | _                    |

| 22:46        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | —                     | —                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         | -                 | -                 | —                        | —                 | _                     | —                     | —                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | E SE0             | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              |                   |                   | TOKBUSY <sup>(1,5)</sup> | USDROI            | TIOSTEIN'             | RESUME                | FFDROI           | SOFEN <sup>(5)</sup> |

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>JSTATE:</b> Live Differential Receiver JSTATE flag bit |

|-------|-----------------------------------------------------------|

|       | 1 = JSTATE was detected on the USB                        |

|       |                                                           |

- 0 = No JSTATE was detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-Ended Zero was detected on the USB

0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### TABLE 12-4: PORTB REGISTER MAP

| sse                         |                  |           |               |               |                              |                              |                              |                              |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|------------------------------|------------------------------|------------------------------|------------------------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13                        | 28/12                        | 27/11                        | 26/10                        | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

| 6100                        | ANSELB           | 31:16     | —             |               | _                            | —                            | _                            | _                            | _            | —            | _            | _                           | _            | _            | _            | _            | _            |              | 0000       |

| 0100                        | ANOLLD           | 15:0      | ANSB15        | ANSB14        | ANSB13 <sup>(3)</sup>        | ANSB12 <sup>(2)</sup>        | _                            | -                            |              | —            |              | —                           | —            |              | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOB       |

| 6110                        | TRISB            | 31:16     | _             | _             |                              | —                            |                              | I                            |              | -            |              |                             | -            |              |              |              |              |              | 0000       |

| 0110                        | TRIBD            | 15:0      | TRISB15       | TRISB14       | TRISB13 <sup>(3)</sup>       | TRISB12 <sup>(2)</sup>       | TRISB11 <sup>(2)</sup>       | TRISB10 <sup>(2)</sup>       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             |                              | —                            |                              | I                            |              | -            |              |                             | -            |              |              |              |              |              | 0000       |

| 0120                        | FORTB            | 15:0      | RB15          | RB14          | RB13 <sup>(3)</sup>          | RB12 <sup>(2)</sup>          | RB11 <sup>(2)</sup>          | RB10 <sup>(2)</sup>          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | —             | _             | —                            | —                            | —                            | —                            | —            | —            | —            | _                           | —            | —            | —            | —            | —            | _            | 0000       |

| 0130                        | LAID             | 15:0      | LATB15        | LATB14        | LATB13 <sup>(3)</sup>        | LATB12 <sup>(2)</sup>        | LATB11 <sup>(2)</sup>        | LATB10 <sup>(2)</sup>        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| 01.40                       | 0000             | 31:16     | —             | _             | —                            | —                            | —                            | —                            | —            | —            | —            | _                           | —            | —            | —            | —            | —            | _            | 0000       |

| 6140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13 <sup>(3)</sup>        | ODCB12 <sup>(2)</sup>        | ODCB11 <sup>(2)</sup>        | ODCB10 <sup>(2)</sup>        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 0450                        |                  | 31:16     | —             | _             | _                            |                              | _                            | _                            | _            | —            | _            | _                           | _            | _            | _            | _            | —            | _            | 0000       |

| 6150                        | CNPUB            | 15:0      | CNPUB15       | CNPUB14       | CNPUB13 <sup>(3)</sup>       | CNPUB12(2)                   | CNPUB11 <sup>(2)</sup>       | CNPUB10 <sup>(2)</sup>       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6(2)                   | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 0400                        |                  | 31:16     | —             | _             | _                            |                              | _                            | _                            | _            | —            | _            | _                           | _            | _            | _            | _            | —            | _            | 0000       |

| 6160                        | CNPDB            | 15:0      | CNPDB15       | CNPDB14       | CNPDB13                      | CNPDB12(2)                   | CNPDB11 <sup>(2)</sup>       | CNPDB10 <sup>(2)</sup>       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6(2)                   | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 0470                        |                  | 31:16     | —             | _             | _                            |                              | _                            | _                            | _            | —            | _            | _                           | _            | _            | _            | _            | —            | _            | 0000       |

| 6170                        | CNCONB           | 15:0      | ON            | _             | SIDL                         |                              | _                            | _                            | _            | —            | _            | _                           | —            | _            | _            | _            | —            | _            | 0000       |

| 0400                        |                  | 31:16     | —             | _             | _                            |                              | _                            | _                            | _            | —            | _            | _                           | —            | _            | _            | _            | —            | _            | 0000       |

| 6180                        | CNENB            | 15:0      | CNIEB15       | CNIEB14       | CNIEB13(3)                   | CNIEB11 <sup>(2)</sup>       | CNIEB11(2)                   | CNIEB10(2)                   | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6(2)                   | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | —             | —             | _                            | —                            | _                            | —                            | —            | —            | —            | _                           | —            | _            | —            | _            | _            |              | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 <sup>(3)</sup> | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 <sup>(2)</sup> | CN<br>STATB10 <sup>(2)</sup> | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

Advance Information

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on USB devices.

3: This bit is not available on VBAT devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        |                   | _                 | _                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | —                 | _                 | —                 | TXBUFELM<4:0>     |                   |                   | )>               |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         |                   | _                 | _                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |  |

#### REGISTER 19-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware               |                    |  |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR + SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

#### REGISTER 21-1: **UxMODE: UARTx MODE REGISTER (CONTINUED) IREN:** IrDA<sup>®</sup> Encoder and Decoder Enable bit bit 12 1 = IrDA is enabled 0 = IrDA is disabled bit 11 RTSMD: Mode Selection for UxRTS Pin bit $1 = \overline{\text{UxRTS}}$ pin is in Simplex mode $0 = \overline{\text{UxRTS}}$ pin is in Flow Control mode bit 10 Unimplemented: Read as '0' UEN<1:0>: UARTx Module Enable bits<sup>(1)</sup> bit 9-8 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register 10 = UxTX, UxRX, $\overline{\text{UxCTS}}$ and $\overline{\text{UxRTS}}$ pins are enabled and used 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit 1 = Wake-up enabled 0 = Wake-up disabled LPBACK: UARTx Loopback Mode Select bit bit 6 1 = Loopback mode is enabled 0 = Loopback mode is disabled bit 5 ABAUD: Auto-Baud Enable bit 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion 0 = Baud rate measurement disabled or completed **RXINV:** Receive Polarity Inversion bit bit 4 1 = UxRX Idle state is '0' 0 = UxRX Idle state is '1' bit 3 BRGH: High Baud Rate Enable bit 1 = High-Speed mode – 4x baud clock enabled 0 = Standard Speed mode - 16x baud clock enabled PDSEL<1:0>: Parity and Data Selection bits bit 2-1 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity bit 0 STSEL: Stop Selection bit 1 = 2 Stop bits 0 = 1 Stop bit

Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see 12.3 "Peripheral Pin Select" for more information).

#### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 10 UTXEN: Transmit Enable bit 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1) 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset The event of disabling an enabled transmitter will release the TX pin to the PORT function and Note: reset the transmit buffers to empty. Any pending transmission is aborted and data characters in the transmit buffers are lost. All transmit status flags are cleared and the TRMT bit is set bit 9 UTXBF: Transmit Buffer Full Status bit (read-only) 1 = Transmit buffer is full 0 = Transmit buffer is not full, at least one more character can be written bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer URXISEL<1:0>: Receive Interrupt Mode Selection bit bit 7-6 11 = Reserved10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 = Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only) 1 = Receive buffer has data, at least one more character can be read 0 =Receive buffer is empty

|              |                   | -                    |                   |                   |                      |                   |                  |                      |

|--------------|-------------------|----------------------|-------------------|-------------------|----------------------|-------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 04-04        | U-0               | U-0                  | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0                  |

| 31:24        | _                 | —                    | _                 | _                 | _                    | _                 | _                | _                    |

| 00.40        | U-0               | U-0                  | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0                  |

| 23:16        | _                 | —                    | _                 | _                 | _                    | _                 | _                | _                    |

| 45-0         | R-0               | R/W-0                | R/W-0             | R/W-0             | R/W-0                | U-0               | R/W-0            | R/W-0                |

| 15:8         | BUSY              | IRQM                 | <1:0>             | INCM              | <1:0>                | _                 | MODE             | <1:0>                |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | WAITB             | <1:0> <sup>(1)</sup> |                   | WAITM             | <3:0> <sup>(1)</sup> |                   | WAITE            | <1:0> <sup>(1)</sup> |

#### REGISTER 22-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

#### bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

#### bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 Unimplemented: Read as '0'

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<7:0>)

- 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMA<x:0>, and PMD<7:0>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS1, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1, and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

#### bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- • 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

#### REGISTER 24-4: AD1CHS: ADC INPUT SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | CH0NB             | —                 | _                 |                   |                   | CH0SB<4:0>        |                  |                  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CHONA             |                   | _                 |                   |                   | CH0SA<4:0>        |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | -                 | _                 | —                 | _                 |                   | _                | _                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 |                   |                   | _                 | _                 | _                |                  |  |

#### Legend:

bit 23

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | = Unimplemented bit, read as '0' |  |  |  |  |

|-------------------|------------------|--------------------------|----------------------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown               |  |  |  |  |

bit 31 CH0NB: Negative Input Select bit for Sample B 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VREFL bit 30-29 Unimplemented: Read as '0' bit 28-24 CH0SB<4:0>: Positive Input Select bits for Sample B 11111 = Reserved •

- 10010 = Reserved

10001 = Channel 0 positive input is VDD/2

10000 = Channel 0 positive input is VBAT

01111 = Reserved

01101 = Channel 0 positive input is IVREF<sup>(1)</sup>

01101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

01100 = Channel 0 positive input is AN12<sup>(3)</sup>

.

.

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

CHONA: Negative Input Select bit for Sample A Multiplexer Setting<sup>(1)</sup>

1 = Channel 0 negative input is AN1

0 = Channel 0 negative input is VREFL

- bit 22-21 Unimplemented: Read as '0'

Note 1: See 26.0 "Comparator Voltage Reference (CVREF)" for more information.

- 2: See 28.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | EL<3:0>           |                   | —                      | —                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.0         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          |                   |                   | ITRIM             | l<5:0>              |                   |                   | IRNG                   | <1:0>            |

#### REGISTER 28-1: CTMUCON: CTMU CONTROL REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 30 EDG1POL: Edge 1 Polarity Select bit

- 1 = Edge1 programmed for a positive edge response

- 0 = Edge1 programmed for a negative edge response

- bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

- bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

- 1 = Edge2 has occurred

- 0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 33-42) in 33.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

#### TABLE 33-25: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH         | ARACTERIS | TICS                                                      |                        | (unless   | tandard Operating Conditions: 2.5V to 3.6V<br>unless otherwise stated)<br>operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |   |     |                                     |                                       |  |

|---------------|-----------|-----------------------------------------------------------|------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------|---------------------------------------|--|

| Param.<br>No. | Symbol    | ool Characteristics                                       |                        |           | 1) Min. I                                                                                                                                                                                                   |   |     | Condit                              | ions                                  |  |