Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| roduct Status             | Active                                                                          |

| ore Processor             | MIPS32® M4K™                                                                    |

| ore Size                  | 32-Bit Single-Core                                                              |

| peed                      | 72MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| eripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                           |

| lumber of I/O             | 21                                                                              |

| rogram Memory Size        | 256KB (256K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 64K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                     |

| ata Converters            | A/D 10x10b                                                                      |

| scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| lounting Type             | Surface Mount                                                                   |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| upplier Device Package    | 28-SOIC                                                                         |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256bt-v-so |

## TABLE 7: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITH VBAT

28-PIN QFN (TOP VIEW)(1,2,3.4)

PIC32MX155F128D PIC32MX175F256D

28

1

| Pin# | Full Pin Name                               |

|------|---------------------------------------------|

| 1    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0        |

| 2    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/RB1 |

| 3    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2        |

| 4    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3    |

| 5    | Vss                                         |

| 6    | OSC1/CLKI/RPA2/RA2                          |

| 7    | OSC2/CLKO/RPA3/PMA0/RA3                     |

| 8    | SOSCI/RPB4/RB4 <sup>(5)</sup>               |

| 9    | SOSCO/RPA4/T1CK/CTED9/RA4                   |

| 10   | VDD                                         |

| 11   | PGED3/RPB5/ASDA2/PMD7/RB5                   |

| 12   | PGEC3/RPB6/ASCL2/PMD6/RB6                   |

| 13   | TDI/RPB7/CTED3/PMD5/INT0/RB7                |

| 14   | TCK/RPB8/SCL1/CTED10/PMD4/RB8               |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 16   | Vss                                            |

| 17   | VCAP                                           |

| 18   | PGED1/RPB10/CTED11/PMD2/RB10                   |

| 19   | PGEC1/TMS/RPB11/PMD1/RB11                      |

| 20   | AN12/PMD0/RB12                                 |

| 21   | VBAT                                           |

| 22   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 24   | AVss                                           |

| 25   | AVDD                                           |

| 26   | MCLR                                           |

| 27   | VREF+/AN0/C3INC/RPA0ASDA1//CTED1/PMA1/RA0      |

| 28   | VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1            |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

- 5: This is an input-only pin.

## 7.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupt Controller"** (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

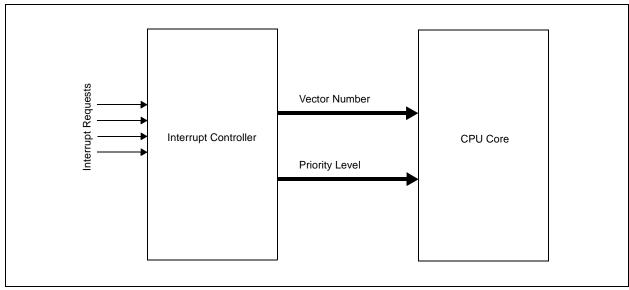

PIC32MX1XX/2XX 28/44-pin XLP Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/44-pin XLP Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- · User-configurable interrupt vector spacing

**Note:** The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/44-pin XLP Family devices.

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                        | _                               | ø         |       |       |       |       |             |       |             | Bits      |      |      |      |                         |             |                |             |        |               |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|-------------|-----------|------|------|------|-------------------------|-------------|----------------|-------------|--------|---------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9        | 24/8      | 23/7 | 22/6 | 21/5 | 20/4                    | 19/3        | 18/2           | 17/1        | 16/0   | All<br>Resets |

| 1100                       | IPC7                            | 31:16     | _     | _     | _     |       | SPI1IP<2:0> |       | SPI1IS      | i<1:0>    |      |      | US   | SBIP<2:0> <sup>(2</sup> | 2)          | USBIS<1:0>(2)  |             | 0000   |               |

| 1100                       | IPC/                            | 15:0      | -     | _     | _     | (     | CMP3IP<2:0> | •     | CMP3IS      | S<1:0>    | _    | _    | _    | CI                      | CMP2IP<2:0> |                | CMP2IS<1:0> |        | 0000          |

| 1110                       | IPC8                            | 31:16     | _     | _     | _     |       | PMPIP<2:0>  |       | PMPIS       | <1:0>     | _    | _    | _    | (                       | CNIP<2:0>   |                | CNIS        | <1:0>  | 0000          |

| 1110                       | IPC8                            | 15:0      | -     | _     | _     |       | I2C1IP<2:0> |       | I2C1IS      | <1:0>     | _    | _    | _    |                         | U1IP<2:0>   | P<2:0> U1IS    |             | <1:0>  | 0000          |

| 1120                       | IPC9                            | 31:16     | -     | _     | _     | (     | CTMUIP<2:0  | >     | CTMUIS<1:0> |           | _    | _    | _    | I2C2IP<2:0>             |             | 2:0> I2C2IS<1: |             | S<1:0> | 0000          |

| 1120                       | IFC9                            | 15:0      | _     | _     | _     |       | U2IP<2:0>   |       | U2IS<       | U2IS<1:0> |      | _    | _    | SPI2IP<2:0>             |             |                | SPI2IS      | S<1:0> | 0000          |

| 1120                       | IPC10                           | 31:16     | _     | _     | _     | 1     | DMA3IP<2:0> |       | DMA3IS<1:0> |           | _    | _    | _    | DMA2IP<2:0>             |             | DMA2I          | S<1:0>      | 0000   |               |

| 1130                       | IPC10                           | 15:0      | -     |       | _     | I     | DMA1IP<2:0> |       | DMA1IS      | S<1:0>    | _    | _    | _    | DI                      | MA0IP<2:0:  | >              | DMA0I       | S<1:0> | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

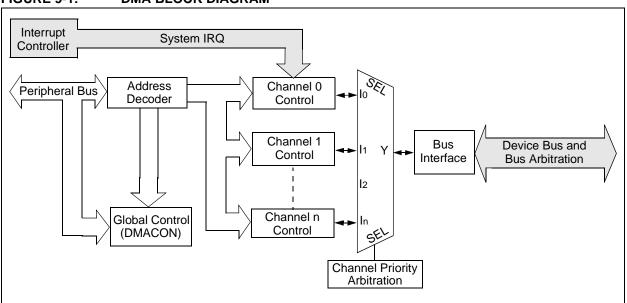

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 31. "Direct Memory Access (DMA) Controller"** (DS60001117), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- · Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| <b>TABLE 9-3</b> : | DMA CHANNELS 0-3 REGISTER MAP ( | (CONTINUED) |

|--------------------|---------------------------------|-------------|

|                    |                                 |             |

| 131-0     131-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SS                          |                                 |           |       |       |       |       |        |       |      | Bi     | ts                   |        |        |          |        |          |         |        |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------|-------|------|--------|----------------------|--------|--------|----------|--------|----------|---------|--------|------------|

| STOP   DCHISSIZ   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7                 | 22/6   | 21/5   | 20/4     | 19/3   | 18/2     | 17/1    | 16/0   | All Resets |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2170                        | DCH18817                        | 31:16     | _     |       | _     |       |        |       | _    | _      | _                    |        |        | _        | _      | _        |         | _      | 0000       |

| State   Chiloral   State   Sta | 3170                        | DCHTSSIZ                        | 15:0      |       |       |       |       |        |       |      | CHSSIZ | <b>'&lt;15:0&gt;</b> |        |        |          |        |          |         | 1      | 0000       |

| 150   CHISPTR   150   CHISPT | 3180                        | DCH1DSI7                        | 31:16     | _     | _     | _     | _     | _      | _     | _    |        | _                    | _      | _      | _        | _      | _        | _       | _      | 0000       |

| 3190   DCH1SPT    15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0100                        | DOITIDOIZ                       | 15:0      |       |       |       |       |        |       |      | CHDSIZ | <b>2</b> <15:0>      |        |        |          |        |          |         |        | 0000       |

| 150   CHSPTR-15:05   CHSPTR-15:05   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   0000   | 3190                        | DCH1SPTR                        |           | _     | _     | _     | _     | _      | _     | _    | _      | _                    | _      | _      | _        | _      | _        | _       | _      | 0000       |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0100                        |                                 |           |       |       |       |       |        |       |      |        |                      |        | 0000   |          |        |          |         |        |            |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31A0                        | DCH1DPTR                        |           | _     | _     | _     | _     | _      | _     | _    |        |                      | _      | _      | _        |        | _        | _       | _      |            |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                                 | _         |       |       |       |       |        |       |      | CHDPTI | R<15:0>              |        |        |          |        |          |         | 1      | _          |

| 3100 DCH1CPTR   3116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31B0                        | DCH1CSIZ                        |           | _     | _     | _     | _     | _      | _     | _    | _      | _                    | _      | _      | _        | _      | _        | _       | _      |            |

| OCH   OCH   15.0   OCH   OCH   15.0   OCH   OC |                             |                                 |           |       |       |       |       |        |       |      | CHCSIZ | Z<15:0>              |        |        |          |        |          |         | 1      | -          |

| 3110   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31C0                        | DCH1CPTR                        |           | _     | _     | _     | _     | _      |       | _    |        |                      | _      | _      | _        |        | _        | _       | _      | _          |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |                                 | -         |       |       |       |       |        |       |      |        |                      |        |        |          |        |          |         |        | _          |

| 31E0   DCH2CON   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31D0                        | DCH1DAT                         | _         |       |       |       |       |        |       |      |        | _                    | _      | _      |          |        | _        | _       | _      |            |

| Signature   Sign |                             |                                 |           |       |       |       |       |        | _     |      |        |                      |        |        | CHPDA    |        |          |         |        | _          |

| 31F0 DCH2ECON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31E0                        | DCH2CON                         |           |       |       |       |       |        |       |      |        |                      |        |        | - CLIAEN |        | - CHEDET | —<br>—  | -      |            |

| Single   DCH2ECON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |                                 |           |       |       |       |       |        |       |      |        | CHEN                 | CHAED  | CHCHN  |          |        | CHEDET   | CHPR    | 1<1:0> | -          |

| October   Octo | 31F0                        | DCH2ECON                        |           | _     |       | _     |       |        |       | _    | _      | CEODOE               | CARORT | DATEN  |          |        |          |         |        | _          |

| DCH2INT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                             |                                 |           |       |       |       | СПЗІК | Q<1:0> |       |      |        |                      |        |        |          |        |          |         | CHEDIE | +          |

| 3210   DCH2SSA   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3200                        | DCH2INT                         |           |       |       |       |       | _      |       | _    |        |                      |        |        |          |        |          |         |        |            |

| Second   S |                             |                                 |           |       |       |       |       |        |       | _    |        | CHODII               | CHOHII | CHDDII | CHDHIII  | CHBCII | Criccii  | CITIAII | CHEKII | -          |

| 3210   DCH2DSA   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3210                        | DCH2SSA                         |           |       |       |       |       |        |       |      | CHSSA  | <31:0>               |        |        |          |        |          |         |        |            |

| 3220   DCH2DSA   15:0     CHDSA<31:0>   0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |                                 |           |       |       |       |       |        |       |      |        |                      |        |        |          |        |          |         |        |            |

| 3230 DCH2SSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3220                        | DCH2DSA                         |           |       |       |       |       |        |       |      | CHDSA  | <31:0>               |        |        |          |        |          |         |        |            |

| 3230 DCH2SSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |                                 |           | _     | _     | _     | _     | _      | _     | _    | _      | _                    | _      | _      | _        |        | _        | _       | _      | _          |

| 3240 DCH2DSIZ 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3230                        | DCH2SSIZ                        |           |       |       |       |       |        |       |      | CHSSIZ | '<15:0>              |        |        |          |        |          |         |        | _          |

| 3240 DCH2DSIZ   15:0   CHDSIZ<15:0>   0000   3250 DCH2SPTR   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             |                                 |           | _     | _     | _     | _     | _      | _     | _    |        |                      | _      | _      | _        |        | _        | _       | _      | _          |

| 3250 DCH2SPTR 31:16 0000 3260 DCH2DPTR 31:16 0000 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3240                        | DCH2DSIZ                        |           |       |       |       |       |        |       |      | CHDSIZ | <b>'</b> <15:0>      |        |        |          |        |          |         |        | -          |

| 3250 DCH2SPTR 15:0 CHSPTR<15:0> 0000 3260 DCH2DPTR 31:16 — — — — — — — — — — — — — — — — — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                                 |           | _     | _     | _     | _     | _      | _     | _    |        | _                    | _      | _      | _        | _      | _        | _       | _      | _          |

| 3260 DCH2DPTR 31:16 0000 15:0 CHDPTR<15:0> CHDPTR<15:0> 0000 3270 DCH2CSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3250                        | DCH2SPTR                        |           |       |       |       |       |        |       |      | CHSPT  | R<15:0>              |        |        |          |        |          |         |        | -          |

| 3260 DCH2DPTR 15:0 CHDPTR<15:0> 0000 3270 DCH2CSIZ 31:16 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | D 01 10 D D ===                 |           | _     | _     | _     | _     | _      | _     | _    |        |                      | _      | _      | _        | _      | _        | _       | _      | _          |

| 3270 DCH2CSIZ 31:16 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3260                        | DCH2DPTR                        |           |       |       |       |       |        |       |      | CHDPTI | R<15:0>              |        |        |          |        |          |         |        | _          |