Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                          |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256d-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-16: JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

|          | Pi                            | in Number         | (1)                    |                         |            |                                                                            |

|----------|-------------------------------|-------------------|------------------------|-------------------------|------------|----------------------------------------------------------------------------|

| Pin Name | n Name 28-pin QFN 28-pin SOIC |                   | 44-pin<br>QFN/<br>TQFP | Pin Buffer<br>Type Type |            | Description                                                                |

|          |                               |                   |                        | Pow                     | er and Gro | ound                                                                       |

| TMO      | 19 <sup>(2)</sup>             | 22 <sup>(2)</sup> | 9(2)                   |                         | ОТ         | ITAO Tantura da antantuin                                                  |

| TMS      | 11(3)                         | 14(3)             | 41(3)                  |                         | ST         | JTAG Test mode select pin                                                  |

| TCK      | 14                            | 17                | 13                     | I                       | ST         | JTAG test clock input pin                                                  |

| TDI      | 13                            | 16                | 35                     | 0                       |            | JTAG test data input pin                                                   |

| TDO      | 15                            | 18                | 32                     | 0                       |            | JTAG test data output pin                                                  |

|          |                               |                   |                        | Progran                 | nming/Deb  | ougging                                                                    |

| DOED4    | 18 <sup>(2)</sup>             | 21 <sup>(2)</sup> | 8(2)                   | 1/0                     | ОТ         | Data I/O pin for Programming/Debugging                                     |

| PGED1    | <sub>3</sub> (3)              | 6 <sup>(3)</sup>  | 23 <sup>(3)</sup>      | I/O                     | ST         | Communication Channel 1                                                    |

| PGEC1    | 19 <sup>(2)</sup>             | 22(2)             | g <b>(2)</b>           |                         | ST         | Clock input pin for Programming/Debugging                                  |

| FGECT    | 4 <sup>(3)</sup>              | 7 <sup>(3)</sup>  | 24 <sup>(3)</sup>      | '                       | 5          | Communication Channel 1                                                    |

| PGED2    | 1                             | 4                 | 21                     | I/O                     | ST         | Data I/O pin for Programming/Debugging Communication Channel 2             |

| PGEC2    | 2                             | 5                 | 22                     | ı                       | ST         | Clock input pin for Programming/Debugging<br>Communication Channel 2       |

| PGED3    | 11 <sup>(2)</sup>             | 14(2)             | 41(2)                  | I/O                     | ST         | Data I/O pin for Programming/Debugging                                     |

| FGEDS    | 27 <sup>(3)</sup>             | 2 <sup>(3)</sup>  | 19 <sup>(3)</sup>      | 1/0                     | 5          | Communication Channel 3                                                    |

| PGEC3    | 12 <sup>(2)</sup>             | 15 <sup>(2)</sup> | 42 <sup>(2)</sup>      | _                       | ST         | Clock input pin for Programming/                                           |

| I GLOS   | 28 <sup>(3)</sup>             | 3(3)              | 20 <sup>(3)</sup>      | '                       | 51         | Debugging Communication Channel 3                                          |

| PGED4    | _                             | _                 | 12                     | I/O                     | ST         | Data I/O pin for Programming/Debugging Communication Channel 4             |

| PGEC4    | _                             | _                 | 13                     | ı                       | ST         | Clock input pin for Programming/<br>Debugging Communication Channel 4      |

| MCLR     | 26                            | 1                 | 18                     | I/P                     | ST         | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select

Analog = Analog input

P = Power I = Input — = N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for General Purpose devices only.

3: Pin number for USB devices only.

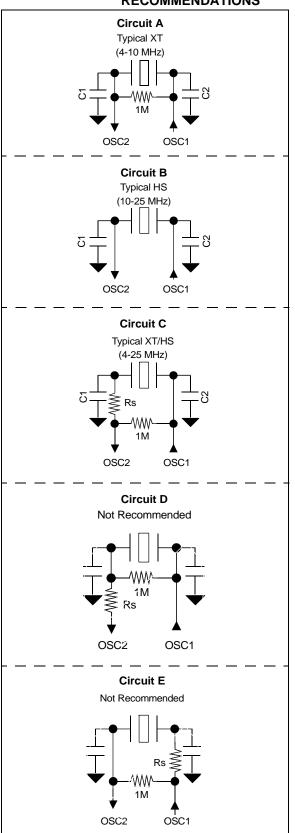

# 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

# EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: CI = C2 = 15 \ pF

Therefore:

CLOAD = \{([CIN + CI]^*[COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 \ pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 \ pF

Rounded to the nearest standard value or 13 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro® Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | NVMDA             | ATA<15:8>         |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# bit 31-0 **NVMDATA<31:0>:** Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

### REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24         | >                 |                  |                  |  |  |  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 13.6         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

REGISTER 8-4: UPLLCON: USB PLL CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |

| 31:24        | -                 | -                 | _                 | _                 | _                 | U                 | PLLODIV<2:0      | )>               |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |

| 23:16        | -                 | -                 | _                 | _                 | _                 | U                 | PLLMULT<2:0      | )>               |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |  |

| 15:8         | -                 | -                 | _                 | _                 | _                 | L                 | UPLLIDIV<2:0>    |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          |                   |                   |                   |                   |                   | _                 |                  |                  |  |

Legend:y = Value set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

```

bit 31-27 Unimplemented: Read as '0'

```

bit 26-24 UPLLODIV<2:0>: USB PLL Output Clock Divider bits

111 = PLL Divide by 16

110 = PLL Divide by 12

101 = PLL Divide by 8

100 = PLL Divide by 6

011 = PLL Divide by 4

010 = PLL Divide by 3

001 = PLL Divide by 2

000 = PLL Divide by 1

bit 23-19 Unimplemented: Read as '0'

bit 18-16 UPLLMULT<2:0>: USB PLL Multiplier bits

111 = Multiply by 24

110 = Multiply by 21

101 = Multiply by 20

100 = Multiply by 19

011 = Multiply by 18

010 = Multiply by 17

001 = Multiply by 16

000 = Multiply by 15

bit 15-11 Unimplemented: Read as '0'

bit 10-8 UPLLIDIV<2:0>: USB PLL Input Clock Divider bits

111 = Divide by 12

110 = Divide by 10

101 = Divide by 6

100 = Divide by 5

011 = Divide by 4

010 = Divide by 3

001 = Divide by 3

000 = Divide by 1

bit 7-0 Unimplemented: Read as '0'

Note 1: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

### REGISTER 11-1: U10TGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | _                 | -                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | -                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | _                | VBUSVDIF         |

**Legend:** WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIF: ID State Change Indicator bit

1 = A change in the ID state was detected0 = No change in the ID state was detected

bit 6 T1MSECIF: 1 Millisecond Timer bit

1 = 1 millisecond timer has expired0 = 1 millisecond timer has not expired

bit 5 LSTATEIF: Line State Stable Indicator bit

1 = USB line state has been stable for 1 ms, but different from last time

0 = USB line state has not been stable for 1 ms

bit 4 ACTVIF: Bus Activity Indicator bit

1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

0 = Activity has not been detected

bit 3 **SESVDIF:** Session Valid Change Indicator bit

1 = VBUS voltage has dropped below the session end level

0 = VBUS voltage has not dropped below the session end level

bit 2 SESENDIF: B-Device VBUS Change Indicator bit

1 = A change on the session end input was detected

0 = No change on the session end input was detected

bit 1 Unimplemented: Read as '0'

bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

1 = A change on the session valid input was detected

0 = No change on the session valid input was detected

### REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | _                 | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | _                 | _                 | 1                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

01001010 = **64-byte** packet

00101010 = 32-byte packet

00011010 = **16-byte** packet

00010010 = 8-byte packet

## REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 |                   | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                 | _                 |                   | -                 | -                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7.0          |                   |                   | В                 | DTPTRL<15:9       | 9>                |                   |                  | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits

This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

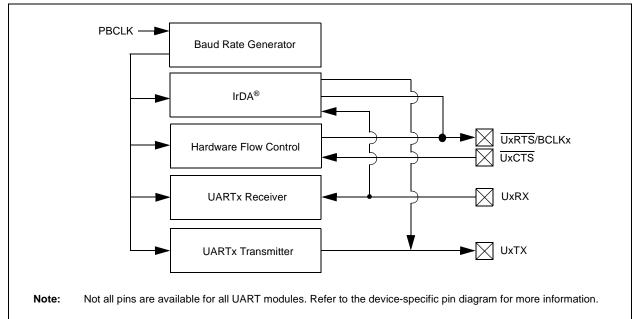

# 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which available from the Documentation > Reference Manual section of the web Microchip PIC32 site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/44-pin XLP Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA®. The UART module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The following are key features of the UART module:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 33.4 bps to 17.5 Mbps at 72 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- · 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

- · Auto-baud support

- · Ability to receive data during Sleep mode

Figure 21-1 illustrates a simplified block diagram of the UART module.

FIGURE 21-1: UART SIMPLIFIED BLOCK DIAGRAM

### REGISTER 23-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0                |

|--------------|---------------------|-------------------|-------------------|-------------------|----------------------------|-------------------|------------------------|---------------------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0                        | U-0               | R/W-0                  | R/W-0                           |

| 31:24        | _                   | _                 | _                 | _                 | _                          | _                 | CAL                    | _<9:8>                          |

| 22,46        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                      | R/W-0             | R/W-0                  | R/W-0                           |

| 23:16        |                     |                   |                   | CAL               | <b>-&lt;7:0&gt;</b>        |                   |                        |                                 |

|              | R/W-0               | U-0               | R/W-0             | U-0               | U-0                        | R/W-0             | R/W-0                  | R/W-0                           |

| 15:8         | ON <sup>(1)</sup>   | -                 | SIDL              | -                 | _                          | RTCCLK            | (SEL<1:0>              | RTC<br>OUTSEL<1> <sup>(2)</sup> |

|              | R/W-0               | R-0               | U-0               | U-0               | R/W-0                      | R-0               | R-0                    | R/W-0                           |

| 7:0          | RTC<br>OUTSEL<0>(2) | RTC<br>CLKON      | _                 |                   | RTC<br>WREN <sup>(3)</sup> | RTC<br>SYNC       | HALFSEC <sup>(4)</sup> | RTCOE                           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25-16 **CAL<9:0>:** Real-Time Clock Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 real-time clock pulses every one minute

•

000000001 = Minimum positive adjustment, adds 1 real-time clock pulse every one minute 0000000000 = No adjustment

1111111111 = Minimum negative adjustment, subtracts 1 real-time clock pulse every one minute

•

1000000000 = Minimum negative adjustment, subtracts 512 real-time clock pulses every one minute

bit 15 **ON**: RTCC On bit<sup>(1)</sup>

1 = RTCC module is enabled

0 = RTCC module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Disables RTCC operation when CPU enters Idle mode

0 = Continue normal operation when CPU enters Idle mode

bit 12-11 Unimplemented: Read as '0'

**Note 1:** The ON bit is only writable when RTCWREN = 1.

**2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

**3:** The RTCWREN bit can be set only when the write sequence is enabled.

4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

### REGISTER 23-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   | HR10              | <1:0>             |                   | HR01              | <3:0>            |                  |

| 22.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        | _                 |                   | MIN10<2:0>        |                   |                   | MIN01             | <3:0>            |                  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | _                 |                   | SEC10<2:0>        |                   |                   | SEC01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**NOTES:**

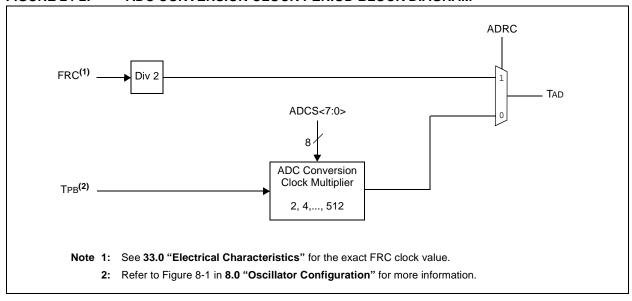

# FIGURE 24-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

TABLE 33-13: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        |                                      | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |        |     |        |                                               |  |

|--------------------|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|--------|-----------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min. Typical <sup>(1)</sup> Max. Units Conditions                                                                                                                                                                                              |        |     |        |                                               |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                |        |     |        |                                               |  |

| D130               | EР     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                         | _      | _   | E/W    | _                                             |  |

| D131               | VPR    | VDD for Read                         | 2.5                                                                                                                                                                                                                                            | _      | 3.6 | V      | _                                             |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.5                                                                                                                                                                                                                                            | _      | 3.6 | V      | _                                             |  |

| D134               | TRETD  | Characteristic Retention             | 10                                                                                                                                                                                                                                             | _      | _   | Year   | Provided no other specifications are violated |  |

| D135               | IDDP   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                              | 10     | -   | mA     | _                                             |  |

|                    | Tww    | Word Write Cycle Time                | _                                                                                                                                                                                                                                              | 471    | _   | es     | See Note 4                                    |  |

| D136               | Trw    | Row Write Cycle Time                 | _                                                                                                                                                                                                                                              | 8020   | _   | Cycles | See Note 2,4                                  |  |

| D137               | TPE    | Page Erase Cycle Time                | _                                                                                                                                                                                                                                              | 240114 | _   | ည      | See Note 4                                    |  |

|                    | TCE    | Chip Erase Cycle Time                | _                                                                                                                                                                                                                                              | 640304 | _   | FRC    | See Note 4                                    |  |

- Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

- 2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to the "PIC32 Flash Programming Specification" (DS60001145) for operating conditions during programming and erase cycles.

- 4: This parameter depends on FRC accuracy (See Table 33-20) and FRC tuning values (See Register 8-2).

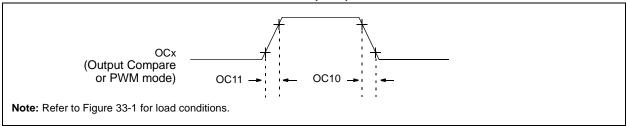

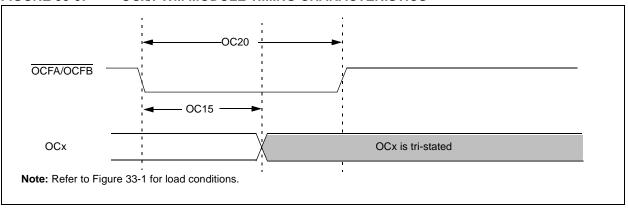

### FIGURE 33-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 33-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                    |  |  |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| OC10               | TCCF   | OCx Output Fall Time           | _                                                                                                                                                                                                                                              | _                      | _    | ns    | See parameter DO32 |  |  |

| OC11               | TCCR   | OCx Output Rise Time           | _                                                                                                                                                                                                                                              | _                      |      | ns    | See parameter DO31 |  |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### FIGURE 33-9: OCx/PWM MODULE TIMING CHARACTERISTICS

### TABLE 33-28: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |     |       |            |  |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                                                            | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | TFD    | Fault Input to PWM I/O Change  | _                                                                                                                                                                                                                                              | _                      | 50  | ns    | _          |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                                                                                                                                                                                                             | _                      | _   | ns    | _          |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE 33-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHA        | RACTERIS |                            | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |            |    |                           |  |

|---------------|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|----|---------------------------|--|

| Param.<br>No. | Symbol   | Charact                    | eristics                                                                                                                                                                                                                                       | Min. | Conditions |    |                           |  |

| IS34          | THD:STO  | Stop Condition             | 100 kHz mode                                                                                                                                                                                                                                   | 4000 | _          | ns | _                         |  |

|               |          | Hold Time                  | 400 kHz mode                                                                                                                                                                                                                                   | 600  | _          | ns |                           |  |

|               |          |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                         | 250  |            | ns |                           |  |

| IS40          | TAA:SCL  | Output Valid from<br>Clock | 100 kHz mode                                                                                                                                                                                                                                   | 0    | 3500       | ns | _                         |  |

|               |          |                            | 400 kHz mode                                                                                                                                                                                                                                   | 0    | 1000       | ns |                           |  |

|               |          |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                            | 0    | 350        | ns |                           |  |

| IS45          | TBF:SDA  | DA Bus Free Time           | 100 kHz mode                                                                                                                                                                                                                                   | 4.7  | _          | μS | The amount of time the bu |  |

|               |          |                            | 400 kHz mode                                                                                                                                                                                                                                   | 1.3  | _          | μS | must be free before a new |  |

|               |          |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                         | 0.5  | _          | μS | transmission can start    |  |

| IS50          | Св       | Bus Capacitive Loading     |                                                                                                                                                                                                                                                | _    | 400        | pF | _                         |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

# DS60001404A-page 343

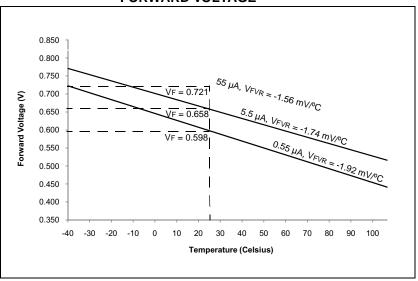

**FIGURE 34-8:** TYPICAL CTMU TEMPERATURE DIODE **FORWARD VOLTAGE**

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

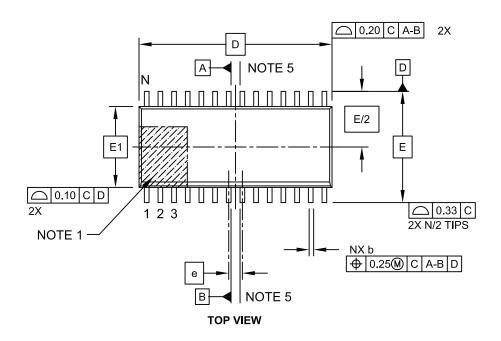

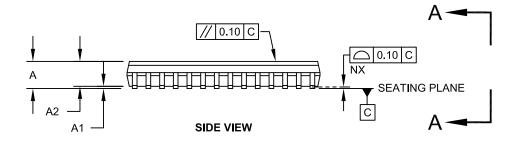

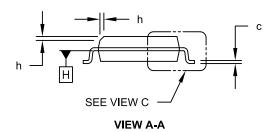

### 35.0 PACKAGING INFORMATION

# 35.1 Package Marking Information

28-Lead SOIC

28-Lead QFN

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Legend: XX...X Customer-specific information Year code (last digit of calendar year) Υ YY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01') NNN Alphanumeric traceability code Pb-free JEDEC designator for Matte Tin (Sn) (e3) This package is Pb-free. The Pb-free JEDEC designator (@3) can be found on the outer packaging for this package. Note: If the full Microchip part number cannot be marked on one line, it is carried over to the next

line, thus limiting the number of available characters for customer-specific information.

# 35.2 Package Details

This section provides the technical details of the packages.

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

# **INDEX**

| A                                                   |         | EJTAG Debug Support                         |      |

|-----------------------------------------------------|---------|---------------------------------------------|------|

| AC Characteristics                                  | 310     | Power Management                            |      |

| 10-Bit Conversion Rate Parameters                   | 332     | CPU Module                                  |      |

| ADC Specifications                                  | 330     | CTMU Pinout I/O Descriptions                |      |

| Analog-to-Digital Conversion Requirements           |         | Customer Change Notification Service        |      |

| EJTAG Timing Requirements                           |         | Customer Notification Service               |      |

| Internal FRC Accuracy                               |         | Customer Support                            | 361  |

| Internal RC Accuracy                                |         | D                                           |      |

| OTG Electrical Specifications                       |         |                                             |      |

| Parallel Master Port Read Requirements              |         | DC and AC Characteristics                   | 0.44 |

| Parallel Master Port Write                          |         | Graphs and Tables                           |      |

| Parallel Master Port Write Requirements             | 338     | DC Characteristics                          |      |

| Parallel Slave Port Requirements                    |         | I/O Pin Input Specifications                |      |

| PLL Clock Timing                                    |         | I/O Pin Output Specifications               |      |

| ADC Pinout I/O Descriptions                         |         | Idle Current (IIDLE)                        |      |

| Analog-to-Digital Converter (ADC)                   |         | Power-Down Current (IPD)                    |      |

| Assembler                                           |         | Program Memory                              |      |

| MPASM Assembler                                     | 294     | Temperature and Voltage Specifications      |      |

| _                                                   |         | Development Support                         |      |

| В                                                   |         | Direct Memory Access (DMA) Controller       | 93   |

| Block Diagrams                                      |         | E                                           |      |

| ADC Module                                          | 233     | Electrical Characteristics                  | 207  |

| Comparator I/O Operating Modes                      | 245     | AC                                          | _    |

| Comparator Voltage Reference                        | 249     |                                             |      |

| Connections for On-Chip Voltage Regulator           | 289     | High/Low-Voltage Detect                     |      |

| Core and Peripheral Modules                         | 19      | Errata                                      | 16   |

| CPU                                                 | 39      | External Clock                              | 246  |

| CTMU Configurations                                 |         | Timer1 Timing Requirements                  |      |

| Time Measurement                                    | 257     | Timer2, 3, 4, 5 Timing Requirements         |      |

| DMA                                                 | 93      | Timing Requirements                         |      |

| I <sup>2</sup> C Circuit                            | 196     | External Interrupts Pinout I/O Descriptions | 22   |

| Input Capture                                       | 179     | F                                           |      |

| Interrupt Controller                                |         | Flash Program Memory                        | 55   |

| JTAG Programming, Debugging and Trace Ports         |         | RTSP Operation                              |      |

| Output Compare Module                               | 183     | K13F Operation                              |      |

| PMP Pinout and Connections to External Devices      | s 211   | Н                                           |      |

| Prefetch Module                                     | 113     | High-Voltage Detect (HVD)                   | 63   |

| Reset System                                        | 61      | riigii-voitage Detect (rivb)                |      |

| RTCC                                                | 223     | I                                           |      |

| SPI Module                                          | 187     | I/O Ports                                   | 147  |

| Timer1                                              | 163     | Parallel I/O (PIO)                          |      |

| Timer2/3/4/5 (16-Bit)                               | 167     | Write/Read Timing                           |      |

| Typical Multiplexed Port Structure                  |         | I2C1 through I2C4 Pinout I/O Descriptions   |      |

| UART                                                |         | IC1 through IC5 Pinout I/O Descriptions     |      |

| WDT and Power-up Timer17                            | 73, 177 | Input Change Notification                   |      |

| Brown-out Reset (BOR)                               |         | Instruction Set                             |      |

| and On-Chip Voltage Regulator                       | 289     | Inter-Integrated Circuit (I <sup>2</sup> C) |      |

|                                                     |         | Internal Voltage Reference Specifications   |      |

| C                                                   |         | Internet Address                            |      |

| C Compilers                                         |         | Interrupt Controller                        |      |

| MPLAB C18                                           | 294     | IRG, Vector and Bit Location                |      |

| Charge Time Measurement Unit (CTMU)                 | 257     |                                             |      |

| Comparator                                          |         | J                                           |      |

| Specifications30                                    | 08, 309 | JTAG, Trace, and Programming/Debugging      |      |

| Comparator 1, 2, and CVREF Pinout I/O Descriptions. | 27      | Pinout I/O Descriptions                     | 32   |

| Comparator Module                                   |         |                                             | 52   |

| Comparator Voltage Reference (CVref                 |         | M                                           |      |

| Configuration Bit                                   |         | Memory Maps                                 |      |

| Configuring Analog Port Pins                        |         | PIC32MX150/250 Devices                      |      |

| CPU                                                 |         | (32 KB RAM, 128 KB Flash)                   | 44   |

| Architecture Overview                               | 40      | PIC32MX170/270                              |      |

| Coprocessor 0 Registers                             | 41      | (64 KB RAM, 256 KB Flash)                   | 45   |

| Core Exception Types                                |         | Memory Organization                         |      |

| • • •                                               |         | , 3                                         |      |

# Worldwide Sales and Service

### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323

Fax: 317-773-8323 Fax: 317-773-5453 Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252

Fax: 86-29-8833-7256

### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444

Fax: 91-80-3090-4123 India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8632

**India - Pune** Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870

Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf** Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611

Fax: 39-0331-466781 **Italy - Venice**

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399

Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

Tel: 44-118-921-5800 Fax: 44-118-921-5820

**UK - Wokingham**

07/14/15