Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| roduct Status             | Active                                                                         |

| ore Processor             | MIPS32® M4K™                                                                   |

| ore Size                  | 32-Bit Single-Core                                                             |

| peed                      | 72MHz                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                          |

| lumber of I/O             | 34                                                                             |

| rogram Memory Size        | 256KB (256K x 8)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 64K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| ata Converters            | A/D 13x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| lounting Type             | Surface Mount                                                                  |

| ackage / Case             | 44-TQFP                                                                        |

| upplier Device Package    | 44-TQFP (10x10)                                                                |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx174f256d-v-pt |

1

#### **Pin Diagrams**

#### TABLE 3: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITH VBAT

28-PIN SOIC (TOP VIEW)<sup>(1,2,3)</sup>

28

SOIC

PIC32MX155F128B PIC32MX175F256B

| Pin # | Full Pin Name                                |

|-------|----------------------------------------------|

| 1     | MCLR                                         |

| 2     | VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0    |

| 3     | VREF-/AN1/RPA1/ASCL1/CTED2/PMRD/RA1          |

| 4     | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0         |

| 5     | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1 |

| 6     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2         |

| 7     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/RB3     |

| 8     | Vss                                          |

| 9     | OSC1/CLKI/RPA2/RA2                           |

| 10    | OSC2/CLKO/RPA3/PMA0/RA3                      |

| 11    | SOSCI/RPB4/RB4 <sup>(4)</sup>                |

| 12    | SOSCO/RPA4/T1CK/CTED9/RA4                    |

| 13    | VDD                                          |

| 14    | PGED3/RPB5/ASDA2/PMD7/RB5                    |

| Pin # | Full Pin Name                                  |

|-------|------------------------------------------------|

| 15    | PGEC3/RPB6/ASCL2/PMD6/RB6                      |

| 16    | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17    | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19    | Vss                                            |

| 20    | VCAP                                           |

| 21    | PGED1/RPB10/CTED11/PMD2/RB10                   |

| 22    | PGEC1/TMS/RPB11/PMD1/RB11                      |

| 23    | AN12/PMD0/RB12                                 |

| 24    | VBAT                                           |

| 25    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 26    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27    | AVss                                           |

| 28    | AVDD                                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

- 4: This is an input-only pin.

#### TABLE 12: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES WITHOUT VBAT

44-PIN QFN AND TQFP (TOP VIEW) $^{(1,2,3,5)}$

PIC32MX154F128D PIC32MX174F256D

1

44

1

| Pin# | Full Pin Name                               |

|------|---------------------------------------------|

| 1    | RPB9/SDA1/CTED4/PMA7/RB9                    |

| 2    | RPC6/PMA1/RC6                               |

| 3    | RPC7/PMCS1/RC7                              |

| 4    | RPC8/PMD5/RC8                               |

| 5    | RPC9/CTED7/PMD6/RC9                         |

| 6    | Vss                                         |

| 7    | VCAP                                        |

| 8    | PGED1/RPB10/CTED11/PMA8/RB10                |

| 9    | PGEC1/TMS/RPB11/PMA9/RB11                   |

| 10   | AN12/PMD0/RB12                              |

| 11   | AN11/RPB13/CTPLS/PMRD/RB13                  |

| 12   | PGED4/PMA10/RA10                            |

| 13   | PGEC4/TCK/CTED8/PMD3/RA7                    |

| 14   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/RB14   |

| 15   | AN9/C3INA/RPB15/SCK2/CTED6/PMA0/RB15        |

| 16   | AVss                                        |

| 17   | AVDD                                        |

| 18   | MCLR                                        |

| 19   | VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/RA0        |

| 20   | VREF-/AN1/RPA1/ASCL1/CTED2/RA1              |

| 21   | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0        |

| 22   | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/RB1 |

| Pin# | Full Pin Name                           |

|------|-----------------------------------------|

| 23   | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2    |

| 24   | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMA2/RB3 |

| 25   | AN6/RPC0/RC0                            |

| 26   | AN7/RPC1/RC1                            |

| 27   | AN8/RPC2/PMWR/RC2                       |

| 28   | VDD                                     |

| 29   | Vss                                     |

| 30   | OSC1/CLKI/RPA2/RA2                      |

| 31   | OSC2/CLKO/RPA3/RA3                      |

| 32   | TDO/RPA8/PMD2/RA8                       |

| 33   | SOSCI/RPB4/CTED11/RB4                   |

| 34   | SOSCO/RPA4/T1CK/RA4                     |

| 35   | TDI/RPA9/PMD1/RA9                       |

| 36   | RPC3/RC3                                |

| 37   | RPC4/PMD4/RC4                           |

| 38   | RPC5/PMD7/RC5                           |

| 39   | Vss                                     |

| 40   | Vod                                     |

| 41   | PGED3/RPB5/ASDA2/PMA3/RB5               |

| 42   | PGEC3/RPB6/ASCL2/PMA6/RB6               |

| 43   | RPB7/CTED3/PMA5/INT0/RB7                |

| 44   | RPB8/SCL1/CTED10/PMA4/RB8               |

Note 1:

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

**NOTES:**

**TABLE 1-11: COMPARATOR 1, COMPARATOR 2, AND COMPARATOR VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS**

|          | Pin Number <sup>(1)</sup> |                |                        |             |                |                                        |

|----------|---------------------------|----------------|------------------------|-------------|----------------|----------------------------------------|

| Pin Name | 28-pin<br>QFN             | 28-pin<br>SOIC | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                            |

|          |                           |                | Co                     | mparate     | or Voltage     | Reference                              |

| VREF-    | 28                        | 3              | 20                     | I           | Analog         | Comparator Voltage Reference (Low)     |

| VREF+    | 27                        | 2              | 19                     | I           | Analog         | Comparator Voltage Reference (High)    |

| CVREFOUT | 22                        | 25             | 14                     | 0           | Analog         | Comparator Voltage Reference Output    |

|          |                           |                |                        | С           | omparator      | 1                                      |

| C1INA    | 4                         | 7              | 24                     | I           | Analog         | Comparator 1 Positive Input            |

| C1INB    | 3                         | 6              | 23                     | I           | Analog         | Comparator 1 Selectable Negative Input |

| C1INC    | 2                         | 5              | 22                     | I           | Analog         |                                        |

| C1IND    | 1                         | 4              | 21                     | I           | Analog         |                                        |

| C1OUT    | PPS                       | PPS            | PPS                    | 0           | _              | Comparator 1 Output                    |

|          |                           |                |                        | С           | omparator      | 2                                      |

| C2INA    | 2                         | 5              | 22                     | I           | Analog         | Comparator 2 Positive Input            |

| C2INB    | 1                         | 4              | 21                     | I           | Analog         | Comparator 2 Selectable Negative Input |

| C2INC    | 4                         | 7              | 24                     | I           | Analog         |                                        |

| C2IND    | 3                         | 6              | 23                     | I           | Analog         |                                        |

| C2OUT    | PPS                       | PPS            | PPS                    | 0           | _              | Comparator 2 Output                    |

|          |                           |                |                        | С           | omparator      | 3                                      |

| C3INA    | 23                        | 26             | 15                     | I           | Analog         | Comparator 3 Positive Input            |

| C3INB    | 22                        | 25             | 14                     | I           | Analog         | Comparator 3 Selectable Negative Input |

| C3INC    | 27                        | 2              | 19                     | ı           | Analog         |                                        |

| C3IND    | 1                         | 4              | 21                     | I           | Analog         |                                        |

| C3OUT    | PPS                       | PPS            | PPS                    | 0           |                | Comparator 3 Output                    |

**Legend:** CMOS = CMOS compatible input or output

TTL = TTL input buffer

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = OutputPPS = Peripheral Pin Select P = Power I=Input --=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

#### REGISTER 8-6: REFOOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRIN            | Л<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | -                 | _                | -                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

111111111 = 511/512 divisor added to RODIV value 111111110 = 510/512 divisor added to RODIV value

•

•

100000000 = 256/512 divisor added to RODIV value

•

•

000000010 = 2/512 divisor added to RODIV value

000000001 = 1/512 divisor added to RODIV value 000000000 = 0 divisor added to RODIV value

bit 22-0 **Unimplemented:** Read as '0'

- **Note 1:** While the ON bit (REFO0CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

- 2: Do not write to this register when the ON bit (REFO0CON<15>) is not equal to the ACTIVE bit (REFO0CON<8>).

- 3: Specified values in this register do not take effect if RODIV<14:0> bits (REFO0CON<30:16>) = 0.

#### REGISTER 9-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 | _                    | _                 | _                | _                |

| 22,46        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 23:16        |                   |                   |                   | CHAIRQ-           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 15.0         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 15:8         |                   |                   |                   | CHSIRQ-           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 7:0          | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |

| 7.0          | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN               |                   |                  | _                |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits(1)

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will initiate a DMA transfer

•

.

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | 1     | _     | _     | _     | _     | _     | _    | _    | I    | _    | _    | _        |        | _      | _       | -      | 0000       |

| 3390                        | OILF9                           | 15:0      | 1     | _     | _     | _     | _     | _     | _    | _    | I    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | -     | _     | _     | _     | _     | _     | _    |      | -    |      | _    | _        |        | _      | _       | _      | 0000       |

| 33A0                        | OTET TO                         | 15:0      | -     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| JJD0                        | O I LI II                       | 15:0      | -     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 3300                        | OTET 12                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 33D0                        | OTET 13                         | 15:0      | -     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53E0                        | U1EP14                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53EU                        | UTEP14                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53F0                        | U1EP15                          | 31:16     | ı     | _     | _     | _     | _     | _     | _    | _    | I    | _    | _    | _        | _      | _      | _       |        | 0000       |

| SSFU                        | UTEPTS                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See 12.2 "CLR, SET and INV Registers" for more information.

- 2: This register does not have associated SET and INV registers.

- 3: This register does not have associated CLR, SET and INV registers.

- 4: Reset value for this bit is undefined.

#### REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | _                 | _                 | _                 | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | _                 | _                 | 1                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

01001010 = **64-byte** packet

00101010 = 32-byte packet

00011010 = **16-byte** packet

00010010 = 8-byte packet

#### REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 |                   | -                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | -                 | _                 |                   | -                 | -                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7.0          |                   |                   | В                 | DTPTRL<15:9       | 9>                |                   |                  | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits

This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

**TABLE 12-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPA0                 | RPA0R    | RPA0R<3:0>  | 0000 = No Connect<br>0001 = U1TX           |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 0010 = <del>U2RTS</del>                    |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = SS1<br>0100 = VBUSON <sup>(4)</sup> |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 0101 = OC1<br>0110 = Reserved              |

| RPC7 <sup>(1)</sup>  | RPC7R    | RPC7R<3:0>  | 0111 = C2OUT                               |

| RPC0 <sup>(1)</sup>  | RPC0R    | RPC0R<3:0>  | 1000 = Reserved                            |

| RPC5 <sup>(1)</sup>  | RPC5R    | RPC5R<3:0>  | 1111 = Reserved                            |

| RPA1                 | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                          |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                |

| RPB11 <sup>(2)</sup> | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                  |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                            |

| RPA8 <sup>(1)</sup>  | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                               |

| RPC8 <sup>(1)</sup>  | RPC8R    | RPC8R<3:0>  | •                                          |

| RPA9 <sup>(1)</sup>  | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                            |

| RPA2                 | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                          |

| RPB6 <sup>(2)</sup>  | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved         |

| RPB13 <sup>(3)</sup> | RPB13R   | RPB13R<3:0> | 0011 = SDO1<br>0100 = SDO2                 |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 0101 = OC4<br>0110 = OC5                   |

| RPC6 <sup>(1)</sup>  | RPC6R    | RPC6R<3:0>  | 0111 = REFCLKO<br>1000 = Reserved          |

| RPC1 <sup>(1)</sup>  | RPC1R    | RPC1R<3:0>  | • • • • • • • • • • • • • • • • • • •      |

| RPC3 <sup>(1)</sup>  | RPC3R    | RPC3R<3:0>  | •<br>1111 = Reserved                       |

| RPA3                 | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                          |

| RPB14                | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0011 = Reserved<br>0100 = SS2              |

| RPB10 <sup>(2)</sup> | RPB10R   | RPB10R<3:0> | 0101 = OC3                                 |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT            |

| RPC9 <sup>(1)</sup>  | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                            |

| RPC2 <sup>(1)</sup>  | RPC2R    | RPC2R<3:0>  | <b>-</b>  -                                |

| RPC4 <sup>(1)</sup>  | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                            |

Note 1: This pin is only available on 44-pin devices.

<sup>2:</sup> This pin is not available on USB devices.

<sup>3:</sup> This pin is not available on VBAT devices.

<sup>4:</sup> This pin is only available on USB devices.

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized

0 = External clock input is not synchronized

When TCS = 0:

This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit

1 = External clock is defined by the TECS<1:0> bits

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### TXCON: TYPE B TIMER CONTROL REGISTER REGISTER 14-1:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | _                    | _                 | -                   | -                 | 1                  | _                 | _                  | _                |

| 22,46        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | _                    | _                 | -                   | -                 | _                  | -                 | _                  | _                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | -                  | _                 | _                  | _                |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

Legend:

W = Writable bit R = Readable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

ON: Timer On bit(1,3) bit 15

> 1 = Module is enabled 0 = Module is disabled

bit 14 Unimplemented: Read as '0' bit 13

**SIDL:** Stop in Idle Mode bit<sup>(4)</sup>

1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

TCKPS<2:0>: Timer Input Clock Prescale Select bits(3) bit 6-4

111 = 1:256 prescale value

110 = 1:64 prescale value

101 = 1:32 prescale value

100 = 1:16 prescale value

011 = 1:8 prescale value

010 = 1:4 prescale value

001 = 1:2 prescale value

000 = 1:1 prescale value

- Note 1: When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- 3: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### REGISTER 20-1: I2CXCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | U-0<br>—          | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } I^2\text{C module}$ ; all  $I^2\text{C pins}$  are controlled by PORT functions

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- Note 1: When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 22-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 7-6 **CSF<1:0>:** Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 functions as Chip Select

- 01 = PMCS1 functions as PMA<14>

- 00 = PMCS1 functions as PMA<14>

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$

- bit 4 Unimplemented: Read as '0'

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = Active-low (\overline{PMCS1})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

#### For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

#### For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = \text{Read Strobe active-low } (\overline{PMRD})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- $0 = \text{Read/write strobe active-low } (\overline{PMRD/PMWR})$

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

# REGISTER 23-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER (CONTINUED)

bit 10-9 RTCCLKSEL<1:0>: RTCC Clock Select bits

When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

- 11 = Reserved

- 10 = Reserved

- 01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)

- 00 = RTCC uses the internal 32 kHz oscillator (LPRC)

- bit 8-7 RTCOUTSEL<1:0>: RTCC Output Data Select bits<sup>(2)</sup>

- 11 = Reserved

- 10 = RTCC Clock is presented on the RTCC pin

- 01 = Seconds Clock is presented on the RTCC pin

- 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered

- bit 6 RTCCLKON: RTCC Clock Enable Status bit

- 1 = RTCC Clock is actively running

- 0 = RTCC Clock is not running

- bit 5-4 Unimplemented: Read as '0'

- bit 3 **RTCWREN:** Real-Time Clock Value Registers Write Enable bit<sup>(3)</sup>

- 1 = Real-Time Clock Value registers can be written to by the user

- 0 = Real-Time Clock Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit

- 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = Real-time clock value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(4)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC output is enabled

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

#### REGISTER 25-1: CMXCON: COMPARATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                   | _                 | _                 |                   | _                | _                |

| 22.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                   | _                 | _                 |                   | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | _                 | _                 | _                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | 1                   | CREF              | _                 | I                 | CCH              | <1:0>            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

1 = Module is enabled. Setting this bit does not affect the other bits in this register

0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

bit 14 COE: Comparator Output Enable bit

1 = Comparator output is driven on the output CxOUT pin

0 = Comparator output is not driven on the output CxOUT pin

bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

1 = Output is inverted

0 = Output is not inverted

bit 12-9 Unimplemented: Read as '0'

bit 8 **COUT:** Comparator Output bit

1 = Output of the Comparator is a '1'

0 = Output of the Comparator is a '0'

bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

00 = Comparator interrupt generation is disabled

bit 5 Unimplemented: Read as '0'

bit 4 CREF: Comparator Positive Input Configure bit

1 = Comparator non-inverting input is connected to the internal CVREF

0 = Comparator non-inverting input is connected to the CxINA pin

bit 3-2 Unimplemented: Read as '0'

bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

11 = Comparator inverting input is connected to the IVREF

10 = Comparator inverting input is connected to the CxIND pin

01 = Comparator inverting input is connected to the CxINC pin

00 = Comparator inverting input is connected to the CxINB pin

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

#### REGISTER 30-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

```

11111111 = Disabled

111111110 = 0xBD00_0FFF

111111101 = 0xBD00_1FFF

111111100 = 0xBD00_2FFF

11111011 = 0xBD00_3FFF

111111010 = 0xBD00_4FFF

11111001 = 0xBD00_5FFF

111111000 = 0xBD00_6FFF

11110111 = 0xBD00_7FFF

11110110 = 0xBD00_8FFF

11110101 = 0xBD00_9FFF

11110100 = 0xBD00_AFFF

11110011 = 0xBD00_BFFF

11110010 = 0xBD00_CFFF

11110001 = 0xBD00_DFFF

11110000 = 0xBD00_EFFF

11101111 = 0xBD00_FFFF

10111111 = 0xBD03 FFFF

10111110 = Reserved

00000000 = Reserved

```

- bit 11-5 Reserved: Write '1'

- bit 4-3 ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits<sup>(2)</sup>

- 11 = PGEC1/PGED1 pair is used

- 10 = PGEC2/PGED2 pair is used

- 01 = PGEC3/PGED3 pair is used

- 00 = PGEC4/PGED4 pair is used(2)

- bit 2 **JTAGEN:** JTAG Enable bit<sup>(1)</sup>

- 1 = JTAG is enabled

- 0 = JTAG is disabled

- bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 1x = Debugger is disabled

- 0x =Debugger is enabled

- **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

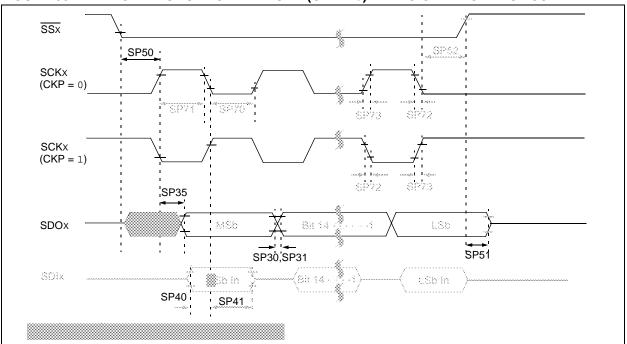

FIGURE 33-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 33-31: SPIx MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS             | TICS                                            | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature- $40^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C for Industrial $-40^{\circ}$ C $\leq$ TA $\leq$ +105 $^{\circ}$ C for V-temp |                     |      |       |                    |

|---------------|-----------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                  | Min.                                                                                                                                                                                                                       | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                    | Tsck/2                                                                                                                                                                                                                     | _                   | _    | ns    | _                  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                   | Tsck/2                                                                                                                                                                                                                     | _                   | _    | ns    | _                  |

| SP72          | TscF                  | SCKx Input Fall Time                            | _                                                                                                                                                                                                                          | _                   | 1    | ns    | See parameter DO32 |

| SP73          | TscR                  | SCKx Input Rise Time                            |                                                                                                                                                                                                                            | _                   |      | ns    | See parameter DO31 |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)             | _                                                                                                                                                                                                                          | _                   |      | ns    | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)             | _                                                                                                                                                                                                                          | _                   |      | ns    | See parameter DO31 |

| SP35          | TscH2DoV,             | SDOx Data Output Valid after                    |                                                                                                                                                                                                                            |                     | 15   | ns    | VDD > 2.7V         |

|               | TscL2doV              | SCKx Edge                                       | _                                                                                                                                                                                                                          | _                   | 20   | ns    | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge      | 10                                                                                                                                                                                                                         |                     |      | ns    | _                  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge       | 10                                                                                                                                                                                                                         | _                   | _    | ns    | _                  |

| SP50          | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx Input                   | 175                                                                                                                                                                                                                        | _                   | _    | ns    | _                  |

| SP51          | TssH2DoZ              | SSx ↑ to SDOx Output<br>High-Impedance (Note 3) | 5                                                                                                                                                                                                                          | _                   | 25   | ns    | _                  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                             | Tsck + 20                                                                                                                                                                                                                  | _                   | _    | ns    | _                  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

**TABLE 33-35: ADC MODULE SPECIFICATIONS**

|               | AC CHAR    | RACTERISTICS                                         | Standard Operating Conditions: 2.5V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |             |                                  |          |                                                                                               |  |  |

|---------------|------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                                                                                                                                                                                           | Typical     | Max.                             | Units    | Conditions                                                                                    |  |  |

| Device        | Supply     |                                                      |                                                                                                                                                                                                                                                |             |                                  |          |                                                                                               |  |  |

| AD01          | AVDD       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                                                                                                                                                                              |             | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                             |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                                                                                                                                                                            |             | AVDD                             | V        | (Note 1)                                                                                      |  |  |

| Referen       | ce Inputs  |                                                      |                                                                                                                                                                                                                                                |             |                                  |          |                                                                                               |  |  |

| AD05<br>AD05a | VREFH      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                                                                                                                                                                              | 1 1         | AVDD<br>3.6                      | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                             |  |  |

| AD06          | VREFL      | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                           |             | VREFH - 2.0                      | V        | (Note 1)                                                                                      |  |  |

| AD07          | VREF       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                                                                                                                                                                            | 1           | AVDD                             | V        | (Note 3)                                                                                      |  |  |

| AD08<br>AD08a | IREF       | Current Drain                                        | _                                                                                                                                                                                                                                              | 250<br>—    | 400<br>3                         | μA<br>μA | ADC operating<br>ADC off                                                                      |  |  |

| Analog        | Input      |                                                      |                                                                                                                                                                                                                                                |             | •                                |          |                                                                                               |  |  |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                                                                                                                                                                                                                                          | _           | VREFH                            | V        | _                                                                                             |  |  |

| AD13          | VINL       | Absolute VINL Input Voltage                          | AVss - 0.3                                                                                                                                                                                                                                     | _           | AVDD/2                           | V        | _                                                                                             |  |  |

| AD14          | VIN        | Absolute Input Voltage                               | AVss - 0.3                                                                                                                                                                                                                                     | _           | AVDD + 0.3                       | V        | _                                                                                             |  |  |

| AD15          | _          | Leakage Current                                      | _                                                                                                                                                                                                                                              | ±0.001      | ±0.610                           | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3.3V$<br>Source Impedance = $10 \text{ k}\Omega$ |  |  |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source |                                                                                                                                                                                                                                                | l           | 5k                               | Ω        | (Note 1)                                                                                      |  |  |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                                                                                                                                                                                                                                   | REF-        |                                  |          |                                                                                               |  |  |

| AD20c         | Nr         | Resolution                                           |                                                                                                                                                                                                                                                | 10 data bit | s                                | bits     | _                                                                                             |  |  |

| AD21c         | INL        | Integral Non-linearity                               | > -1                                                                                                                                                                                                                                           |             | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                                                                                                                                                                                                                                           | _           | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                  |  |  |

| AD23c         | GERR       | Gain Error                                           | > -1                                                                                                                                                                                                                                           | _           | < 1                              | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |  |  |

| AD24c         | EOFF       | Offset Error                                         | > -1                                                                                                                                                                                                                                           | _           | < 1                              | Lsb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                              |  |  |

| AD25c         | _          | Monotonicity                                         | _                                                                                                                                                                                                                                              | _           | _                                | _        | Guaranteed                                                                                    |  |  |

- Note 1: These parameters are not characterized or tested in manufacturing.

- 2: With no missing codes.

- **3:** These parameters are characterized, but not tested in manufacturing.

- 4: Characterized with a 1 kHz sine wave.

- **5:** The ADC module is functional at VBORMIN < VDD < 2.0V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

**TABLE 33-36: 10-BIT CONVERSION RATE PARAMETERS**

| AC CHARA                          | S <sup>(2)</sup> | (unless o             | therwise st | Conditions: 2.5V to 3.6V tated) e $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |                            |

|-----------------------------------|------------------|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ADC Speed                         | TAD Min.         | Sampling<br>Time Min. | Rs Max.     | VDD                                                                                                                                                                                      | ADC Channels Configuration |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns            | 132 ns                | 500Ω        | 3.0V to<br>3.6V                                                                                                                                                                          | ANX CHX ADC                |

| Up to 400 ksps                    | 200 ns           | 200 ns                | 5.0 kΩ      | 2.0V to<br>3.6V                                                                                                                                                                          | ANX SHA ADC  ANX OF VREF-  |

- **Note 1:** External VREF+ pins must be used for correct operation.

- 2: These parameters are characterized, but not tested in manufacturing.

- **3:** The ADC module is functional at VBORMIN < VDD < 2.0V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

**NOTES:**