Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Active                                                                         |

|                          |                                                                                |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 72MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| eripherals               | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| umber of I/O             | 17                                                                             |

| rogram Memory Size       | 128KB (128K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| AM Size                  | 32K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| ta Converters            | A/D 9x10b                                                                      |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| pplier Device Package    | 28-SOIC                                                                        |

| ırchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx254f128b-i-so |

TABLE 1: PIC32MX1XX 28/44-PIN XLP (GENERAL PURPOSE) FAMILY FEATURES

|                 |      |                                    |                  | Re              | mappab                                         | le Per | iphera              | als                                |                    |                    |     | <del>©</del>                             |      | els)                         |      |          |      |      |              |

|-----------------|------|------------------------------------|------------------|-----------------|------------------------------------------------|--------|---------------------|------------------------------------|--------------------|--------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|------|--------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/<br>Compare/PWM | UART   | SPIN <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | I <sup>2</sup> Стм | dWd | DMA Channels<br>(Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | suid O/I | JTAG | VBAT | Packages     |

| PIC32MX154F128B | 28   |                                    |                  | 20              |                                                |        |                     |                                    |                    |                    |     |                                          |      | 10                           |      | 21       |      | Ν    | SOIC,<br>QFN |

| PIC32MX154F128D | 44   | 400.40                             | 20               | 30              | F /F /F /F                                     |        |                     | _                                  |                    |                    | Y   | 4/0                                      | V    | 13                           | Υ    | 35       | Υ    | Ν    | TQFP,<br>QFN |

| PIC32MX155F128B | 28   | 128+12                             | 32               | 19              | 5/5/5/5                                        | 2      | 2                   | 5                                  | 3                  | 2                  | Y   | 4/2                                      | Y    | 9                            | Y    | 20       | Y    | Υ    | SOIC,<br>QFN |

| PIC32MX155F128D | 44   |                                    |                  | 29              |                                                |        |                     |                                    |                    |                    |     |                                          |      | 12                           |      | 35       |      | Υ    | TQFP,<br>QFN |

| PIC32MX174F256B | 28   |                                    |                  | 20              |                                                |        |                     |                                    |                    |                    |     |                                          |      | 10                           |      | 21       |      | N    | SOIC,<br>QFN |

| PIC32MX174F256D | 44   | 256+12                             | 64               | 30              | 5/5/5/5                                        | 2      | 2                   | 5                                  | 3                  | 2                  | Υ   | 4/2                                      | Y    | 13                           | Υ    | 35       | Υ    | N    | TQFP,<br>QFN |

| PIC32MX175F256B | 28   | 200+12                             | 04               | 19              | 0/0/0/0                                        |        |                     | 5                                  | 3                  |                    | r   | 4/2                                      | r    | 9                            | ſ    | 20       | 1    | Υ    | SOIC,<br>QFN |

| PIC32MX175F256D | 44   |                                    |                  | 29              |                                                |        |                     |                                    |                    |                    |     |                                          |      | 12                           |      | 35       |      | Υ    | TQFP,<br>QFN |

Note 1: This device features 12 KB of Boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

TABLE 2: PIC32MX2XX 28/44-PIN XLP (USB) FAMILY FEATURES

|                 |      |                                    |                  | Re              | mappabl                                        | e Per | ipher                | als                                |                    |                     |                    |                                       | <del>©</del>                             |       | els)                         |      |          |      |      |              |

|-----------------|------|------------------------------------|------------------|-----------------|------------------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|--------------------|---------------------------------------|------------------------------------------|-------|------------------------------|------|----------|------|------|--------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/<br>Compare/PWM | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> Стм | PMP                                   | DMA Channels<br>(Programmable/Dedicated) | СТМО  | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | VBAT | Packages     |

| PIC32MX254F128B | 28   |                                    |                  | 17              |                                                |       |                      |                                    |                    |                     |                    |                                       |                                          |       | 9                            |      | 17       |      | N    | SOIC,<br>QFN |

| PIC32MX254F128D | 44   | 400 40                             |                  | 29              | - /- /- /-                                     |       |                      | _                                  |                    | .,                  |                    | Y                                     | 4/0                                      |       | 13                           | .,   | 35       | ,,   | Ν    | TQFP,<br>QFN |

| PIC32MX255F128B | 28   | 128+12                             | 32               | 16              | 5/5/5/5                                        | 2     | 2                    | 5                                  | 3                  | Y                   | 2                  | Y                                     | 4/2                                      | Υ     | 8                            | Y    | 16       | Υ    | Υ    | SOIC,<br>QFN |

| PIC32MX255F128D | 44   |                                    |                  | 28              |                                                |       |                      |                                    |                    |                     |                    |                                       |                                          |       | 12                           |      | 35       | •    | Υ    | TQFP,<br>QFN |

| PIC32MX274F256B | 28   |                                    |                  | 17              |                                                |       |                      |                                    |                    |                     |                    |                                       |                                          |       | 9                            |      | 17       |      | N    | SOIC,<br>QFN |

| PIC32MX274F256D | 44   | 050.40                             | 0.4              | 29              | E/E/E                                          |       |                      | _                                  |                    | V                   | 0                  | , , , , , , , , , , , , , , , , , , , | 4/0                                      | \ \ \ | 13                           | V    | 35       | ,    | Ν    | TQFP,<br>QFN |

| PIC32MX275F256B | 28   | 256+12                             | 64               | 16              | 5/5/5                                          | 2     | 2                    | 5                                  | 3                  | Y                   | 2                  | Y                                     | 4/2                                      | Υ     | 8                            | Υ    | 16       | Y    | Υ    | SOIC,<br>QFN |

| PIC32MX275F256D | 44   |                                    |                  | 28              |                                                |       |                      |                                    |                    |                     |                    |                                       |                                          |       | 12                           |      | 35       | ,    | Υ    | TQFP,<br>QFN |

Note 1: This device features 12 KB of Boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**TABLE 1-4:** OC1 THROUGH OC5 PINOUT I/O DESCRIPTIONS

|          | P             | in Number      | (1)                    |             |                |                              |

|----------|---------------|----------------|------------------------|-------------|----------------|------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SOIC | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                  |

|          |               |                |                        | Ou          | tput Comp      | are                          |

| OC1      | PPS           | PPS            | PPS                    | 0           | _              | Output Compare Output 1-5    |

| OC2      | PPS           | PPS            | PPS                    | 0           | _              |                              |

| OC3      | PPS           | PPS            | PPS                    | 0           | _              |                              |

| OC4      | PPS           | PPS            | PPS                    | 0           | _              |                              |

| OC5      | PPS           | PPS            | PPS                    | 0           | _              |                              |

| OCFA     | PPS           | PPS            | PPS                    | I           | ST             | Output Compare Fault A Input |

| OCFB     | PPS           | PPS            | PPS                    | I           | ST             | Output Compare Fault B Input |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output

P = Power

TTL = TTL input buffer

PPS = Peripheral Pin Select

I = Input--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**EXTERNAL INTERRUPTS PINOUT I/O DESCRIPTIONS TABLE 1-5:**

|          | Pi            | in Number      | (1)                    |             |                |                        |

|----------|---------------|----------------|------------------------|-------------|----------------|------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SOIC | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description            |

|          |               |                |                        | Exte        | rnal Interr    | upts                   |

| INT0     | 13            | 16             | 43                     | I           | ST             | External Interrupt 0-4 |

| INT1     | PPS           | PPS            | PPS                    | I           | ST             |                        |

| INT2     | PPS           | PPS            | PPS                    | I           | ST             |                        |

| INT3     | PPS           | PPS            | PPS                    | I           | ST             |                        |

| INT4     | PPS           | PPS            | PPS                    | I           | ST             |                        |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input

P = Power

O = Output

PPS = Peripheral Pin Select

I = Input--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

TABLE 1-12: PARALLEL MASTER PORT PINOUT I/O DESCRIPTIONS

| IABLE 1-1 |                                          | in Number <sup>(</sup>                 |                                        |             |                | DESCRIPTIONS                                                                              |

|-----------|------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|-------------------------------------------------------------------------------------------|

| Pin Name  | 28-pin<br>QFN                            | 28-pin<br>SOIC                         | 44-pin<br>QFN/<br>TQFP                 | Pin<br>Type | Buffer<br>Type | Description                                                                               |

|           |                                          |                                        |                                        | Para        | llel Master    | Port                                                                                      |

| PMA0      | 7                                        | 10                                     | 15                                     | I/O         | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |

| PMA1      | 27 <sup>(2)</sup><br>22 <sup>(3)</sup>   | 2 <sup>(2)</sup><br>25 <sup>(3)</sup>  | 2                                      | I/O         | TTL/ST         | Parallel Master Port Address bit 1 Input (Buffered Slave modes) and Output (Master modes) |

| PMA2      | _                                        | _                                      | 24                                     | 0           | _              | Parallel Master Port Address (Demultiplexed Master                                        |

| PMA3      | _                                        | _                                      | 41 <sup>(2)</sup>                      | 0           | _              | modes)                                                                                    |

| PMA4      | _                                        | _                                      | 44                                     | 0           | _              |                                                                                           |

| PMA5      | _                                        | _                                      | 43                                     | 0           | _              |                                                                                           |

| PMA6      | _                                        | _                                      | 42 <sup>(2)</sup><br>20 <sup>(3)</sup> | 0           | _              |                                                                                           |

| PMA7      | _                                        | _                                      | 1                                      | 0           | _              |                                                                                           |

| PMA8      | _                                        | _                                      | 8 <sup>(2)</sup><br>23 <sup>(3)</sup>  | 0           | _              |                                                                                           |

| PMA9      | _                                        | _                                      | 9 <sup>(2)</sup><br>22 <sup>(3)</sup>  | 0           | _              |                                                                                           |

| PMA10     | _                                        | _                                      | 12 <sup>(2)</sup><br>21 <sup>(3)</sup> | 0           | _              |                                                                                           |

| PMCS1     | 23                                       | 26                                     | 3                                      | 0           | _              | Parallel Master Port Chip Select 1 Strobe                                                 |

| PMD0      | 20 <sup>(2)</sup>                        | 23 <sup>(2)</sup>                      | 10 <sup>(2)</sup>                      | I/O         | TTL/ST         | Parallel Master Port Data (Demultiplexed Master                                           |

|           | 1 <sup>(3)</sup>                         | 4(3)                                   | 12 <sup>(3)</sup>                      | 1/0         | 1112/01        | mode) or Address/Data (Multiplexed Master modes)                                          |

| PMD1      | 19 <sup>(2)</sup><br>2 <sup>(3)</sup>    | 22 <sup>(2)</sup><br>5 <sup>(3)</sup>  | 35                                     | I/O         | TTL/ST         |                                                                                           |

| PMD2      | 18 <sup>(2)</sup>                        | 21 <sup>(2)</sup>                      | 32                                     | I/O         | TTL/ST         |                                                                                           |

|           | 3(3)                                     | 6(3)                                   | 52                                     | 1/0         | 111/31         |                                                                                           |

| PMD3      | 15                                       | 18                                     | 13                                     | I/O         | TTL/ST         |                                                                                           |

| PMD4      | 14                                       | 17                                     | 37                                     | I/O         | TTL/ST         |                                                                                           |

| PMD5      | 13                                       | 16                                     | 4                                      | I/O         | TTL/ST         |                                                                                           |

| PMD6      | 12 <sup>(2)</sup>                        | 15 <sup>(2)</sup>                      | 5                                      | I/O         | TTL/ST         |                                                                                           |

|           | 28 <sup>(3)</sup>                        | 3(3)                                   |                                        |             |                |                                                                                           |

| PMD7      | 11 <sup>(2)</sup>                        | 14 <sup>(2)</sup>                      | 38                                     | I/O         | TTL/ST         |                                                                                           |

| DMDD      | 27 <sup>(3)</sup>                        | 2 <sup>(3)</sup>                       |                                        |             |                | D. H.IM. A. D. AD. ACC. A                                                                 |

| PMRD      | 21 <sup>(2,5)</sup>                      | 24 <sup>(2,5)</sup>                    | 11 <sup>(4)</sup>                      | 0           | _              | Parallel Master Port Read Strobe                                                          |

| DMANACO   | 11 <sup>(3,5)</sup><br>22 <sup>(2)</sup> | 14 <sup>(3)</sup><br>25 <sup>(2)</sup> | 36 <sup>(5)</sup>                      |             |                | Parallel Master Port Write Strobe                                                         |

| PMWR      | 4(3)                                     | 7 <sup>(3)</sup>                       | 27                                     | 0           | _              | Parallel Master Port Write Strode                                                         |

|           | 41-7                                     | '`'                                    |                                        |             | ĺ              |                                                                                           |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

O = Output

P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

Analog = Analog input

-=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

- 2: Pin number for General Purpose devices only.

- 3: Pin number for USB devices only.

- **4:** Pin number for devices with VBAT only.

- 5: Pin number for devices without VBAT only.

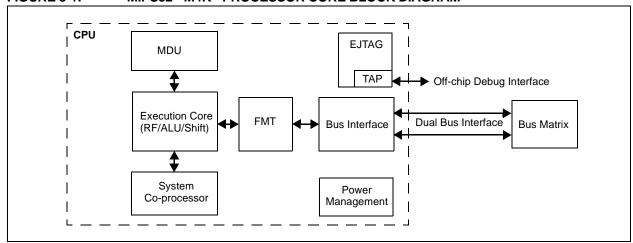

### 3.0 CPU

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX1XX/2XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the destinations.

### 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple dual bus interface

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

### FIGURE 3-1: MIPS32® M4K® PROCESSOR CORE BLOCK DIAGRAM

### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 |                   |                   |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits

This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | -                    |                       | _                      | -                 | -                | _                |

| 22,46        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                    |                       | _                      | -                 | -                | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | 1                 | 1                    | 1                     |                        | NVMOF             | P<3:0>           |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit

This bit is writable when WREN = 1 and the unlock sequence is followed.

1 = Initiate a Flash operation. Hardware clears this bit when the operation completes

0 = Flash operation is complete or inactive

bit 14 WREN: Write Enable bit

This is the only bit in this register reset by a device Reset.

1 = Enable writes to WR bit and enables HLVD circuit

0 = Disable writes to WR bit and disables HLVD circuit

bit 13 **WRERR:** Write Error bit<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11 LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set and cleared by the hardware.

1 = Low-voltage event is active

0 = Low-voltage event is not active

bit 10-4 Unimplemented: Read as '0'

bit 3-0 **NVMOP<3:0>:** NVM Operation bits

These bits are writable when WREN = 0.

1111 = Reserved

•

.

0111 = Reserved

0110 = No operation

0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected

0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

0010 = No operation

0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected

0000 = No operation

Note 1: This bit is cleared by setting NVMOP == 'b0000, and initiating a Flash operation (i.e., WR).

### 6.1 Reset Control Registers

### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                 | 0         |       | Bits  |       |       |         |          |      |      |           |      |      |      | so.   |      |                      |                     |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|----------|------|------|-----------|------|------|------|-------|------|----------------------|---------------------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10    | 25/9 | 24/8 | 23/7      | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1                 | 16/0                | All Resets |

| F040                        | RCON                            | 31:16     | _     | _     | _     | _     | BCFGERR | BCFGFAIL | _    | _    | _         | _    | _    |      | _     | _    | VBPOR <sup>(3)</sup> | VBAT <sup>(3)</sup> | C802       |

| F040                        | RCON                            | 15:0      | _     |       | _     | _     | _       | DPSLP    | CMR  | _    | EXTR      | SWR  | -    | WDTO | SLEEP | IDLE | BOR                  | POR                 | 0003       |

| EOEO                        | RSWRST                          | 31:16     | _     | 1     | 1     | _     |         | _        | _    | 1    |           | _    | 1    | I    | 1     | I    | -                    | _                   | 0000       |

| 1 030                       | KOWKOI                          | 15:0      | _     | 1     | -     | _     | 1       | _        | _    | 1    | -         | _    | 1    | -    | -     | -    | _                    | SWRST               | 0000       |

| EOGO                        | RNMICON                         | 31:16     | _     | 1     | -     | _     | 1       | _        | _    | WDTO | SWNMI     | _    | 1    | -    | GNMI  | HLVD | CF                   | WDTS                | 0000       |

| 1 000                       | KINIVIICON                      | 15:0      |       |       |       |       |         |          |      | NMI  | CNT<15:0> | •    |      |      |       |      |                      |                     | 0000       |

| E070                        | PWRCON                          | 31:16     | -     |       | _     | _     | _       | _        | _    |      |           | _    | 1    | 1    | _     | 1    | _                    | _                   | 0000       |

| 1 070                       | FWINCOIN                        | 15:0      | _     | _     | _     | _     | _       | _        |      | _    | _         | _    | _    | _    | _     | _    | _                    | VREGS               | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

- 2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

- 3: This bit is only available on devices with VBAT.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0' bit 15-13 **Unimplemented:** Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for Multi-vectored mode

0 = Interrupt controller configured for Single-vectored mode

bit 11 Unimplemented: Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 111 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 Unimplemented: Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

```

bit 9-8

IS01<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 7-5

Unimplemented: Read as '0'

bit 4-2

IP00<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 1-0

IS00<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

```

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 |                   |                   | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 |                   |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** DMA On bit<sup>(1)</sup>

1 = DMA module is enabled 0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 DMABUSY: DMA Module Busy bit

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   |                       | BYTO              | <1:0>             | WBO <sup>(1)</sup> | -                 | _                | BITO             |

| 22.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                     | _                 | _                 | _                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       | •                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit (1)

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) =  $\underline{1}$  (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 PLEN<4:0>: Polynomial Length bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Denotes the length of the polynomial – 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

**Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

### REGISTER 10-12: CHEPFABT: PREFETCH CACHE ABORT STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 31.24        | CHEPFABT<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 22.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 23:16        | CHEPFABT<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHEPFAB           | T<15:8>           |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHEPFAE           | 3T<7:0>           |                   |                  |                  |  |  |  |  |  |  |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 CHEPFABT<31:0>: Prefab Abort Count bits

Incremented each time an automatic prefetch cache is aborted due to a non-sequential instruction fetch, load or store.

#### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | _                 | -                 | -                 | -                | -                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 |                   | _                 | -                 | 1                 | -                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| /.0          | _                 | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2-0 FRMH<2:0>: The Upper 3 bits of the Frame Numbers bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

### **REGISTER 11-15: U1TOK: USB TOKEN REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |

| 15:8         | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | PID<              | 3:0> <sup>(1)</sup> | •                 | EP<3:0>           |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction

0001 = OUT (TX) token type transaction

**Note:** All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

TABLE 12-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                            |           |       |       |       |       |       |       |      | В     | its    |      |      |      |            |       |        |      |            |

|-----------------------------|----------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|--------|------|------|------|------------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name           | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4 | 19/3       | 18/2  | 17/1   | 16/0 | All Resets |

| E404                        | INT1R                      | 31:16     | 1     | _     | _     | _     | _     | _     | _    | _     | 1      | 1    | _    | _    | _          | 1     | _      | 1    | 0000       |

| FA04                        | INTIK                      | 15:0      | I     | _     | _     | _     | _     | _     | _    | _     | 1      | 1    | _    | _    |            | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R                      | 31:16     | 1     | _     | _     | _     | _     | -     | _    | _     | 1      | 1    | _    | _    | _          | 1     | _      | 1    | 0000       |

| FAUO                        | INTZK                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R                      | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FAUC                        | INTOK                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | INT3F | R<3:0> |      | 0000       |

| FA10                        | INT4R                      | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FAIU                        | IIN I 4K                   | 15:0      | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    |            | INT4F | R<3:0> |      | 0000       |

| FA18                        | T2CKR                      | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FATO                        | IZCKK                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | T2CKI | R<3:0> |      | 0000       |

| EA40                        | TOCKD                      | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA1C                        | A1C T3CKR 15:0 — — — — — — |           | _     | _     | -     | _     | _     | _     |      | T3CKI | R<3:0> |      | 0000 |      |            |       |        |      |            |

| FA20                        | T4CKR                      | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA20                        | 14CKK                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | T4CKR<3:0> |       |        |      | 0000       |

| EA 24                       | TECKD                      | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA24                        | T5CKR                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | T5CKI | R<3:0> |      | 0000       |

| FA28                        | IC4D                       | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FAZ8                        | IC1R                       | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | IC1R  | <3:0>  |      | 0000       |

| FA2C                        | ICOD                       | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FAZC                        | IC2R                       | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | IC2R  | <3:0>  |      | 0000       |

| FA30                        | IC3R                       | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FASU                        | IUSK                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    |            | IC3R  | <3:0>  |      | 0000       |

| FA34                        | IC4R                       | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA34                        | IC4K                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    |            | IC4R  | <3:0>  |      | 0000       |

| FA38                        | IC5R                       | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FASO                        | ICSK                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    |            | IC5R  | <3:0>  |      | 0000       |

| EA 40                       | OCFAR                      | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA48                        | OCFAR                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | _    | _    | _    |            | OCFA  | R<3:0> |      | 0000       |

| FA4C                        | OCFBR                      | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA4C                        | OCEBR                      | 15:0      | _     | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _    |            | OCFB  | R<3:0> |      | 0000       |

| E450                        | LIADVD                     | 31:16     | -     | _     | _     | _     | _     | _     | _    | _     |        | _    | _    | _    | _          | _     | _      | _    | 0000       |

| FA50                        | U1RXR                      | 15:0      | -     | _     | _     | _     | _     | _     | _    | _     | -      | -    | _    | _    |            | U1RX  | R<3:0> |      | 0000       |

#### TXCON: TYPE B TIMER CONTROL REGISTER REGISTER 14-1:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | _                    | _                 | -                   | -                 | 1                  | -                 | _                  | _                |

| 22,46        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | _                    | _                 | -                   | -                 | 1                  | -                 | _                  | _                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | -                  | _                 | _                  | _                |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

Legend:

W = Writable bit R = Readable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

ON: Timer On bit(1,3) bit 15

> 1 = Module is enabled 0 = Module is disabled

bit 14 Unimplemented: Read as '0' bit 13

**SIDL:** Stop in Idle Mode bit<sup>(4)</sup>

1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

TCKPS<2:0>: Timer Input Clock Prescale Select bits(3) bit 6-4

111 = 1:256 prescale value

110 = 1:64 prescale value

101 = 1:32 prescale value

100 = 1:16 prescale value

011 = 1:8 prescale value

010 = 1:4 prescale value

001 = 1:2 prescale value

000 = 1:1 prescale value

- Note 1: When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- 3: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3, and Timer5). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

### 27.1 Control Registers

### TABLE 27-1: HIGH/LOW-VOLTAGE DETECT REGISTER MAP

| ess                       | _                               | ø         | Bits  |       |       |       |       |       |      |        |      |      |      |      | S    |        |       |      |           |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|--------|------|------|------|------|------|--------|-------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1  | 16/0 | All Reset |

| 1000                      | HLVDCON                         | 31:16     | _     |       |       |       |       |       | _    | _      | _    |      | _    | _    | _    |        |       | -    | 0000      |

| 1800                      | HLVDCON                         | 15:0      | ON    | _     | _     | _     | VDIR  | BGVST | _    | HLVDET | _    | _    | _    | _    |      | HLVDL∙ | <3:0> |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 13.2 "CLR, SET, and INV Registers" for more information.

**NOTES:**

### 35.0 PACKAGING INFORMATION

### 35.1 Package Marking Information

28-Lead SOIC

28-Lead QFN

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Legend: XX...X Customer-specific information Year code (last digit of calendar year) Υ YY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01') NNN Alphanumeric traceability code Pb-free JEDEC designator for Matte Tin (Sn) (e3) This package is Pb-free. The Pb-free JEDEC designator (@3) can be found on the outer packaging for this package. Note: If the full Microchip part number cannot be marked on one line, it is carried over to the next

line, thus limiting the number of available characters for customer-specific information.

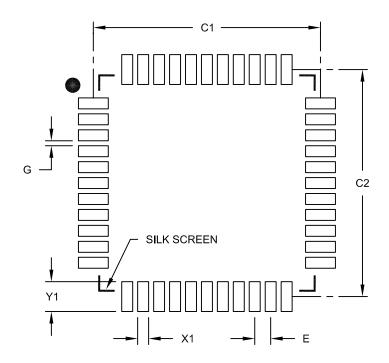

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |       |      |  |  |  |

|--------------------------|-------------|------|-------|------|--|--|--|

| Dimension                | MIN         | NOM  | MAX   |      |  |  |  |

| Contact Pitch            | E 0.80 BSC  |      |       |      |  |  |  |

| Contact Pad Spacing      | C1          |      | 11.40 |      |  |  |  |

| Contact Pad Spacing      | C2          |      | 11.40 |      |  |  |  |

| Contact Pad Width (X44)  | X1          |      |       | 0.55 |  |  |  |

| Contact Pad Length (X44) | Y1          |      |       | 1.50 |  |  |  |

| Distance Between Pads    | G           | 0.25 |       |      |  |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B