Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 17                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx254f128b-v-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 9: PIN NAMES FOR 28-PIN USB DEVICES WITH VBAT

# 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

#### PIC32MX255F128B PIC32MX275F256B

|       | FIC32WIAZ73F230B                                             |              |                                                        |

|-------|--------------------------------------------------------------|--------------|--------------------------------------------------------|

|       |                                                              | 28           | 1                                                      |

| Pin # | Full Pin Name                                                | Pin #        | Full Pin Name                                          |

| 1     | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                    | 15           | TDO/RPB9/SDA1/CTED4/PMD3/RB9                           |

| 2     | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/PMD1/RB1             | 16           | Vss                                                    |

| 3     | PGED1/AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2              | 17           | VCAP                                                   |

| 4     | PGEC1/AN5/C1INA/C2INC/RTCC/RPB3/SCL2/CTPLS/PMWR/RB3          | 18           | D+                                                     |

| 5     | Vss                                                          | 19           | D-                                                     |

| 6     | OSC1/CLKI/RPA2/RA2                                           | 20           | VUSB3V3                                                |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                                      | 21           | VBAT                                                   |

| 8     | SOSCI <sup>/</sup> RPB4/CTED11/RB4 <sup>(5)</sup>            | 22           | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMA1/RB14         |

| 9     | SOSCO/RPA4/T1CK/CTED9/RA4                                    | 23           | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15                  |

| 10    | VDD                                                          | 24           | AVss                                                   |

| 11    | TMS/RPB5/USBID/PMRD/RB5                                      | 25           | AVdd                                                   |

| 12    | VBUS                                                         | 26           | MCLR                                                   |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7                                 | 27           | PGED3/VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMD7/RA0        |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                | 28           | PGEC3/VREF-/AN1/RPA1/ASCL1/CTED2/PMD6/RA1              |

| Nata  | 1. The PPn pine can be used by remanable peripherals. See Ta | bla 1 for th | a susible suiskand and 40.2 "Parinkand Pin Calast" (se |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to VSs externally.

4: Shaded pins are 5V tolerant.

5: This is an input-only pin.

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

- Section 38. "High/Low Voltage Detect (HLVD)" (DS number pending)

NOTES:

|          | Р                                    | in Number <sup>(</sup> | [1]                    |             |                |                                                                    |                                   |

|----------|--------------------------------------|------------------------|------------------------|-------------|----------------|--------------------------------------------------------------------|-----------------------------------|

| Pin Name | 28-pin<br>QFN                        | 28-pin<br>SOIC         | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                        |                                   |

|          |                                      |                        |                        |             | PORT A         |                                                                    |                                   |

| RA0      | 27                                   | 2                      | 19                     | I/O         | ST             | PORTA is a bidirectional I/O port                                  |                                   |

| RA1      | 28                                   | 3                      | 20                     | I/O         | ST             |                                                                    |                                   |

| RA2      | 6                                    | 9                      | 30                     | I/O         | ST             |                                                                    |                                   |

| RA3      | 7                                    | 10                     | 31                     | I/O         | ST             |                                                                    |                                   |

| RA4      | 9                                    | 12                     | 34                     | I/O         | ST             | ]                                                                  |                                   |

| RA7      | _                                    |                        | 13                     | I/O         | ST             | ]                                                                  |                                   |

| RA8      |                                      |                        | 32                     | I/O         | ST             | ]                                                                  |                                   |

| RA9      | —                                    | —                      | 35                     | I/O         | ST             |                                                                    |                                   |

| RA10     | _                                    |                        | 12                     | I/O         | ST             | 1                                                                  |                                   |

|          |                                      |                        |                        |             | PORTB          | •                                                                  |                                   |

| RB0      | 1                                    | 4                      | 21                     | I/O         | ST             | PORTB is a bidirectional I/O port                                  |                                   |

| RB1      | 2                                    | 5                      | 22                     | I/O         | ST             |                                                                    |                                   |

| RB2      | 3                                    | 6                      | 23                     | I/O         | ST             |                                                                    |                                   |

| RB3      | 4                                    | 7                      | 24                     | I/O         | ST             |                                                                    |                                   |

| RB4      | 8                                    | 11                     | 33                     | I/O         | ST             |                                                                    |                                   |

| RB5      | 11                                   | 14                     | 41                     | I/O         | ST             |                                                                    |                                   |

| RB6      | 12 <sup>(2)</sup>                    | 15 <sup>(2)</sup>      | 42 <sup>(4)</sup>      | I/O         | ST             | 1                                                                  |                                   |

| RB7      | 13                                   | 16                     | 43                     | I/O         | ST             | 1                                                                  |                                   |

| RB8      | 14                                   | 17                     | 44                     | I/O         | ST             | ]                                                                  |                                   |

| RB9      | 15                                   | 18                     | 1                      | I/O         | ST             | ]                                                                  |                                   |

| RB10     | 18 <sup>(4)</sup>                    | 21 <sup>(4)</sup>      | 8 <sup>(4)</sup>       | I/O         | ST             | ]                                                                  |                                   |

| RB11     | 19 <sup>(4)</sup>                    | 22 <sup>(4)</sup>      | 9 <sup>(4)</sup>       | I/O         | ST             | ]                                                                  |                                   |

| RB12     | 20 <sup>(4)</sup>                    | 23 <sup>(4)</sup>      | 10 <sup>(4)</sup>      | I/O         | ST             | ]                                                                  |                                   |

| RB13     | 21 <sup>(3)</sup>                    | 24 <sup>(3)</sup>      | 11 <sup>(3)</sup>      | I/O         | ST             | ]                                                                  |                                   |

| RB14     | 22                                   | 25                     | 14                     | I/O         | ST             | ]                                                                  |                                   |

| RB15     | 23                                   | 26                     | 15                     | I/O         | ST             | ]                                                                  |                                   |

| - ;      | CMOS = CI<br>ST = Schmi<br>TTL = TTL | itt Trigger in         |                        |             |                | Analog = Analog input<br>O = Output<br>PPS = Peripheral Pin Select | P = Power<br>I = Input<br>— = N/A |

# TABLE 1-6: PORTA THROUGH PORTC PINOUT I/O DESCRIPTIONS

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for General Purpose devices only.

3: This pin is not available for devices with VBAT.

4: This pin is not available for devices with USB.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   | •                 |                   | CHEW1             | <7:0>             |                   |                  | •                |  |  |  |

# REGISTER 10-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### REGISTER 10-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW2<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   | •                 | CHEW2             | <7:0>             |                   |                  | •                |  |  |  |

| Legend:           |                                 |                      |                    |

|-------------------|---------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit |                      | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 |                   | _                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   |                   | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 |                   |                   |                   | -                 |                  | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | _                | VBUSVDIE         |

#### REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

#### bit 6 **T1MSECIE:** 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

#### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 **SESVDIE:** Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | -                 | —                 |                   | —                 |                   | —                 | —                | —                |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | _                 |                   | —                 |                   |                   |                  | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | _                 | —                 |                   | —                 |                   | —                 | —                | —                |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |  |

#### REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

| REGIOT       | LEGISTER II-19. OTBDTF5. OSB BOTTER DESCRIPTOR TABLE FAGE 5 REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|----------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 21.24        | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                                                                      | —                 | _                 | —                 | -                 |                   | —                | —                |  |  |

| 00.40        | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                                                                      | —                 | _                 | —                 |                   |                   | —                | —                |  |  |

| 15:8         | U-0                                                                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         |                                                                      | —                 | _                 | —                 |                   |                   | —                | —                |  |  |

| 7:0          | R/W-0                                                                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                                                                      |                   |                   | BDTPTR            | J<31:24>          |                   |                  |                  |  |  |

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRU<31:24>:** Buffer Descriptor Table Base Address bits This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

## TABLE 12-2: OUTPUT PIN SELECTION

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|----------------------|----------|-------------|---------------------------------------------|

| RPA0                 | RPA0R    | RPA0R<3:0>  | 0000 = No Connect<br>0001 = U1TX            |

| RPB3                 | RPB3R    | RPB3R<3:0>  | $0010 = \overline{U2RTS}$                   |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = SS1<br>0100 = VBUSON <sup>(4)</sup>  |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 0101 = OC1<br>0110 = Reserved               |

| RPC7 <sup>(1)</sup>  | RPC7R    | RPC7R<3:0>  | 0111 = C2OUT                                |

| RPC0 <sup>(1)</sup>  | RPC0R    | RPC0R<3:0>  | 1000 = Reserved                             |

| RPC5 <sup>(1)</sup>  | RPC5R    | RPC5R<3:0>  | 1111 = Reserved                             |

| RPA1                 | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 0001 = Reserved                             |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11 <sup>(2)</sup> | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8 <sup>(1)</sup>  | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                                |

| RPC8 <sup>(1)</sup>  | RPC8R    | RPC8R<3:0>  |                                             |

| RPA9 <sup>(1)</sup>  | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2                 | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6 <sup>(2)</sup>  | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB13 <sup>(3)</sup> | RPB13R   | RPB13R<3:0> | 0011 = SDO1<br>0100 = SDO2                  |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 0101 = OC4<br>0110 = OC5                    |

| RPC6 <sup>(1)</sup>  | RPC6R    | RPC6R<3:0>  | 0111 = REFCLKO<br>1000 = Reserved           |

| RPC1 <sup>(1)</sup>  | RPC1R    | RPC1R<3:0>  | •                                           |

| RPC3 <sup>(1)</sup>  | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3                 | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14                | RPB14R   | RPB14R<3:0> |                                             |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10 <sup>(2)</sup> | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9 <sup>(1)</sup>  | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2 <sup>(1)</sup>  | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4 <sup>(1)</sup>  | RPC4R    | RPC4R<3:0>  | •<br>1111 = Reserved                        |

**Note 1:** This pin is only available on 44-pin devices.

2: This pin is not available on USB devices.

3: This pin is not available on VBAT devices.

4: This pin is only available on USB devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 |                   | —                 | _                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | -                 | —                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | _                 | TECS             | <1:0>            |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled

- 0 = Timer is disabled

#### bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode0 = Continue module operation when the device enters Idle mode

#### bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to Timer1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

#### bit 11 TWIP: Asynchronous Timer Write in Progress bit

#### In Asynchronous Timer mode:

- 1 = Asynchronous write to the Timer1 register in progress

- 0 = Asynchronous write to Timer1 register is complete

- In Synchronous Timer mode:

This bit is read as '0'.

- bit 10 Unimplemented: Read as '0'

- bit 9-8 TECS<1:0>: Timer1 External Clock Selection bits

- 11 = Reserved

- 10 = External clock comes from the LPRC

- 01 = External clock comes from the T1CK pin

- 00 = External clock comes from the SOSC

#### bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0: 1 = Gated time accumulation is enabled

#### 0 = Gated time accumulation is disabled

#### bit 6 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

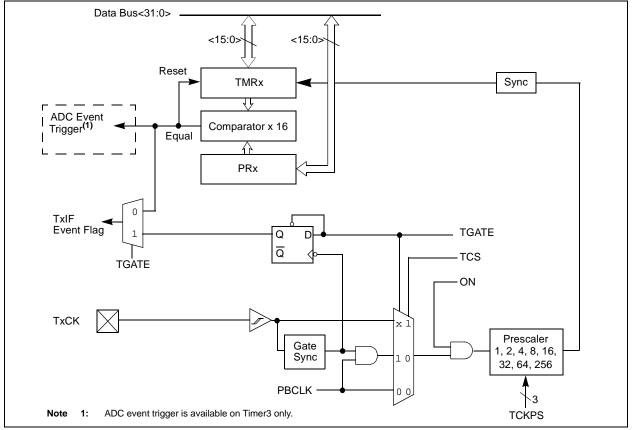

# 14.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

# 14.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 14-1 and Figure 14-2 illustrate block diagrams of Timer2/3 and Timer4/5.

## FIGURE 14-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

NOTES:

#### **REGISTER 17-1:** ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

ICM<2:0>: Input Capture Mode Select bits

bit 2-0

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 18.1 Output Compare Control Registers

# TABLE 18-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |       |            |       |       |       |       |      | Bi    | ts       |      |      |              |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|-------|------------|-------|-------|-------|-------|------|-------|----------|------|------|--------------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14      | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5 | 20/4         | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         | -     | —          | —     | —     | —     | —     | —    | -     |          | -    | —    | —            | —      | —    | —        | -    | 0000         |

| 0000                        | 001001                          | 15:0          | ON    | —          | SIDL  | —     | —     | —     | —    | —     | —        | —    | OC32 | OCFLT        | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0 |       | OC1R<31:0> |       |       |       |       |      |       |          |      |      | XXXX<br>XXXX |        |      |          |      |              |

| 3020                        | OC1RS                           | 31:16<br>15:0 |       |            |       |       |       |       |      | OC1RS | \$<31:0> |      |      |              |        |      |          |      | XXXX<br>XXXX |

| 2000                        | 00000                           | 31:16         | -     | _          | —     | —     | —     | —     | —    | _     | _        | _    | _    | —            | —      | —    | _        | _    | 0000         |

| 3200                        | OC2CON                          | 15:0          | ON    | _          | SIDL  | _     | _     |       | _    |       |          | -    | OC32 | OCFLT        | OCTSEL |      | OCM<2:0> |      | 0000         |

| 224.0                       | OC2R                            | 31:16         |       |            |       |       |       |       |      | OC2R  | .01.0.   |      |      |              |        |      |          |      | XXXX         |

| 3210                        | UC2R                            | 15:0          |       |            |       |       |       |       |      | UCZR  | <31:0>   |      |      |              |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16         |       |            |       |       |       |       |      | OC2RS | 221:0    |      |      |              |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0          |       |            |       |       |       |       |      | UCZRC | \$<31.0> |      |      |              |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16         |       | _          | _     |       | _     | -     |      |       |          |      | _    | _            | —      | _    | —        |      | 0000         |

| 3400                        | 003001                          | 15:0          | ON    | —          | SIDL  | —     | —     | —     | —    | —     | —        | —    | OC32 | OCFLT        | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0 |       |            |       |       |       |       |      | OC3R  | <31:0>   |      |      |              |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16         |       |            |       |       |       |       |      | OC3R5 |          |      |      |              |        |      |          |      | XXXX         |

| 3420                        | UC3K3                           | 15:0          |       |            |       |       |       |       |      | UCSRC | \$<31.0> |      |      |              |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16         | _     | —          | —     | —     | —     | _     |      | _     | _        | _    | —    | —            | _      | —    | —        | —    | 0000         |

| 0000                        | 004001                          | 15:0          | ON    | —          | SIDL  | —     | —     | —     | —    | —     | —        | —    | OC32 | OCFLT        | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16         |       |            |       |       |       |       |      | OC4R  | <31.0>   |      |      |              |        |      |          |      | XXXX         |

|                             | 00                              | 15:0          |       |            |       |       |       |       |      | 00    | 10 1107  |      |      |              |        |      |          |      | XXXX         |

| 3620                        | OC4RS                           | 31:16         |       |            |       |       |       |       |      | OC4RS | S<31:0>  |      |      |              |        |      |          |      | XXXX         |

|                             |                                 | 15:0          |       |            |       |       |       |       |      |       |          |      | -    |              |        |      |          |      | XXXX         |

| 3800                        | OC5CON                          | 31:16         | -     | _          | —     | _     | _     | _     | —    | _     | _        | _    | —    | _            | -      |      | —        | —    | 0000         |

|                             |                                 | 15:0          | ON    |            | SIDL  |       |       | _     |      |       | _        | _    | OC32 | OCFLT        | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16         |       |            |       |       |       |       |      | OC5R  | <31:0>   |      |      |              |        |      |          |      | XXXX         |

|                             |                                 | 15:0          |       |            |       |       |       |       |      |       |          |      |      |              |        |      |          |      | XXXX         |

| 3820                        | OC5RS                           | 31:16<br>15:0 |       |            |       |       |       |       |      | OC5R5 | 6<31:0>  |      |      |              |        |      |          |      | XXXX         |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

# REGISTER 20-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                 |                   |                   | —                 |                   |                  | -                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | —                 | —                 | —                 | _                | —                |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |

| 15:8         | ACKSTAT           | TRSTAT            |                   | —                 | —                 | BCL               | GCSTAT           | ADD10            |  |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |

| Legend:           | HS = Set in hardware | ardware HSC = Hardware set/cleared |                   |  |  |

|-------------------|----------------------|------------------------------------|-------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                   |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | C = Clearable bit |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation  $0 = No \ collision$ Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection. bit 7 IWCOL: Write Collision Detect bit 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy  $0 = No \ collision$ Hardware set at occurrence of write to I2CxTRN while busy (cleared by software). bit 6 I2COV: Receive Overflow Flag bit 1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflowHardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software). bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) 1 = Indicates that the last byte received was data

0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 |                   | —                 |                   | _                 | -                 | —                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | RDATAIN<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   |                   |                   | RDATAIN<          | :7:0>             |                   |                  |                  |  |  |  |

## REGISTER 22-8: PMRDIN: PARALLEL PORT READ INPUT DATA REGISTER

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

Legend:

bit 15-0 RDATAIN<15:0>: Port Read Input Data bits

**Note:** This register is only used when the DUALBUF bit (PMCON<17>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN register is used for reads instead of PMRDIN.

## REGISTER 27-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

- bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit Select bits<sup>(1)</sup>

- 1111 = External LVDIN pin 1110 = Reserved; do not use 1101 = Reserved; do not use 1100 = Reserved: do not use 1011 = Reserved; do not use 1010 = Selects Trip Point 10 1001 = Selects Trip Point 9 1000 = Selects Trip Point 8 0111 = Selects Trip Point 7 0110 = Selects Trip Point 6 0101 = Selects Trip Point 5 0100 = Selects Trip Point 4 0011 = Reserved; do not use 0010 = Reserved; do not use 0001 = Reserved; do not use 0000 = Reserved; do not use

- **Note 1:** To avoid false HLVD events, all HLVD module setting changes should occur only when the module is disabled (ON = 0). See Table 33-6 in the "**Electrical Characteristics**" chapter for the actual trip points.

# 32.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 32.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

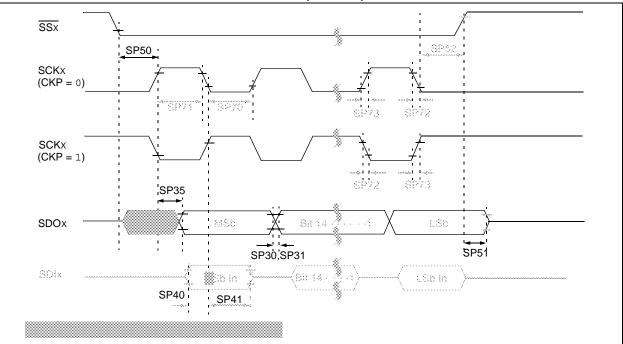

# FIGURE 33-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

# TABLE 33-31: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | TICS                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                    |  |  |

|---------------|-----------------------|--------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                               | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                 | TSCK/2                                                | _                   |      | ns    | _                  |  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                | TSCK/2                                                | _                   |      | ns    | —                  |  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                         | —                                                     | —                   |      | ns    | See parameter DO32 |  |  |

| SP73          | TscR                  | SCKx Input Rise Time                                         | —                                                     | —                   | _    | ns    | See parameter DO31 |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                          | —                                                     | —                   |      | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                          | —                                                     | _                   |      | ns    | See parameter DO31 |  |  |

| SP35          |                       | SDOx Data Output Valid after                                 | _                                                     | _                   | 15   | ns    | VDD > 2.7V         |  |  |

|               | TSCL2DOV              | SCKx Edge                                                    | —                                                     | —                   | 20   | ns    | Vdd < 2.7V         |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                   | 10                                                    |                     |      | ns    | —                  |  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                 | 10                                                    | _                   | _    | ns    | —                  |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                   | _                   | _    | ns    | —                  |  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>       | 5                                                     | —                   | 25   | ns    | —                  |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | Тѕск + 20                                             | _                   |      | ns    | —                  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

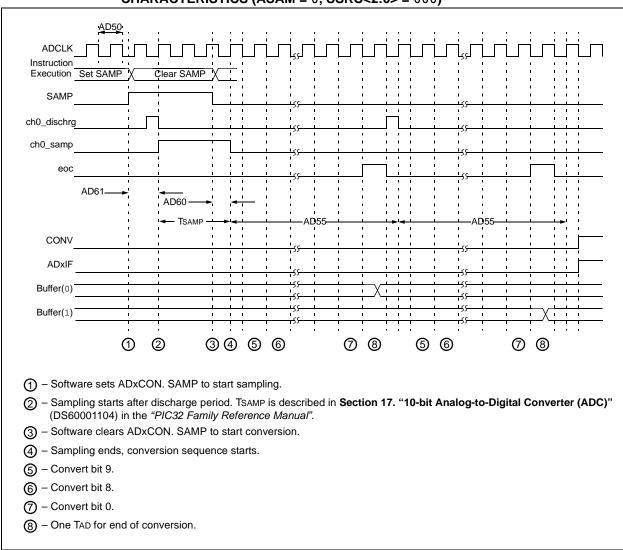

## FIGURE 33-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

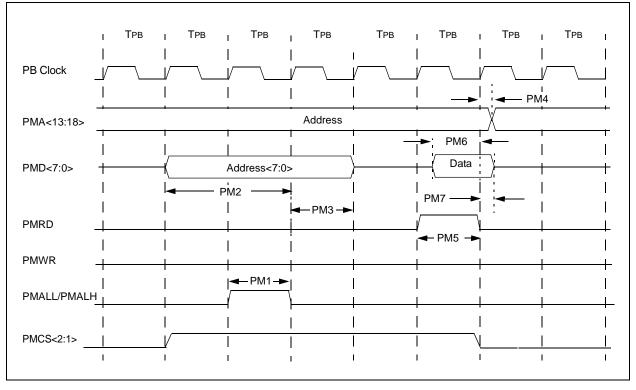

#### TABLE 33-38: PARALLEL SLAVE PORT REQUIREMENTS

| АС СН         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |   |    |    |   |  |  |  |

|---------------|--------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|---|--|--|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                   |   |    |    |   |  |  |  |

| PS1           | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                | _ | _  | ns | _ |  |  |  |

| PS2           | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                | — | -  | ns | — |  |  |  |

| PS3           | TrdL2dt<br>V | $\overline{RD}$ and $\overline{CS}$ Active to Data-Out Valid                     | _                                                                                                                                                                                                                                                                                 | — | 60 | ns | _ |  |  |  |

| PS4           | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                 | — | 10 | ns | _ |  |  |  |

| PS5           | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                          | _ | _  | ns | — |  |  |  |

| PS6           | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                          | _ | _  | ns | — |  |  |  |

| PS7           | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                          |   | _  | ns | _ |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

## FIGURE 33-21: PARALLEL MASTER PORT READ TIMING DIAGRAM