Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 72MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 17                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx254f128bt-v-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Pi                                     | in Number <sup>(</sup> | 1)                     |             |                                                                    |                                   |  |  |  |  |  |

|----------|----------------------------------------|------------------------|------------------------|-------------|--------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| Pin Name | 28-pin<br>QFN                          | 28-pin<br>SOIC         | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer Description<br>Type                                         |                                   |  |  |  |  |  |

| PORTC    |                                        |                        |                        |             |                                                                    |                                   |  |  |  |  |  |

| RC0      | —                                      |                        | 25                     | I/O         | ST                                                                 | PORTC is a bidirectional I/O port |  |  |  |  |  |

| RC1      | —                                      | —                      | 26                     | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC2      | —                                      | —                      | 27                     | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC3      | —                                      | —                      | 36                     | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC4      | —                                      | —                      | 37                     | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC5      | —                                      | —                      | 38                     | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC6      | —                                      | —                      | 2                      | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC7      | —                                      | —                      | 3                      | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC8      | —                                      | —                      | 4                      | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| RC9      | —                                      | —                      | 5                      | I/O         | ST                                                                 |                                   |  |  |  |  |  |

| •        | CMOS = CN<br>ST = Schmi<br>TTL = TTL i | tt Trigger in          |                        |             | Analog = Analog input<br>O = Output<br>PPS = Peripheral Pin Select | P = Power<br>I=Input<br>— = N/A   |  |  |  |  |  |

#### **TABLE 1-6:** PORTA THROUGH PORTC PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for General Purpose devices only.

3: This pin is not available for devices with VBAT.

4: This pin is not available for devices with USB.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **8.0 "Oscillator Configuration"** for details).

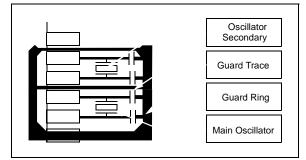

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: S

### : SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.9 Typical Application Connection Examples

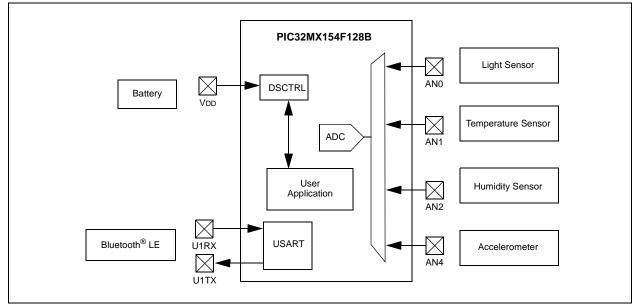

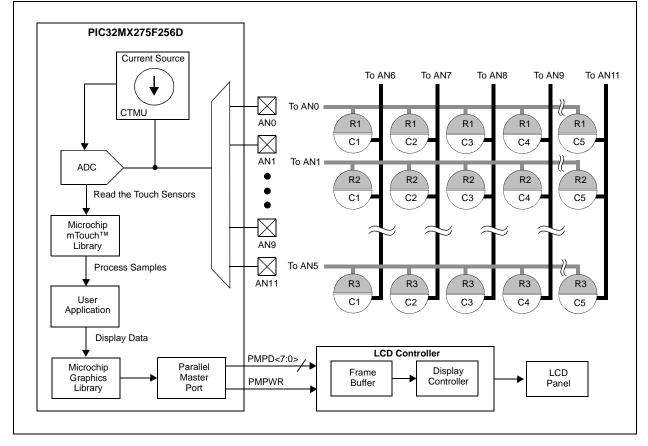

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-5: REMOTE SENSING APPLICATION

## 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

## 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER<br/>MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                        |

| DSS       | EJTAG debug single step.                                                                                                         |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external EJ_DINT input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                         |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                     |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                  |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                          |

| IBE       | Instruction fetch bus error.                                                                                                     |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                               |

| Sys       | Execution of SYSCALL instruction.                                                                                                |

| Вр        | Execution of BREAK instruction.                                                                                                  |

| RI        | Execution of a reserved instruction.                                                                                             |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                    |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                              |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                          |

| Tr        | Execution of a trap (when trap condition is true).                                                                               |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                    |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                            |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                    |

| DBE       | Load or store bus error.                                                                                                         |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                     |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **29.0 "Power-Saving Features"**.

# 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |  |  |  |

## REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| · J · · ·         |                           |                      |                    |

|-------------------|---------------------------|----------------------|--------------------|

| R = Readable bit  | able bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

## bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

# 8.2 Oscillator Control Registers

| sse                         |                  |           |       |       |           |       |            |                  |             |                     | Bits       |      |         |         |           |               |         |        | -                         |

|-----------------------------|------------------|-----------|-------|-------|-----------|-------|------------|------------------|-------------|---------------------|------------|------|---------|---------|-----------|---------------|---------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13     | 28/12 | 27/11      | 26/10            | 25/9        | 24/8                | 23/7       | 22/6 | 21/5    | 20/4    | 19/3      | 18/2          | 17/1    | 16/0   | All Resets <sup>(1)</sup> |

| F000                        | OSCCON           | 31:16     | _     | _     | —         | —     | —          |                  | FRCDIV<2:0  | >                   | DRMEN      | _    | SLP2SPD | _       | —         | —             | —       | —      | 0020                      |

| F000                        | USCCON           | 15:0      | Ι     | (     | COSC<2:0> |       | —          |                  | NOSC<2:0>   |                     | CLKLOCK    | _    | —       | SLPEN   | CF        | UFRCEN        | SOSCEN  | OSWEN  | xx0x                      |

| F010                        | OSCTUN           | 31:16     | —     | _     | —         | —     | —          | —                | —           | —                   | —          |      | —       | —       | _         | —             | —       | —      | 0000                      |

| F010                        | 15:              |           | _     | _     | _         |       | —          | _                | —           |                     | —          |      |         |         | ΤL        | JN<5:0>       | •       |        | 00xx                      |

| F000                        |                  | 31:16     | _     | _     | _         |       | —          | - PLLODIV<2:0> - |             |                     |            |      | —       | _       | —         | PLLMULT<2:0>  |         | 01xx   |                           |

| F020                        | F020 SPLLCON     | 15:0      | —     |       | —         | —     | —          | I                | PLLIDIV<2:0 | >                   | PLLICLK    | _    | —       | —       | —         | —             | —       | —      | 0x0x                      |

| F030                        | UPLLCON          | 31:16     | —     |       | —         | —     | —          | UP               | LLODIV<2:0  | > <sup>(1)</sup>    | —          | _    | —       | —       | —         | UPLLMULT<2:0> |         | 01xx   |                           |

| FU30                        | UPLLCON          | 15:0      | —     |       | —         | —     | —          | UF               | PLLIDIV<2:0 | <sub>&gt;</sub> (1) | —          | _    | —       | —       | —         | —             | —       | —      | 0x0x                      |

| E090                        | REF00CON         | 31:16     | —     |       |           |       |            |                  |             |                     | RODIV<14:0 | )>   |         |         |           |               |         |        | 0000                      |

| FU0U                        | REFUCCON         | 15:0      | ON    |       | SIDL      | OE    | RSLP       | —                | DIVSWEN     | ACTIVE              | —          | —    | —       | —       |           | ROS           | EL<3:0> |        | 0000                      |

| E000                        | <b>REFOOTRIM</b> | 31:16     |       |       |           |       | ROTRIM<8:0 | )>               |             |                     |            | _    | —       |         | _         | _             | —       | _      | 0000                      |

| F090                        | REFOULKIN        | 15:0      | -     | _     | _         | _     | —          | _                | —           | —                   | _          | _    | —       |         | _         | _             | —       | _      | 0000                      |

| F0A0                        | PB0DIV           | 31:16     | -     | _     | _         | _     | —          | _                | —           | —                   | _          | _    | —       |         | _         | _             | —       | _      | 0000                      |

| FUAU                        | FOUDIV           | 15:0      | —     |       | —         | —     | PBDIVRDY   | —                | —           | —                   | —          |      |         |         | PBDIV<6:0 | )>            |         |        | 8801                      |

| F0C0                        | CLKSTAT          | 31:16     | —     |       | —         | —     | —          | —                | —           | —                   | —          | —    | —       | —       | —         | —             | —       | —      | 0000                      |

| FUCU                        | GENSTAT          | 15:0      | _     | _     | _         | _     | _          | _                | _           | UPLLRDY             | SPLLRDY    | _    | LPRCRDY | SOSCRDY | _         | POSCRDY       | SPLLRDY | FRCRDY | 0000                      |

# TABLE 8-1: OSCILLATOR CONFIGURATION REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | ROTRIM<0>         | —                 | —                 | —                 | —                 | _                 | —                | —                |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          |                   |                   |                   | _                 |                   |                   |                  | _                |  |  |  |  |

## REGISTER 8-6: REFOOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

## Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

bit 22-0 Unimplemented: Read as '0'

**Note 1:** While the ON bit (REFO0CON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

Do not write to this register when the ON bit (REFO0CON<15>) is not equal to the ACTIVE bit (REFO0CON<8>).

3: Specified values in this register do not take effect if RODIV<14:0> bits (REFO0CON<30:16>) = 0.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| ILCIOIC L    | LEGISTER 3-10. DOTACOLL. DIMA CHANNEL & CELE-SIZE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                                                          | —                 | —                 |                   |                   | —                 |                  | —                |  |  |  |  |

| 22.16        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                                                          | —                 | _                 | —                 | _                 | _                 | _                | —                |  |  |  |  |

| 45.0         | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHCSIZ<15:8>                                               |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                                                            |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |

# REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

111111111111111 = 65,535 bytes transferred on an event

## **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

## Note: When in Pattern Detect mode, this register is reset on a pattern detect.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| INE OIO I    | LK 11-5.          |                   |                   |                   |                        |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | -                 | —                 | —                      | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | —                      | _                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 | —                 | _                      | —                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | —                 |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

## REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

# Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

- (Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

- **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

## REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

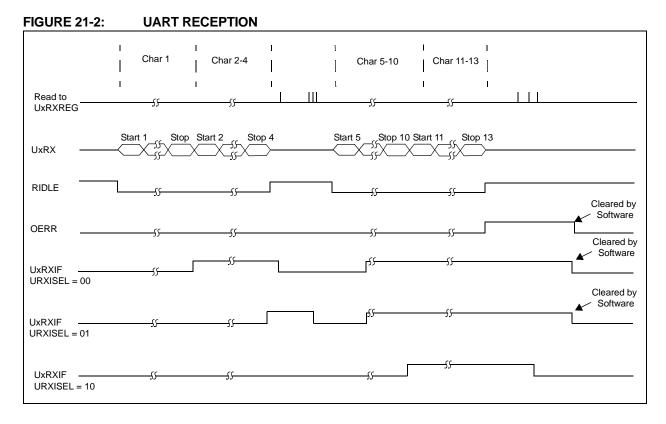

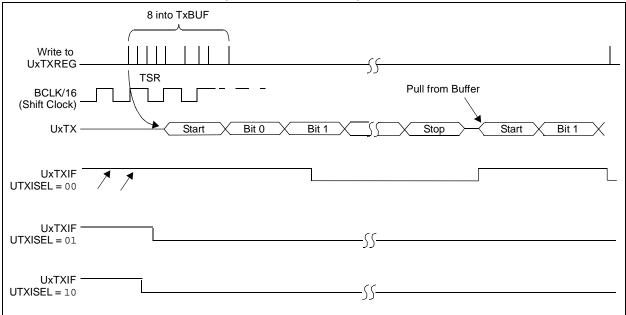

Figure 21-2 and Figure 21-3 illustrate typical receive and transmit timing for the UART module.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   | -                 |                   | -                | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

## **REGISTER 26-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

- 1 = Module is enabled

- Setting this bit does not affect other bits in the register.

- 0 = Module is disabled and does not consume current.

- Clearing this bit does not affect the other bits in the register.

- bit 14-7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

- bit 5 **CVRR:** CVREF Range Selection bit

- 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

- $\rm 0$  = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size

- bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)

- 0 = Comparator voltage reference source, CVRSRC = AVDD AVSS

- bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

- $\frac{\text{When CVRR} = 1:}{\text{CVREF} = (\text{CVR}<3:0>/24) \bullet (\text{CVRSRC})}$  $\frac{\text{When CVRR} = 0:}{\text{CVREF} = 1/4 \bullet (\text{CVRSRC}) + (\text{CVR}<3:0>/32) \bullet (\text{CVRSRC})}$

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 28.1 CTMU Control Registers

## TABLE 28-1: CTMU REGISTER MAP

| ess                        |                                 |           |         |         |          |       |         |          |          | Bits     |         |         |        |       |          |      |      |       | ú          |

|----------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|--------|-------|----------|------|------|-------|------------|

| Virtual Addre:<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5   | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Resets |

| 4000                       | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |        | EDG2S | SEL<3:0> |      | _    | —     | 0000       |

| A200                       |                                 | 15:0      | ON      | —       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM< | <5:0> |          |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

DS60001404A-page 258

#### REGISTER 30-2: **DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)** bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits 11 = PBCLK is SYSCLK divided by 8 10 = PBCLK is SYSCLK divided by 4 01 = PBCLK is SYSCLK divided by 2 00 = PBCLK is SYSCLK divided by 1 bit 11 Reserved: Write '1' bit 10 **OSCIOFNC:** CLKO Enable Configuration bit 1 = CLKO output disabled 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00) bit 9-8 POSCMOD<1:0>: Primary Oscillator Configuration bits 11 = Primary Oscillator is disabled 10 = HS Oscillator mode is selected 01 = XT Oscillator mode is selected 00 = External Clock mode is selected bit 7 IESO: Internal External Switchover bit 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled) 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled) Reserved: Write '1' bit 6 FSOSCEN: Secondary Oscillator Enable bit bit 5 1 = Enable Secondary Oscillator 0 = Disable Secondary Oscillator bit 4-3 Reserved: Write '1' bit 2-0 FNOSC<2:0>: Oscillator Selection bits 111 = Fast RC Oscillator with divide-by-N (FRCDIV) 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler 101 = Low-Power RC Oscillator (LPRC) 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL) 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup> 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

# 31.0 INSTRUCTION SET

The PIC32MX1XX/2XX XLP instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

## TABLE 33-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHA        | RACTER  | ISTICS           |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |       |                                        |  |  |

|---------------|---------|------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------|--|--|

| Param.<br>No. | Symbol  | Charac           | teristics              | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Max. | Units | Conditions                             |  |  |

| IM40          | TAA:SCL | Output Valid     | 100 kHz mode           | _                                                                                                                                                                                                                                                                                 | 3500 | ns    | —                                      |  |  |

|               |         | from Clock       | 400 kHz mode           | —                                                                                                                                                                                                                                                                                 | 1000 | ns    | —                                      |  |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | —                                                                                                                                                                                                                                                                                 | 350  | ns    | _                                      |  |  |

| IM45          | TBF:SDA | Bus Free Time    | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                               | —    | μS    | The amount of time the                 |  |  |

|               |         |                  | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                               | —    | μS    | bus must be free                       |  |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | 0.5                                                                                                                                                                                                                                                                               | —    | μS    | before a new<br>transmission can start |  |  |

| IM50          | Св      | Bus Capacitive L | oading                 | —                                                                                                                                                                                                                                                                                 | 400  | pF    | —                                      |  |  |

| IM51          | Tpgd    | Pulse Gobbler D  | elay                   | 52                                                                                                                                                                                                                                                                                | 312  | ns    | See Note 3                             |  |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

**2:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# FIGURE 34-4: TYPICAL IDD CURRENT @ VDD = 3.3V

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

NOTES:

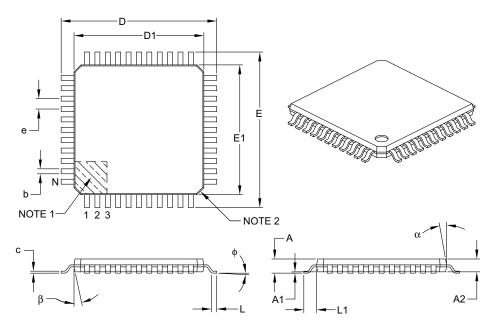

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |      |           |      |  |  |

|--------------------------|-----------|------|-----------|------|--|--|

| Dimensio                 | on Limits | MIN  | NOM       | MAX  |  |  |

| Number of Leads          | Ν         |      | 44        |      |  |  |

| Lead Pitch               | е         |      | 0.80 BSC  |      |  |  |

| Overall Height           | Α         | _    | —         | 1.20 |  |  |

| Molded Package Thickness | A2        | 0.95 | 1.00      | 1.05 |  |  |

| Standoff                 | A1        | 0.05 | —         | 0.15 |  |  |

| Foot Length              | L         | 0.45 | 0.60      | 0.75 |  |  |

| Footprint                | L1        |      | 1.00 REF  |      |  |  |

| Foot Angle               | ¢         | 0°   | 3.5°      | 7°   |  |  |

| Overall Width            | E         |      | 12.00 BSC |      |  |  |

| Overall Length           | D         |      | 12.00 BSC |      |  |  |

| Molded Package Width     | E1        |      | 10.00 BSC |      |  |  |

| Molded Package Length    | D1        |      | 10.00 BSC |      |  |  |

| Lead Thickness           | С         | 0.09 | —         | 0.20 |  |  |

| Lead Width               | b         | 0.30 | 0.37      | 0.45 |  |  |

| Mold Draft Angle Top     | α         | 11°  | 12°       | 13°  |  |  |

| Mold Draft Angle Bottom  | β         | 11°  | 12°       | 13°  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B