Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 72MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx254f128dt-v-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES WITHOUT VBAT

#### 28-PIN SOIC (TOP VIEW)<sup>(1,2,3)</sup>

|      | 28 |

|------|----|

| SOIC |    |

1

#### PIC32MX154F128B PIC32MX174F256B

| Pin # | Full Pin Name                                |    | Full Pin Name                                  |

|-------|----------------------------------------------|----|------------------------------------------------|

| 1     | MCLR                                         | 15 | PGEC3/RPB6/ASCL2/PMD6/RB6                      |

| 2     | VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMA1/RA0    | 16 | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 3     | VREF-/AN1/RPA1/ASCL1/CTED2/RA1               | 17 | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 4     | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0         | 18 | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 5     | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12//RB1 | 19 | Vss                                            |

| 6     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2         | 20 | VCAP                                           |

| 7     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3           | 21 | PGED1/RPB10/CTED11/PMD2/RB10                   |

| 8     | Vss                                          | 22 | PGEC1/TMS/RPB11/PMD1/RB11                      |

| 9     | OSC1/CLKI/RPA2/RA2                           | 23 | AN12/PMD0/RB12                                 |

| 10    | OSC2/CLKO/RPA3/PMA0/RA3                      | 24 | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 11    | SOSCI/RPB4/RB4 <sup>(4)</sup>                | 25 | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 12    | SOSCO/RPA4/T1CK/CTED9/RA4                    | 26 | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 13    | Vdd                                          | 27 | AVss                                           |

| 14    | PGED3/RPB5/ASDA2/PMD7/RB5                    | 28 | AVdd                                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: This is an input-only pin.

#### **TABLE 12:** PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES WITHOUT VBAT

### 44-PIN QFN AND TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

#### PIC32MX154F128D PIC32MX174F256D

44

44

1

1

| Pin # | Full Pin Name                               | Pin # | Full Pin Name                           |

|-------|---------------------------------------------|-------|-----------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMA7/RB9                    | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2    |

| 2     | RPC6/PMA1/RC6                               | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMA2/RB3 |

| 3     | RPC7/PMCS1/RC7                              | 25    | AN6/RPC0/RC0                            |

| 4     | RPC8/PMD5/RC8                               | 26    | AN7/RPC1/RC1                            |

| 5     | RPC9/CTED7/PMD6/RC9                         | 27    | AN8/RPC2/PMWR/RC2                       |

| 6     | Vss                                         | 28    | Vdd                                     |

| 7     | VCAP                                        | 29    | Vss                                     |

| 8     | PGED1/RPB10/CTED11/PMA8/RB10                | 30    | OSC1/CLKI/RPA2/RA2                      |

| 9     | PGEC1/TMS/RPB11/PMA9/RB11                   | 31    | OSC2/CLKO/RPA3/RA3                      |

| 10    | AN12/PMD0/RB12                              | 32    | TDO/RPA8/PMD2/RA8                       |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                  | 33    | SOSCI/RPB4/CTED11/RB4                   |

| 12    | PGED4/PMA10/RA10                            | 34    | SOSCO/RPA4/T1CK/RA4                     |

| 13    | PGEC4/TCK/CTED8/PMD3/RA7                    | 35    | TDI/RPA9/PMD1/RA9                       |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/RB14   | 36    | RPC3/RC3                                |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMA0/RB15        | 37    | RPC4/PMD4/RC4                           |

| 16    | AVss                                        | 38    | RPC5/PMD7/RC5                           |

| 17    | AVdd                                        | 39    | Vss                                     |

| 18    | MCLR                                        | 40    | Vdd                                     |

| 19    | VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/RA0        | 41    | PGED3/RPB5/ASDA2/PMA3/RB5               |

| 20    | VREF-/AN1/RPA1/ASCL1/CTED2/RA1              | 42    | PGEC3/RPB6/ASCL2/PMA6/RB6               |

| 21    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/RB0        | 43    | RPB7/CTED3/PMA5/INT0/RB7                |

| 22    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/RB1 | 44    | RPB8/SCL1/CTED10/PMA4/RB8               |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information. 2:

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 4: Shaded pins are 5V tolerant.

#### TABLE 1-2: OSCILLATOR PINOUT I/O DESCRIPTIONS

|             | Pi                        | in Number <sup>(</sup> | 1)                     |             |                |                                                                                                                                                                                    |  |  |  |  |

|-------------|---------------------------|------------------------|------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name    | 28-pin<br>QFN             | 28-pin<br>SOIC         | 44-pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                        |  |  |  |  |

| Oscillators |                           |                        |                        |             |                |                                                                                                                                                                                    |  |  |  |  |

| CLKI        | 6                         | 9                      | 30                     | Ι           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                             |  |  |  |  |

| CLKO        | 7                         | 10                     | 31                     | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |  |

| OSC1        | 6                         | 9                      | 30                     | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |  |  |  |  |

| OSC2        | 7                         | 10                     | 31                     | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |  |  |  |  |

| SOSCI       | 8                         | 11                     | 33                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input;<br>CMOS otherwise.                                                                                                                  |  |  |  |  |

| SOSCO       | 9                         | 12                     | 34                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |  |  |  |  |

| REFCLKI     | PPS                       | PPS                    | PPS                    | I           | ST             | Reference Input Clock                                                                                                                                                              |  |  |  |  |

| REFCLKO     | PPS                       | PPS                    | PPS                    | 0           | _              | Reference Output Clock                                                                                                                                                             |  |  |  |  |

| -           | ST = Schmi<br>FTL = TTL i | •                      | put with CN            | MOS lev     | els            | Analog = Analog input $P = Power$ $O = Output$ $I = Input$ $PPS = Peripheral Pin Select$ $ = N/A$ "Pin Diagrams" section for device pin availability.                              |  |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

|                                             | Pin Number <sup>(1)</sup> |                |                        |                         |                             |                         |           |  |

|---------------------------------------------|---------------------------|----------------|------------------------|-------------------------|-----------------------------|-------------------------|-----------|--|

| Pin Name                                    | 28-pin<br>QFN             | 28-pin<br>SOIC | 44-pin<br>QFN/<br>TQFP | Pin Buffer<br>Type Type |                             | Description             |           |  |

|                                             |                           |                |                        | In                      | put Captu                   | re                      |           |  |

| IC1                                         | PPS                       | PPS            | PPS                    | Ι                       | ST                          | Input Capture Input 1-5 |           |  |

| IC2                                         | PPS                       | PPS            | PPS                    | I                       | ST                          |                         |           |  |

| IC3                                         | PPS                       | PPS            | PPS                    | I                       | ST                          |                         |           |  |

| IC4                                         | PPS                       | PPS            | PPS                    | I                       | ST                          |                         |           |  |

| IC5                                         | PPS                       | PPS            | PPS                    | I                       | ST                          |                         |           |  |

| <b>Legend:</b> CMOS = CMOS compatible input |                           |                | or outpu               | t                       | Analog = Analog input       | P = Power               |           |  |

| ST = Schmitt Trigger input with CN          |                           |                |                        |                         | els                         | O = Output              | l = Input |  |

| TTL = TTL input buffer                      |                           |                |                        |                         | PPS = Peripheral Pin Select | — = N/A                 |           |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

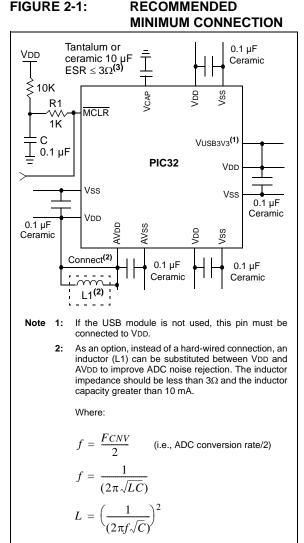

1: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

## 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **33.0 "Electrical Characteristics"** for additional information on CEFC specifications.

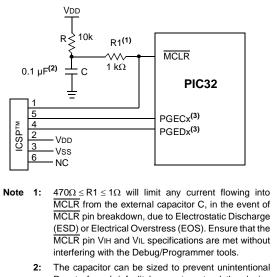

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device programming and debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS

2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

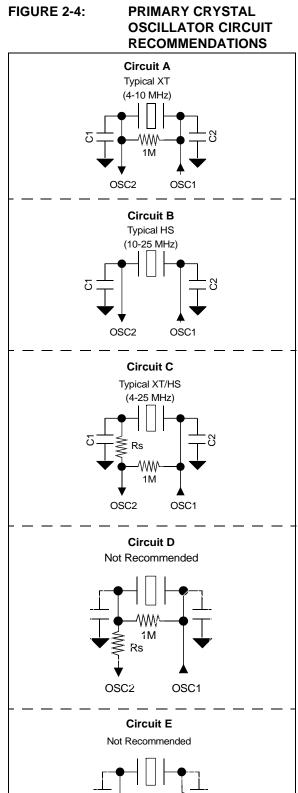

## 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

#### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

| Crystal manufacturer recommended: $C1 = C2 = 15 pF$                                                              |

|------------------------------------------------------------------------------------------------------------------|

| Therefore:                                                                                                       |

| $CLOAD = \{ ([CIN + C1] * [COUT + C2]) / [CIN + C1 + C2 + COUT] \} + estimated oscillator PCB stray capacitance$ |

| $= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 pF$                                                          |

| = {( [20][20]) / [40] } + 2.5                                                                                    |

| = 10 + 2.5 = 12.5  pF                                                                                            |

| Rounded to the nearest standard value or 13 pF in this example for Primary Oscillator crystals "C1" and "C2".    |

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro® Oscillator Design"

NOTES:

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 9-8 | IS01<1:0>: Interrupt Subpriority bits                                                                                 |  |  |  |  |  |  |  |

|         | 11 = Interrupt subpriority is 3                                                                                       |  |  |  |  |  |  |  |

|         | 10 = Interrupt subpriority is 2                                                                                       |  |  |  |  |  |  |  |

|         | 01 = Interrupt subpriority is 1                                                                                       |  |  |  |  |  |  |  |

|         | 00 = Interrupt subpriority is 0                                                                                       |  |  |  |  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |  |  |  |  |  |  |  |

| bit 4-2 | IP00<2:0>: Interrupt Priority bits                                                                                    |  |  |  |  |  |  |  |

|         | 111 = Interrupt priority is 7                                                                                         |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | •                                                                                                                     |  |  |  |  |  |  |  |

|         | 010 = Interrupt priority is 2                                                                                         |  |  |  |  |  |  |  |

|         | 001 = Interrupt priority is 1                                                                                         |  |  |  |  |  |  |  |

|         | 000 = Interrupt is disabled                                                                                           |  |  |  |  |  |  |  |

| bit 1-0 | IS00<1:0>: Interrupt Subpriority bits                                                                                 |  |  |  |  |  |  |  |

|         | 11 = Interrupt subpriority is 3                                                                                       |  |  |  |  |  |  |  |

|         | 10 = Interrupt subpriority is 2                                                                                       |  |  |  |  |  |  |  |

|         | 01 = Interrupt subpriority is 1                                                                                       |  |  |  |  |  |  |  |

|         | 00 = Interrupt subpriority is 0                                                                                       |  |  |  |  |  |  |  |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |  |  |  |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| 0                                 |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 **SUSPEND:** DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

#### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | _                 | _                 |                   | _                 |                   |                  |                  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | -                 | _                 |                   | _                 |                   |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         |                   | -                 | _                 |                   | _                 |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7:0          | _                 | _                 |                   | _                 | _                 |                   | FRMH<2:0>        |                  |  |

#### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| •                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

|              | CEGISTER II-13. UTTOR: USB TOREN REGISTER |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                                         |                   | -                 | —                 |                   | _                 |                  | —                |

| 23:16        | U-0                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                                         | -                 | -                 | —                 | _                 | _                 | -                | —                |

| 15:8         | U-0                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                                         | -                 | -                 | —                 | _                 | _                 | -                | —                |

| 7:0          | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                                           | PID<3             | 3:0>(1)           |                   | EP<3:0>           |                   |                  |                  |

#### REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

- 1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

- Note: All other values are reserved and must not be used.

- bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### 18.1 Output Compare Control Registers

#### TABLE 18-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 | 6             |       |       |       |       |       |       |      | В     | its          |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|-------|--------------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7         | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         |       | —     | -     | -     | —     | -     | —    | —     | —            | —    | —    | —     | —      | —    | —        |      | 0000         |

| 0000                        | 001001                          | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —            | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC1R  | <31:0>       |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3020                        | OC1RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC1RS | S<31:0>      |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 2000                        | 00000                           | 31:16         | _     | —     | _     | _     | —     | _     | —    | —     | —            | —    | _    | —     | —      | —    | _        | _    | 0000         |

| 3200                        | OC2CON                          | 15:0          | ON    | _     | SIDL  | -     |       |       | _    | _     | _            | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 2210                        | OC2R                            | 31:16         |       |       |       |       |       |       |      | OC2R  | .21.0.       |      |      |       |        |      |          |      | XXXX         |

| 3210                        | UC2R                            | 15:0          |       |       |       |       |       |       |      | UC2R  | <31:0>       |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16         |       |       |       |       |       |       |      | OC2RS | 2-21:05      |      |      |       |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0          |       |       |       |       |       |       |      | UCZRO | 5<31.0>      |      |      |       |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16         | _     |       |       |       | -     |       |      |       | _            | _    | —    | —     | —      | _    | _        |      | 0000         |

| 3400                        | 003001                          | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —            | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC3R  | <31:0>       |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16         |       |       |       |       |       |       |      | OC3RS | 2 - 21 - 0 - |      |      |       |        |      |          |      | XXXX         |

| 3420                        | UC3K3                           | 15:0          |       |       |       |       |       |       |      | UCSRC | 5<31.0>      |      |      |       |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16         | —     | —     | _     | _     | _     | _     |      |       | —            | —    |      | —     |        | —    | _        | —    | 0000         |

| 0000                        | 004001                          | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —            | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16         |       |       |       |       |       |       |      | OC4R  | <31.0>       |      |      |       |        |      |          |      | XXXX         |

| 0010                        |                                 | 15:0          |       |       |       |       |       |       |      | 00.11 | 101107       |      |      |       |        |      |          |      | XXXX         |

| 3620                        | OC4RS                           | 31:16         |       |       |       |       |       |       |      | OC4RS | S<31:0>      |      |      |       |        |      |          |      | XXXX         |

|                             |                                 | 15:0          |       |       |       |       |       |       |      |       |              |      |      | -     |        |      |          |      | XXXX         |

| 3800                        | OC5CON                          | 31:16         | -     | —     | -     | _     | —     | —     | —    | —     | —            | —    | —    | _     | —      |      | —        | —    | 0000         |

|                             |                                 | 15:0          | ON    | _     | SIDL  | —     | —     | _     | —    | _     | _            | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16         |       |       |       |       |       |       |      | OC5R  | <31:0>       |      |      |       |        |      |          |      | XXXX         |

|                             | <b> </b>                        | 15:0          |       |       |       |       |       |       |      |       |              |      |      |       |        |      |          |      | XXXX         |

| 3820                        | OC5RS                           | 31:16         |       |       |       |       |       |       |      | OC5RS | 6<31:0>      |      |      |       |        |      |          |      | XXXX         |

|                             |                                 |               |       |       |       |       |       |       |      |       |              |      |      |       |        |      |          |      |              |

PIC32MX1XX/2XX 28/44-PIN X

U

FAMIL

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | RCS1              | —                 | —                 | —                 | F                 | RADDR<10:8       | >                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | RADDR<7:0>        |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 22-7: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

#### Legend:

| 9                 |                               |                      |                    |  |

|-------------------|-------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit |                      | it, read as '0'    |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-15 Unimplemented: Read as '0'

bit 14 RCS1: Chip Select 1 bit

1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive (RADDR14 function is selected)

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 RADDR<13:0>: Address bits

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

#### REGISTER 24-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

1 = The ADC sample and hold amplifier is sampling

0 = The ADC sample/hold amplifier is holding

When ASAM = 0, writing '1' to this bit starts sampling.

When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 DONE: Analog-to-Digital Conversion Status bit<sup>(3)</sup>

1 = Analog-to-digital conversion is done

0 = Analog-to-digital conversion is not done or has not started Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

#### REGISTER 24-4: AD1CHS: ADC INPUT SELECT REGISTER (CONTINUED)

bit 20-16 CH0SA<4:0>: Positive Input Select bits for Sample A Multiplexer Setting

|      | 11111 = Reserved                                                                                                                                                                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | 10010 = Reserved<br>10001 = Channel 0 positive input is VDD/2<br>10000 = Channel 0 positive input is VBAT<br>01111 = Reserved<br>01110 = Channel 0 positive input is IVREF <sup>(1)</sup><br>01101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup><br>01100 = Channel 0 positive input is AN12 <sup>(3)</sup> |

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | •                                                                                                                                                                                                                                                                                                                                          |

|      | 00001 = Channel 0 positive input is AN1<br>00000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                         |

| 15-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                 |

|      |                                                                                                                                                                                                                                                                                                                                            |

Note 1: See 26.0 "Comparator Voltage Reference (CVREF)" for more information.

- 2: See 28.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.

bit

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                     |                   | _                 | _                 |                  | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | _                 |                   | _                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

|              | EVPOL             | _<1:0>            | _                   | CREF              | _                 | _                 | CCH              | <1:0>            |

#### REGISTER 25-1: CMXCON: COMPARATOR CONTROL REGISTER

#### Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

#### bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

#### bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 **Unimplemented:** Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

#### 29.3.4 DEEP SLEEP MODE

Deep Sleep mode brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device.

#### • Deep Sleep

In this mode, the CPU, RAM and most peripherals are powered down. Power is maintained to the DSGPR0 register and one or more of the RTCC, DSWDT and DSGPR1 through DSGPR32 registers.

Which of these peripherals is active depends on the state of the following register bits when Deep Sleep mode is entered:

#### • RTCDIS (DSCON<12>)

This bit must be set to disable the RTCC in Deep Sleep mode (see Register 29-1).

#### • DSWDTEN (DEVCFG2<30>)

This Configuration bit must be set to enable the DSWDT register in Deep Sleep mode (see Register 30-3)

#### • DSGPREN (DSCON<13>)

This bit must be set to enable the DSGPR1 through DSGPR32 registers in Deep Sleep mode (see Register 29-1).

Note: The Deep Sleep Control registers can only be accessed after the system unlock sequence has been performed. In addition, the Deep Sleep Control registers must be written twice.

In addition to the conditionally enabled peripherals described above, the MCLR filter and INT0 pin are enabled in Deep Sleep mode.

#### 29.3.5 VBAT MODE

VBAT mode is similar to Deep Sleep mode, except that the device is powered from the VBAT pin. VBAT mode is controlled strictly by hardware, without any software intervention. VBAT mode is initiated when VDD falls VPOR (refer the 33.0 "Electrical below to Characteristics" for definitions of VDD and VPOR). An external power source must be connected to the VBAT pin before power is removed from VDD to enter VBAT mode. VBAT is the lowest battery-powered mode that can maintain an RTCC. Wake-up from VBAT mode can only occur when VDD is reapplied. The wake-up will appear to be a POR to the rest of the device.

In VBAT mode, the Deep Sleep Watchdog Timer is disabled. The RTCC and DSGPR1 through DSGPR32 registers may be enabled or disabled depending on the state of the RTCDIS bit (DSCON<12>) and the DSGPREN bit (DSCON<13>), respectively. Deep Sleep Persistent General Purpose Register 0 (DSGPR0) is always enabled in VBAT mode.

#### 29.3.6 XLP POWER-SAVING MODES

Figure 29-1 shows a block diagram of the system domain for XLP devices and the related power-saving features. The various blocks are controlled by the following Configuration bit settings and SFRs:

- DSBOREN (DEVCFG2<20>)

- DSEN (DSCON<15>)

- DSGPREN (DSCON<13>)

- DSWDTEN (DEVCFG2<30>)

- DSWDTOSC (DEVCFG2<29>)

- RELEASE (DSCON<0>)

- RTCCLKSEL (RTCCON <9:8>)

- RTCDIS (DSCON<12>)

- SLPEN (OSCCON<4>)

- VREGS (PWRCON<0>)

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|----------------------|-------------------|-----------------------|------------------|--|

| 04-04        | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   |                      | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                      |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                      |                   |                       |                  |  |

| 7:0          | R                           | R                 | R                   | R                 | R                    | R                 | R                     | R                |  |

|              |                             |                   |                     | DEVID<            | <7:0> <sup>(1)</sup> |                   |                       |                  |  |

#### Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and munfacture of development systems is ISO 9001:2000 certified.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0583-2