Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| peed                      | 72MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| eripherals                | Brown-out Detect/Reset, DMA, HLVD, I2S, POR, PWM, WDT                           |

| lumber of I/O             | 17                                                                              |

| rogram Memory Size        | 256KB (256K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 64K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                     |

| ata Converters            | A/D 9x10b                                                                       |

| scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| lounting Type             | Surface Mount                                                                   |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package   | 28-SOIC                                                                         |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx274f256bt-v-so |

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES WITHOUT VBAT

28-PIN SOIC (TOP VIEW)(1,2,3)

28

SOIC

PIC32MX254F128B PIC32MX274F256B

| Pin# | Full Pin Name                                     |

|------|---------------------------------------------------|

| 1    | MCLR                                              |

| 2    | PGED3/VREF+/AN0/C3INC/RPA0/ASDA1/CTED1/PMD7/RA0   |

| 3    | PGEC3/VREF-/AN1/RPA1/ASCL1/CTED2/PMD6/RA1         |

| 4    | PGED2/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         |

| 5    | PGEC2/AN3/C1INC/C2INA/LVDIN/RPB1/CTED12/PMD1//RB1 |

| 6    | PGED1/AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2   |

| 7    | PGEC1/AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3     |

| 8    | Vss                                               |

| 9    | OSC1/CLKI/RPA2/RA2                                |

| 10   | OSC2/CLKO/RPA3/PMA0/RA3                           |

| 11   | SOSCI/RPB4/CTED11/RB4 <sup>(4)</sup>              |

| 12   | SOSCO/RPA4/T1CK/CTED9/RA4                         |

| 13   | VDD                                               |

| 14   | TMS/RPB5/USBID/RB5                                |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | VBUS                                           |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19   | Vss                                            |

| 20   | VCAP                                           |

| 21   | D+                                             |

| 22   | D-                                             |

| 23   | Vusb3v3                                        |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMA1/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27   | AVss                                           |

| 28   | AVDD                                           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and 12.3 "Peripheral Pin Select" for restrictions

- 2: Every I/O port pin (RAx-RBx) can be used as a change notification pin (CNAx-CNBx). See 12.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

- 4: This is an input-only pin.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/44-pin XLP Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note:

The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

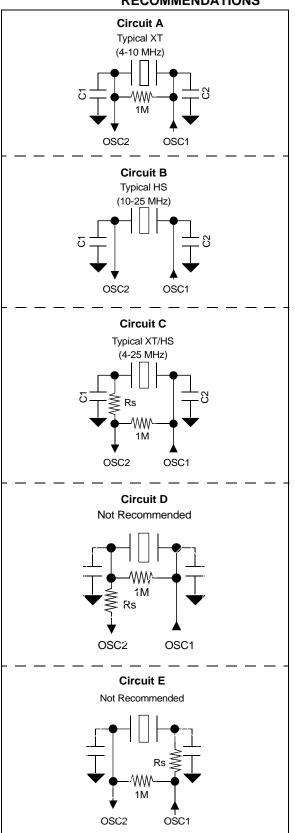

## 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: CI = C2 = 15 \ pF

Therefore:

CLOAD = \{([CIN + CI]^*[COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 \ pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 \ pF

Rounded to the nearest standard value or 13 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro® Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-1             | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | BMX<br>CHEDMA     | _                | _                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        |                   | -                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | BMXARB<2:0:      | >                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-27 Unimplemented: Read as '0'

bit 26 BMXCHEDMA: BMX PFM Cacheability for DMA Access bit

- 1 = Enable Program Flash memory (data) cacheability for DMA accesses (requires cache to have data caching enabled)

- 0 = Disable program Flash memory (data) cacheability for DMA accesses (hits are still read from the cache, but misses do not update the cache)

- bit 25-21 Unimplemented: Read as '0'

- bit 20 BMXERRIXI: Enable Bus Error from IXI bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus

- 0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus

- bit 19 BMXERRICD: Enable Bus Error from ICD Debug Unit bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from ICD

- 0 = Disable bus error exceptions for unmapped address accesses initiated from ICD

- bit 18 BMXERRDMA: Bus Error from DMA bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from DMA

- 0 = Disable bus error exceptions for unmapped address accesses initiated from DMA

- bit 17 BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)

- 1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access

- 0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access

- bit 16 BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)

- 1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access

- 0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access

- bit 15-7 Unimplemented: Read as '0'

- bit 6 BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit

- 1 = Data RAM accesses from CPU have one wait state for address setup

- 0 = Data RAM accesses from CPU have zero wait states for address setup

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 BMXARB<2:0>: Bus Matrix Arbitration Mode bits

- 111 = Reserved (using these Configuration modes will produce undefined behavior)

:

- 011 = Reserved (using these Configuration modes will produce undefined behavior)

- 010 = Arbitration Mode 2

- 001 = Arbitration Mode 1 (default)

- 000 = Arbitration Mode 0

**NOTES:**

#### 7.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupt Controller"** (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

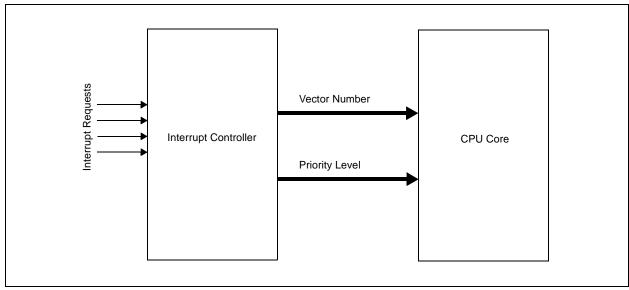

PIC32MX1XX/2XX 28/44-pin XLP Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/44-pin XLP Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- · User-configurable interrupt vector spacing

**Note:** The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/44-pin XLP Family devices.

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| Ç      |

|--------|

| 2600   |

| 710    |

| 104A   |

| \-page |

| ge 9   |

| 7      |

| TABLE 9-3: DMA CHA | NNELS 0-3 REGISTER | MAP (CONTINUED) |

|--------------------|--------------------|-----------------|

|--------------------|--------------------|-----------------|

| ess                         |                                 | 0             |                   |       |       |       |       |       |      | Bi     | ts           |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|-------------------|-------|-------|-------|-------|-------|------|--------|--------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15             | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7         | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      |              | _      |        | _      | _      | _      | _      | _      | 0000       |

| 0200                        | DOTIZOT TIX                     | 15:0          |                   |       |       |       |       |       |      | CHCPT  | R<15:0>      |        |        |        |        |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      | -            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3290                        | DOTIZDAT                        | 15:0          | _                 | _     | _     | _     | _     | _     | _    | _      |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 3210                        | DCH3CON                         | 31:16         |                   | _     | _     | _     | _     |       | _    | _      | 1            | -      |        | _      |        | _      | _      | _      | 0000       |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY            | _     | _     | _     | _     | _     | _    | CHCHNS | CHEN         | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      |              |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 02D0                        | DOI IOLOOIN                     | 15:0          |                   |       |       |       |       |       |      |        |              |        |        |        | FF00   |        |        |        |            |

| 32C0                        | DCH3INT                         | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      | CHSDIE       | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        | DOTTON                          | 15:0          |                   |       |       |       |       |       |      |        |              |        | 0000   |        |        |        |        |        |            |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 |                   |       |       |       |       |       |      |        |              |        |        |        |        | 0000   |        |        |            |

| 32E0                        | DCH3DSA                         | 31:16         |                   |       |       |       |       |       |      | CHDSA  | <31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |                   |       |       |       |       |       |      |        |              |        |        |        |        |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 31:16         | _                 | _     | _     | _     | _     | _     | _    | -      | 7 45:0       | _      | _      |        | _      | _      | _      | _      | 0000       |

| -                           |                                 | 15:0          |                   |       |       |       |       |       |      | CHSSIZ |              |        |        |        |        |        |        |        | 0000       |

| 3300                        | DCH3DSIZ                        | 31:16<br>15:0 | _                 |       | _     |       |       |       | _    | CHDSIZ | —<br>7<15:0> | _      |        |        |        | _      | _      | _      | 0000       |

| -                           |                                 | 31:16         | _                 |       | _     | _     |       |       |      |        |              | _      |        |        |        | _      | _      | _      | 0000       |

| 3310                        | DCH3SPTR                        | 15:0          |                   |       |       |       |       |       |      | CHSPTF | R<15:0>      |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _                 |       | _     | _     |       | _     | _    | _      | _            | _      | _      |        | _      | _      | _      | _      | 0000       |

| 3320                        | DCH3DPTR                        | 15:0          |                   |       |       |       |       |       |      | CHDPT  | R<15:0>      |        |        |        |        |        |        |        | 0000       |

|                             | DOLLOGO 17                      | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3330                        | DCH3CSIZ                        | 15:0          |                   |       |       |       |       |       |      | CHCSIZ | Z<15:0>      |        |        |        |        |        |        |        | 0000       |

| 2240                        | DCH3CPTR                        | 31:16         | _                 | _     | _     | _     | _     | _     | _    | _      | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3340                        | DCH3CPTR                        | 15:0          | CHCPTR<15:0> 0000 |       |       |       |       |       |      |        |              |        |        | 0000   |        |        |        |        |            |

| 3350                        | DCH3DAT                         | 31:16         | _                 |       | _     | _     | _     | _     | _    | _      | _            | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3330                        | DOLIODAL                        | 15:0          | _                 |       | _     | _     | _     |       | _    | _      |              |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information. Note 1:

#### REGISTER 10-2: CHEACC: CACHE ACCESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | CHEWEN            | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | -                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | CHEID             | X<3:0>           |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 **CHEWEN:** Cache Access Enable bits for registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3

1 = The cache line selected by CHEIDX<3:0> is writeable

0 = The cache line selected by CHEIDX<3:0> is not writeable

bit 30-4 **Unimplemented:** Write '0'; ignore read bit 3-0 **CHEIDX<3:0>:** Cache Line Index bits

The value selects the cache line for reading or writing.

TABLE 12-5: PORTC REGISTER MAP

| ess                         | _                                 |           |       |       |       |       |       |       |          |          | Bits     |          |          |          |          |          |          |          | ,,         |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8     | 23/7     | 22/6     | 21/5     | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     | _     | _     | _     | _     | _     | _     | _        | _        | _        | _        | _        | _        | _        | _        | _        |          | 0000       |

| 0200                        | ANOLLO                            | 15:0      | _     | _     | _     | _     |       |       | _        | _        |          | _        | _        |          | ANSC3    | ANSC2    | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | _     | _     | _     | _     | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | 0000       |

| 0210                        | 111100                            | 15:0      | _     | _     | _     | _     | _     | _     | TRISC9   | TRISC8   | TRISC7   | TRISC6   | TRISC5   | TRISC4   | TRISC3   | TRISC2   | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | _     | _     | _     | _     | _     | _     | _        | _        | _        | _        | _        |          |          |          |          |          | 0000       |

| 0220                        | 101110                            | 15:0      | _     | _     | _     | _     | _     | _     | RC9      | RC8      | RC7      | RC6      | RC5      | RC4      | RC3      | RC2      | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | _     | _     | _     | _     | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | 0000       |

| 0200                        |                                   | 15:0      | _     |       | _     | _     | _     | _     | LATC9    | LATC8    | LATC7    | LATC6    | LATC5    | LATC4    | LATC3    | LATC2    | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     | _     | -     | _     | _     | _     | _     | _        | _        | _        | _        | _        | _        | _        | _        | _        | -        | 0000       |

| 0240                        |                                   | 15:0      |       |       | _     |       |       |       | ODCC9    | ODCC8    | ODCC7    | ODCC6    | ODCC5    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | ODCC0    | 0000       |

| 6250                        | CNPUC                             | 31:16     |       |       | _     |       |       |       | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | 0000       |

| 0200                        |                                   | 15:0      | _     |       |       |       |       |       | CNPUC9   | CNPUC8   | CNPUC7   | CNPUC6   | CNPUC5   | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | CNPUC0   | 0000       |

| 6260                        | CNPDC                             | 31:16     | _     |       |       |       |       |       | _        | _        | _        | _        | _        |          | _        | _        | _        | _        | 0000       |

| 0200                        |                                   | 15:0      | _     | _     |       | _     |       |       | CNPDC9   | CNPDC8   | CNPDC7   | CNPDC6   | CNPDC5   | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | CNPDC0   | 0000       |

| 6270                        | CNCONC                            | 31:16     | _     | _     | _     | _     |       |       | _        |          |          | _        |          |          |          | _        | _        | _        | 0000       |

| 0210                        |                                   | 15:0      | ON    |       | SIDL  |       |       |       | _        |          |          | _        |          |          |          | _        |          |          | 0000       |

| 6280                        | CNENC                             | 31:16     | _     |       |       |       |       |       | _        | _        |          | _        | _        |          | _        | _        | _        | _        | 0000       |

| 3200                        |                                   | 15:0      | _     | _     |       | _     |       |       | CNIEC9   | CNIEC8   | CNIEC7   | CNIEC6   | CNIEC5   | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | CNIEC0   | 0000       |

| 6290                        | CNSTATC                           | 31:16     | _     | _     |       | _     |       |       | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        | 0000       |

| 0200                        | 0.101/110                         | 15:0      | _     | _     | _     | _     |       | _     | CNSTATC9 | CNSTATC8 | CNSTATC7 | CNSTATC6 | CNSTATC5 | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

PORTC is not available on 28-pin devices.

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized

0 = External clock input is not synchronized

When TCS = 0:

This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit

1 = External clock is defined by the TECS<1:0> bits

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### 15.1 Watchdog Timer Control Registers

#### TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | σ         |       | Bits  |       |       |             |       |      |      |          |      |      |      |      |      |      | S    |           |

|---------------------------|-----------------------|-----------|-------|-------|-------|-------|-------------|-------|------|------|----------|------|------|------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8 | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| F000                      | WDTCON <sup>(1)</sup> | 31:16     |       |       |       |       |             |       |      | WDTO | CLRKEY<1 | 5:0> |      |      |      |      |      |      | 0000      |

| F600                      | WDTCON                | 15:0      | ON    | _     | _     |       | RUNDIV<4:0> |       |      |      |          |      |      |      |      | xxxx |      |      |           |

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

### 17.1 Input Capture Control Registers

#### TABLE 17-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

| ess                         |                       |               |       |                                         |       |       |       |       |       | Bi       | ts       |      |      |      |        |      |            |      | "          |

|-----------------------------|-----------------------|---------------|-------|-----------------------------------------|-------|-------|-------|-------|-------|----------|----------|------|------|------|--------|------|------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14                                   | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8     | 23/7     | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1       | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         | _     | _                                       | _     | _     | _     | _     | _     | _        | _        | _    | _    | _    | _      | _    | _          | _    | 0000       |

| 2000                        | IC ICON.              | 15:0          | ON    | _                                       | SIDL  | _     | _     | _     | FEDGE | C32      | ICTMR    | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000       |

| 2010                        | IC1BUF                | 31:16         |       |                                         |       |       |       |       |       | IC1BUF   | <31.0>   |      |      |      |        |      |            |      | xxxx       |

| 2010                        |                       | 15:0          |       |                                         |       |       |       |       |       | 101501   |          |      |      |      |        |      |            |      | xxxx       |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         | _     | _                                       | _     | _     | _     | _     | _     | _        | _        | -    | _    | _    | _      | _    | _          | _    | 0000       |

| 2200                        | 1020011               | 15:0          | ON    | 1.222 1.22 1.22 1.22 1.22 1.22 1.22 1.2 |       |       |       |       |       |          |          |      |      |      |        | 0000 |            |      |            |

| 2210                        | IC2BUF                | 31:16<br>15:0 |       | IC2BUF<31:0>                            |       |       |       |       |       |          |          |      |      |      | -      |      |            |      |            |

|                             |                       | 21.16         |       | _                                       | _     | _     | _     | _     | _     |          | _        | _    |      | _    | _      | _    | _          | _    | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0          | ON    |                                         | SIDL  |       |       |       | FEDGE | C32      | ICTMR    | ICI< | 1:0> | ICOV | ICBNE  | _    | ICM<2:0>   | _    | 0000       |

|                             |                       | 31:16         | 011   |                                         | OIDL  |       |       |       | TEDOL | 002      | TOTIVITO | 101< | 1.02 | 1001 | IODIVE |      | 10101<2.0> |      | xxxx       |

| 2410                        | IC3BUF                | 15:0          |       |                                         |       |       |       |       |       | IC3BUF   | <31:0>   |      |      |      |        |      |            |      | xxxx       |

|                             | (1)                   | 31:16         | _     | _                                       | _     | _     | _     | _     | _     | _        | _        | _    | _    | _    | _      | _    | _          | _    | 0000       |

| 2600                        | IC4CON <sup>(1)</sup> | 15:0          | ON    | _                                       | SIDL  | _     | _     | _     | FEDGE | C32      | ICTMR    | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000       |

| 0040                        | IC4BUF                | 31:16         |       |                                         |       |       |       |       |       | IO ADUIT | . 04.0   |      |      |      |        | ,    |            |      | xxxx       |

| 2610                        | IC4BUF                | 15:0          |       |                                         |       |       |       |       |       | IC4BUF   | <31:0>   |      |      |      |        |      |            |      | xxxx       |

| 2000                        | IC5CON <sup>(1)</sup> | 31:16         | _     | _                                       | _     | _     | _     | _     | _     | _        | _        | _    | ı    | _    | _      | _    | _          | _    | 0000       |

| 2000                        | ICOCON.               | 15:0          | ON    | —                                       | SIDL  | _     | _     | _     | FEDGE | C32      | ICTMR    | ICI< | 1:0> | ICOV | ICBNE  | , .  | ICM<2:0>   |      | 0000       |

| 2810                        | IC5BUF                | 31:16         |       |                                         |       |       |       |       |       | IC5BUF   | ~31·0~   |      |      |      |        |      |            |      | xxxx       |

| 2010                        |                       | 15:0          |       | Dagati                                  |       |       |       |       |       |          |          |      |      |      |        |      |            |      | xxxx       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

### 20.1 I<sup>2</sup>C Control Registers

#### TABLE 20-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 | •             |         |        |       |        |                              |                                       |        | Bi    | ts    |       |             |               |          |      |      |      |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|------------------------------|---------------------------------------|--------|-------|-------|-------|-------------|---------------|----------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11                        | 26/10                                 | 25/9   | 24/8  | 23/7  | 22/6  | 21/5        | 20/4          | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 5000                        | I2C1CON                         | 31:16         | _       | _      |       |        |                              | _                                     | _      |       |       |       |             | _             |          |      |      | _    | 0000       |

|                             |                                 | 15:0          | ON      |        | SIDL  | SCLREL | STRICT                       | A10M                                  | DISSLW | SMEN  | GCEN  | STREN | ACKDT       | ACKEN         | RCEN     | PEN  | RSEN | SEN  | 1000       |

| 5010                        | I2C1STAT                        | 31:16         | _       |        |       |        |                              | _                                     | -      | -     |       | -     | _           | _             | _        | _    | _    |      | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT |       |        |                              | BCL                                   | GCSTAT | ADD10 | IWCOL | I2COV | D_A         | Р             | S        | R_W  | RBF  | TBF  | 0000       |

| 5020                        | I2C1ADD                         | 31:16<br>15:0 | _       | _      |       | _      | _                            | _                                     | _      | _     | _     | _     |             | Dogiotor      | _        | _    | _    | _    | 0000       |

|                             |                                 | 31:16         | _       |        |       |        |                              | Address Register                      |        |       |       |       |             |               |          |      | 0000 |      |            |

| 5030                        | I2C1MSK                         | 15:0          | _       |        |       |        |                              |                                       |        |       |       |       |             |               |          |      | 0000 |      |            |

|                             |                                 | 31:16         |         |        |       |        |                              |                                       | _      |       |       | _     | Address IVI | ask ivegister | _        | _    | _    | _    | 0000       |

| 5040                        | I2C1BRG                         | 15:0          | _       | _      |       | _      |                              |                                       |        |       |       |       |             |               |          | 0000 |      |      |            |

|                             |                                 | 31:16         | _       | _      |       | _      | _                            | _                                     | _      | _     | _     | _     | —           | _             | _        | _    | _    | _    | 0000       |

| 5050                        | I2C1TRN                         | 15:0          | _       | _      |       | _      |                              |                                       | _      |       |       |       |             | Transmit      | Register |      |      |      | 0000       |

|                             |                                 | 31:16         | _       | _      |       | _      | _                            | _                                     | _      | _     | _     | _     | _           | _             |          | _    | _    | _    | 0000       |

| 5060                        | I2C1RCV                         | 15:0          | _       | _      | _     | _      | _                            | _                                     | _      | _     |       |       |             | Receive       | Register |      |      |      | 0000       |

| 5400                        | 1000001                         | 31:16         | _       | _      | _     | _      | _                            | _                                     | _      | _     | _     | _     | _           | _             | _        | _    | _    | _    | 0000       |

| 5100                        | I2C2CON                         | 15:0          | ON      | _      | SIDL  | SCLREL | STRICT                       | A10M                                  | DISSLW | SMEN  | GCEN  | STREN | ACKDT       | ACKEN         | RCEN     | PEN  | RSEN | SEN  | 1000       |

| 5110                        | I2C2STAT                        | 31:16         | _       | _      | _     | _      | _                            | _                                     | _      | _     | _     | _     | _           | _             | _        | _    | _    | _    | 0000       |

| 3110                        | 120231A1                        | 15:0          | ACKSTAT | TRSTAT | _     | _      | _                            | BCL                                   | GCSTAT | ADD10 | IWCOL | I2COV | D_A         | Р             | S        | R_W  | RBF  | TBF  | 0000       |

| 5120                        | I2C2ADD                         | 31:16         | _       | _      | _     | _      | _                            | 1                                     | _      | _     | _     | 1     | _           | _             | 1        | _    | _    | -    | 0000       |

| 3120                        | IZCZADD                         | 15:0          | _       | _      |       | _      | _                            |                                       |        |       |       |       | Address     | Register      |          |      |      |      | 0000       |

| 5130                        | I2C2MSK                         | 31:16         | _       | _      | _     | _      | _                            | _                                     | _      | _     | _     | _     | _           | _             | _        | _    | _    | _    | 0000       |

| 0100                        | IZOZIVIOIX                      | 15:0          | _       | _      | _     | _      | _                            | _                                     |        |       |       |       | Address Ma  | ask Register  | ·        |      |      |      | 0000       |

| 5140                        | I2C2BRG                         | 31:16         | _       | _      |       | _      | _                            | _                                     | _      | _     |       | _     | _           | _             | _        | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | _       | _      |       | _      |                              | · · · · · · · · · · · · · · · · · · · |        |       |       |       |             |               |          | 0000 |      |      |            |

| 5150                        | I2C2TRN                         | 31:16         | _       | _      |       | _      | _                            | _                                     | _      | _     | _     | _     | _           |               | _        | _    | _    | _    | 0000       |

|                             |                                 | 15:0          |         | _      |       | _      | _                            | _                                     | _      | _     |       |       |             | Transmit      | Register |      |      |      | 0000       |

| 5160                        | I2C2RCV                         | 31:16         | _       |        |       | _      | _                            |                                       | _      |       | _     | _     | _           |               |          | _    | _    | _    | 0000       |

|                             |                                 | 15:0          | _       | _      |       | _      | —   —   —   Receive Register |                                       |        |       |       |       |             |               |          | 0000 |      |      |            |

PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### 21.1 UART Control Registers

#### TABLE 21-1: UART1 AND UART2 REGISTER MAP

| ess                         | Register<br>Name      |           | Bits                            |        |        |       |        |       |           |            |             |         |       |          |          |       |        |        |            |

|-----------------------------|-----------------------|-----------|---------------------------------|--------|--------|-------|--------|-------|-----------|------------|-------------|---------|-------|----------|----------|-------|--------|--------|------------|

| Virtual Address<br>(BF80_#) |                       | Bit Range | 31/15                           | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9      | 24/8       | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0   | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _                               | _      | _      | 1     |        | _     |           | _          | SLPEN       | ACTIVE  |       | 1        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

| 0000                        |                       | 15:0      | ON                              | -      | SIDL   | IREN  | RTSMD  | _     | UEN-      | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | MASK<7:0>                       |        |        |       |        |       |           |            | ADDR<7:0>   |         |       |          |          |       |        | 0000   |            |

|                             | OTOTA'                | 15:0      | UTXISE                          | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF     | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

| 6020                        | U1TXREG               | 31:16     | _                               | _      | _      | -     | _      | _     | 1         | _          | _           | _       | _     | 1        | _        | _     | _      | _      | 0000       |

| 0020                        | UTIAREG               | 15:0      | _                               | 1      | _      | 1     | _      | _     | 1         | TX8        |             |         |       | Transmit | Register |       |        |        | 0000       |

| 6030                        | U1RXREG               | 31:16     |                                 | _      | _      | -     | _      | _     | 1         | _          | _           | _       | _     | 1        | _        | _     | _      | _      | 0000       |

| 0030                        |                       | 15:0      | _                               | -      | _      | 1     | _      | _     | I         | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | _                               | 1      | _      | 1     | _      | _     | 1         | 1          | _           | _       | 1     | 1        | 1        | _     | _      | _      | 0000       |

| 0040                        | OTDINO                | 15:0      | Baud Rate Generator Prescaler 0 |        |        |       |        |       |           |            |             |         |       |          |          |       | 0000   |        |            |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | _                               | _      | _      | _     | _      | _     | _         | _          | SLPEN       | ACTIVE  | _     | _        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

| 0200                        |                       | 15:0      | ON                              | _      | SIDL   | IREN  | RTSMD  |       | UEN-      | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | 6 MASK<7:0>                     |        |        |       |        |       | ADDR<7:0> |            |             |         |       |          | 0000     |       |        |        |            |

| 0210                        |                       | 15:0      | UTXISE                          | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF     | TRMT       | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

| 6220                        | U2TXREG               | 31:16     | _                               | _      | _      | 1     | -      |       | _         | _          | _           | _       | _     | _        | _        | _     | _      | _      | 0000       |

| 6220                        |                       | 15:0      | _                               | _      | _      | -     | -      | -     | _         | TX8        |             |         |       | Transmit | Register |       |        |        | 0000       |

| 6230                        | U2RXREG               | 31:16     | _                               | 1      | _      | 1     |        |       | I         | -          | _           | _       |       | 1        | -        | _     | _      | _      | 0000       |

|                             |                       | 15:0      | _                               | -      |        | 1     | -      |       | 1         | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 6240                        | U2BRGU -              | 31:16     | _                               | _      | _      |       | _      | _     | _         | _          | _           | _       | _     |          | _        | _     | _      | _      | 0000       |

| 0240                        |                       | 15:0      | •                               |        |        | •     |        |       | Bau       | d Rate Gen | erator Pres | caler   |       |          |          | •     | •      |        | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.2 "CLR, SET and INV Registers" for more information.

**NOTES:**

#### REGISTER 22-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | _                 | _                 |                   | _                 | _                 | _                | _                |  |  |  |

| 00:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | CS1               | _                 | _                 | _                 |                   | ADDR<10:8>       | ,                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 14 CS1: Chip Select 1 bit

1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

bit 13-11 **Unimplemented:** Read as '0'

bit 10-0 ADDR<10:0>: Destination Address bits

#### REGISTER 22-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 | -                 | -                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

**Legend:** HSC = Set by Hardware; Cleared by Software

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

#### REGISTER 30-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

```

11111111 = Disabled

111111110 = 0xBD00_0FFF

111111101 = 0xBD00_1FFF

111111100 = 0xBD00_2FFF

11111011 = 0xBD00_3FFF

111111010 = 0xBD00_4FFF

11111001 = 0xBD00_5FFF

111111000 = 0xBD00_6FFF

11110111 = 0xBD00_7FFF

11110110 = 0xBD00_8FFF

11110101 = 0xBD00_9FFF

11110100 = 0xBD00_AFFF

11110011 = 0xBD00_BFFF

11110010 = 0xBD00_CFFF

11110001 = 0xBD00_DFFF

11110000 = 0xBD00_EFFF

11101111 = 0xBD00_FFFF

10111111 = 0xBD03 FFFF

10111110 = Reserved

000000000 = Reserved

```

- bit 11-5 Reserved: Write '1'

- bit 4-3 ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits<sup>(2)</sup>

- 11 = PGEC1/PGED1 pair is used

- 10 = PGEC2/PGED2 pair is used

- 01 = PGEC3/PGED3 pair is used

- 00 = PGEC4/PGED4 pair is used(2)

- bit 2 **JTAGEN:** JTAG Enable bit<sup>(1)</sup>

- 1 = JTAG is enabled

- 0 = JTAG is disabled

- bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 1x = Debugger is disabled

- 0x = Debugger is enabled

- **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

#### REGISTER 30-2: **DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)** bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits 11 = PBCLK is SYSCLK divided by 8 10 = PBCLK is SYSCLK divided by 4 01 = PBCLK is SYSCLK divided by 2 00 = PBCLK is SYSCLK divided by 1 bit 11 Reserved: Write '1' bit 10 OSCIOFNC: CLKO Enable Configuration bit 1 = CLKO output disabled 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00) bit 9-8 POSCMOD<1:0>: Primary Oscillator Configuration bits 11 = Primary Oscillator is disabled 10 = HS Oscillator mode is selected 01 = XT Oscillator mode is selected 00 = External Clock mode is selected bit 7 IESO: Internal External Switchover bit 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled) 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled) Reserved: Write '1' bit 6 FSOSCEN: Secondary Oscillator Enable bit bit 5 1 = Enable Secondary Oscillator 0 = Disable Secondary Oscillator bit 4-3 Reserved: Write '1' bit 2-0 FNOSC<2:0>: Oscillator Selection bits 111 = Fast RC Oscillator with divide-by-N (FRCDIV) 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler 101 = Low-Power RC Oscillator (LPRC) 100 = Secondary Oscillator (Sosc) 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL) 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup> 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL) 000 = Fast RC Oscillator (FRC)

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.