Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 72MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx274f256d-v-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                    | -     |

|-------|----------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    |       |

| 3.0   | CPU                                                |       |

| 4.0   | Memory Organization                                |       |

| 5.0   | Flash Program Memory                               |       |

| 6.0   | Resets                                             |       |

| 7.0   | Interrupt Controller                               |       |

| 8.0   | Oscillator Configuration                           |       |

| 9.0   | Direct Memory Access (DMA) Controller              |       |

| 10.0  | Prefetch Cache                                     |       |

| 11.0  | USB On-The-Go (OTG)                                |       |

|       | I/O Ports                                          |       |

| 13.0  | Timer1                                             |       |

| 14.0  | Timer2/3, Timer4/5                                 |       |

| 15.0  | Watchdog Timer (WDT)                               |       |

| 16.0  | Deep Sleep Watchdog Timer (DSWDT)                  |       |

| 17.0  | Input Capture                                      | . 179 |

|       | Output Compare                                     |       |

| 19.0  | Serial Peripheral Interface (SPI)                  |       |

| 20.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |       |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART) |       |

|       | Parallel Master Port (PMP)                         |       |

|       | Real-Time Clock and Calendar (RTCC)                |       |

| 24.0  | 10-bit Analog-to-Digital Converter (ADC)           |       |

| 25.0  | Comparator                                         | . 245 |

| 26.0  | Comparator Voltage Reference (CVREF)               | . 249 |

| 27.0  | High/Low-Voltage Detect (HLVD)                     |       |

| 28.0  | Charge Time Measurement Unit (CTMU)                | . 257 |

| 29.0  | Power-Saving Features                              | . 263 |

| 30.0  | Special Features                                   | . 277 |

| 31.0  | Instruction Set                                    |       |

| 32.0  | Development Support                                | . 293 |

| 33.0  | Electrical Characteristics                         | . 297 |

|       | DC and AC Device Characteristics Graphs            |       |

| 35.0  | Packaging Information                              | . 345 |

|       | Vicrochip Web Site                                 |       |

|       | omer Change Notification Service                   |       |

| Custo | omer Support                                       | . 361 |

| Produ | uct Identification System                          | . 362 |

# 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This document contains device-specific information for PIC32MX1XX/2XX 28/44-pin XLP Family devices.

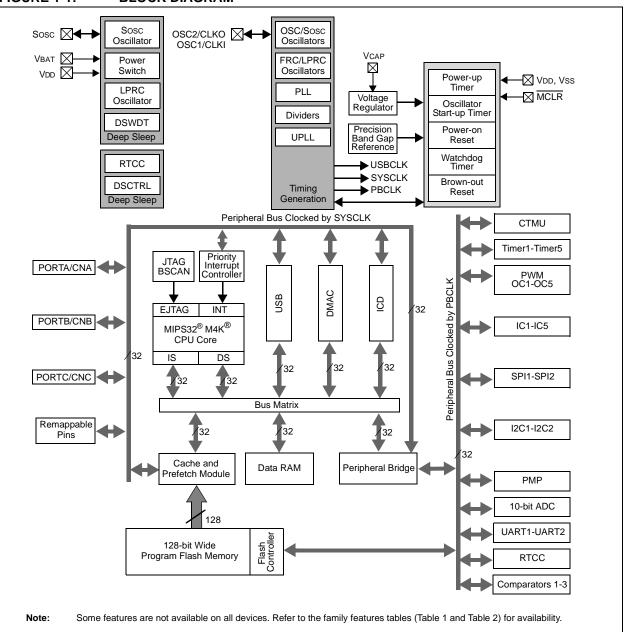

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX1XX/2XX 28/44-pin XLP Family of devices.

Table 1-1 through Table 1-16 list the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1: BLOCK DIAGRAM

| <b>TABLE 1-13</b> : | <b>USB PINOUT I/O DESCRIPTIONS</b> |

|---------------------|------------------------------------|

|---------------------|------------------------------------|

|          | Pin Number <sup>(1,2)</sup>                                                           |                                           |             |                                                                    |                                   |                                                                     |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------|-------------------------------------------|-------------|--------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 28-pin<br>QFN28-pin<br>SOIC44-pin<br>QFN/<br>TQFPPin<br>TypeBuffer<br>TypeDescription |                                           | Description |                                                                    |                                   |                                                                     |  |  |  |  |  |

|          | Universal Serial Bus                                                                  |                                           |             |                                                                    |                                   |                                                                     |  |  |  |  |  |

| VBUS     | 12                                                                                    | 15                                        | 42          | I                                                                  | Analog                            | USB Bus Power Monitor                                               |  |  |  |  |  |

| VUSB3V3  | 20                                                                                    | 23                                        | 10          | Р                                                                  | —                                 | USB Internal Transceiver Supply. This pin must be connected to VDD. |  |  |  |  |  |

| VBUSON   | PPS                                                                                   | PPS                                       | PPS         | 0                                                                  | —                                 | USB Host and OTG Bus Power Control Output                           |  |  |  |  |  |

| D+       | 18                                                                                    | 21                                        | 8           | I/O                                                                | Analog                            | USB D+                                                              |  |  |  |  |  |

| D-       | 19                                                                                    | 22                                        | 9           | I/O                                                                | Analog                            | USB D-                                                              |  |  |  |  |  |

| USBID    | 11                                                                                    | 14                                        | 41          | I                                                                  | ST                                | USB OTG ID Detect                                                   |  |  |  |  |  |

| USBON    | 14                                                                                    | 17                                        | 44          | 0                                                                  |                                   | ON Signal for External VBUS Source                                  |  |  |  |  |  |

| 5        | ST = Schmi                                                                            | MOS compa<br>tt Trigger in<br>nput buffer |             | Analog = Analog input<br>O = Output<br>PPS = Peripheral Pin Select | P = Power<br>I = Input<br>— = N/A |                                                                     |  |  |  |  |  |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

**2:** All pins are only available on USB devices.

3: Pin number for devices without VBAT.

4: Pin number for devices with USB only.

5: Pin number for devices without USB.

## 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

## 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER<br/>MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

|                                 | IRQ | Vector |              | Persistent    |             |              |           |

|---------------------------------|-----|--------|--------------|---------------|-------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup> | #   | #      | Flag         | Enable        | Priority    | Sub-priority | Interrupt |

|                                 |     | Highes | st Natural C | rder Priority | ,           |              |           |

| CT – Core Timer Interrupt       | 0   | 0      | IFS0<0>      | IEC0<0>       | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0 | 1   | 1      | IFS0<1>      | IEC0<1>       | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1 | 2   | 2      | IFS0<2>      | IEC0<2>       | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt       | 3   | 3      | IFS0<3>      | IEC0<3>       | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                     | 4   | 4      | IFS0<4>      | IEC0<4>       | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E – Input Capture 1 Error    | 5   | 5      | IFS0<5>      | IEC0<5>       | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1           | 6   | 5      | IFS0<6>      | IEC0<6>       | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1          | 7   | 6      | IFS0<7>      | IEC0<7>       | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1     | 8   | 7      | IFS0<8>      | IEC0<8>       | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                     | 9   | 8      | IFS0<9>      | IEC0<9>       | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E – Input Capture 2          | 10  | 9      | IFS0<10>     | IEC0<10>      | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2           | 11  | 9      | IFS0<11>     | IEC0<11>      | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2          | 12  | 10     | IFS0<12>     | IEC0<12>      | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2     | 13  | 11     | IFS0<13>     | IEC0<13>      | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                     | 14  | 12     | IFS0<14>     | IEC0<14>      | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E – Input Capture 3          | 15  | 13     | IFS0<15>     | IEC0<15>      | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3           | 16  | 13     | IFS0<16>     | IEC0<16>      | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3          | 17  | 14     | IFS0<17>     | IEC0<17>      | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3     | 18  | 15     | IFS0<18>     | IEC0<18>      | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                     | 19  | 16     | IFS0<19>     | IEC0<19>      | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error    | 20  | 17     | IFS0<20>     | IEC0<20>      | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4           | 21  | 17     | IFS0<21>     | IEC0<21>      | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4          | 22  | 18     | IFS0<22>     | IEC0<22>      | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4     | 23  | 19     | IFS0<23>     | IEC0<23>      | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                     | 24  | 20     | IFS0<24>     | IEC0<24>      | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E – Input Capture 5 Error    | 25  | 21     | IFS0<25>     | IEC0<25>      | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5           | 26  | 21     | IFS0<26>     | IEC0<26>      | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5          | 27  | 22     | IFS0<27>     | IEC0<27>      | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done         | 28  | 23     | IFS0<28>     | IEC0<28>      | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor  | 29  | 24     | IFS0<29>     | IEC0<29>      | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and      | 30  | 25     | IFS0<30>     | IEC0<30>      | IPC6<12:10> | IPC6<9:8>    | No        |

| Calendar                        | 04  |        |              |               |             |              | NIa       |

| FCE – Flash Control Event       | 31  | 26     | IFS0<31>     | IEC0<31>      | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt     | 32  | 27     | IFS1<0>      | IEC1<0>       | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt     | 33  | 28     | IFS1<1>      | IEC1<1>       | IPC7<4:2>   | IPC7<1:0>    | No        |

| CMP3 – Comparator Interrupt     | 34  | 29     | IFS1<2>      | IEC1<2>       | IPC7<12:10> | IPC7<9:8>    | No        |

| USB – USB Interrupts            | 35  | 30     | IFS1<3>      | IEC1<3>       | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1E – SPI1 Fault              | 36  | 31     | IFS1<4>      | IEC1<4>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1RX – SPI1 Receive Done      | 37  | 31     | IFS1<5>      | IEC1<5>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1TX – SPI1 Transfer Done     | 38  | 31     | IFS1<6>      | IEC1<6>       | IPC7<28:26> | IPC7<25:24>  | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/44-Pin XLP (General Purpose) Family Features" and TABLE 2: "PIC32MX2XX 28/44-Pin XLP (USB) Family Features" for the lists of available peripherals.

| REGIS   | STER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10- | 8 NOSC<2:0>: New Oscillator Selection bits                                                                                                      |

|         | 111 = Reserved                                                                                                                                  |

|         | 110 = Reserved                                                                                                                                  |

|         | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                                                   |

|         | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                                             |

|         | 011 = Reserved<br>010 = Primary Oscillator (Posc) (HS or EC)                                                                                    |

|         | 001 = System PLL (SPLL)                                                                                                                         |

|         | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                    |

|         | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>                                                    |

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit                                                                                                        |

|         | 1 = Clock and PLL selections are locked                                                                                                         |

|         | 0 = Clock and PLL selections are not locked and may be modified                                                                                 |

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                      |

| bit 4   | SLPEN: Sleep Mode Enable bit                                                                                                                    |

|         | 1 = Device will enter Sleep mode when a WAIT instruction is executed                                                                            |

|         | 0 = Device will enter Idle mode when a WAIT instruction is executed                                                                             |

| bit 3   | CF: Clock Fail Detect bit                                                                                                                       |

|         | 1 = FSCM has detected a clock failure                                                                                                           |

|         | 0 = No clock failure has been detected                                                                                                          |

| bit 2   | UFRCEN: USB FRC Clock Enable bit                                                                                                                |

|         | 1 = Enable FRC as the USB clock source                                                                                                          |

|         | 0 = Use the Primary Oscillator or UPLL as the USB clock source                                                                                  |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                  |

|         | <ul> <li>1 = Enable Secondary Oscillator</li> <li>0 = Disable Secondary Oscillator</li> </ul>                                                   |

| hit O   | OSWEN: Oscillator Switch Enable bit <sup>(1)</sup>                                                                                              |

| bit 0   |                                                                                                                                                 |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul> |

|         |                                                                                                                                                 |

|         |                                                                                                                                                 |

**Note 1:** The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the reset value is '1'. When IESO = 0, the reset value is '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

# 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/44-pin XLP Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

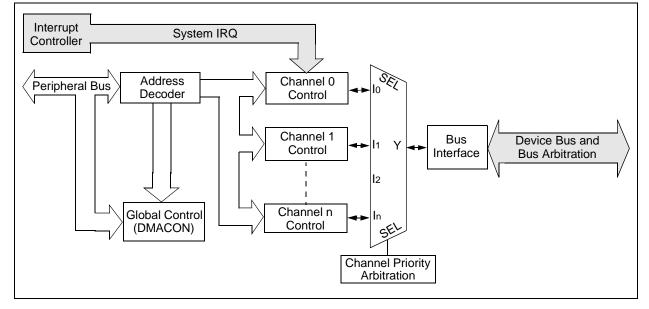

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

## FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

## REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address. **Note:** This must be the physical address of the destination.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 |                   | _                 |                   |                   |                   |                  | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | _                 | _                 | _                 | -                 | _                 | —                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |

## REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

## Legend:

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      | read as '0'        |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |

## bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source •

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

## REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   | _                 |                   | _                 | _                 | —                | _                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | _                 |                   | —                 |                   | —                | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        |                   | —                 | _                 | —                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | -                 | —                 | —                 | —                 | DCSZ<1:0>        |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | —                 | —                 | PREFEN<1:0>       |                   | —                 | PFMWS<2:0>        |                  |                  |

## REGISTER 10-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 **Unimplemented:** Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

|              | -                 |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 |                   | —                 |                   |                   |                  | -                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | —                 | _                 | _                 | -                | —                |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | -                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | CNT<7:0>          |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits

- Typical values of the threshold are:

- 01001010 = 64-byte packet

- 00101010 = 32-byte packet

- 00011010 = 16-byte packet

- 00010010 = 8-byte packet

## REGISTER 11-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   |                   |                   |                   |                   |                   |                  | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   | —                 |                   |                   |                   |                   | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         |                   |                   |                   |                   |                   |                   |                  | —                |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |

| 7.0          | BDTPTRL<15:9>     |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-1 **BDTPTRL<15:9>:** Buffer Descriptor Table Base Address bits This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

| REGISTE | ER 20-1: I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <b>GCEN:</b> General Call Enable bit (when operating as I <sup>2</sup> C slave)<br>1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)                                                                                                |

|         | 0 = General call address is disabled                                                                                                                                                                                                                                                            |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                           |

| bit 5   | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send a NACK during an Acknowledge sequence<br>0 = Send an ACK during an Acknowledge sequence |

| bit 4   | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as $I^2C$ master, applicable during master receive)                                                                                                                                                                               |

|         | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul>                                                                            |

| bit 3   | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence not in progress</li> </ul>                                                                                                                 |

| bit 2   | PEN: Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                      |

|         | <ul><li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li><li>0 = Stop condition not in progress</li></ul>                                                                                                                                  |

| bit 1   | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                                                             |

| bit 0   | <b>SEN:</b> Start Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                                                                        |

|         | <ul><li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li><li>0 = Start condition not in progress</li></ul>                                                                                                                               |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|

| 24.24        | U-0                     | U-0              |

| 31:24        |                   | —                 | _                 | —                 | —                 | —                 | —                       | —                |

| 00.40        | R/W-0             | R-0, HS, HC       | U-0               | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0            |

| 23:16        | SLPEN             | ACTIVE            | _                 | —                 | —                 | CLKSE             | CLKSEL<1:0> R           |                  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0                   | R/W-0            |

| 15:8         | ON                | —                 | SIDL              | IREN              | RTSMD             | —                 | UEN<1:0> <sup>(1)</sup> |                  |

| 7.0          | R/W-0                   | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>                   | STSEL            |

## REGISTER 21-1: UXMODE: UARTX MODE REGISTER

| Legend:           | HS = Hardware set | set HC = Hardware cleared          |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-24 Unimplemented: Read as '0'

- bit 23 SLPEN: Run During Sleep Enable bit

- 1 = UARTx BRG clock runs during Sleep mode

- 0 = UARTx BRG clock is turned off during Sleep mode

- **Note:** SLPEN = 1 only applies if CLKSEL = FRC. All clocks, as well as the UART, are disabled in Deep Sleep mode.

- bit 22 ACTIVE: UARTx Module Running Status bit

- 1 = UARTx module is active (UxMODE register should not be updated)

- 0 = UARTx module is not active (UxMODE register can be updated)

- bit 21-19 Unimplemented: Read as '0'

- bit 18-17 CLKSEL<1:0>: UARTx Module Clock Selection bits

- 11 = BRG clock is PBCLK2

- 10 = BRG clock is FRC

- 01 = BRG clock is SYSCLK (turned off in Sleep mode)

- 00 = BRG clock is PBCLK2 (turned off in Sleep mode)

#### bit 16 **RUNOVF:** Run During Overflow Condition Mode bit

- 1 = When an Overflow Error (OERR) condition is detected, the shift register continues to run to remain synchronized

- 0 = When an Overflow Error (OERR) condition is detected, the shift register stops accepting new data (Legacy mode)

#### bit 15 ON: UARTx Enable bit

- 1 = UARTx module is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- 0 = UARTx module is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx, and LATx registers; UARTx power consumption is minimal

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see 12.3 "Peripheral Pin Select" for more information).

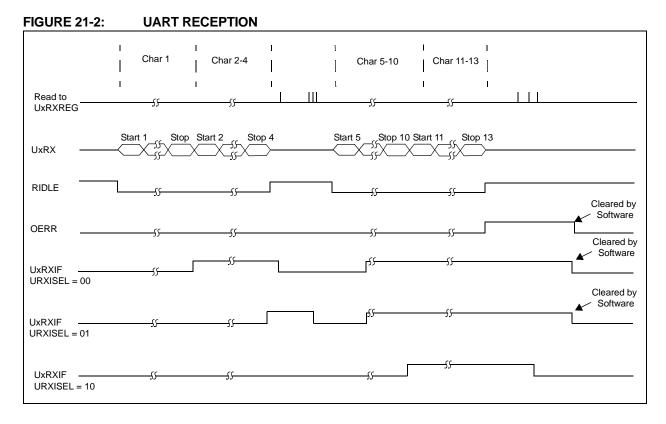

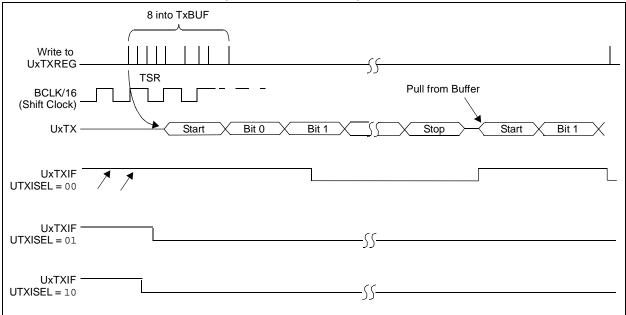

Figure 21-2 and Figure 21-3 illustrate typical receive and transmit timing for the UART module.

# PIC32MX1XX/2XX 28/44-PIN XLP FAMILY

## REGISTER 24-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | —                        | —                 | —                 | —                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | _                        | _                 | —                 | —                | _                |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ADRC              | —                 | _                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |

| 7:0          |                   |                   |                   | ADCS<                    | 7:0> <b>(2)</b>   |                   |                  |                  |  |  |

## Legend:

| R = Readable bit  | bit W = Writable bit |                      | ead as '0'         |

|-------------------|----------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ADRC:** ADC Conversion Clock Source bit 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- **2:** This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        | _                 | —                 | —                 | _                 | —                 | —                 | FWDTWI           | NSZ<1:0>         |  |

| 00.40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | WDTSPGM           |                   | WDTPS<4:0>        |                   |                  |                  |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM<1:0>        |                   | FPBDIV<1:0>       |                   | - OSCIOFNC        |                   | POSCMOD<1:0>     |                  |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | —                 | FSOSCEN           |                   | —                 | - FNOSC<2         |                  |                  |  |

## REGISTER 30-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | egend: r = Reserved bit P = Programmable bit |                                    |                    |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

- bit 23 **FWDTEN:** Watchdog Timer Enable bit 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

- bit 22 **WINDIS:** Watchdog Timer Window Enable bit 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

- bit 21 **WDTSPGM:** Watchdog Timer Stop During Flash Programming bit 1 = Watchdog Timer stops during Flash programming

- 1 = Watchdog Timer stops during Flash programming 0 = Watchdog Timer runs during Flash programming

- bit 20-16 WDTPS<4.0>• Watchdog Timer Postecolo Soloct bits

| 20-16 | WDTPS<4:0>: Watchdog Timer Postscale Select bits             |

|-------|--------------------------------------------------------------|

|       | 10100 <b>= 1:1048576</b>                                     |

|       | 10011 <b>= 1:524288</b>                                      |

|       | 10010 <b>= 1:262144</b>                                      |

|       | 10001 = 1:131072                                             |

|       | 10000 <b>= 1:65536</b>                                       |

|       | 01111 <b>= 1:32768</b>                                       |

|       | 01110 <b>= 1:16384</b>                                       |

|       | 01101 = 1:8192                                               |

|       | 01100 <b>= 1:4096</b>                                        |

|       | 01011 <b>= 1:2048</b>                                        |

|       | 01010 = 1:1024                                               |

|       | 01001 <b>= 1:512</b>                                         |

|       | 01000 <b>= 1:256</b>                                         |

|       | 00111 <b>= 1:128</b>                                         |

|       | 00110 <b>= 1:64</b>                                          |

|       | 00101 <b>= 1:32</b>                                          |

|       | 00100 <b>= 1:16</b>                                          |

|       | 00011 = 1:8                                                  |

|       | 00010 = 1:4                                                  |

|       | 00001 = 1:2                                                  |

|       | 00000 = 1:1                                                  |

|       | All other combinations not shown result in operation = 10100 |

|       |                                                              |

Note 1: Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

## TABLE 33-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

|                   |        |                                                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |       |            |  |

|-------------------|--------|---------------------------------------------------------------------------|-------------------------------------------------------|------|-------|-------|------------|--|

| Param.<br>No.     | Symbol | Characteristics                                                           | Min.                                                  | Тур. | Max.  | Units | Conditions |  |

| Operating Voltage |        |                                                                           |                                                       |      |       |       |            |  |

| DC10              | Vdd    | Supply Voltage (Note 2)                                                   | 2.5                                                   |      | 3.6   | V     | —          |  |

| DC12              | Vdr    | RAM Data Retention Voltage<br>(Note 1)                                    | 2.0                                                   | _    | —     | V     | _          |  |

| DC16              | VPOR   | VDD Start Voltage (Note 3)<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                  | _    | 2.1   | V     | _          |  |

| DC17              | SVDD   | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal              | 0.00005                                               | _    | 0.115 | V/µs  | _          |  |

| DC18              | VBAT   | Battery Supply Voltage                                                    | 1.94                                                  | _    | 3.6   | V     | —          |  |

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 33-5 for BOR values.

**3:** VDD voltage must remain below VPOR for a minimum of 200 µs to ensure POR.

## TABLE 33-5: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |       |            |  |

|--------------------|--------|--------------------------------------------------|-------------------------------------------------------|------|-------|-------|------------|--|

| Param.<br>No.      | Symbol | ool Characteristics                              |                                                       | Тур. | Max.  | Units | Conditions |  |

| BO10               | VBOR   | BOR Event on VDD transition high-to-low (Note 2) | 2.2                                                   |      | 2.384 | V     | _          |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

| DC<br>CHARAC  | TERISTICS              |               | $\begin{array}{ll} \mbox{Standard Operating Conditions: } 2.5V \mbox{ to } 3.6V \mbox{ (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |        |                                                         |  |  |  |

|---------------|------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Maximum       | Units                                                                                                                                                                                                                                                                                          |        | Conditions                                              |  |  |  |

| Power-Do      | own Curren             | t (IPD) (Note | 1)                                                                                                                                                                                                                                                                                             |        |                                                         |  |  |  |

| DC40k         |                        |               | μA                                                                                                                                                                                                                                                                                             | -40°C  |                                                         |  |  |  |

| DC40I         | 25                     | 42            | μA                                                                                                                                                                                                                                                                                             | +25°C  | Sloop (Note 1)                                          |  |  |  |

| DC40m         | 240                    | 390           | μA                                                                                                                                                                                                                                                                                             | +85°C  | Sleep (Note 1)                                          |  |  |  |

| DC40n         | _                      |               | μA                                                                                                                                                                                                                                                                                             | +105°C |                                                         |  |  |  |

| DC41k         | _                      |               | nA                                                                                                                                                                                                                                                                                             | -40°C  |                                                         |  |  |  |

| DC41I         | 673                    | 800           | nA                                                                                                                                                                                                                                                                                             | +25°C  | Deep Sleep (Note 5)                                     |  |  |  |

| DC41m         | _                      |               | nA                                                                                                                                                                                                                                                                                             | +85°C  | Deep Sleep (Note 5)                                     |  |  |  |

| DC41n         | _                      |               | nA                                                                                                                                                                                                                                                                                             | +105°C |                                                         |  |  |  |

| DC42k         | _                      |               | nA                                                                                                                                                                                                                                                                                             | -40°C  |                                                         |  |  |  |

| DC42I         | _                      |               | nA                                                                                                                                                                                                                                                                                             | +25°C  | VBAT <b>(Note 6)</b>                                    |  |  |  |

| DC42m         | _                      |               | nA                                                                                                                                                                                                                                                                                             | +85°C  | VDAT (NOLE O)                                           |  |  |  |

| DC42n         | _                      | _             | nA                                                                                                                                                                                                                                                                                             | +105°C |                                                         |  |  |  |

| Module D      | oifferential (         | Current       |                                                                                                                                                                                                                                                                                                |        |                                                         |  |  |  |

| DC44a         | 5                      | _             | μA                                                                                                                                                                                                                                                                                             | 3.6V   | Watchdog Timer Current: AIWDT (Note 3)                  |  |  |  |